(12) 发明专利

(10) 授权公告号 CN 102914924 B

(45) 授权公告日 2016.01.20

(21) 申请号 201210390814.1

(56) 对比文件

(22) 申请日 2006.12.05

US 6552706 B1, 2003.04.22,

(30) 优先权数据

US 2003/0146893 A1, 2003.08.07,

10-2005-0118067 2005.12.06 KR

US 6552706 B1, 2003.04.22,

(62) 分案原申请数据

审查员 桑青

200610164539.6 2006.12.05

(73) 专利权人 三星显示有限公司

地址 韩国京畿道龙仁市

(72) 发明人 白承洙 金东奎 李柏远

(74) 专利代理机构 北京铭硕知识产权代理有限

公司 11286

代理人 刘灿强

(51) Int. Cl.

G02F 1/1362(2006.01)

G02F 1/1368(2006.01)

G02F 1/133(2006.01)

G09G 3/36(2006.01)

权利要求书2页 说明书7页 附图8页

(54) 发明名称

显示装置

(57) 摘要

本发明公开了一种具有显示装置特定的像素布置的显示装置，以防止在高速驱动时的连接缺陷和带缺陷。所述显示装置包括：多个像素，以矩阵形状布置；开关元件，连接到每个像素；数据线和栅极线，连接到所述开关元件；数据驱动器，产生数据电压并将数据电压施加到数据线。成对的数据线设置在像素的两侧，具有不同极性的相同幅度的数据电压被施加到成对的数据线。以这种方式，可以防止高速驱动时的连接缺陷和带缺陷。

1. 一种显示装置，包括：

第一像素，所述第一像素包括：

第一子像素，具有第一子像素电极和第一薄膜晶体管，以及

第二子像素，具有第二子像素电极和第二薄膜晶体管；

与第一像素相邻的第二像素，所述第二像素设置在所述第一像素的右侧，所述第二像素包括：

第三子像素，具有第三子像素电极和第三薄膜晶体管，以及

第四子像素，具有第四子像素电极和第四薄膜晶体管；

栅极线，电连接到第一子像素、第二子像素、第三子像素和第四子像素，所述栅极线沿着第一方向延伸并被构造成传输栅极信号；

第一数据线，电连接到第二子像素，第一数据线沿着第二方向延伸并被构造成传输第一数据电压；

第二数据线，电连接到第一子像素，第二数据线沿着第二方向延伸，设置在第一数据线的右侧，并被构造成传输第二数据电压；

第三数据线，电连接到第三子像素，第三数据线沿着第二方向延伸，设置在第二数据线的右侧，并被构造成传输第三数据电压；以及

第四数据线，电连接到第四子像素，第四数据线沿着第二方向延伸，设置在第三数据线的右侧，并被构造成传输第四数据电压，

其中，在平面图中，第一子像素电极与第二子像素电极分隔开，

第一薄膜晶体管设置在栅极线的上侧，第二薄膜晶体管设置在栅极线的下侧，

在平面图中，第三子像素电极与第四子像素电极分隔开，

第三薄膜晶体管设置在栅极线的上侧，第四薄膜晶体管设置在栅极线的下侧，

所述第一像素的第一子像素连接到第二数据线，所述第一像素的第二子像素连接到第一数据线，所述第二像素的第三子像素连接到第三数据线，所述第二像素的第四子像素连接到第四数据线，

栅极线设置在第一子像素与第二子像素之间并在第三子像素与第四子像素之间，

第一子像素和第二子像素被设置成对应于第一滤色器，第三子像素和第四子像素被设置成对应于第二滤色器。

2. 根据权利要求 1 所述的显示装置，其中，第一数据电压不同于第二数据电压，由单个图像信息获得第一数据电压和第二数据电压，第三数据电压不同于第四数据电压，由另一个单个图像信息获得第三数据电压和第四数据电压。

3. 根据权利要求 2 所述的显示装置，其中，第一数据电压具有与第二数据电压的极性相反的极性，第三数据电压具有与第四数据电压的极性相反的极性，第一数据电压和第三数据电压具有相同的极性，第四数据电压和第二数据电压具有相同的极性。

4. 根据权利要求 3 所述的显示装置，其中，第一子像素和第二子像素设置在第一数据线与第二数据线之间，第三子像素和第四子像素设置在第三数据线与第四数据线之间。

5. 根据权利要求 1 所述的显示装置，其中，第一数据电压具有与第二数据电压的极性相反的极性，第三数据电压具有与第四数据电压的极性相反的极性，第一数据电压和第三数据电压具有相同的极性，第四数据电压和第二数据电压具有相同的极性。

6. 根据权利要求 5 所述的显示装置,其中,第一子像素和第二子像素设置在第一数据线与第二数据线之间,第三子像素和第四子像素设置在第三数据线与第四数据线之间。

7. 根据权利要求 1 所述的显示装置,其中,第一子像素和第二子像素设置在第一数据线与第二数据线之间,第三子像素和第四子像素设置在第三数据线与第四数据线之间。

8. 根据权利要求 1 所述的显示装置,其中,第一数据电压不同于第二数据电压,由单个图像信息获得第一数据电压和第二数据电压,第三数据电压不同于第四数据电压,由另一个单个图像信息获得第三数据电压和第四数据电压。

9. 根据权利要求 8 所述的显示装置,其中,第一数据电压具有与第二数据电压的极性相反的极性,第三数据电压具有与第四数据电压的极性相反的极性,第一数据电压和第三数据电压具有相同的极性,第四数据电压和第二数据电压具有相同的极性。

10. 根据权利要求 9 所述的显示装置,其中,第一子像素和第二子像素设置在第一数据线与第二数据线之间,第三子像素和第四子像素设置在第三数据线与第四数据线之间。

11. 根据权利要求 8 所述的显示装置,其中,第一子像素和第二子像素设置在第一数据线与第二数据线之间,第三子像素和第四子像素设置在第三数据线与第四数据线之间。

12. 根据权利要求 1 所述的显示装置,其中,第一数据电压具有与第二数据电压的极性相反的极性,第三数据电压具有与第四数据电压的极性相反的极性,第一数据电压和第三数据电压具有相同的极性,第四数据电压和第二数据电压具有相同的极性。

13. 根据权利要求 12 所述的显示装置,其中,第一子像素和第二子像素设置在第一数据线与第二数据线之间,第三子像素和第四子像素设置在第三数据线与第四数据线之间。

14. 根据权利要求 1 所述的显示装置,其中,第一子像素和第二子像素设置在第一数据线与第二数据线之间,第三子像素和第四子像素设置在第三数据线与第四数据线之间。

## 显示装置

[0001] 本申请是 2006 年 12 月 5 日提交的专利申请 200610164539.6 的分案申请。

### 技术领域

[0002] 本公开涉及一种液晶显示器。

### 背景技术

[0003] 传统的液晶显示器(LCD)包括设置有像素电极和共电极的两个显示面板,以及设置在这两个面板之间并具有介电各向异性的液晶层。像素电极以矩阵形状布置并连接到开关元件(如薄膜晶体管(TFT)),从而被逐行顺次地施加数据电压。共电极形成在显示面板的整个表面上并被施加共电压。从电路角度来看,像素电极、共电极和它们之间的液晶层形成液晶电容器,该液晶电容器是与连接到其的开关元件一起组成像素的基本单元。

[0004] 在这种液晶显示器中,对两个电极施加电压,从而在液晶层中形成电场,通过调节电场的幅值来调节穿过液晶层的光的透射率,从而获得期望的图像。为了防止对液晶层长时间在一个方向上施加电场而导致的退化现象,对于各个帧、各个行或各个像素,数据电压相对于共电压的极性被反转。

[0005] 目前正将各种方法作为一种尝试来改进这种液晶显示器的运动画面显示特性,例如,以每秒 120 帧的速度驱动的高速驱动方法正处于开发中。对于高速驱动,液晶的响应速度应该是每秒 60 帧的速度的两倍,目前估计这是可能的。

[0006] 另外,由于在高速驱动技术中使用高的帧速度导致消耗大量的电功率,所以已经通过采用反转驱动方法中的列反转来进行将功耗最小化的尝试。

[0007] 列反转按一帧改变相同数据线的数据电压的极性,由于在一帧中数据电压的反转次数是一,所以基本提高了功耗特性。

[0008] 然而,列反转中存在两个问题。问题之一是连接缺陷(coupling defect),另一问题是带缺陷(stripe defect)。

[0009] 连接缺陷是因为由于通过数据线和像素电极的叠置而产生寄生电容使得对一帧连续施加相同极性的电压,所以液晶面板组件的上部和下部的各自的亮度变得彼此不同的现象。更具体地讲,如果在具有低灰度值的根图像(rootimage)上显示具有比根图像的灰度值大的灰度值的盒状单元(box),则盒状单元以上和以下的部分具有与根图像不同的灰度值,在这种情况下出现垂直串扰现象。为了解决这种连接缺陷,由数据线与像素电极的叠置导致的寄生电容与该设备的整个电容的比率应该小于或等于 1%,但是很难实现。

[0010] 带缺陷是在垂直方向施加相同极性的数据电压并且正极性的数据电压和负极性的数据电压之间存在差别时形成带的现象。

[0011] 在背景部分中公开的以上信息仅用于提高对本发明背景的理解,因此,也可能包含没有形成本领域的普通技术人员在国内公知的现有技术的信息。

### 发明内容

[0012] 本发明的示例性实施例提供了一种具有在显示器的高速驱动下防止连接缺陷和带缺陷的优点的液晶显示器。

[0013] 本发明的示例性实施例提供了一种液晶显示器，所述液晶显示器包括：多个像素，以矩阵形状布置；开关元件，连接到各像素；数据线和栅极线，连接到所述开关元件；数据驱动器，产生数据电压和将所述数据电压施加到所述数据线。所述数据线成对地布置在所述像素的两侧，具有不同的极性的相同幅度的数据电压被施加到所述成对的数据线。

[0014] 每个像素的所述开关元件可仅连接到所述成对的数据线之一，在像素列的垂直方向上两个相邻的像素的开关元件交替地连接到所述成对的数据线。

[0015] 所述数据驱动器可执行  $N \times 2$  反转。

[0016] 所述像素列中第偶数列的像素布置和第奇数像素列的像素布置相对于位于它们之间的数据线可形成镜像对称，所述数据驱动器可执行  $N \times 1$  反转。

[0017] 根据本发明的示例性实施例的液晶显示器包括：多个像素，以矩阵形状布置，并且每个像素包括第一子像素和第二子像素；第一开关元件和第二开关元件，连接到所述第一子像素和第二子像素；数据线和栅极线，连接到所述第一子像素和第二子像素；数据驱动器，产生数据电压并将所述数据电压施加到所述数据线。所述数据线成对地布置在所述像素的两侧，具有不同的极性的相同幅度的数据电压被施加到所述成对的数据线。

[0018] 所述像素的所述第一开关元件和所述第二开关元件可分别连接到所述成对的数据线的不同数据线，所述数据驱动器可执行  $N \times 2$  反转。

[0019] 可选地，所述数据驱动器可执行  $N \times 1$  反转。

[0020] 所述像素列中第偶数列的像素布置和第奇数像素列的像素布置可相对于位于它们之间的数据线形成镜像对称。

[0021] 在列方向上相邻像素的第一子像素和第二子像素的第一开关元件和第二开关元件可连接到相同的数据线。

[0022] 所述像素列中第偶数列的像素布置和第奇数像素列的像素布置可相对于位于它们之间的数据线形成镜像对称。

## 附图说明

[0023] 以下简要描述的附图与说明书一起示出了本发明的示例性实施例，以解释本发明的原理。

[0024] 图 1 是根据本发明的示例性实施例的液晶显示器的框图。

[0025] 图 2 是根据本发明的示例性实施例的液晶显示器的一个像素的等效电路图。

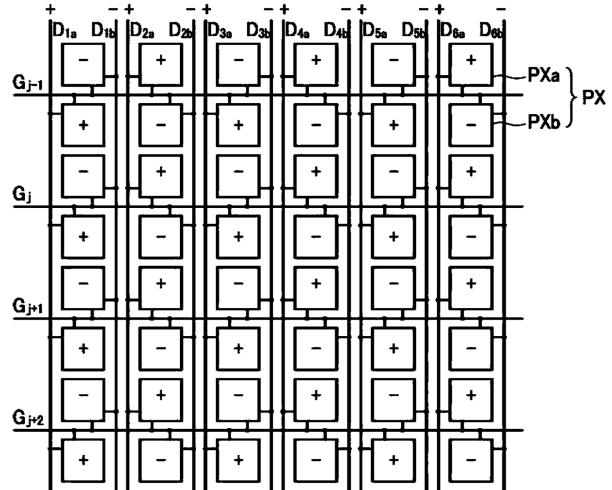

[0026] 图 3 是示出根据本发明的示例性实施例的液晶显示器的像素布置的视图。

[0027] 图 4 是示出根据本发明的示例性实施例的液晶显示器的像素布置的示例的视图。

[0028] 图 5 是用于解释在图 4 所示的像素布置中去除连接缺陷的原理的波形图。

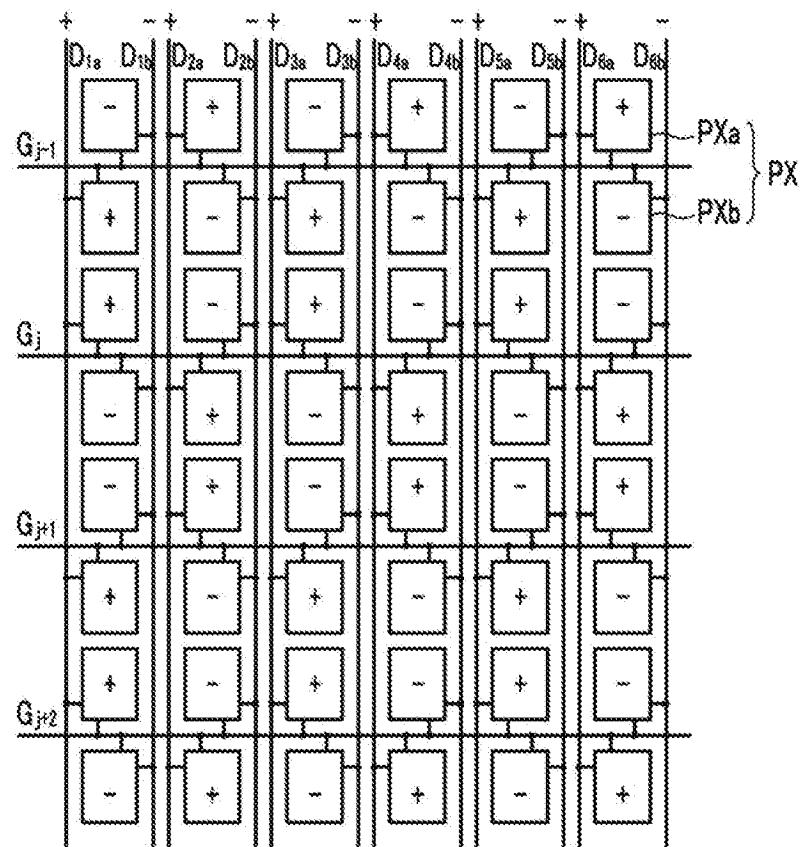

[0029] 图 6A 和图 6B 是示出图 4 所示的像素布置的示例性改变的视图。

[0030] 图 7 是示出根据本发明的示例性实施例的液晶显示器的像素布置的视图。

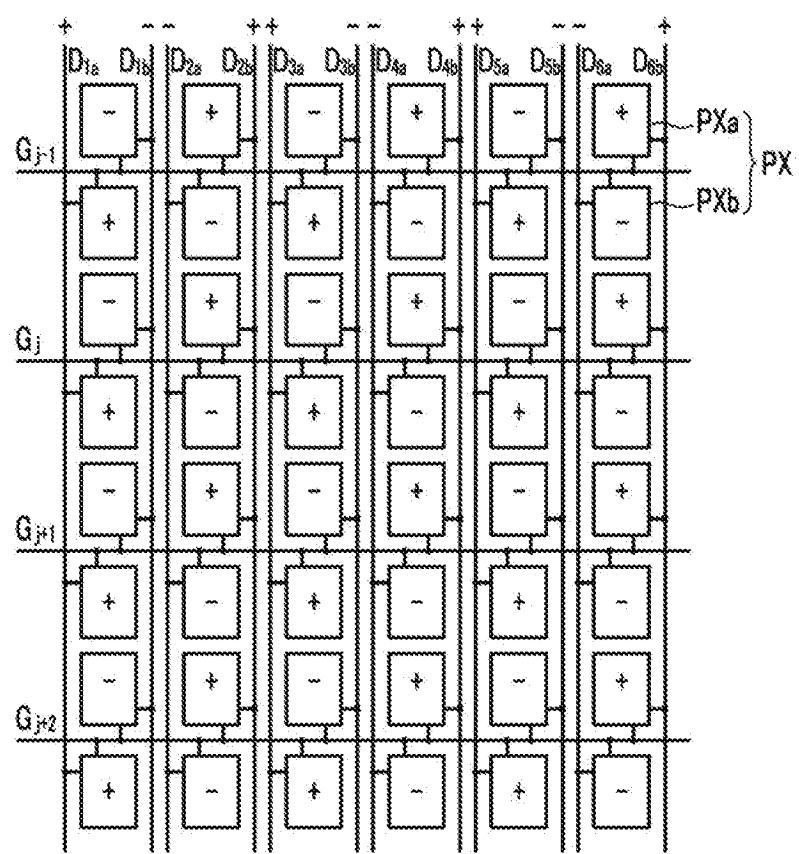

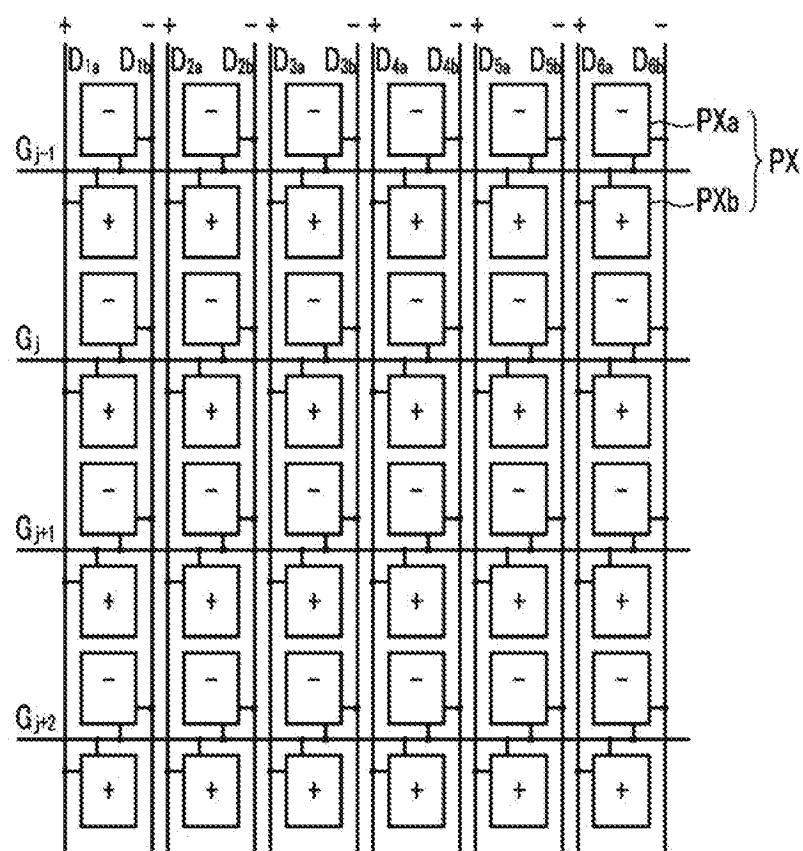

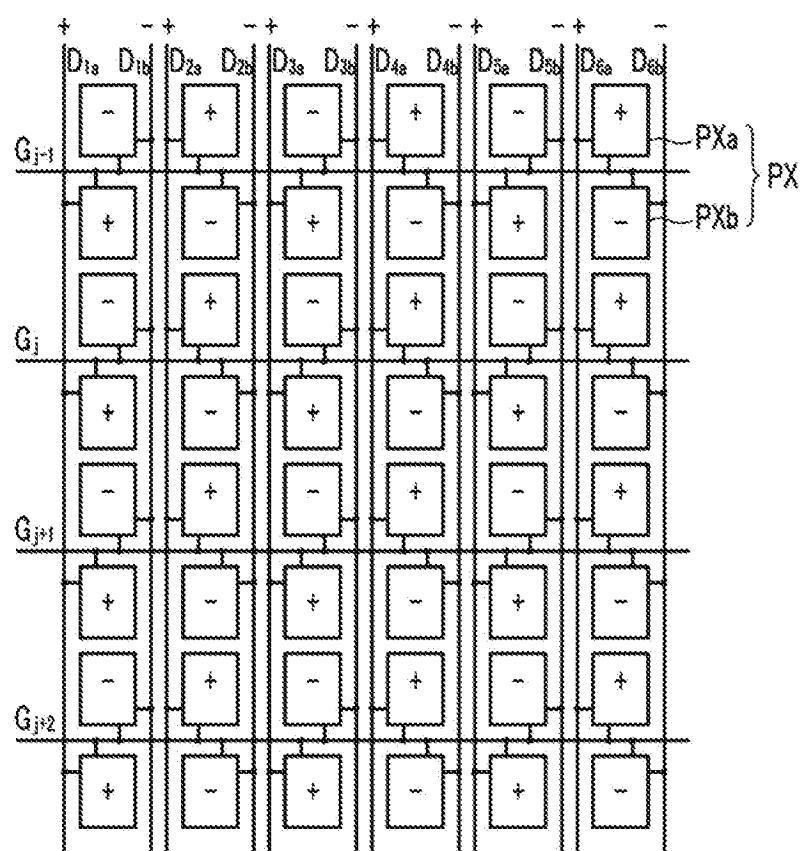

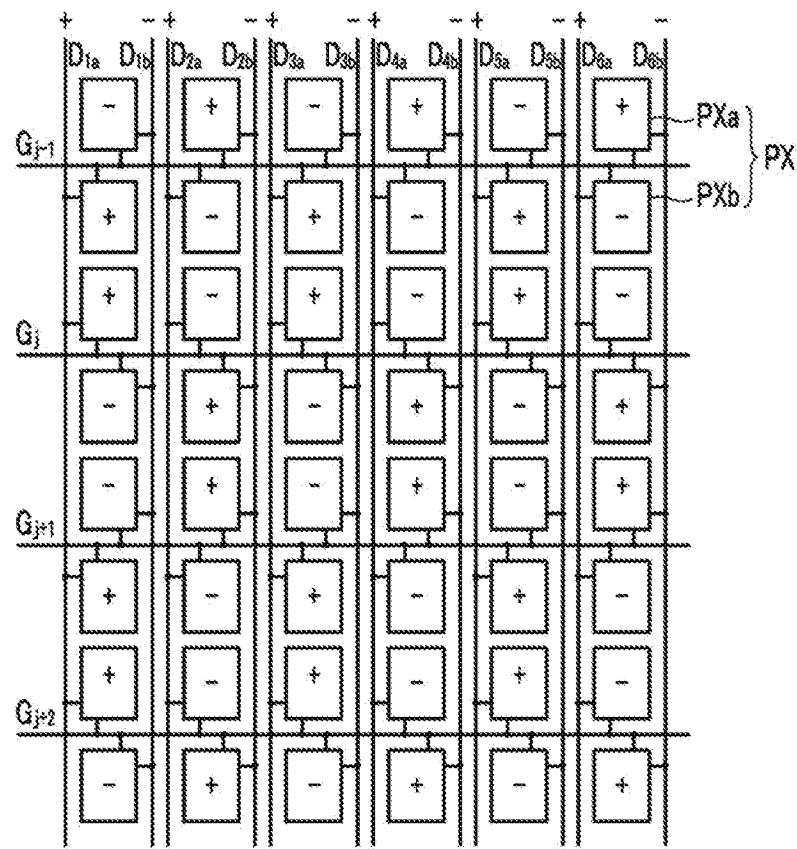

[0031] 图 8A 至图 8D 是示出图 7 所示的像素布置的示例性改变的视图。

## 具体实施方式

[0032] 现在将参照附图更充分地描述本发明，本发明的示例性实施例示出在附图中。

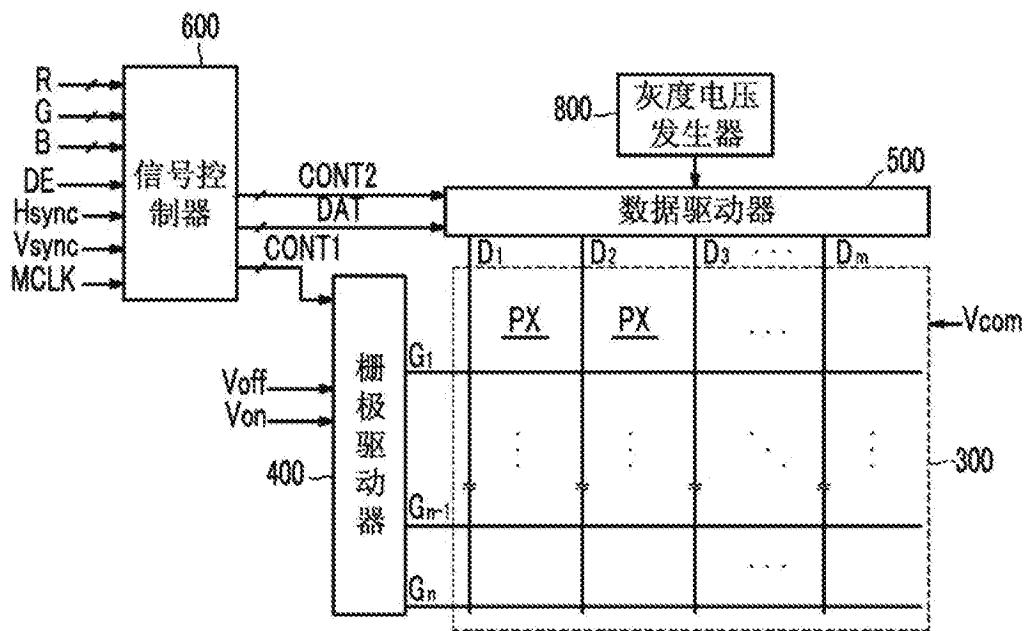

[0033] 现在将参照图 1 和图 2 详细说明根据本发明示例性实施例的液晶显示器。

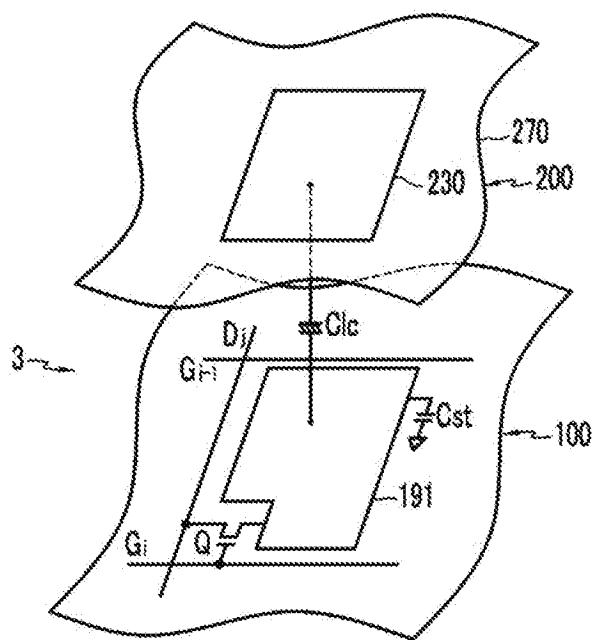

[0034] 图 1 是根据本发明示例性实施例的液晶显示器的框图，图 2 是根据本发明示例性实施例的液晶显示器的一个像素的等效电路图。

[0035] 如图 1 所示，根据本发明示例性实施例的液晶显示器包括液晶面板组件 300、连接到液晶面板组件 300 的栅极驱动器 400 和数据驱动器 500、连接到数据驱动器 500 的灰度电压发生器 800 和控制这些元件的信号控制器 600。

[0036] 根据等效电路，液晶面板组件 300 包括多条信号线  $G_1$  至  $G_n$  和  $D_1$  至  $D_m$ ，以及连接到这些信号线并基本以矩阵形状排列的多个像素 PX。同时，在图 2 所示的结构中，图 1 中的液晶面板组件 300 包括彼此面对的下面板 100 和上面板 200，以及置于面板 100 和 200 之间的液晶层 3 (未示出)。

[0037] 信号线  $G_1$  至  $G_n$  和  $D_1$  至  $D_m$  包括多条传输栅极信号(也称作扫描信号)的栅极线  $G_1$  至  $G_n$  和多条传输数据信号的数据线  $D_1$  至  $D_m$ 。栅极线  $G_1$  至  $G_n$  在行方向基本相互平行地延伸，数据线  $D_1$  至  $D_m$  在列方向基本相互平行地延伸。

[0038] 每个像素 PX，例如，连接到第  $i$  ( $i=1, 2, \dots, n$ ) 栅极线  $G_i$  和第  $j$  ( $j = 1, 2, \dots, m$ ) 数据线  $D_j$  的像素 PX 包括连接到信号线  $G_i$  和  $D_j$  的开关元件 Q 以及连接到开关元件 Q 的液晶电容器 Clc 和存储电容器 Cst。如果需要，可以省略存储电容器 Cst。

[0039] 开关元件 Q 是设置在下面板 100 上的三端子元件，如薄膜晶体管，该元件的控制端连接到栅极线  $G_i$ ，该元件的输入端连接到数据线  $D_j$ ，该元件的输出端连接到液晶电容器 Clc 和存储电容器 Cst。

[0040] 液晶电容器 Clc 具有两个端子，一端连接到下面板 100 的像素电极 191，另一端连接到上面板 200 的共电极 270。位于两个电极 191 和 270 之间的液晶层 3 作为介电材料。像素电极 191 连接到开关元件 Q，共电极 270 可以形成在上面板 200 的整个表面上。对共电极 270 施加共电压 Vcom。与图 2 中所示的不同，共电极 270 可设置在下面板 100 上。在这种情况下，两个电极 191 和 270 中的至少一个可以形成为线形或条形。

[0041] 存储电容器 Cst 补充液晶电容器 Clc，并具有单独的信号线(未示出)，当设置在下面板 100 上的像素电极 191 相互叠置并且其间设置有绝缘体时形成存储电容器 Cst。对单独的信号线施加固定的电压(如共电压 Vcom)。存储电容器 Cst 也可以通过通过绝缘体彼此叠置布置的像素电极 191 和叠置的前一栅极线来形成。

[0042] 对于彩色显示，随着时间的流逝，每个像素 PX 唯一地显示三原色中的一种颜色(空间划分)或每个像素 PX 交替地显示三原色(时间划分)，通过原色的空间或时间和来识别期望的颜色。三原色的示例包括红色、绿色和蓝色。图 2 示出了空间划分的示例。在这个示例中，每个像素 PX 在上面板 200 的与像素电极 191 对应的区域中具有用于原色之一的滤色器 230。与图 2 中所示的不同，滤色器 230 可以形成在下面板 100 的像素电极 191 的上方或下方。

[0043] 将用于使光偏振的至少一个偏振器(未示出)附于液晶面板组件 300 的外表面上。

[0044] 再次参照图 1，灰度电压发生器 800 产生两组灰度电压，这两组灰度电压与形成一组基准灰度电压的像素 PX 的透光率有关。这两组灰度电压分别相对于共电压 Vcom 具有正值和负值。

[0045] 棚极驱动器 400 连接到液晶面板组件 300 的棚极线  $G_1$  至  $G_n$ , 并将棚极信号施加到棚极线  $G_1$  至  $G_n$ , 其中, 所述棚极信号是棚极导通电压  $V_{on}$  和棚极截止电压  $V_{off}$  的组合。

[0046] 数据驱动器 500 连接到液晶显示面板组件 300 的数据线  $D_1$  至  $D_m$ 。数据驱动器 500 从灰度电压发生器 800 选择一个灰度电压, 并将选择的灰度电压施加到数据线  $D_1$  至  $D_m$  作为数据信号。然而在灰度电压发生器 800 只提供预定数量的基准灰度电压, 而不提供所有灰度级的电压的情况下, 数据驱动器 500 划分基准灰度电压, 以产生用于所有灰度级的灰度电压并从这些灰度电压中选择数据电压。

[0047] 信号控制器 600 控制棚极驱动器 400、数据驱动器 500 和其它元件。

[0048] 这些显示驱动元件 400、500、600 和 800 的每个可以以至少一个 IC 芯片的形式直接安装在液晶面板组件 300 上, 可以通过 TCP (载带封装) 安装在柔性印刷电路膜(未示出)上的同时附于液晶面板组件 300, 或者可以安装在单独的印刷电路板(未示出)上。可选择地, 驱动元件 400、500、600 或 800 可以与信号线  $G_1$  至  $G_n$  和  $D_1$  至  $D_m$  以及薄膜晶体管开关元件 Q 一起与液晶面板组件 300 集成。可选择地, 驱动元件 400、500、600 或 800 可集成为单一芯片。在这种情况下, 所述元件中的至少一个, 或组成这些元件的至少一个电路元件可以在单一芯片的外部。

[0049] 现在将详细描述液晶显示器的显示操作。

[0050] 信号控制器 600 接收输入图像信号 R、G、B 和用于控制输入图像信号 R、G、B 的显示的输入控制信号。输入控制信号的示例包括垂直同步信号 Vsync、水平同步信号 Hsync、主时钟信号 MCLK 和数据使能信号 DE 等。

[0051] 信号控制器 600 基于输入图像信号 R、G、B 根据液晶面板组件 300 的操作条件来处理输入图像信号 R、G、B, 并产生棚极控制信号 CONT1 和数据控制信号 CONT2。然后, 信号控制器 600 将棚极控制信号 CONT1 供给至棚极驱动器 400, 将数据控制信号 CONT2 和处理的图像信号 DAT 供给至数据驱动器 500。

[0052] 棚极控制信号 CONT1 可包括指示开始扫描的扫描起始信号和控制棚极导通电压  $V_{on}$  的输出时序的至少一个棚极时钟信号。棚极控制信号 CONT1 还可以包括限制棚极导通电压  $V_{on}$  的持续时间的输出使能信号。

[0053] 数据控制信号 CONT2 包括: 水平同步起始信号, 用于通知对像素 PX 的一行发送输出图像信号 DAT; 加载信号, 用于指示将数据信号施加到数据线  $D_1$  至  $D_m$ ; 和数据时钟信号。数据控制信号 CONT2 还可以包括用于将数据信号相对于共电压  $V_{com}$  的电压极性反转的反转信号, 以下, 将数据信号相对于共电压的电压极性简称为数据信号的极性。

[0054] 根据来自信号控制器 600 的数据控制信号 CONT2, 数据驱动器 500 接收用于像素 PX 的一行(组)的数字图像信号 DAT, 然后从灰度电压发生器 800 选择与每个数字图像信号 DAT 对应的灰度电压。随后, 数据驱动器 500 将数字图像信号 DAT 转换成模拟数据信号, 并将模拟数据信号施加到对应的数据线  $D_1$  至  $D_m$ 。

[0055] 棚极驱动器 400 根据来自信号控制器 600 的棚极控制信号 CONT1, 将棚极导通电压  $V_{on}$  施加到棚极线  $G_1$  至  $G_n$ , 以导通与棚极线  $G_1$  至  $G_n$  连接的开关元件 Q。因此, 通过导通的开关元件 Q 将施加到数据线  $D_1$  至  $D_m$  的数据信号施加到对应的像素 PX。

[0056] 施加到像素 PX 的数据信号的电压和共电压  $V_{com}$  之间的差为液晶电容器  $C_{lc}$  的充电电压, 即, 为像素电压。液晶分子的取向根据像素电压的值而变化, 因此, 改变穿过液晶层

3的光的偏振。偏振的改变导致通过附于液晶面板组件 300 的偏振器的光的透射率的改变。

[0057] 通过对每一个水平周期(称作“1H”，等于水平同步信号 Hsync 和数据使能信号 DE 的一个周期)重复这个操作,对所有栅极线 G<sub>1</sub>至 G<sub>n</sub>顺序地施加栅极导通电压 Von,对所有像素 PX 施加数据信号,从而显示与一帧对应的图像。

[0058] 当完成一帧时,下一帧开始,控制将被施加到数据驱动器 500 的反转信号的状态,从而将被施加到每个像素的数据电压的极性与其在前一帧的极性相反(帧反转)。同时,根据反转信号的特性,可以在一帧内改变一条数据线上的数据信号的极性(例如行反转或点反转),或者施加到一个像素行的数据信号的极性可以彼此不同(例如列反转或点反转)。

[0059] 现在将参照图 3 至图 8D 详细解释根据本发明示例性实施例的液晶显示器的像素布置。

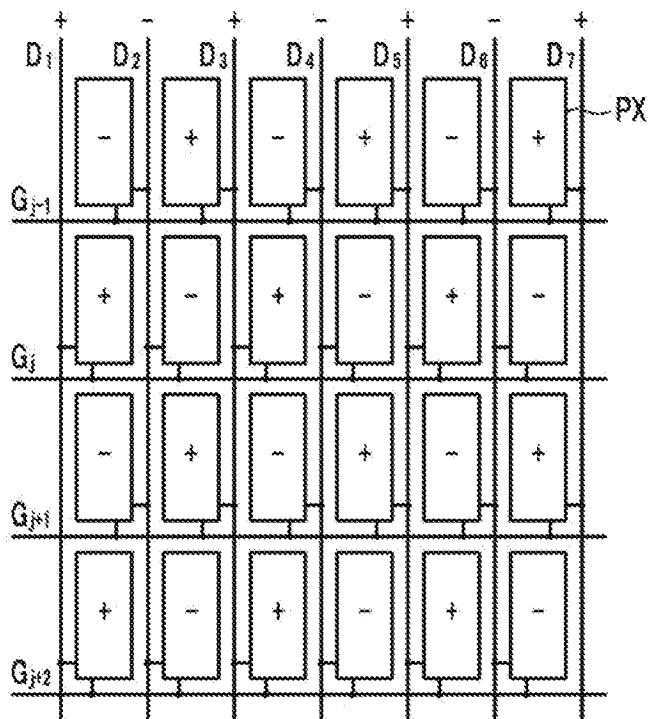

[0060] 图 3 是示出根据本发明示例性实施例的液晶显示器的像素布置的视图。

[0061] 这里,为了更好的理解和便于描述,示出了仅部分数据线(D<sub>1</sub>-D<sub>7</sub>)和仅部分栅极线(G<sub>j-1</sub>-G<sub>j+2</sub>),数据驱动器 500 执行列反转,如数据线 D<sub>1</sub>-D<sub>7</sub>的极性所示。在这种情况下,列反转可包括重复一次相同的极性(未示出),以及交替正极性和负极性。例如,列反转包括数据电压的两种极性交替地重复的情况,如“+, -, +, -, +, -, ...”,即, N×1 反转,以及重复一次相同的极性然后反转该极性,即 N×2 反转(未示出)。另外,以下将仅对左端的数据线施加单独的电压并执行 1+N×2 反转驱动的情况简称为 N×2 反转。此外,尽管像素 PX 的开关元件 Q 连接到数据线 D<sub>1</sub>-D<sub>7</sub>和栅极线 G<sub>j-1</sub>-G<sub>j+2</sub>,但是将解释像素 PX 连接到两种信号线 D<sub>1</sub>-D<sub>7</sub>和 G<sub>j-1</sub>-G<sub>j+2</sub>的情况。

[0062] 如图 3 所示,一行中的各个像素 PX 连接到位于其左边或右边的数据线 D<sub>1</sub>-D<sub>7</sub>,一列中的像素交替地连接到位于其左边或右边的数据线 D<sub>1</sub>-D<sub>7</sub>。因此,在像素 PX 中显示的数据电压的极性(以下称作像素的极性)交替地显示为正(+)极性和负(-)极性,这样导致执行点反转。因此,可以防止当一列中像素 PX 的极性相互相同时产生的带缺陷。

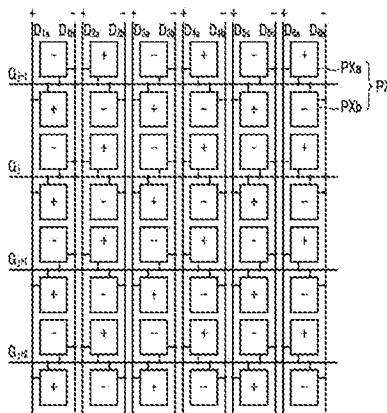

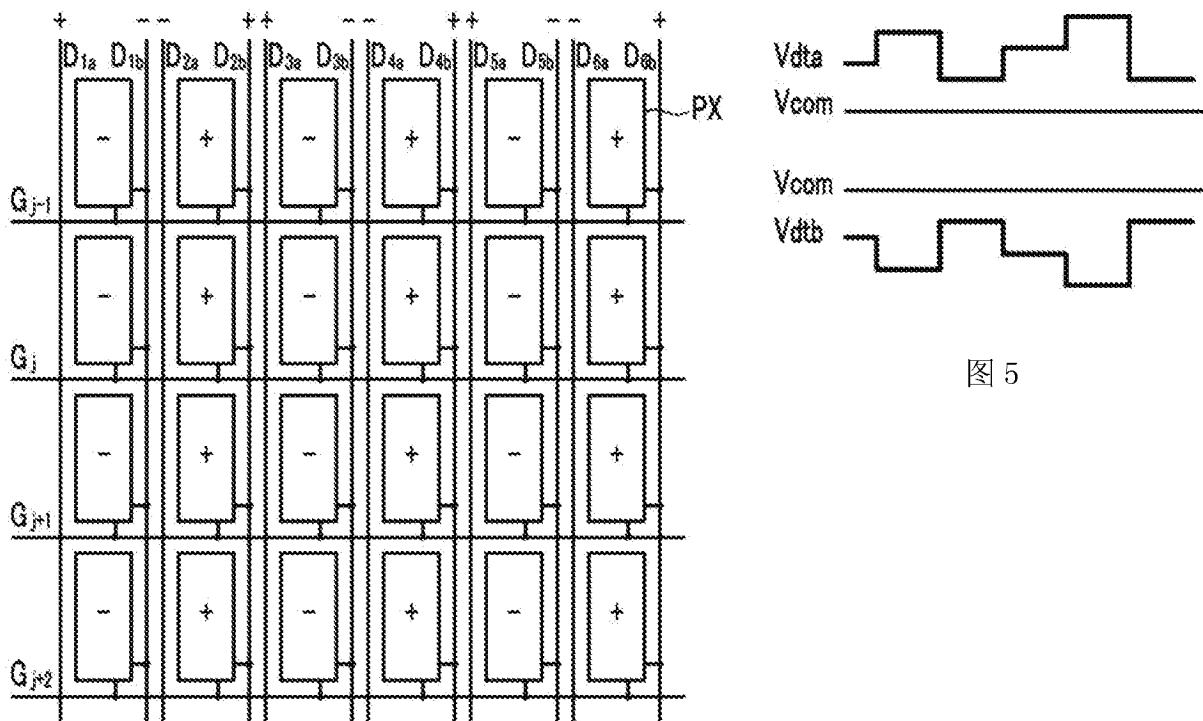

[0063] 图 4 是示出根据本发明示例性实施例的液晶显示器的像素布置的示例的视图。

[0064] 参照图 4,与图 3 所示的不同,成对的数据线 D<sub>1a</sub>和 D<sub>1b</sub>、D<sub>2a</sub>和 D<sub>2b</sub>、D<sub>3a</sub>和 D<sub>3b</sub>、D<sub>4a</sub>和 D<sub>4b</sub>、D<sub>5a</sub>和 D<sub>5b</sub>、D<sub>6a</sub>和 D<sub>6b</sub>分别设置在各个像素 PX 的左边和右边,像素 PX 分别连接到位于其右边的数据线 D<sub>1b</sub>、D<sub>2b</sub>、D<sub>3b</sub>、D<sub>4b</sub>、D<sub>5b</sub>、D<sub>6b</sub>。

[0065] 因此,一行中的像素 PX 的极性交替地改变,一列中的像素 PX 的极性均相同。成对的数据线 D<sub>1a</sub>和 D<sub>1b</sub>、D<sub>2a</sub>和 D<sub>2b</sub>、D<sub>3a</sub>和 D<sub>3b</sub>、D<sub>4a</sub>和 D<sub>4b</sub>、D<sub>5a</sub>和 D<sub>5b</sub>、D<sub>6a</sub>和 D<sub>6b</sub>中没有与像素 PX 连接的数据线 D<sub>1a</sub>、D<sub>2a</sub>、D<sub>3a</sub>、D<sub>4a</sub>、D<sub>5a</sub>、D<sub>6a</sub>的极性与连接到像素 PX 的数据线 D<sub>1b</sub>、D<sub>2b</sub>、D<sub>3b</sub>、D<sub>4b</sub>、D<sub>5b</sub>、D<sub>6b</sub>的极性相反。

[0066] 例如,在包括在第一列中的一对数据线 D<sub>1a</sub>和 D<sub>1b</sub>中,对右边的数据线 D<sub>1b</sub>施加负极性的数据电压 Vdtb,对左边的数据线 D<sub>1a</sub>施加正极性的数据电压 Vdtb。在图 5 中相对于共电压 Vcom 示出了这些数据电压。即,与施加到右边的数据线 D<sub>1b</sub>的数据电压的幅值相同但具有与施加到右边的数据线 D<sub>1b</sub>的数据电压的极性相反的极性的数据电压被施加到左边的数据线 D<sub>1a</sub>。这样导致在各个像素 PX 中寄生电容器两端的电压相互抵消,从而不出现连接缺陷。

[0067] 图 6A 和图 6B 是示出图 4 中示出的像素布置的示例性变化的视图。

[0068] 在图 6A 所示的像素布置中,同行的像素 PX 分别连接到相同的数据线 D<sub>1b</sub>、D<sub>2b</sub>、D<sub>3b</sub>、

D<sub>4b</sub>、D<sub>5b</sub>、D<sub>6b</sub>或D<sub>1a</sub>、D<sub>2a</sub>、D<sub>3a</sub>、D<sub>4a</sub>、D<sub>5a</sub>、D<sub>6a</sub>，相同列的像素PX每行分别交替地连接到成对的数据线D<sub>1a</sub>和D<sub>1b</sub>、D<sub>2a</sub>和D<sub>2b</sub>、D<sub>3a</sub>和D<sub>3b</sub>、D<sub>4a</sub>和D<sub>4b</sub>、D<sub>5a</sub>和D<sub>5b</sub>、D<sub>6a</sub>和D<sub>6b</sub>。在图6B所示的像素布置中，在第奇数列中的像素布置与图6A中示出的像素布置相同，在第偶数列中的像素布置和第奇数列中的像素布置相对于位于它们之间的数据线形成镜像对称。例如，第二列的像素布置和第一列的像素布置相对于数据线D<sub>1b</sub>和D<sub>2a</sub>形成镜像对称。

[0069] 由于施加到一列的像素PX的数据电压的极性相同，所以在图4所示的像素布置中可能会出现带缺陷。然而，图6A和图6B所示的像素布置不仅可以防止连接缺陷，而且可以防止带缺陷。

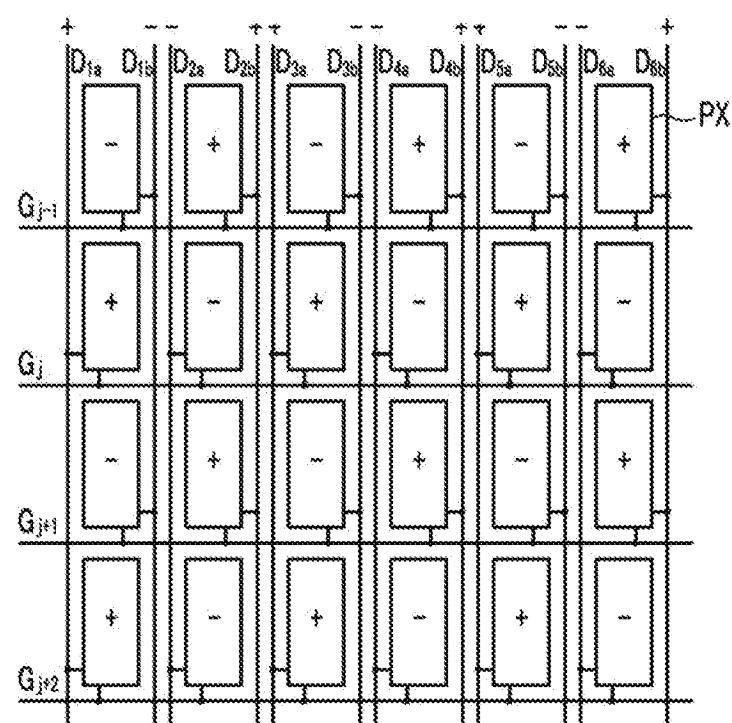

[0070] 图7是示出根据本发明示例性实施例的液晶显示器的像素布置的视图，图8A至图8D是示出图7所示的像素布置的示例性变化的视图。

[0071] 图7示出了通过将图4、图6A和图6B所示的像素结构中的各个像素PX相对于栅极线G<sub>j+1</sub>至G<sub>j+2</sub>划分成两个子像素PXa和PXb而获得的像素结构。这种结构用于提高侧面可视性，并主要用于垂直取向(VA)模式的液晶显示器中。

[0072] 组成一个像素PX的两个子像素PXa和PXb分别连接到不同的数据线D<sub>1a</sub>和D<sub>1b</sub>、D<sub>2a</sub>和D<sub>2b</sub>、D<sub>3a</sub>和D<sub>3b</sub>、D<sub>4a</sub>和D<sub>4b</sub>、D<sub>5a</sub>和D<sub>5b</sub>或D<sub>6a</sub>和D<sub>6b</sub>，并且在行方向和列方向上重复这种结构，从而形成如图中所示的像素PX的极性。

[0073] 由于在其间设置有像素PX的成对的数据线D<sub>1a</sub>和D<sub>1b</sub>、D<sub>2a</sub>和D<sub>2b</sub>、D<sub>3a</sub>和D<sub>3b</sub>、D<sub>4a</sub>和D<sub>4b</sub>、D<sub>5a</sub>和D<sub>5b</sub>、D<sub>6a</sub>和D<sub>6b</sub>的数据线的极性彼此相反，所以不出现连接缺陷。此外，由于在一列中像素PX的极性交替地重复，所以不出现带缺陷。

[0074] 图8A所示的像素布置与图7中所示的像素布置相同。然而，他们的不同之处在于施加到数据电压的极性，从而即使是相同的结构，像素PX的极性也会变得不同。即，尽管在图7所示的像素布置的行方向和列方向上，像素PX的极性示出了正极性和负极性，但是在图8A所示的像素布置中像素PX的极性在行方向上相同。然而，即使在这种情况下也可以防止带缺陷或连接缺陷。

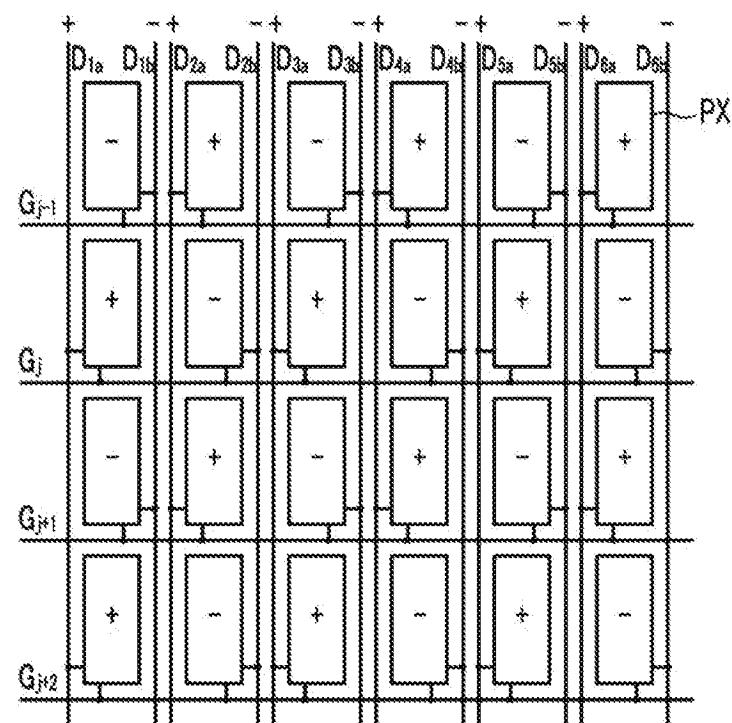

[0075] 在图8B所示的像素布置中，组成一个像素PX的两个子像素PXa和PXb分别连接到不同的数据线D<sub>1a</sub>和D<sub>1b</sub>、D<sub>2a</sub>和D<sub>2b</sub>、D<sub>3a</sub>和D<sub>3b</sub>、D<sub>4a</sub>和D<sub>4b</sub>、D<sub>5a</sub>和D<sub>5b</sub>、或D<sub>6a</sub>和D<sub>6b</sub>。然而，在列方向上两个相邻的像素的两个相邻的子像素连接到相同的数据线D<sub>1a</sub>或D<sub>1b</sub>、D<sub>2a</sub>或D<sub>2b</sub>、D<sub>3a</sub>或D<sub>3b</sub>、D<sub>4a</sub>或D<sub>4b</sub>、D<sub>5a</sub>或D<sub>5b</sub>、或者D<sub>6a</sub>或D<sub>6b</sub>。例如，第一列的第(j-1)行的下面的子像素PXb和第一列的相邻的第j行的上面的子像素PXa连接到相同的数据线D<sub>1a</sub>，第j行的下面的子像素PXb和相邻的第(j+1)行的上面的子像素PXa连接到相同的数据线D<sub>1b</sub>。

[0076] 在图8C所示的像素布置中，第奇数列的像素布置与图8A所示的像素布置相同，第偶数列的像素布置和第奇数列的像素布置相对于位于它们之间的数据线形成镜像对称。例如，第二列的像素布置和第一列的像素布置相对于数据线D<sub>1b</sub>和D<sub>2a</sub>形成镜像对称。

[0077] 在图8D所示的像素布置中，第奇数列的像素布置与图8B所示的像素布置相同。即，组成一个像素PX的两个子像素PXa和PXb分别连接到不同的数据线D<sub>1a</sub>和D<sub>1b</sub>、D<sub>2a</sub>和D<sub>2b</sub>、D<sub>3a</sub>和D<sub>3b</sub>、D<sub>4a</sub>和D<sub>4b</sub>、D<sub>5a</sub>和D<sub>5b</sub>、或者D<sub>6a</sub>和D<sub>6b</sub>，并在列方向重复这种结构。第偶数列的像素布置和第奇数列的像素布置相对于位于它们之间的数据线形成镜像对称，就像图8C所示的像素布置一样。

[0078] 这样，具有不同极性的相同幅度的数据电压被施加到各个成对的数据线D<sub>1a</sub>和D<sub>1b</sub>、

D<sub>2a</sub>和D<sub>2b</sub>、D<sub>3a</sub>和D<sub>3b</sub>、D<sub>4a</sub>和D<sub>4b</sub>、D<sub>5a</sub>和D<sub>5b</sub>、D<sub>6a</sub>和D<sub>6b</sub>的数据线，并且交替地重复在列方向上的像素的极性，从而可以防止连接缺陷和带缺陷。

[0079] 以这种方式，在防止连接缺陷和带缺陷的同时，可以执行高速驱动。

[0080] 尽管已经结合目前被认为是可行的示例性实施例描述了本发明，但是应该理解，本发明并不限于公开的实施例，相反，意在覆盖包括在权利要求的精神和范围内的各种修改和等价布置。

图 1

图 2

图 3

图 5

图 4

图 6A

图 6B

图 7

图 8A

图 8B

图 8C

图 8D

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置                                           |         |            |

| 公开(公告)号        | <a href="#">CN102914924B</a>                   | 公开(公告)日 | 2016-01-20 |

| 申请号            | CN201210390814.1                               | 申请日     | 2006-12-05 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                       |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                       |         |            |

| 当前申请(专利权)人(译)  | 三星显示有限公司                                       |         |            |

| [标]发明人         | 白承洙<br>金东奎<br>李柏远                              |         |            |

| 发明人            | 白承洙<br>金东奎<br>李柏远                              |         |            |

| IPC分类号         | G02F1/1362 G02F1/1368 G02F1/133 G09G3/36       |         |            |

| CPC分类号         | G09G3/3614 G09G2300/08 G09G2310/0218           |         |            |

| 代理人(译)         | 刘灿强                                            |         |            |

| 审查员(译)         | 桑青                                             |         |            |

| 优先权            | 1020050118067 2005-12-06 KR                    |         |            |

| 其他公开文献         | <a href="#">CN102914924A</a>                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

## 摘要(译)

本发明公开了一种具有显示装置特定的像素布置的显示装置，以防止在高速驱动时的连接缺陷和带缺陷。所述显示装置包括：多个像素，以矩阵形状布置；开关元件，连接到每个像素；数据线和栅极线，连接到所述开关元件；数据驱动器，产生数据电压并将数据电压施加到数据线。成对的数据线设置在像素的两侧，具有不同极性的相同幅度的数据电压被施加到成对的数据线。以这种方式，可以防止高速驱动时的连接缺陷和带缺陷。