(12) 发明专利

(10) 授权公告号 CN 102237029 B

(45) 授权公告日 2013. 05. 29

(21) 申请号 201010158961. 7

(22) 申请日 2010. 04. 23

(73) 专利权人 北京京东方光电科技有限公司

地址 100176 北京市经济技术开发区西环中

路 8 号

(72) 发明人 韩承佑

(74) 专利代理机构 北京路浩知识产权代理有限

公司 11002

代理人 王莹

(51) Int. Cl.

G09G 3/20 (2006. 01)

G09G 3/36 (2006. 01)

(56) 对比文件

CN 1941063 A, 2007. 04. 04, 全文 .

CN 1326178 A, 2001. 12. 12, 全文 .

US 2009251443 A1, 2009. 10. 08, 全文 .

JP 2010086640 A, 2010. 04. 15, 全文 .

CN 101562048 A, 2009. 10. 21, 全文 .

审查员 孟祥龙

权利要求书2页 说明书5页 附图2页

(54) 发明名称

移位寄存器、液晶显示器栅极驱动装置和数

据线驱动装置

(57) 摘要

本发明公开了一种移位寄存器、液晶显示器

栅极驱动装置和数据线驱动装置,是增加了降低

驱动薄膜晶体管的数量以及每隔一帧轮流施加时

钟信号的方式,降低降低驱动薄膜晶体管的占空

比,有效防止降低驱动薄膜晶体管的偏执作用,从

而保证移位寄存器单元的可靠性。

1. 一种移位寄存器，包括至少两个移位寄存器单元，其特征在于，其中一个移位寄存器单元包括：

升高信号薄膜晶体管，其接收第一时钟信号，在导通状态下向输出端输出高电压信号；

升高驱动第一薄膜晶体管，其接收帧起始信号或者另一个移位寄存器单元的输出信号导通升高信号薄膜晶体管；

升高驱动第二薄膜晶体管，其接收复位信号或者另一个移位寄存器单元的输出信号导通升高信号薄膜晶体管；

降低信号第一薄膜晶体管，其接收复位信号或者另一个移位寄存器单元的输出信号，在导通状态下向输出端输出低电压信号；

降低驱动第一薄膜晶体管，其接收第二时钟信号导通降低信号第二薄膜晶体管和降低信号第三薄膜晶体管；

降低驱动第二薄膜晶体管，其接收第三时钟信号导通降低信号第四薄膜晶体管和降低信号第五薄膜晶体管；

降低信号第二薄膜晶体管，其接收降低驱动第一薄膜晶体管的输出信号，在导通状态下降低输出端的输出信号；

降低信号第三薄膜晶体管，其接收降低驱动第一薄膜晶体管的输出信号，在导通状态下降低输出端的输出信号；

关闭驱动第一薄膜晶体管，其接收升高驱动第一薄膜晶体管的输出信号，在导通状态下截止降低信号第二薄膜晶体管和降低信号第三薄膜晶体管；

降低信号第四薄膜晶体管，其接收降低驱动第二薄膜晶体管的输出信号，在导通状态下降低输出端的输出信号；

降低信号第五薄膜晶体管，其接收降低驱动第二薄膜晶体管的输出信号，在导通状态下降低输出端的输出信号；

关闭驱动第二薄膜晶体管，在接收升高驱动第一薄膜晶体管的输出信号，在导通状态下截止降低信号第四薄膜晶体管和降低信号第五薄膜晶体管，

并且与所述移位寄存器单元相邻的另一个移位寄存器单元的升高信号薄膜晶体管、降低驱动第一薄膜晶体管、降低驱动第二薄膜晶体管分别接收第四时钟信号、第五时钟信号、第六时钟信号。

2. 根据权利要求 1 所述的移位寄存器，其特征在于，所述移位寄存器单元还包括辅助第一薄膜晶体管和辅助第二薄膜晶体管，分别接收升高驱动第一薄膜晶体管的输出信号，在导通状态下释放降低驱动第一薄膜晶体管和降低驱动第二薄膜晶体管的电荷。

3. 根据权利要求 1 所述的移位寄存器，其特征在于，所述移位寄存器单元还包括辅助第三薄膜晶体管、辅助第四薄膜晶体管和辅助第五薄膜晶体管，分别接收第一时钟信号、第二时钟信号和第三时钟信号，在导通状态下减少升高信号薄膜晶体管、降低驱动第一薄膜晶体管和降低驱动第二薄膜晶体管的偏执作用。

4. 根据权利要求 1 所述的移位寄存器，其特征在于，所述移位寄存器单元还包括一电容，其两端分别与所述升高驱动第一薄膜晶体管的漏极和输出端连接。

5. 根据权利要求 1 所述的移位寄存器，其特征在于，所述移位寄存器单元接收的第二

时钟信号、第三时钟信号是隔一帧轮流输出时钟信号。

6. 根据权利要求 1 所述的移位寄存器，其特征在于，与所述移位寄存器单元相邻的另一个移位寄存器单元接收的第五时钟信号、第六时钟信号是隔一帧轮流输出的时钟信号。

7. 包括一种根据权利要求 1-4 任一权利要求所述的移位寄存器的液晶显示器栅极驱动装置。

8. 包括一种根据权利要求 1-4 任一权利要求所述的移位寄存器的液晶显示器数据线驱动装置。

## 移位寄存器、液晶显示器栅极驱动装置和数据线驱动装置

### 技术领域

[0001] 本发明涉及液晶显示领域,尤其涉及一种移位寄存器、液晶显示器栅极驱动装置和数据线驱动装置。

### 背景技术

[0002] 现有技术中的移位寄存器单元,包括用于输出驱动信号的信号输出端。驱动信号为高电平时,移位寄存器单元控制一行薄膜晶体管导通;驱动信号为低电平时,移位寄存器单元控制一行薄膜晶体管截止。

[0003] 液晶显示器通常采用逐行扫描的方式,当扫描到某一行或某一列时,相应的移位寄存器单元输出高电平的驱动信号,其余的移位寄存器输出低电平的驱动信号,可见,对于一个移位寄存器单元来说,大部分时间驱动信号为低电平。

[0004] 在驱动信号为低电平期间,驱动信号很容易受到输入的时钟信号的干扰而产生噪声。为了抑制噪声,移位寄存器单元通常包括用于在驱动信号为低电平期间将驱动信号拉低的降低信号薄膜晶体管。与降低信号薄膜晶体管的栅极连接的结点控制降低信号薄膜晶体管导通,从而能够拉低信号输出端的栅极驱动信号的电平。

[0005] 现有技术中的移位寄存器单元存在的问题是:通常与降低信号薄膜晶体管的栅极连接的节点大部分时间保持高电平,这样大部分时间降低信号薄膜晶体管保持导通,从而使得降低信号薄膜晶体管的阈值电压产生较大偏移。如果降低信号薄膜晶体管的阈值电压不断升高,会导致降低信号薄膜晶体管无法导通,从而无法起到抑制噪声的作用,影响整个移位寄存器的性能。

### 发明内容

[0006] 本发明的目的在于针对现有技术存在的问题,提供一种移位寄存器、液晶显示器栅极驱动装置和数据线驱动装置,能够使得移位寄存器中用于抑制噪声的薄膜晶体管保持导通,保证移位寄存器的可靠性。

[0007] 为了实现上述目的,本发明提供一种移位寄存器,包括:至少两个移位寄存器单元,其中一个移位寄存器单元包括:

[0008] 升高信号薄膜晶体管,其接收第一时钟信号,在导通状态下向输出端输出高电压信号;

[0009] 升高驱动第一薄膜晶体管,其接收帧起始信号或者另一个移位寄存器单元的输出信号导通升高信号薄膜晶体管;

[0010] 升高驱动第二薄膜晶体管,其接收复位信号或者另一个移位寄存器单元的输出信号导通升高信号薄膜晶体管;

[0011] 降低信号第一薄膜晶体管,其接收复位信号或者另一个移位寄存器单元的输出信号,在导通状态下向输出端输出低电压信号;

[0012] 降低驱动第一薄膜晶体管,其接收第二时钟信号导通降低信号第二薄膜晶体管和

降低信号第三薄膜晶体管；

[0013] 降低驱动第二薄膜晶体管，其接收第三时钟信号导通降低信号第四薄膜晶体管和降低信号第五薄膜晶体管；

[0014] 降低信号第二薄膜晶体管，其接收降低驱动第一薄膜晶体管的输出信号，在导通状态下降低输出端的输出信号；

[0015] 降低信号第三薄膜晶体管，其接收降低驱动第一薄膜晶体管的输出信号，在导通状态下降低输出端的输出信号；

[0016] 关闭驱动第一薄膜晶体管，其接收升高驱动第一薄膜晶体管的输出信号，在导通状态下截止降低信号第二薄膜晶体管和降低信号第三薄膜晶体管；

[0017] 降低信号第四薄膜晶体管，其接收降低驱动第二薄膜晶体管的输出信号，在导通状态下降低输出端的输出信号；

[0018] 降低信号第五薄膜晶体管，其接收降低驱动第二薄膜晶体管的输出信号，在导通状态下降低输出端的输出信号；

[0019] 关闭驱动第二薄膜晶体管，在接收升高驱动第一薄膜晶体管的输出信号，在导通状态下截止降低信号第四薄膜晶体管和降低信号第五薄膜晶体管，

[0020] 并且与上述移位寄存器单元相邻的另一个移位寄存器单元的升高信号薄膜晶体管、降低驱动第一薄膜晶体管、降低驱动第二薄膜晶体管分别接收第四时钟信号、第五时钟信号、第六时钟信号。

[0021] 本发明提供的移位寄存器还包括辅助第一薄膜晶体管和辅助第二薄膜晶体管，分别接收升高驱动第一薄膜晶体管的输出信号，在导通状态下释放降低驱动第一薄膜晶体管和降低驱动第二薄膜晶体管的电荷。

[0022] 本发明提供的移位寄存器还包括辅助第三薄膜晶体管、辅助第四薄膜晶体管和辅助第五薄膜晶体管，分别接收第一时钟信号、第二时钟信号和第三时钟信号，在导通状态下减少升高信号薄膜晶体管、降低驱动第一薄膜晶体管和降低驱动第二薄膜晶体管的偏执作用。

[0023] 本发明提供的移位寄存器还包括一电容，其两端分别与所述升高驱动第一薄膜晶体管的漏极和输出端连接。

[0024] 本发明提供的移位寄存器，上述移位寄存器单元接收的第二时钟信号、第三时钟信号是隔一帧轮流输出时钟信号。

[0025] 本发明提供的移位寄存器，与上述移位寄存器单元相邻的另一个移位寄存器单元接收的第五时钟信号、第六时钟信号是隔一帧轮流输出的时钟信号。

[0026] 本发明还提供一种包括上述的移位寄存器的液晶显示器栅极驱动装置。

[0027] 本发明还提供一种包括上述的移位寄存器的液晶显示器数据线驱动装置。

[0028] 下面通过具体实施例并结合附图对本发明做进一步的详细描述。

## 附图说明

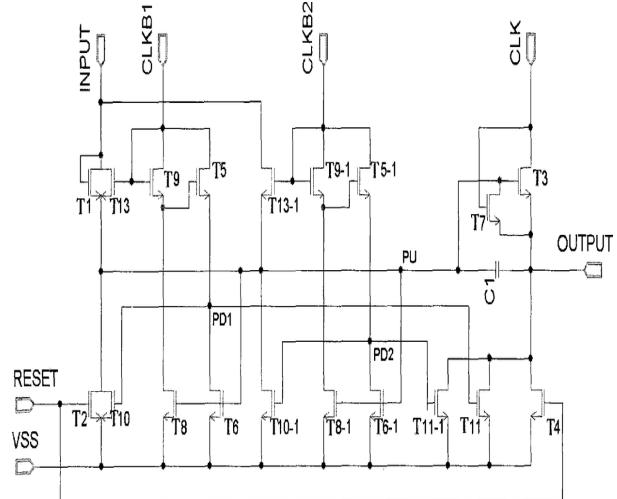

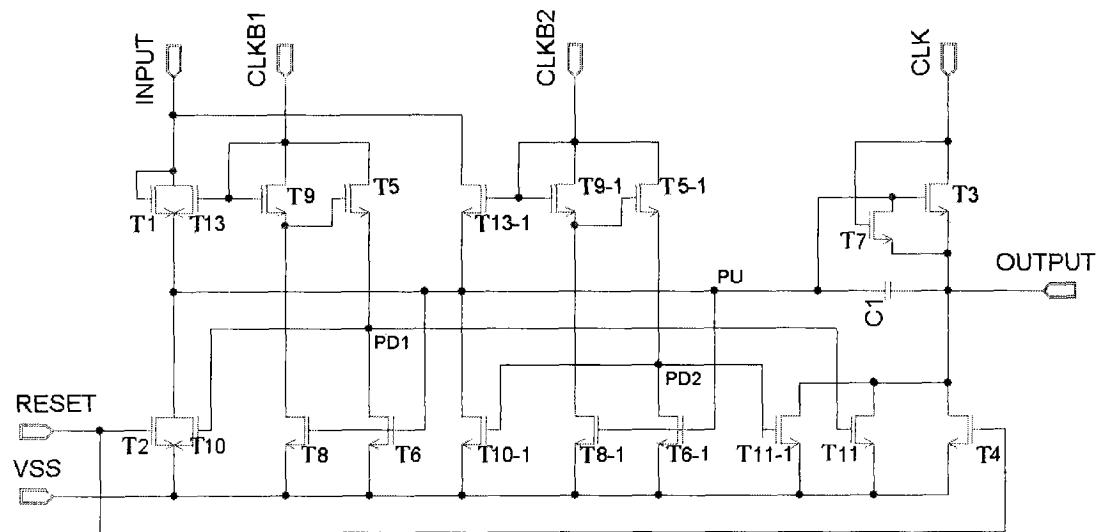

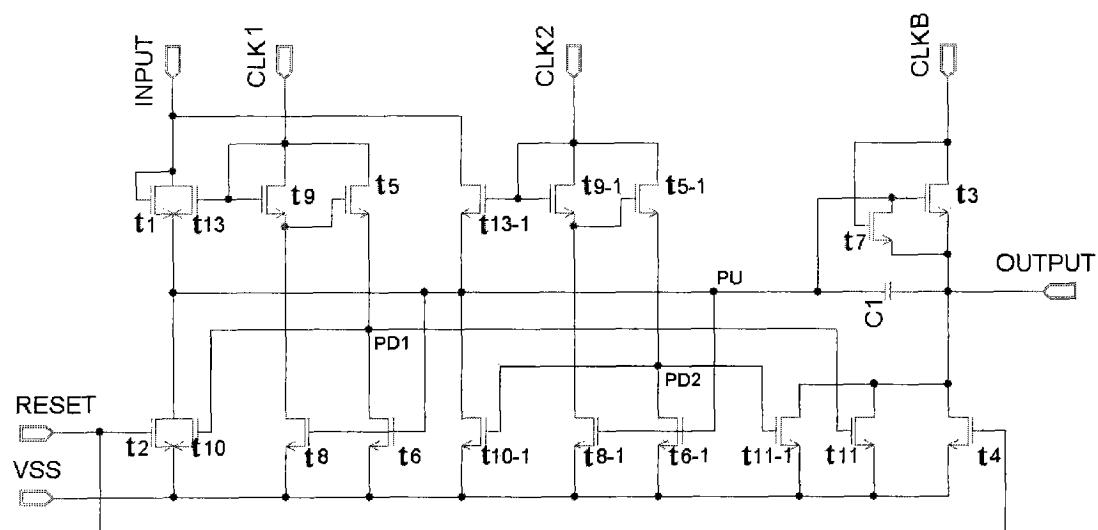

[0029] 图 1a 所示为本发明移位寄存器单元结构示意图；

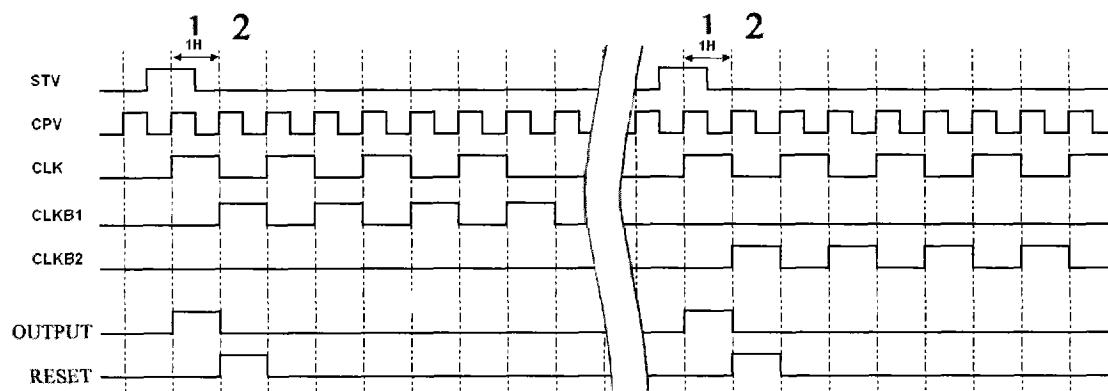

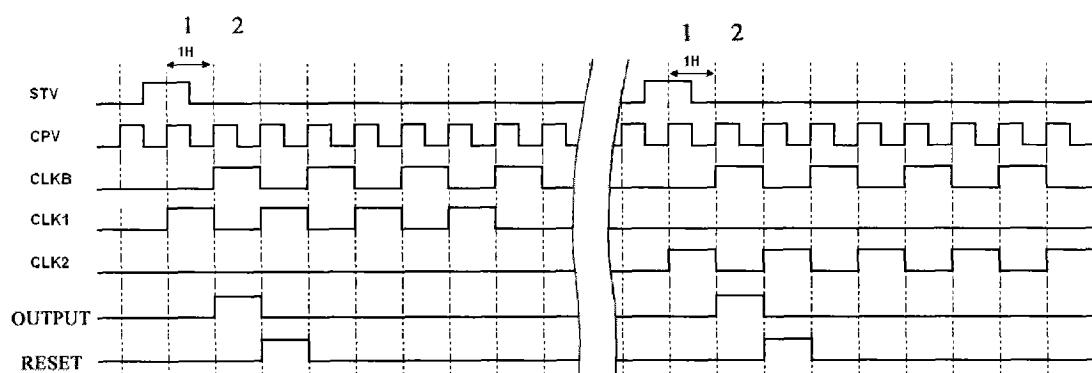

[0030] 图 1b 所示为图 1 所示的移位寄存器单元的输入输出时序图；

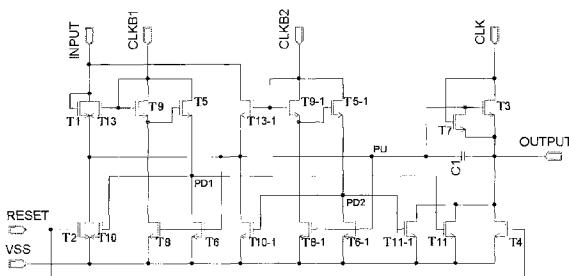

[0031] 图 2a 所示为本发明另一移位寄存器单元结构示意图；

[0032] 图 2b 所示为图 3 所示的另一移位寄存器单元的输入输出时序图。

### 具体实施方式

[0033] 本发明公开了一种移位寄存器，包括至少两个移位寄存器单元，其中一个移位寄存器单元包括：

[0034] 如图 1a 所示，本发明移位寄存器单元包括升高信号薄膜晶体管 T3，其接收第一时钟信号 CLK，在导通状态下向输出端输出高电压信号；升高驱动第一薄膜晶体管 T1，其接收帧起始信号或者上一个移位寄存器单元的输出信号导通升高信号薄膜晶体管 T3；升高驱动第二薄膜晶体管 T2，其接收下一个移位寄存器单元的输出信号导通升高信号薄膜晶体管 T3；降低信号第一薄膜晶体管 T4，其接收下一个移位寄存器单元的输出信号，在导通状态下向输出端输出低电压信号；降低驱动第一薄膜晶体管 T5，其接收第二时钟信号 CLKB1 导通降低信号第二薄膜晶体管 T10 和降低信号第三薄膜晶体管 T11；降低驱动第二薄膜晶体管 T5-1，其接收第三时钟信号 CLKB2 导通降低信号第四薄膜晶体管 T10-1 和降低信号第五薄膜晶体管 T11-1；降低信号第二薄膜晶体管 T10，其接收降低驱动第一薄膜晶体管 T5 的输出信号，在导通状态下降低输出端的输出信号；降低信号第三薄膜晶体管 T11，其接收降低驱动第一薄膜晶体管 T5 的输出信号，在导通状态下降低输出端的输出信号；降低信号第四薄膜晶体管 T10-1，其接收降低驱动第二薄膜晶体管 T5-1 的输出信号，在导通状态下降低输出端得输出信号；关闭驱动第一薄膜晶体管 T6，其接收升高驱动第一薄膜晶体管 T1 的输出信号，在导通状态下截止降低信号第二薄膜晶体管 T10 和降低信号第三薄膜晶体管 T11；关闭驱动第二薄膜晶体管 T6-1，在接收升高驱动第一薄膜晶体管 T1 的输出信号，在导通状态下截止降低信号第四薄膜晶体管 T10-1 和降低信号第五薄膜晶体管 T11-1。

[0035] 如图 2a 所示，本发明另一移位寄存器单元的升高信号薄膜晶体管 t3、降低驱动第一薄膜晶体管 t5、降低驱动第二薄膜晶体管 t5-1 分别接收第四时钟信号 CLKB、第五时钟信号 CLK1、第六时钟信号 CLK2。

[0036] 本发明提供的移位寄存器单元接收的第二时钟信号、第三时钟信号是隔一帧轮流输出时钟信号。

[0037] 本发明提供的移位寄存器单元接收的第五时钟信号、第六时钟信号是隔一帧轮流输出时钟信号。

[0038] 需要说明的是，对于液晶显示领域的薄膜晶体管来说，漏极和源极没有明确的区别，所以本发明中所提到的薄膜晶体管的源极可以为薄膜晶体管的漏极，薄膜晶体管的漏极也可以为薄膜晶体管的源极。

[0039] 下面结合图 1a 和图 1b，来说明本发明移位寄存器单元的工作原理。

[0040] 选择图 1b 所示时序图的第一帧一部分并选择其中前 2 个阶段，在第一阶段，输入信号 (INPUT) 信号为帧起始信号 (STV) 是高电平，升高驱动第一薄膜晶体管 T1 导通，PU 节点电压升高；关闭驱动第一薄膜晶体管 T6、关闭驱动第二薄膜晶体管 T6-1 导通，使 PD1、PD2 节点电压为低电平，因此降低信号第二薄膜晶体管 T10、降低信号第三薄膜晶体管 T11 截止；辅助薄膜晶体管 T8、T8-1 导通，释放降低驱动第一薄膜晶体管 T5、降低驱动第二薄膜晶体管 T5-1 的电荷；升高信号薄膜晶体管 T3 导通，此时第一时钟信号 CLK 为高电平，因此信号输出端 (OUT) 输出信号 (OUTPUT) 为高电平，复位信号输入端 (RESETIN) 输入信号 (RESET)

为低电平,升高驱动第二薄膜晶体管 T2、降低信号第一薄膜晶体管 T4 截止。

[0041] 在第二阶段,输入信号 (INPUT) 信号为低电平,升高驱动第一薄膜晶体管 T1 截止;复位信号 (RESET) 为高电平,升高驱动第二薄膜晶体管 T2、降低信号第一薄膜晶体管 T4 导通,PU 节点释放电荷,变为低电平,信号输出端(OUT)输出信号(OUTPUT)在降低信号第一薄膜晶体管 T4 的拉低作用下变为低电平;第二时钟信号(CLKB1)为高电平,降低驱动第一薄膜晶体管 T5 导通,PD1 节点升高,使降低信号第二薄膜晶体管 T10、降低信号第三薄膜晶体管 T11 导通,信号输出端(OUT)输出信号(OUTPUT)在降低信号第二薄膜晶体管 T10、降低信号第三薄膜晶体管 T11 的拉低作用下变为低电平,因此降低驱动薄膜晶体管的占空比比现有降低驱动薄膜晶体管的占空比降低,能有效防止降低驱动薄膜晶体管的偏执作用。即使得降低信号第一薄膜晶体管 T4、降低信号第二薄膜晶体管 T10、降低信号第三薄膜晶体管 T11 能够起到抑制噪声的作用,保证移位寄存器单元的可靠性。

[0042] 选择图 1b 所示时序图的第二帧一部分并选择其中前 2 个阶段,在第一阶段,输入信号 (INPUT) 信号为帧起始信号 (STV) 是高电平,升高驱动第一薄膜晶体管 T1 导通,PU 节点电压升高;关闭驱动第一薄膜晶体管 T6、关闭驱动第二薄膜晶体管 T6-1 导通,使 PD1、PD2 节点电压为低电平,因此降低信号第二薄膜晶体管 T10、降低信号第三薄膜晶体管 T11 截止;辅助薄膜晶体管 T8、T8-1 导通,释放降低驱动第一薄膜晶体管 T5、降低驱动第二薄膜晶体管 T5-1 的电荷;升高信号薄膜晶体管 T3 导通,此时第一时钟信号 CLK 为高电平,因此信号输出端(OUT)输出信号(OUTPUT)为高电平,复位信号输入端(RESETIN)输入信号(RESET)为低电平,升高驱动第二薄膜晶体管 T2、降低信号第一薄膜晶体管 T4 截止。

[0043] 在第二阶段,输入信号 (INPUT) 信号为低电平,升高驱动第一薄膜晶体管 T1 截止;复位信号 (RESET) 为高电平,升高驱动第二薄膜晶体管 T2、降低信号第一薄膜晶体管 T4 导通,PU 节点释放电荷,变为低电平,信号输出端(OUT)输出信号(OUTPUT)在降低信号第一薄膜晶体管 T4 的拉低作用下变为低电平;第三时钟信号(CLKB1)为高电平,降低驱动第二薄膜晶体管 T5-1 导通,PD2 节点升高,使降低信号第四薄膜晶体管 T10-1、降低信号第五薄膜晶体管 T11-1 导通,信号输出端(OUT)输出信号(OUTPUT)在降低信号第四薄膜晶体管 T10-1、降低信号第五薄膜晶体管 T11-1 的拉低作用下变为低电平,因此降低驱动薄膜晶体管的占空比比现有降低驱动薄膜晶体管的占空比降低,能有效防止降低驱动薄膜晶体管的偏执作用。即使得降低信号第一薄膜晶体管 T4、降低信号第四薄膜晶体管 T10-1、降低信号第五薄膜晶体管 T11-1 能够起到抑制噪声的作用,保证移位寄存器单元的可靠性。

[0044] 在上述移位寄存器的工作过程中辅助第一薄膜晶体管 T8 和辅助第二薄膜晶体管 T8-1,分别接收升高驱动第一薄膜晶体管 T1 的输出信号,在导通状态下释放降低驱动第一薄膜晶体管 T5 和降低驱动第二薄膜晶体管 T5-1 的电荷;辅助第三薄膜晶体管 T7、辅助第四薄膜晶体管 T9 和辅助第五薄膜晶体管 T9-1,分别接收第一时钟信号 CLK、第二时钟信号 CLKB1 和第三时钟信号 CLKB2,在导通状态下减少升高信号薄膜晶体管 T3、降低驱动第一薄膜晶体管 T5 和降低驱动第二薄膜晶体管 T5-1 的偏执作用。

[0045] 在上述移位寄存器单元中的电容 C1 的两端分别与升高信号薄膜晶体管 T3 的栅极和信号输出端(OUT)连接,在移位寄存器单元工作时,PU 结点处的信号的电平,由于第一电容 C1 的耦合作用,可以升到较高的高电平。

[0046] 图 2a 所示为本发明另一移位寄存器单元结构示意图;

[0047] 图 2b 所示为图 3 所示的另一移位寄存器单元的输入输出时序图。

[0048] 如图 2a、2b 所示的另一移位寄存器的工作原理与上述移位寄存器的工作原理类似, 此处不再赘述。

[0049] 本发明还提供了一种包括上述移位寄存器的液晶显示器的栅驱动装置及数据线驱动装置(此部分未画出)。

[0050] 本发明实施例提供的移位寄存器是降低降低驱动薄膜晶体管的占空比, 有效防止降低驱动薄膜晶体管的偏执作用, 从而保证移位寄存器单元的可考性。

[0051] 最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

图 1a

图 1b

图 2a

图 2b

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 移位寄存器、液晶显示器栅极驱动装置和数据线驱动装置                      |         |            |

| 公开(公告)号        | <a href="#">CN102237029B</a>                   | 公开(公告)日 | 2013-05-29 |

| 申请号            | CN201010158961.7                               | 申请日     | 2010-04-23 |

| [标]申请(专利权)人(译) | 北京京东方光电科技有限公司                                  |         |            |

| 申请(专利权)人(译)    | 北京京东方光电科技有限公司                                  |         |            |

| 当前申请(专利权)人(译)  | 北京京东方光电科技有限公司                                  |         |            |

| [标]发明人         | 韩承佑                                            |         |            |

| 发明人            | 韩承佑                                            |         |            |

| IPC分类号         | G09G3/20 G09G3/36                              |         |            |

| CPC分类号         | G09G3/3674 G09G2310/0286 G11C19/28             |         |            |

| 代理人(译)         | 王莹                                             |         |            |

| 审查员(译)         | 孟祥龙                                            |         |            |

| 其他公开文献         | CN102237029A                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明公开了一种移位寄存器、液晶显示器栅极驱动装置和数据线驱动装置，是增加了降低驱动薄膜晶体管的数量以及每隔一帧轮流施加时钟信号的方式，降低降低驱动薄膜晶体管的占空比，有效防止降低驱动薄膜晶体管的偏执作用，从而保证移位寄存器单元的可靠性。