[12] 发明专利申请公开说明书

[51] Int. Cl.

G02F 1/136 (2006.01)

G02F 1/133 (2006.01)

[21] 申请号 200610066784.3

[43] 公开日 2006 年 10 月 18 日

[11] 公开号 CN 1847964A

[22] 申请日 2006.4.13

[21] 申请号 200610066784.3

[30] 优先权

[32] 2005.4.13 [33] KR [31] 10-2005-0030678

[71] 申请人 三星电子株式会社

地址 韩国京畿道

[72] 发明人 金东奎

[74] 专利代理机构 北京康信知识产权代理有限责任公司

代理人 李伟

权利要求书 5 页 说明书 35 页 附图 15 页

[54] 发明名称

液晶显示器

[57] 摘要

一种液晶显示器包括一个阵列的像素。每个像素分成第一子像素和第二子像素，向这两个子像素分别地施加(提供)不同的数据电压，从而增强侧面可视性。每个子像素包括与子像素的存储电极相重叠的子像素电极(连接至子像素的开关元件的漏电极)。向第一子像素施加第一预定电压，向第二子像素施加第二预定电压，从而使第一子像素电极可接收低于第二子像素电极的电压的电压。第一子像素面积可大于第二子像素电极。第一漏电极与第一子像素的存储电极之间的重叠面积可大于该漏电极与第二子像素的存储电极之间的重叠面积。从而使第一子像素的反冲电压基本上等于第二子像素的反冲电压。

1. 一种液晶显示器，包括：

多个像素，其排布成矩阵形式，每个像素包括第一和第二子像素，其中，每个子像素包括：

子像素电极；

存储电极；

开关的栅电极；

所述开关的源电极；以及

所述开关的漏电极，其连接至所述子像素电极，

其中，向所述第一子像素电极施加第一预定电压，向所述第二子像素电极施加第二预定电压。

2. 根据权利要求 1 所述的液晶显示器，其中，所述第一预定电压低于所述第二预定电压。

3. 根据权利要求 1 所述的液晶显示器，其中，所述第一和第二漏电极重叠所述第一和第二存储电极，并且所述第一漏电极与所述第一存储电极之间的重叠面积大于所述第二漏电极与所述第二存储电极之间的重叠面积。

4. 根据权利要求 1 所述的液晶显示器，还包括：第一和第二栅极线，用于分别发送栅极信号至所述第一和第二栅电极；以及数据线，用于分别发送数据电压至所述第一和第二源电极。

5. 根据权利要求 4 所述的液晶显示器，其中，施加给所述第一和第二栅极线的所述栅极信号的时刻互不相同。

6. 根据权利要求 1 所述的液晶显示器，还包括：栅极线，用于发送栅极信号至所述第一和第二栅电极；以及第一和第二数据线，用于发送数据电压至第一和第二源电极。

7. 根据权利要求 1 所述的液晶显示器，还包括：栅极线，用于发送栅极信号至所述第一和第二栅电极；以及数据线，用于发送数据电压至第一和第二源电极。

8. 根据权利要求 7 所述的液晶显示器，其中，所述第一和第二存储电极分别与所述第一和第二漏电极相重叠，并彼此物理分离和电分离。

9. 根据权利要求 1 所述的液晶显示器，其中，施加给所述第一和第二子像素电极的数据电压大小互不相同。

10. 根据权利要求 1 所述的液晶显示器，其中，所述第一开关是第一薄膜晶体管，第二开关是第二薄膜晶体管，其中，所述第一薄膜晶体管的通道宽度长度比大于所述第二薄膜晶体管的通道宽度长度比。

11. 根据权利要求 1 所述的液晶显示器，其中，所述第一子像素电极面积大于所述第二子像素电极。

12. 一种液晶显示器，包括：

- 多个像素，其排布成矩阵形式，其中，每个像素包括第一和第二子像素；

- 第一栅极线，连接至所述第一子像素；以及

- 数据线，其垂直于所述第一栅极线，并连接至所述第一子像素，

其中，所述第二子像素连接至所述第一栅极线和所述第一数据线中的至少一条。

13. 根据权利要求 12 所述的液晶显示器，其中，所述第一子像素的反冲电压基本上等于所述第二子像素的反冲电压；以及

其中，向所述第一子像素施加预定电压，并且所述第一子像素接收比所述第二子像素所接收的电压大的电压。

14. 根据权利要求 12 所述的液晶显示器，还包括连接至所述第二子像素的第二栅极线，其中，所述第二子像素连接至所述第一数据线。

15. 根据权利要求 14 所述的液晶显示器，其中，所述第一子像素包括：

第一开关元件，其连接至所述第一栅极线，并连接至所述第一数据线；

第一液晶电容器，其连接至所述第一开关元件，并连接至第一存储电容器；以及

其中，所述第二子像素包括：

第二开关元件，其连接至所述第二栅极线，并连接至所述第一数据线；

第二液晶电容器，其连接至所述第二开关元件，具有比所述第一液晶电容器的电容小的电容；以及

第二存储电容器，其连接至所述第二开关元件，具有比所述第一存储电容器的电容小的电容。

16. 根据权利要求 12 所述的液晶显示器，还包括连接至所述第二子像素的第二数据线，其中，所述第二子像素连接至所述第一栅极线。

17. 根据权利要求 16 所述的液晶显示器，其中，所述第一子像素包括：

第一开关元件，其连接至所述第一栅极线，并连接至所述第一数据线；

第一液晶电容器，其连接至所述第一开关元件；以及

第一存储电容器，其连接至所述第一开关元件；以及

所述第二子像素包括：

第二开关元件，其连接至所述第一栅极线，并连接至所述第二数据线；

第二液晶电容器，其连接至所述第二开关元件，具有比所述第一液晶电容器的电容小的电容；以及

第二存储电容器，其连接至所述第二开关元件，具有比所述第一存储电容器的电容小的电容。

18. 一种液晶显示器，包括：

一个阵列的像素，其排布成矩阵形式，其中，每个像素包括第一和第二子像素；

多条第一栅极线，所述多条第一栅极线中的一条连接至所述多个第一子像素中的一个；以及

多条第一数据线，其垂直于所述第一栅极线，所述多条数据线中的一条连接至所述多个第一子像素中的一个，

其中，每个所述第一子像素包括：

第一开关元件，其连接至所述第一栅极线，并连接至所述第一数据线；

第一液晶电容器，其连接至所述第一开关元件，并连接至第一存储电容器；以及

每个所述第二子像素包括：

第二开关元件，其连接至所述第一栅极线和所述第一数据线中的至少一条；

第二液晶电容器，其连接至所述第二开关元件，具有比所述第一液晶电容器的电容小的电容；以及

第二存储电容器，其连接至所述第二开关元件，具有比所述第一存储电容器的电容小的电容。

19. 根据权利要求 18 所述的液晶显示器，其中，向所述第一子像素施加预定电压，并且所述第一子像素接收比所述第二子像素所接收的电压大的电压。

20. 根据权利要求 18 所述的液晶显示器，还包括多条第二栅极线，所述多条第二栅极线中的一条连接至所述多个第二开关元件中的一个，其中，所述多个第二开关元件中的一个连接至所述多条第一数据线中的一条。

21. 根据权利要求 18 所述的液晶显示器，还包括多条第二数据线，所述多条第二数据线中的一条连接至所述多个第二开关元件中的一个，其中，所述多个第二开关元件中的一个连接至所述多条第一栅极线中的一条。

## 液晶显示器

本申请要求于 2005 年 4 月 13 日提交的韩国专利申请第 10-2005-0030678 号的优先权，其全部内容结合于此作为参考。

### 技术领域

本发明涉及一种液晶显示器。

### 背景技术

通常，液晶显示器（“LCD”）（一种最广泛应用的平板显示装置）包括两块上面安装有场致（field-generating）电极（例如像素电极和共电极）的基板，以及介于这些基板之间的液晶层。LCD 通过对场致电极施加电压以在液晶层中产生电场，然后排列液晶层的液晶分子，以控制（例如，从“背光”）入射它的光的偏振，从而显示期望的图像。

在垂直排列（“VA”）模式 LCD 中，液晶分子的方向排列成，当不施加电压时垂直于上和下面板（基板），具有高对比度和宽参考视角（reference viewing angle）。宽参考视角是指具有 1:10 对比度的视角，或者中间灰度亮度反转临界角（inter-gray luminance inversion limit angle）。

在 VA 模式 LCD 中，在场致电极处可形成切口（cutout）或突起（protrusion），以实现宽视角。由于液晶分子要倾斜的方向是由

切口或突起所确定，所以可使液晶分子的倾斜方向变化，从而拓宽参考视角。

然而，VA 模式 LCD 在其侧面处的可视性相比于其正面的可视性表现较差。例如，在具有切口的图样化垂直排列（patterned vertically aligned，缩写为 PVA）模式 LCD 中，其亮度随着到达其侧面而被高亮，严重情况下，高灰度之间的亮度差被消除，使得显示图像可能显示失真。

为了改善侧面可视性，人们提出了应该将由一个数据控制的像素（例如，一个彩色像素）分成两个子像素，这两个子像素彼此电容结合。将电压直接施加于这些子像素中的一个上，由于电容结合，导致另一个子像素上的电压降。这样，这两个子像素电压彼此不同，并具有不同的透光率。

然而，以这种方法，不能将这两个子像素的透射率直接且准确地控制至期望水平，尤其是，对于各种颜色，透光率不同。不能相对于各种颜色直接调节电压。此外，由于电容结合带来的额外导体，导致开口率（aperture ratio）恶化，而且由于电容结合感应的电压降，导致透光率下降。

## 发明内容

一种液晶显示器包括一个阵列的像素。每个像素分成第一子像素和第二子像素，将不同的数据电压分别地施加给这两个子像素，从而增强侧面可视性。每个子像素包括与子像素的存储电极相重叠的子像素电极（连接至子像素的开关元件的漏电极）。第一子像素电极面积可大于第二子像素电极。可向第一子像素施加第一预定电压，可向第二子像素施加第二预定电压，从而使第一子像素电极可接收低于第二子像素电极的电压的电压。第一漏电极与第一子像素

的存储电极之间的重叠面积可大于该漏电极与第二子像素的存储电极之间的重叠面积。从而使第一子像素的反冲电压基本上等于第二子像素的反冲电压。

本发明的实施例提供了一种液晶显示器，其具有增强的侧面可视性，以及合适的透光率和开口率。

根据本发明的一个方面，提供了一种液晶显示器，其包括多个（一个阵列的）像素，每个像素包括：第一和第二子像素。每个子像素包括开关（例如，具有漏电极、栅电极、和源电极的薄膜晶体管（TFT））、（ $lc$  电容器的）子像素电极、以及（存储电容器的）存储电极。漏电极重叠存储电极，向第二子像素电极施加预定电压，第一子像素电极接收低于第二子像素电极的电压的电压。第一和第二存储电极彼此电分离。第一漏电极与存储电极之间的重叠面积可大于第二漏电极与存储电极之间的重叠面积。从而使第一子像素的反冲电压基本上等于第二子像素的反冲电压。

施加于每个像素的第一和第二子像素电极的数据电压可以彼此（大小或时刻（timing））不同，它们可来自于一个图像信息信号。

在一些实施例中，第一和第二栅极线分别发送（不同的）栅极信号至第一和第二栅电极，然后数据线发送（相同的）数据电压至第一和第二源电极。

施加给第一和第二栅极线的栅极信号（电压）的定时可以彼此不同。

在另一些实施例中，栅极线发送（相同的）栅极线至第一和第二栅电极，同时第一和第二数据线分别发送（不同的）数据电压至第一和第二源电极。

在另一些实施例中，栅极线发送(相同的)栅极线至第一和第二栅电极，数据线发送(相同的)数据电压至第一和第二源电极。

第一子像素的第一薄膜晶体管(TFT)的通道(channel)宽度长度比可以不同于(例如大于)第二子像素的第二薄膜晶体管(TFT)的通道宽度长度比。

第一子像素电极可以面积大于第二子像素电极。

根据本发明的另一方面，提供了一种液晶显示器，其包括多个(一个阵列的)像素，每个像素包括：第一和第二子像素。多条第一栅极线连接至第一子像素。多条第一数据线越过(垂直于)第一栅极线，并连接至第一子像素。第二子像素连接至第一栅极线和第一数据线中的一条或都连接(例如，至少一条)。向第一子像素施加预定电压，第二子像素接收的电压高于第一子像素接收的电压。可使第一子像素的反冲电压基本上等于第二子像素的反冲电压。

在一些实施例中，多条栅极线可连接至第二子像素，同时第二子像素连接至第一数据线。从而，第一子像素可包括：第一开关元件，连接至第一栅极线和第一数据线；第一液晶电容器，连接至第一开关元件；以及第一存储电容器，连接至第一开关元件。第二子像素可包括：第二开关元件，连接至第二栅极线和第一数据线；第二液晶电容器，连接至第二开关元件，其具有的电容小于第一液晶电容器的电容；以及第二存储电容器，连接至第二开关元件，其具有的电容小于第一存储电容器的电容。

在另一些实施例中，多条第二数据线可连接至第二子像素，同时，第二子像素可连接至第一栅极线。从而，第一子像素可包括：第一开关元件，连接至第一栅极线和第一数据线；第一液晶电容器，连接至第一开关元件；以及第一存储电容器，连接至第一开关元件。

第二子像素可包括：第二开关元件，连接至第二栅极线和第一数据线；第二液晶电容器，连接至第二开关元件，其具有的电容小于第一液晶电容器的电容；以及第二存储电容器，连接至第二开关元件，其具有的电容小于第一存储电容器的电容。

根据本发明的另一方面，提供了一种液晶显示器，其包括矩阵形式的多个（一个阵列的）像素，每个像素包括：第一和第二子像素。多条第一栅极线连接至第一子像素。多条第一数据线越过（垂直于）第一栅极线，并连接至第一子像素。第一子像素包括：第一开关元件，连接至第一栅极线和第一数据线；第一液晶电容器，连接至第一开关元件；以及第一存储电容器，连接至第一开关元件。第二子像素包括：第二开关元件，连接至第二栅极线和第一数据线中的一条或都连接（至少一条）；第二液晶电容器，连接至第二开关元件，其具有的电容小于第一液晶电容器的电容；以及第二存储电容器，连接至第二开关元件，其具有的电容小于第一存储电容器的电容。向第二子像素施加预定电压，第一子像素可接收比第二子像素所接收电压小的电压。

多条第二栅极线可连接至第二开关元件，同时第二开关元件可连接至第一数据线。

可选地，多条第二数据线可连接至第二开关元件，同时第二开关元件可连接至第一栅极线。

下面将参照附图更详细地描述本发明，附图中示出了本发明的优选实施例。然而，本发明也可以其他形式实施，而不应局限于本文中所列举的典型实施例。

附图中，为了清晰起见，将层、薄膜、和区域的厚度放大了。全文中，相同的部件用相同的标号。应该明白，当提到例如层、薄

膜、区域、或基板等部件在另一部件“上面”时，可以是直接在另一部件上面，也可以是之间介有其他部件。下面，将参照附图来详细说明根据本发明的实施例的 LCD。

### 附图说明

本发明的上述和其他优点将通过结合附图对示例性实施例的详细描述而变得更加显而易见，在附图中：

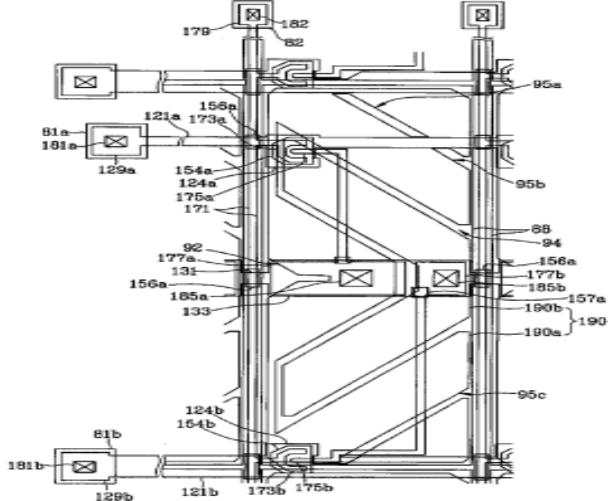

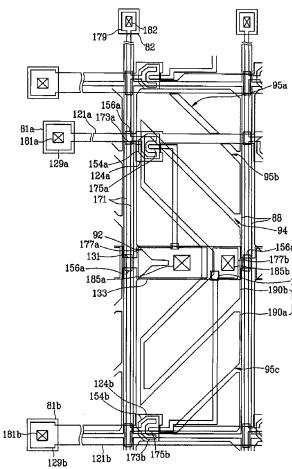

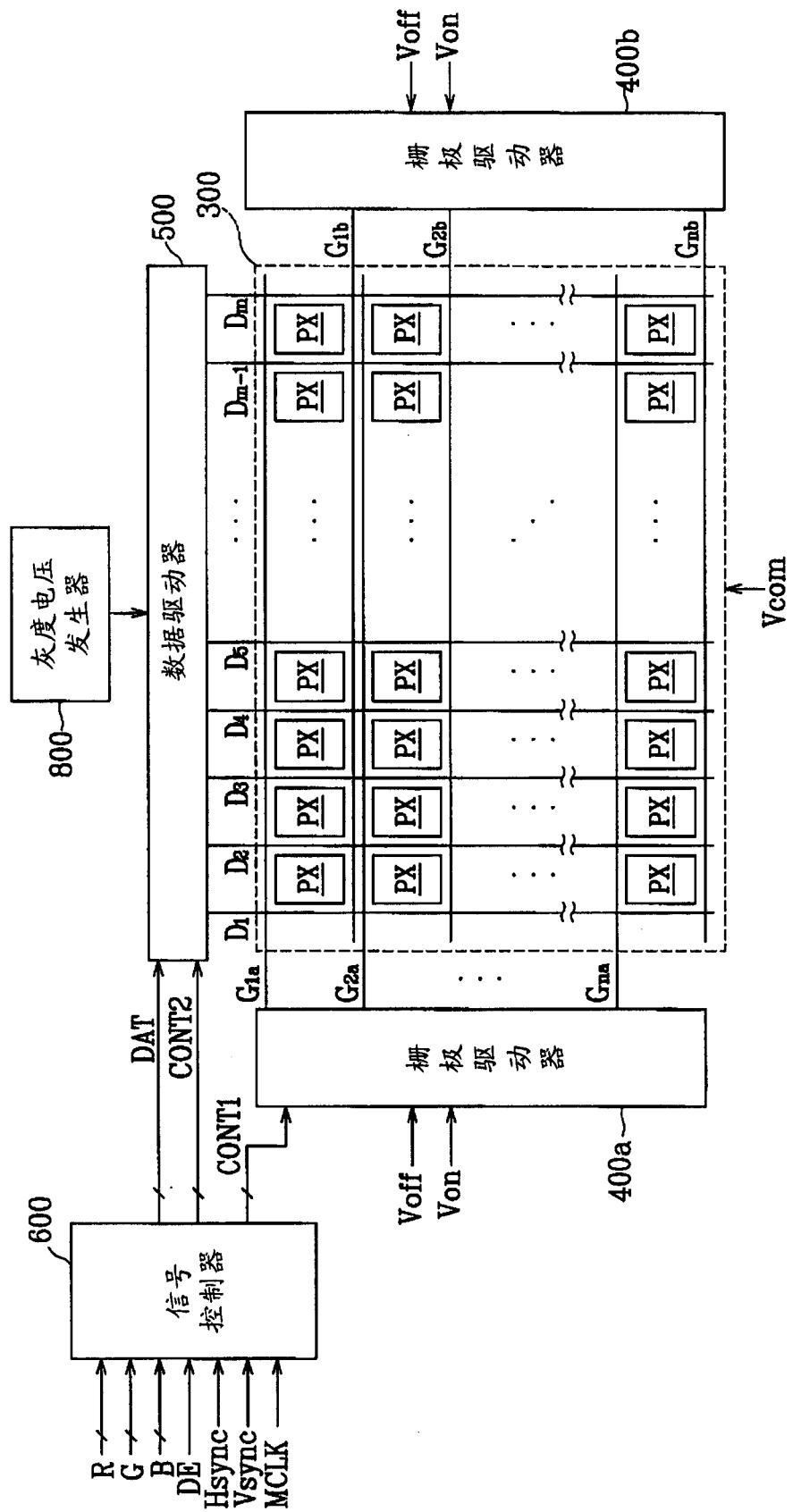

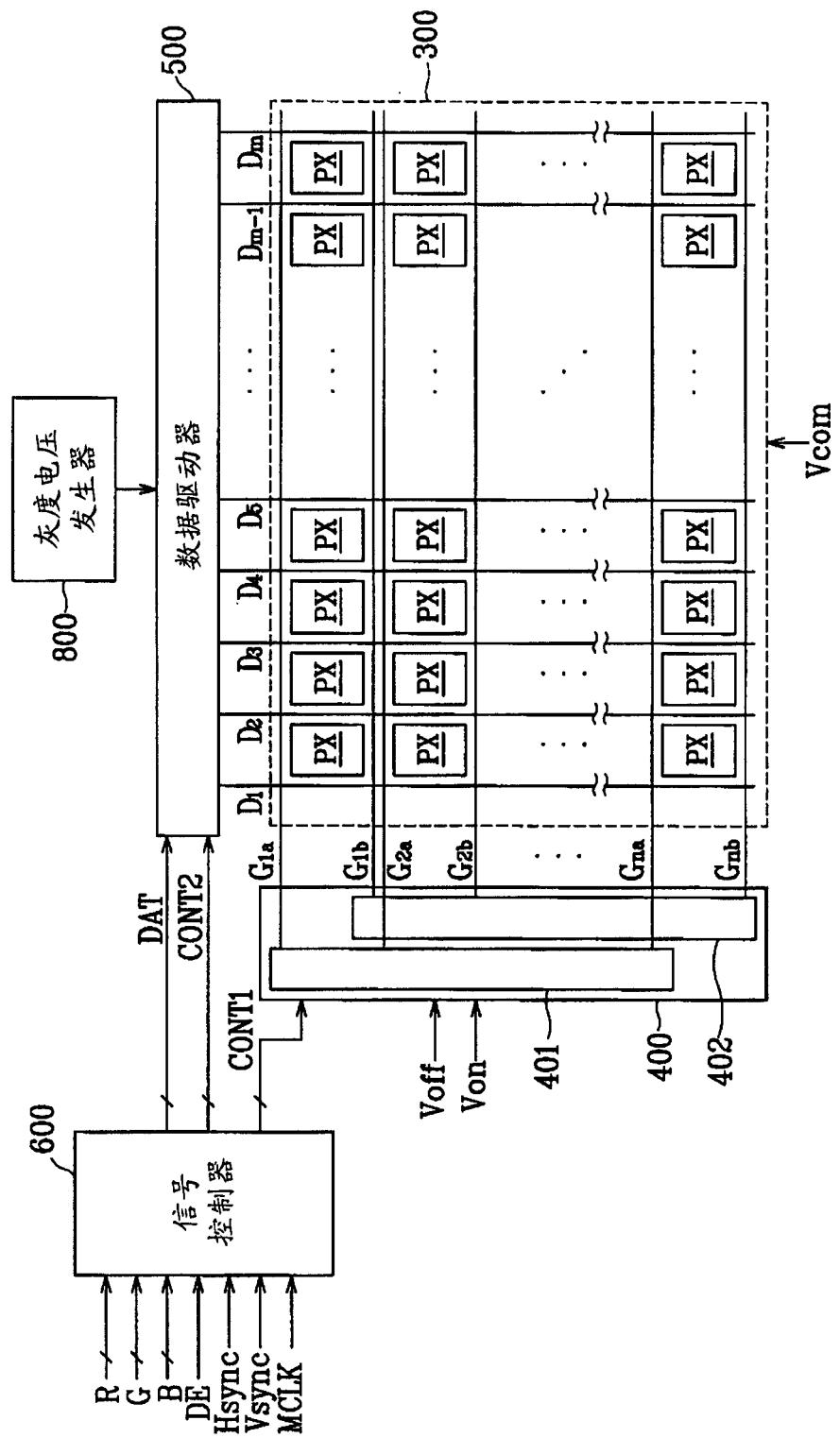

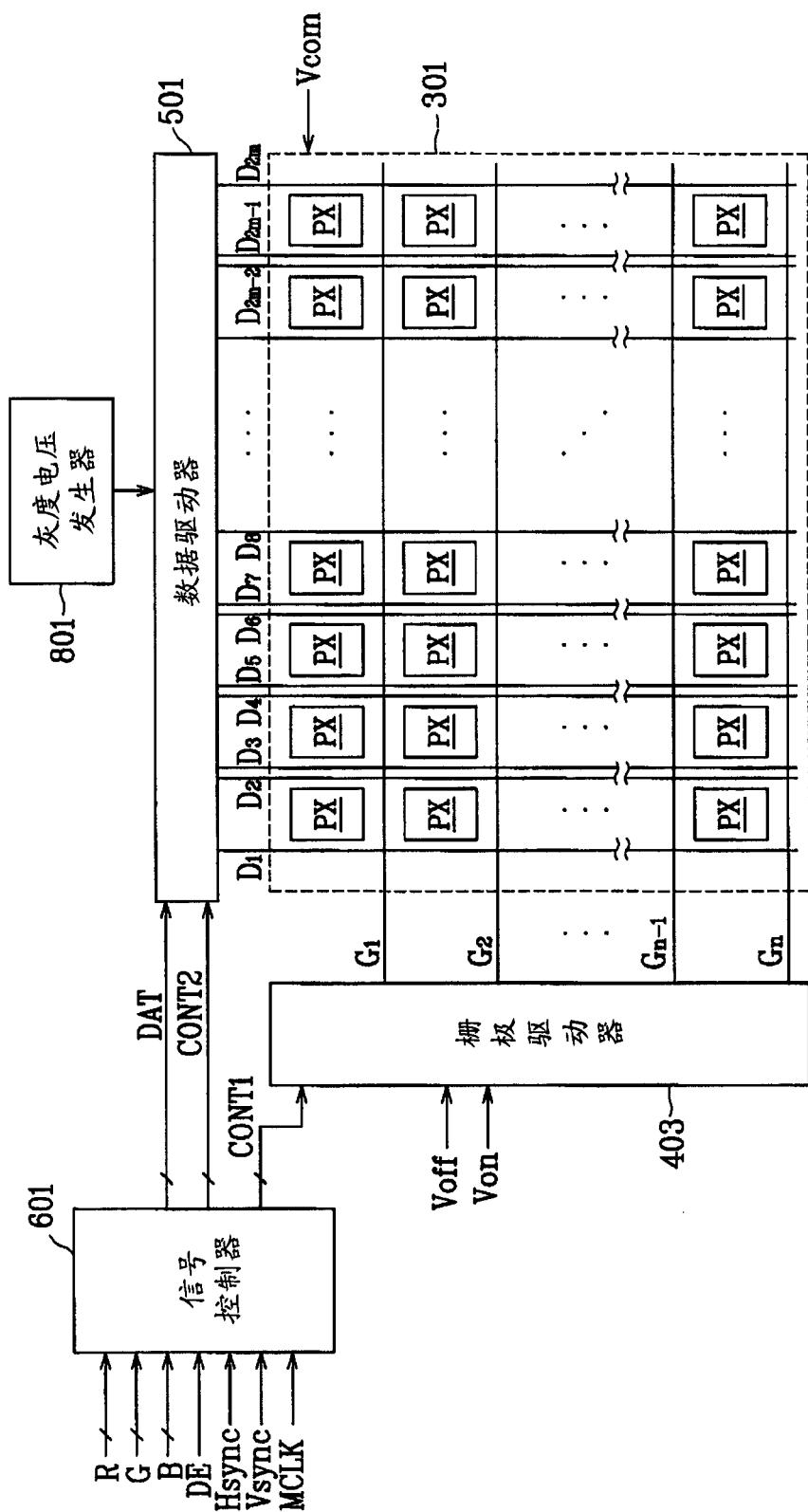

图 1A、1B、和 1C 是示出具有根据本发明的第一实施例构造的像素的 LCD 的框图；

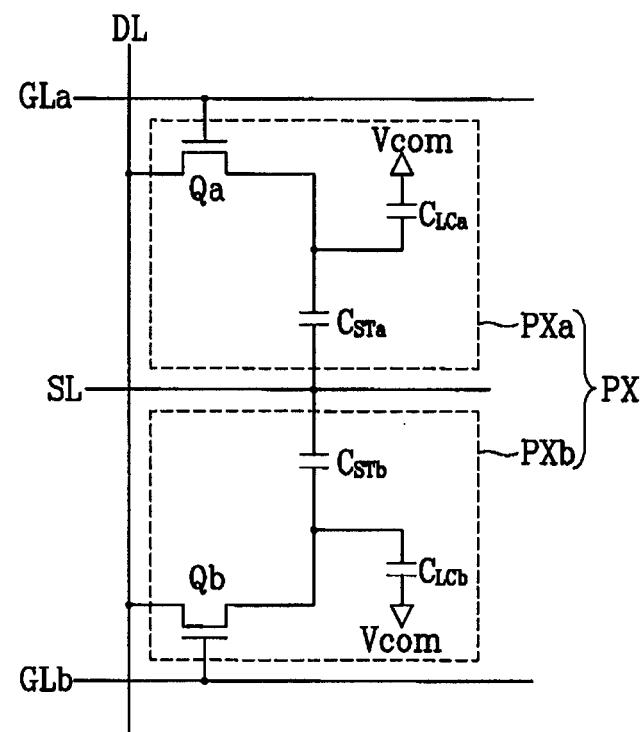

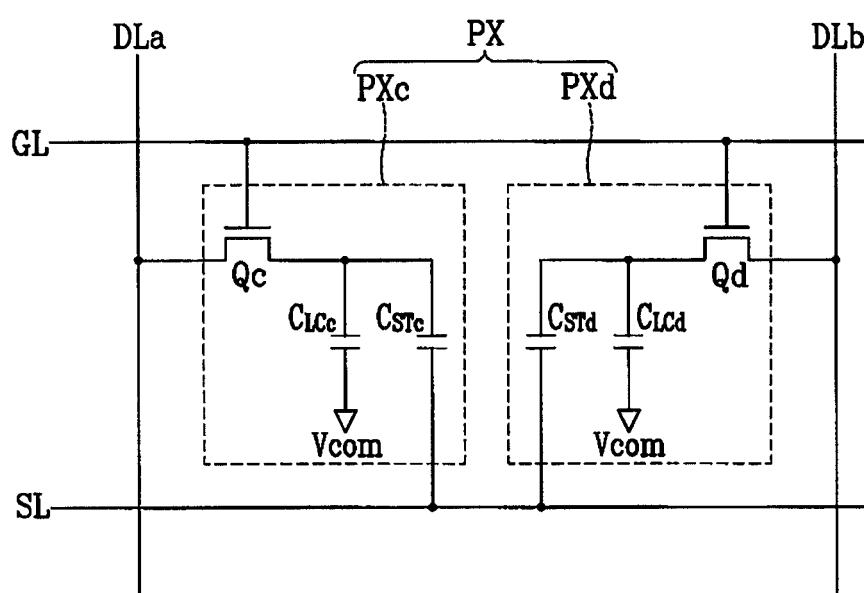

图 2 是根据本发明的第一实施例的 LCD 的像素的等效电路图；

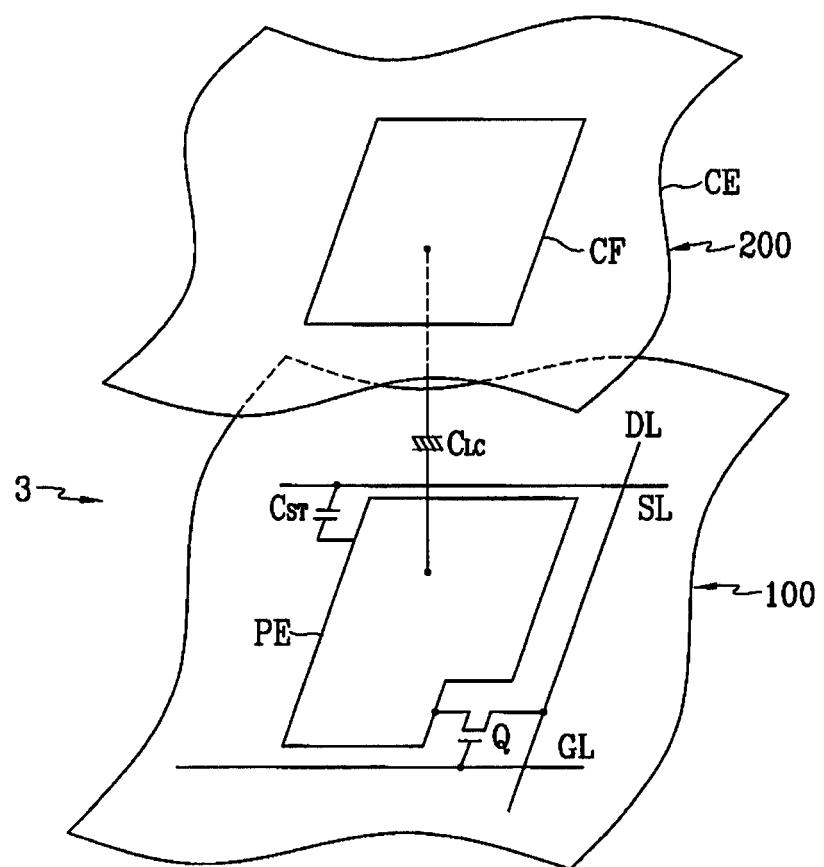

图 3 是根据本发明的各种实施例的 LCD 的像素的子像素的等效电路图；

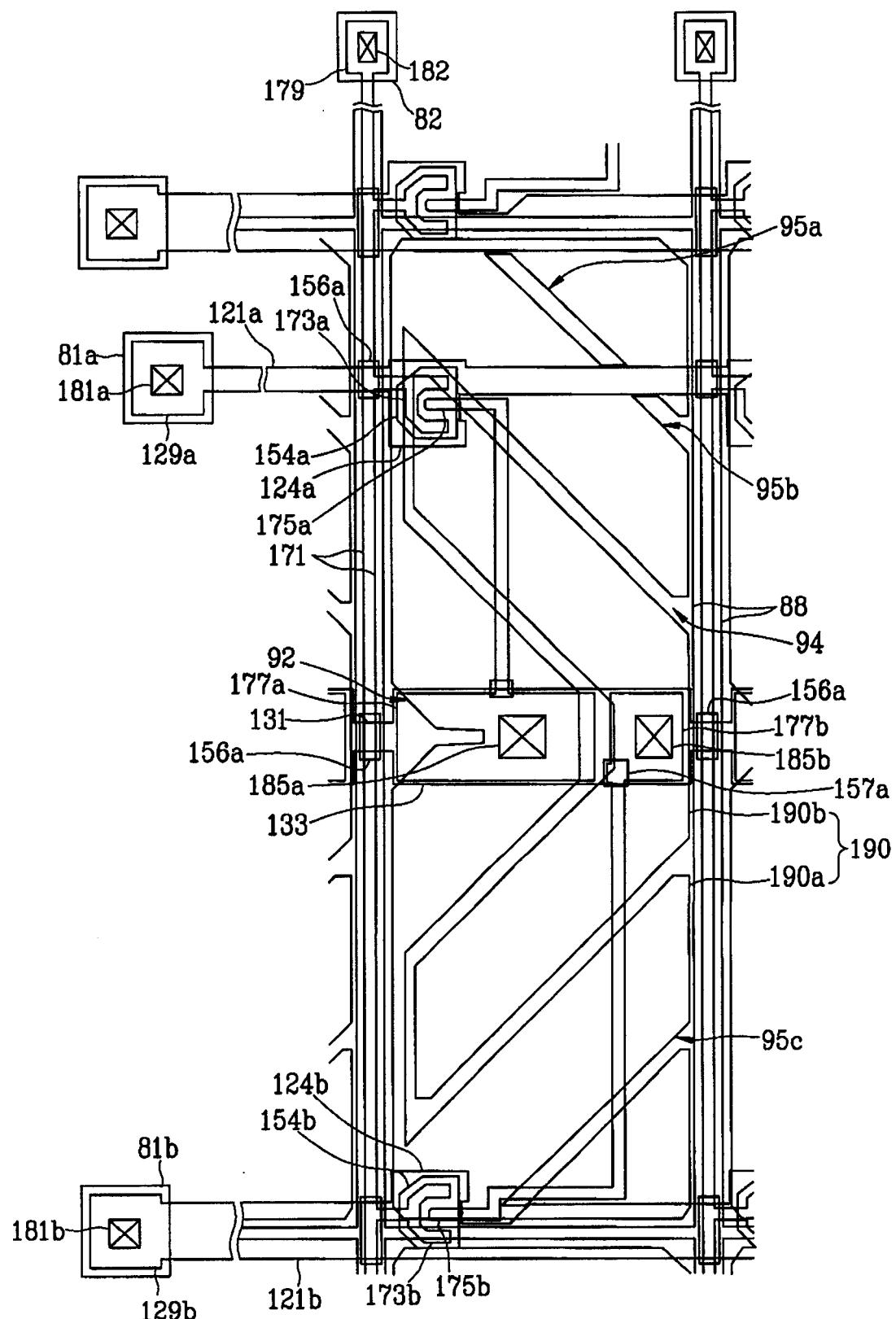

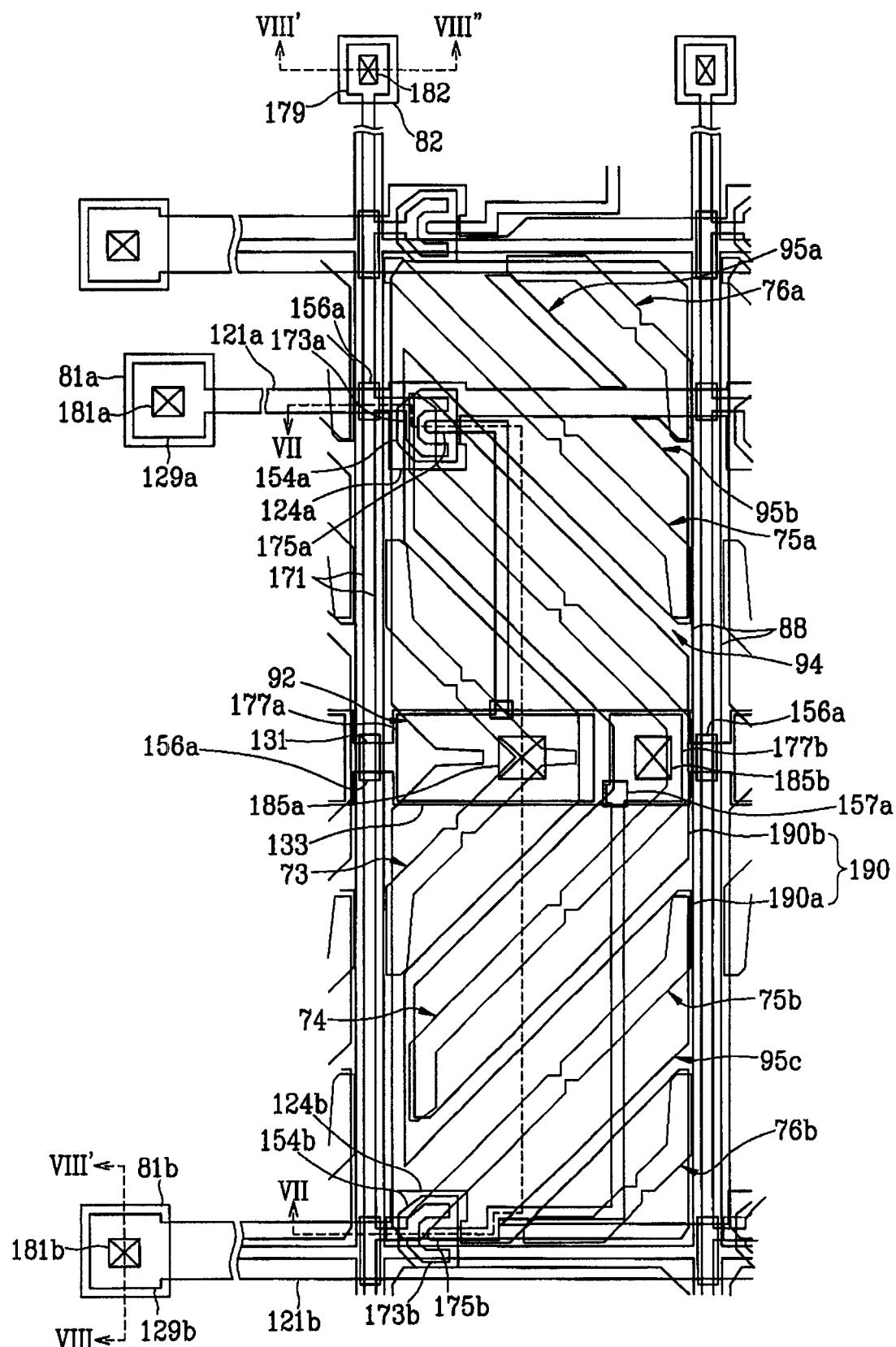

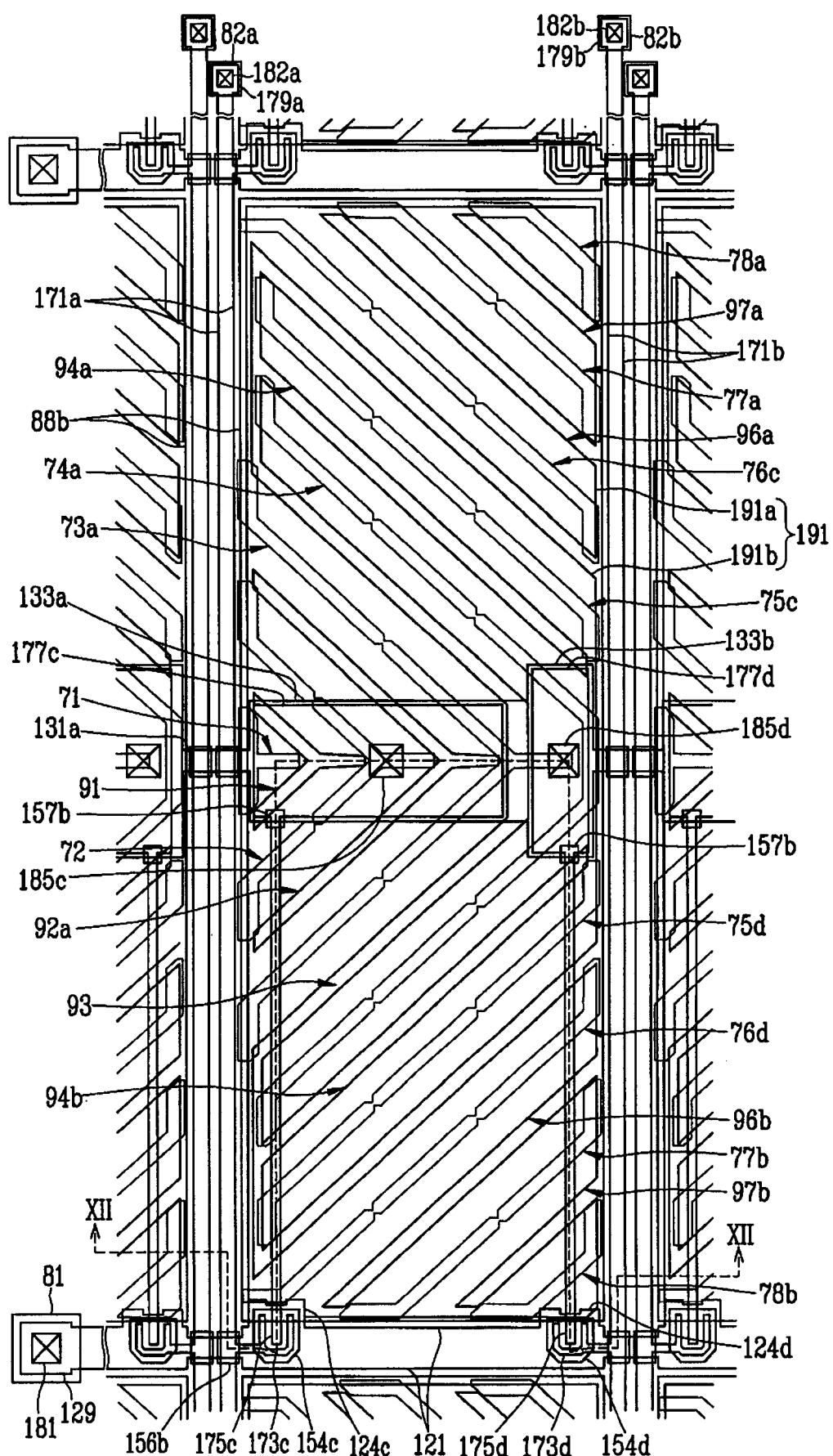

图 4 是用于根据本发明的第一实施例的 LCD 的下基板（面板）的平面图；

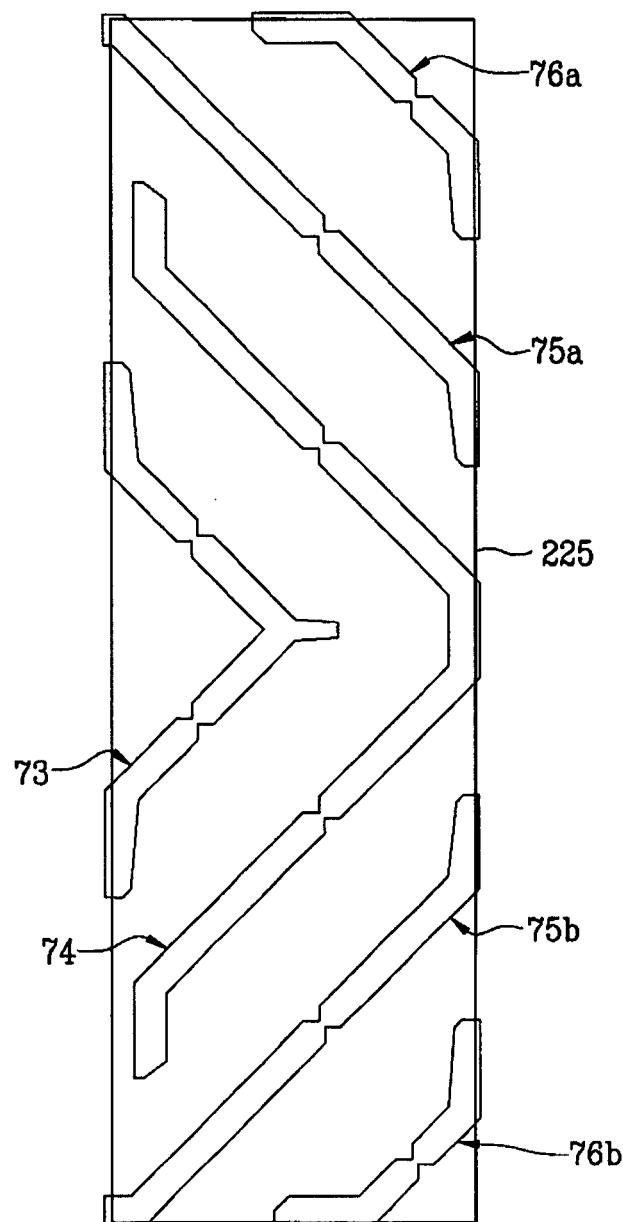

图 5 是用于根据本发明的第一实施例的 LCD 的上基板（面板）的平面图；

图 6 是具有图 4 的下基板（面板）和图 5 的上基板（面板）的液晶面板组件的平面图；

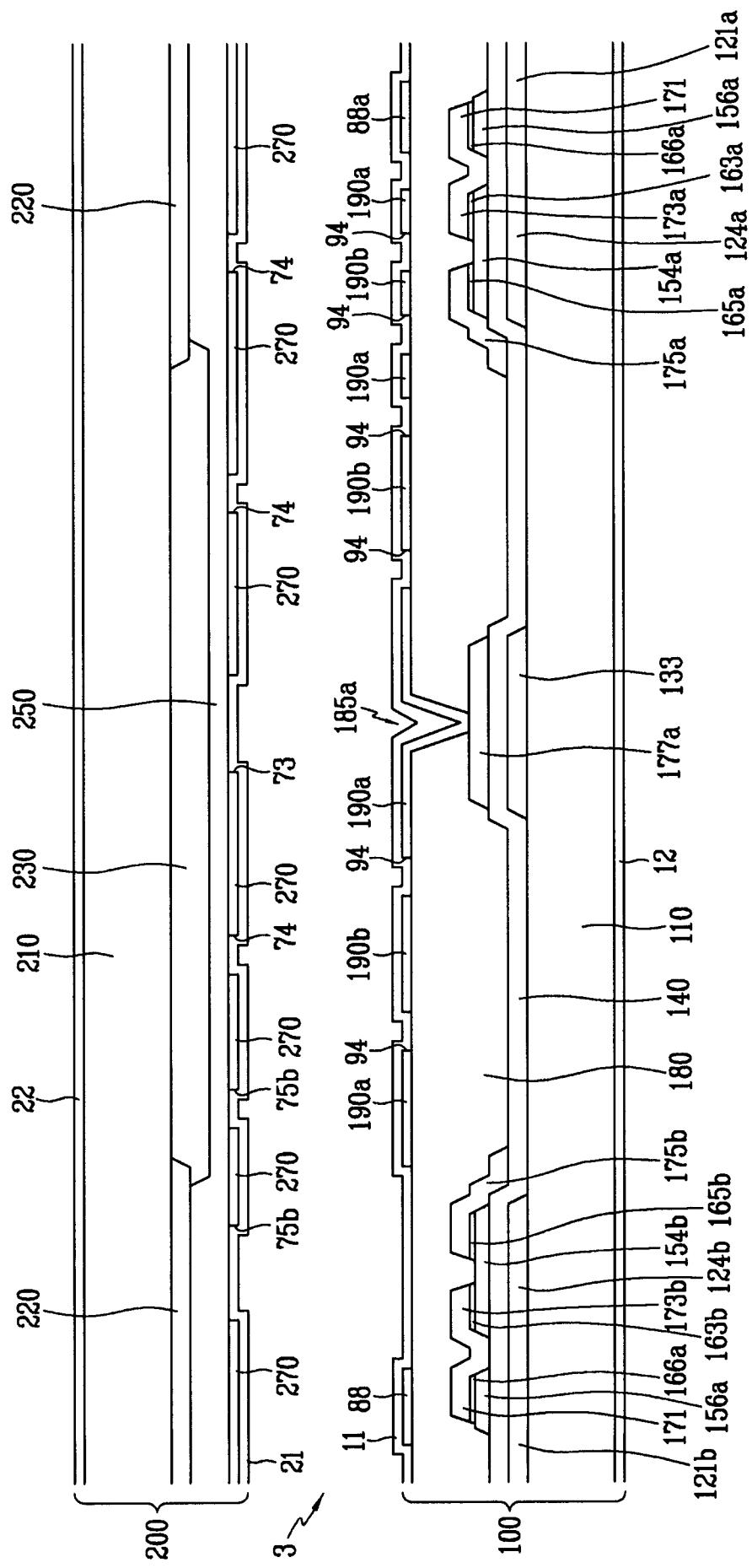

图 7 和图 8 是图 6 的液晶面板组件取剖线 VII-VII 和剖线 VIII-VIII 的剖视图；

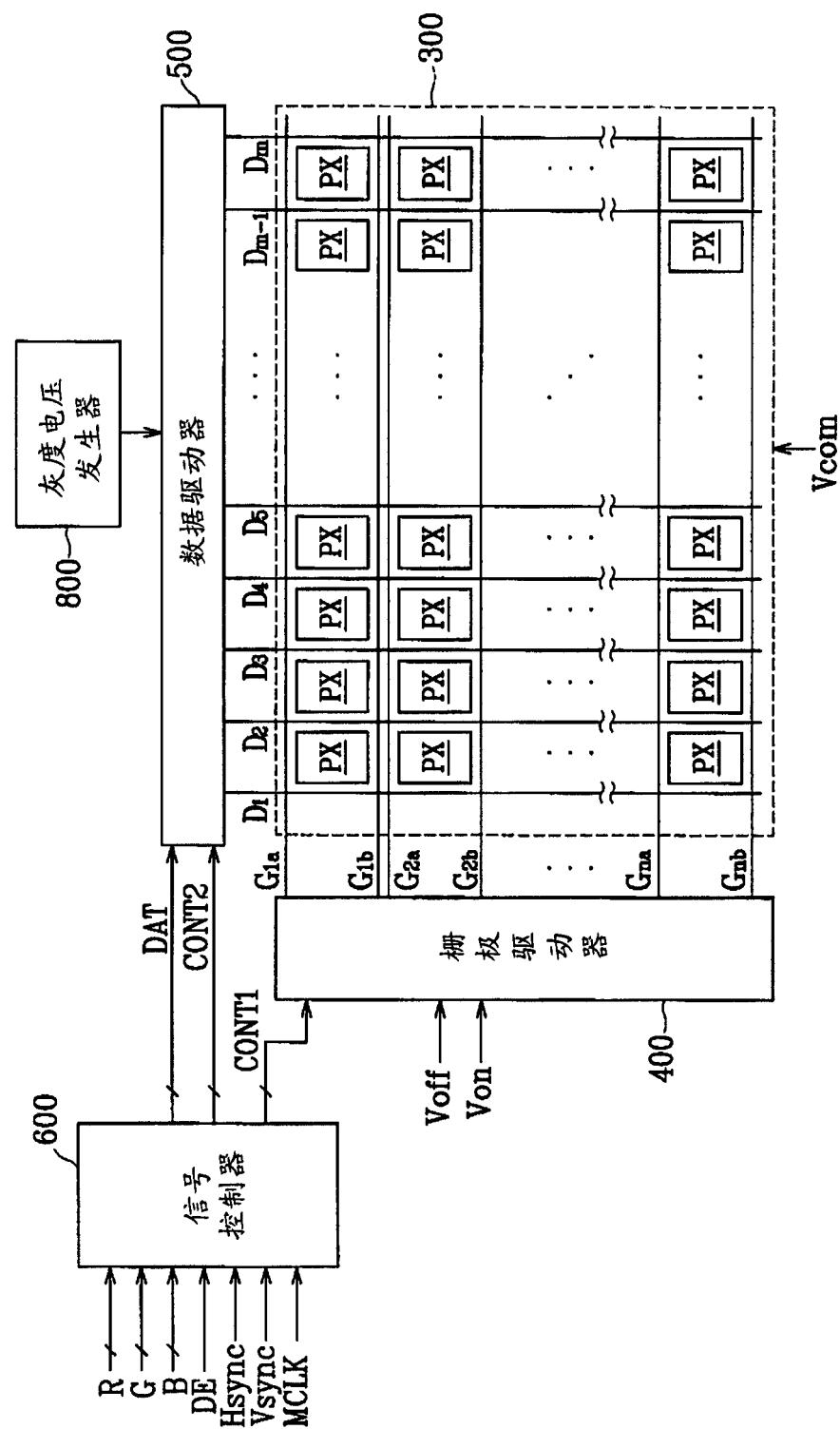

图 9 是包括根据本发明的第二实施例构造的像素的 LCD 的框图；

图 10 是根据本发明的第二实施例的 LCD 的像素的等效电路图；

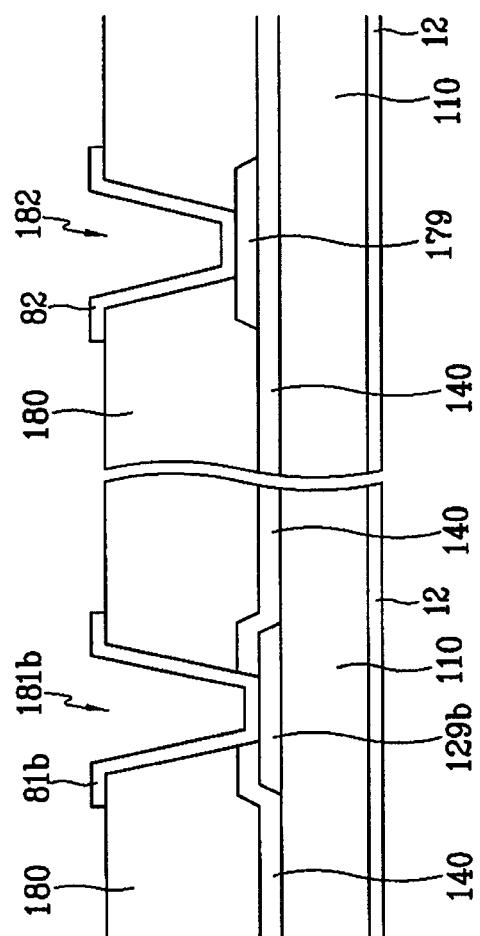

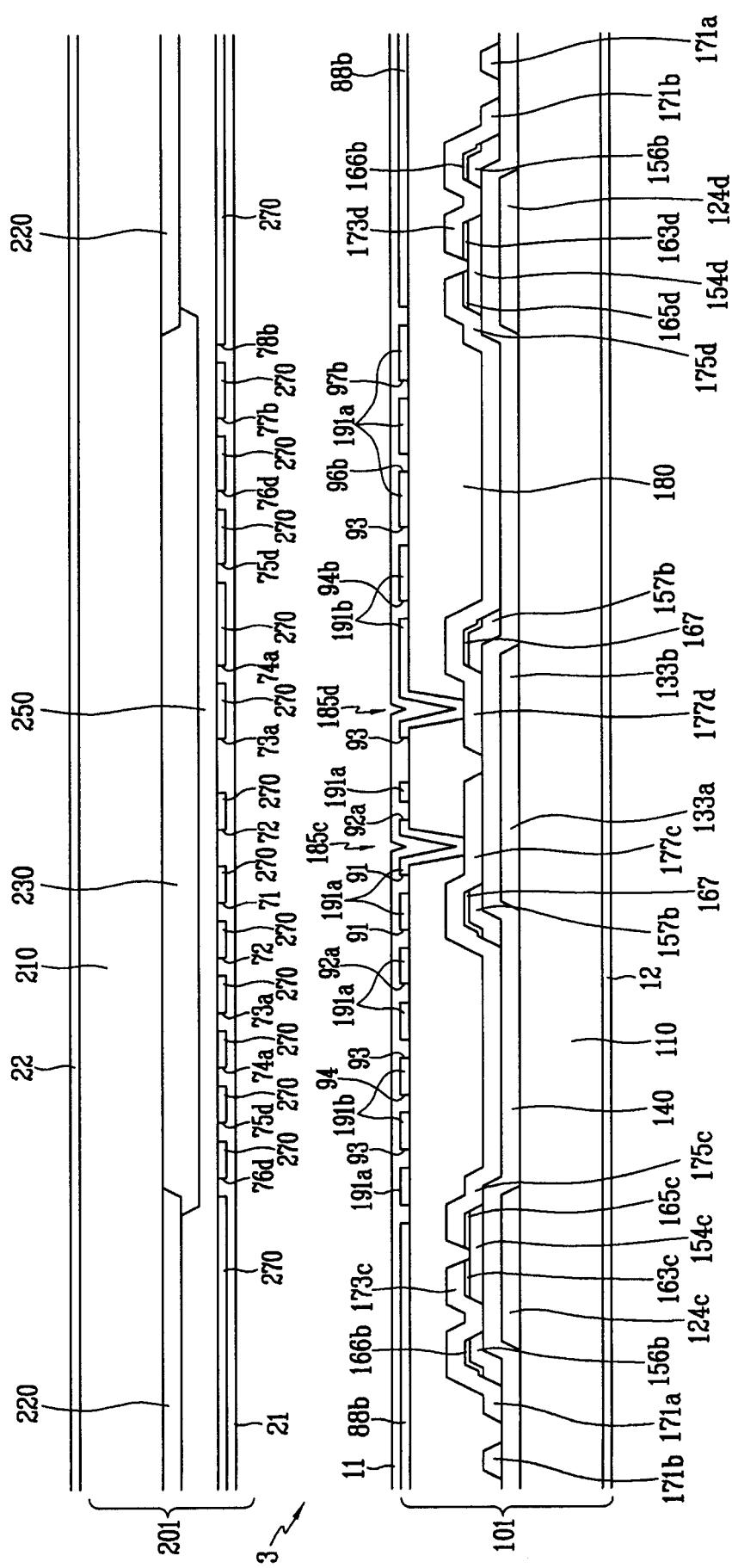

图 11 是根据本发明的第二实施例的液晶面板组件的平面图；

图 12 是图 11 的液晶面板组件取剖线 XII-XII 的剖视图；以及

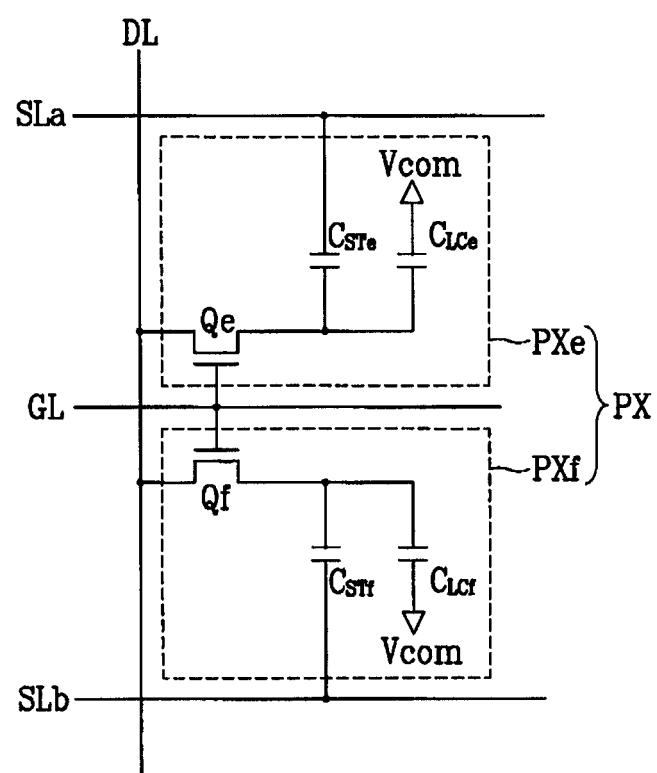

图 13 是根据本发明的第三实施例的 LCD 的像素的等效电路图。

### 具体实施方式

图 1A、1B、和 1C 分别是示出根据本发明的第一实施例的三种变化中的一种的 LCD 的框图。图 2 是根据图 1A、1B 和 1C 中所示的本发明的第一实施例的任何一个实施例中的 LCD 的像素的等效电路图，图 3 是根据本发明的图 1A、1B 和 1C 中所示的第一实施例的任何一个实施例的 LCD 中的像素的子像素的等效电路图。

如图 1A、1B 和 1C 中所示，根据本发明的第一实施例的 LCD 包括：液晶面板组件 300；一对栅极驱动器 400a 和 400b（图 1A）或单个栅极驱动器 400（图 1B），其连接至液晶面板组件 300；数据驱动器 500，连接至液晶面板组件 300；灰度电压发生器 800，连接至数据驱动器 500；以及信号控制器 600，用于控制它们。

液晶面板组件 300 包括多条显示信号线（栅极线 G1a-Gnb，和数据线 D1-Dm）、和多个（一个阵列的）像素 PX，其连接至这些显示信号线（如图 2 中所详细示出的那样连接），并排布成矩阵形式。如图 3 所示，结构上，液晶面板组件 300 包括彼此面对的第一基板（下面板）100 和第二基板（上面板）200，以及介于这两个基板（面板）之间的液晶层 3。

显示信号线（栅极线 G1a-Gnb，和数据线 D1-Dm）设置于第一基板（下面板）100 上。这些栅极线 G1a-Gnb 发送栅极信号（也称之为“扫描信号”），而数据线 D1-Dm 发送数据信号。栅极线 G1a-Gnb 沿（彼此平行的）像素行的（水平）方向延伸，而数据线 D1-Dm 沿（彼此平行的）像素列的（垂直）方向延伸。

图 2 示出了一个由“a”子像素和“b”子像素组成的像素（PX）的等效电路图，这两个子像素均连接至对应的显示信号线（分别连接至栅极线 GLa 和 GLb，以及数据线 DL）。显示信号线还包括存储电极线 SL。存储电极线 SL（水平地）平行于栅极线 GLa 和 GLb 而延伸。

像素阵列中的每个像素 PX 均包括一对子像素 PXa 和 PXb，每个子像素 PXa 和 PXb 分别包括开关元件 Qa 和 Qb，液晶电容器 C<sub>LCa</sub> 和 C<sub>LCb</sub> 分别连接至开关元件 Qa 和 Qb，以及存储电容器 C<sub>STa</sub> 和 C<sub>STb</sub>。每个存储电容器 C<sub>STa</sub> 和 C<sub>STb</sub> 分别连接至对应的开关元件（Qa 和 Qb），并都连接至存储电极线 SL。

参照图 3，每个子像素 PXa 和 PXb 的开关元件 Q（Qa 或 Qb）由形成于第一基板（下面板）100 上的薄膜晶体管 TFT 形成。开关元件 Q（Qa 或 Qb）是三极管器件，具有连接至栅极线 GL 的控制端（称为“栅极”）、连接至数据线 DL 的输入端（称为“源极”）、以及输出端（称为“漏极”）。开关元件 Q（Qa 或 Qb）的漏极连接至液晶电容器 C<sub>LC</sub> 和存储电容器 C<sub>ST</sub>。

如图 3 所示，液晶电容器 C<sub>LC</sub> 包括：两个端子，其由第一基板（下面板）100 的子像素电极 PE 和第二基板（上面板）200 的共电极 CE 组成；以及电介质，其由设置于两个电极 PE 和 CE 之间的液晶层 3 组成。子像素电极 PE 连接至开关元件 Q，共电极 CE 可形成于第二基板（上面板）200 整个表面之上，以接收共电压 V<sub>com</sub>。

可选地，与图 3 中所示的结构反之，共电极 CE 可设置于第一基板（下面板）100 之上，这样，这两个电极 PE 和 CE 中的一个或两个都以线状或条带状靠近另一电极而形成于第一基板（下面板）100 上。

通过将设置于第一基板（下面板）100 上的存储电极线 SL 与像素电极 PE 重叠并插入绝缘体，来形成与液晶电容器  $C_{LC}$  并联的存储电容器  $C_{ST}$ ，且将例如共电压  $V_{com}$  的预定电压施加于存储电极线 SL。可选地，可通过将子像素电极 PE 与不同行的像素的栅极线重叠并插入绝缘体，来形成存储电容器  $C_{ST}$ 。

各个像素 PX 中的每一个优选地表现多种原色中的一种原色的光（空间分割（spatial division）），或可选地以时序（temporal order）表现每种原色（时间分割（time division）），使得像素阵列的彩色输出可感知为原色的空间或时间总和。这些原色包括红色、绿色、和蓝色。

图 3 示出了当每个像素在第二基板（上面板）200 上具有表现一种原色的滤色器 CF 的情况下空间分割的实例。不同于图 3 中所示的结构，可选地，滤色器 CF 可以形成于第一基板（下面板）100 上的子像素电极 PE 之上或之下。

如图 1A、1B、和 1C 所示，栅极驱动器（400a 和 400b、或 400）连接至多条栅极线 G1a-Gnb，以施加栅极信号至每个子像素中的 TFT 的栅极（见图 3）。栅极信号作为二进制信号以栅极导通（gate on）电压和栅极关断（gate off）电压（ $V_{on}$  和  $V_{off}$ ）发送，被从外部接收。

如图 1A 中所示，一对栅极驱动器 400a 和 400b 形成全栅极驱动器（类似于图 1B 和 1C 中所示的栅极驱动器 400），并分别位于

液晶面板组件 400 的左侧和右侧，并分别连接至第奇数条和第偶数条栅极线 G1a-Gnb。可选地，如图 1B 和 1C 中所示，一个栅极驱动器 400 位于液晶面板组件 300 的一侧，并连接至所有的栅极线 G1a-Gnb。如图 1C 所示，两个驱动电路 401 和 402 内建于栅极驱动器 400 中，并分别连接至第奇数条和第偶数条栅极线 G1a-Gnb。

灰度电压发生器 800 产生与每个像素的两个透光率（每个子像素一个透光率）相关联的两个灰度电压设置（set）（或参考灰度电压设置）。将两个不同的灰度电压分别地供送至构成每一个像素的两个子像素。每个灰度电压设置包括相对于共电压 Vcom 为正值的灰度电压，和相对应共电压 Vcom 为负值的灰度电压。可选地，可以只生成单个（参考）灰度电压设置，而不是两个（参考）灰度电压设置。

单个数据驱动器 500 连接至液晶面板组件 300 的所有数据线 D1-Dm，以从灰度电压发生器 800 中选择和输出两个灰度电压设置中所选的一个设置，并将一个所选灰度电压设置的灰度电压施加于子像素作为数据电压。然而，当灰度电压发生器 800 不提供所有灰度电压，而只提供参考灰度电压时，数据驱动器 500 分离这些参考灰度电压，并生成（输出）所有灰度电压。

栅极驱动器 400（或 400a 和 400b）或数据驱动器 500 直接安装于第一基板（下面板）100 上，形式为一个或多个驱动集成电路芯片，或安装于柔性印刷电路膜（未示出）上且以带载封装（tape carrier package，缩写为 TCP）方式附着至液晶面板组件 300。反之，栅极驱动器 400（或 400a 和 400b）或数据驱动器 500 可集成于第一基板（下面板）100 上。

信号控制器 600 控制栅极驱动器 400 和数据驱动器 500 的操作。

下面将参照图 4 至图 8 详细说明液晶面板组件 300 的结构。

图 4 是用于根据本发明(图 1A、1B、1C)的第一实施例的 LCD 的第一基板(下面板)100 的平面图；图 5 是用于根据本发明的第一实施例的 LCD 的第二基板(上面板)200 的平面图。图 6 是具有图 4 所示的第一基板(下面板)和图 5 所示的第二基板(上面板)的液晶面板组件的组合平面图。图 7 和图 8 分别是图 6 的液晶面板组件取剖线 VII-VII 和剖线 VIII-VIII'-VIII' 的剖视图。

如图 4 至图 8 所示，根据第一实施例的 LCD 面板组件包括：下面板 100；上面板 200，面向下面板 100；以及液晶层 3，设置于这些面板之间。

下面将参照图 4、6、7 和 8 详细说明下面板 100。

在可包括透明玻璃或塑料的绝缘基板 110 上形成多对第一和第二栅极线 121a 和 121b 以及多条存储电极线 131。

第一和第二栅极线 121a 和 121b 彼此平行(水平地)延伸，并彼此物理地分离且电分离，并发送栅极信号至子像素中的 TFT 的栅极。第一和第二栅极线 121a 和 121b 水平地排布。每条栅极线 121a 具有多个第一栅电极 124a，每条栅极线 121b 具有多个栅电极 124b。栅电极 124a 和 124b 向上和向下突起。第一和第二栅极线 121a 和 121b 还具有左侧区域加宽端部(端子)129a 和 129b，以连接至其他层或驱动电路。可选地，端部(端子)129a 和 129b 排布于第一和第二栅极线 121a 和 121b 的右侧、或分别排布于其左侧和右侧。

存储电极线 131 水平地延伸，并且相比于第二栅极线 121b，位置可更靠近第一栅极线 121a。各条存储电极线 131 包括多个存储电极 133。存储电极 133 为矩形形状，以相对于存储电极线 131 对称。然而，包括有存储电极 133 的存储电极线 131 的形状和排布可以各

种方式变化。向存储电极线 131 施加预定电压，例如向上面板 200 的共电极 270 施加共电压。

栅极线 121a 和 121b 以及存储电极线 131 由基于铝的金属材料例如铝 (Al) 和铝合金形成，或者由基于银的金属材料例如银 (Ag) 和银合金形成，或者由基于铜的金属材料例如铜 (Cu) 和铜合金形成，或者由基于钼的金属材料例如钼 (Mo) 和钼合金形成，或者由铬 (Cr)、钛 (Ti)、或钽 (Ta) 形成。可选地，栅极线 121a 和 121b 以及存储电极线 131 可包括由物理性质不相同的两个导电层 (未示出) 形成的多层结构。一个导电层用低电阻常数金属材料例如基于铝的金属材料、基于银的金属材料、和基于铜的金属材料形成，使得其减少栅极线 121a 和 121b 以及存储电极线 131 的信号延迟或电压降。反之，另一个导电层用相对于其他材料例如铟锡氧化物 ITO 和铟锌氧化物 IZO 而言具有优异接触 (附着) 性的材料形成，例如基于钼的金属材料、铬、钛、和钽。该结合的优选实例是用基于铬的下层和基于铝 (合金) 的上层构成的结构，以及用基于铝 (合金) 的下层和基于钼 (合金) 的上层构成的结构。另外，栅极线 121a 和 121b 以及存储电极线 131 可以用各种或其他金属材料和导体形成。

栅极线 121a 和 121b 的侧面以及存储电极线 131 的侧面相对于基板 110 的表面倾斜，优选地为 30-80°。

栅极绝缘层 140 由硅氮化物 (SiNx) 形成于栅极线 121a 和 121b 以及存储电极线 131 上。

在栅极绝缘层 140 上由氢化非晶硅 (hydrogenated amorphous silicon) (简称为 a-Si) 或多晶硅形成多个半导体岛 (semiconductor island)。在栅电极 124a 和 124b 上分别形成半导体岛 154a 和 154b。

在半导体岛 **154a**、**154b**、和 **156a** 上，由硅化物或其中高浓度掺杂 n 型杂质例如磷的 n+氢化非晶硅形成多个欧姆接触。在第一和第二半导体岛 **154a** 和 **154b** 上分别设置一对第一欧姆接触 **163a** 和 **163b** 以及一对第二欧姆接触 **165a** 和 **165b**。在第三半导体岛 **156a** 上设置第三欧姆接触 **166a**。

半导体岛 **154a**、**154b**、**156a**、和 **157a** 以及欧姆接触 **163a**、**163b**、**165a**、**165b**、和 **166a** 的侧面相对于基板 **110** 的表面倾斜 30-80°。

在欧姆接触 **163a**、**163b**、**165a**、**165b**、和 **166a** 和栅极绝缘层 **140** 上形成多条数据线 **171** 和多对第一和第二漏电极 **175a** 和 **175b**。

数据线 **171** 垂直地延伸，使得它们越过（跨过）栅极线 **121a** 和 **121b** 以及（跨过）存储电极线 **131**，以发送数据电压至像素。各条数据线 **171** 包括多个分别延伸向第一和第二栅电极 **124a** 和 **124b** 的第一和第二源（TFT 源极）电极 **173a** 和 **173b**。各条数据线 **171** 具有宽度扩大的端部（端子）**179**，以便于与其他层或与外部器件进行连接。

第一和第二漏电极 **175a** 和 **175b** 与数据线 **171** 分开，分别面向围绕着栅电极 **124a** 和 **124b** 的源电极 **173a** 和 **173b**。第一和第二漏电极 **175a** 和 **175b** 具有设置于半导体岛 **154a** 和 **154b** 上的条带状端部（端子），并具有延长部，其从条带状端部伸出，且被具有宽区域的存储电极 **133** 重叠。第一和第二漏电极 **175a** 和 **175b** 的条带状端部被 U 形源电极 **173a** 和 **173b** 部分地围绕。第二漏电极 **175b** 的延长部 **177b** 的面积比第一漏电极 **175a** 的延长部 **177a** 的面积小。

第一和第二薄膜晶体管 **Qa** 和 **Qb** 由以下组成：半导体岛 **154a** 和 **154b** 以及第一和第二栅电极 **124a** 和 **124b**、第一和第二源电极 **173a** 和 **173b**、以及第一和第二漏电极 **175a** 和 **175b**。薄膜晶体管

Qa 和 Qb 的通道分别形成于第一和第二源电极 173a 和 173b 与第一和第二漏电极 175a 和 175b 之间的半导体岛 154a 和 154b 中。

数据线 171 和漏电极 175a 和 175b 优选地用难熔金属例如钼、铬、钽、和钛或它们的合金形成，或者可包括多层结构，其具有难熔金属层（未示出）和低电阻导电层（未示出）。多层结构的实例为双层结构，具有基于铬或钼（合金）的下层和基于铝（合金）的上层；以及三层结构，具有基于钼（合金）的下层、基于铝（合金）的中层和基于钼（合金）的上层。另外，数据线 171 和漏电极 175a 和 175b 可由各种其他金属或导体形成。

漏电极 175a 和 175b 倾斜 30-80°（类似于栅极线 121a 和 121b 和存储电极线 131、数据线 171 的侧面）。

欧姆接触 163a、163b、165a、165b、和 166a 仅位于下层半导体岛 154a、154b、156a、和 157a 与上层数据线 171 和漏电极 175a 和 175b 之间，以降低接触电阻。半导体岛 154a 和 154b 具有透过源电极 173a 和 173b 以及漏电极 175a 和 175b 而暴露的部分。半导体岛 156a 和 157a 使栅极线 121a 和 121b 以及存储电极线 131 的表面轮廓光滑，从而防止数据线 171 和漏电极 175a 和 175b 被切割。

在数据线 171、漏电极 175a 和 175b、以及半导体岛 154a 和 154b 的暴露部分上形成钝化层 180。钝化层 180 由无机绝缘材料例如硅氮化物和硅氧化物、有机绝缘材料、或低介电常数绝缘材料形成。有机绝缘材料和低介电常数绝缘材料优选地具有 4.0 或低于 4.0 的介电常数，低介电常数绝缘材料的实例是通过等离子体增强化学气相沉积（PECVD）形成的 a-Si:C:O 和 a-Si:O:F。钝化层 180 可以用具有光敏性的有机绝缘材料形成，可使钝化层 180 的表面变平。可选地，钝化层 180 可具有双层结构，其具有无机物下层和有机物上

层，使得它表现出有机层的优异绝缘特性，且不会伤害半导体岛 154a 和 154b 的暴露部分。

穿过钝化层 180 形成多个接触孔 182、185a、和 185b，从而分别暴露数据线 171 的端部 179 以及漏电极 175a 和 175b 的延长部 177a 和 177b。穿过钝化层 180 和栅极绝缘层 140 形成多个接触孔 181a 和 181b，从而暴露栅极线 121a 和 121b 的端部 129a 和 129b。

在钝化层 180 上用透明导电材料例如 ITO 和 IZO、或反射性金属材料例如铝、银、和其合金形成多个像素电极 190（由第一和第二子像素电极 190a 和 190b 组成）、屏蔽电极 88、以及多个接触辅助件（contact assistant）81a、81b、和 82。

第一和第二子像素电极 190a 和 190b 通过接触孔 185a 和 185b 物理连接且电连接至第一和第二漏电极 175a 和 175b，以接收来自于第一和第二漏电极 175a 和 175b 的数据电压。将相对于一个输入图像信号（一个对应于一种颜色的亮度的图像数据）不同的预定电压施加于子像素电极对 190a 和 190b，并依据子像素电极 190a 和 190b 的大小和形状确定其大小。此外，子像素电极 190a 和 190b 的面积可互不相同。例如，当第二子像素电极 190b 面积小于第一子像素电极 190a 时，它可以接收比第一子像素电极 190a 所接收电压高的电压。

一旦收到数据电压，子像素电极 190a 和 190b 与共电极 270 一起产生电场，该电场排列两个电极 190（190a 和 190b）和 270 之间的液晶层 3 的液晶分子。

正如前面说明过的，子像素电极 190a 和 190b 与共电极 270（介电液晶层 3 的液晶分子）形成液晶电容器  $C_{LCa}$  和  $C_{LCb}$ ，以维持施加于它们的电压在薄膜晶体管 Qa 和 Qb 关断之后平稳。存储电容器

$C_{STA}$  和  $C_{STB}$  设置成与液晶电容器  $C_{LCa}$  和  $C_{LCb}$  并联, 以增强电压存储能力 (用于在薄膜晶体管  $Qa$  和  $Qb$  关断之后保持平稳)。通过将第一和第二子像素电极 **190a** 和 **190b** 与存储电极 **133** 相重叠以形成存储电容器  $C_{STA}$  和  $C_{STB}$ , 其中第一和第二子像素电极在与其连接的漏电极 **175a** 和 **175b** 的延长部之上。

由于第一子像素电极 **190a** 面积比第二子像素电极 **190b** 大, 所以第一液晶电容器  $C_{LCa}$  的电容大于第二液晶电容器  $C_{LCb}$  的电容。由于重叠于存储电极的第一漏电极的延长部 **177a** 面积大于第二漏电极 **175b** 的延长部 **177b**, 所以第一存储电容器  $C_{STA}$  的电容大于第二存储电容器  $C_{STB}$  的电容。因此, 第一薄膜晶体管  $Qa$  的电流驱动能力应该大于第二薄膜晶体管  $Qb$  的电流驱动能力, 并且第一薄膜晶体管  $Qa$  的  $W/L$  值 (其中,  $W$  是通道宽度,  $L$  是通道长度) 相应地高于第二薄膜晶体管  $Qb$  的  $W/L$  值。

各像素电极 **190** 的 4 个角被切边 (edge-cut at), 并且切割腿 (cut leg) 相对于栅极线 **121a** 和 **121b** 倾斜  $45^\circ$ 。一对 (形成一个像素电极 **190** 的) 第一和第二子像素电极 **190a** 和 **190b** 彼此交错 (intermix), 同时被间隙 **94** 分开, 整个像素电极 **190** 外形基本上为矩形形状。第二子像素电极 **190b** 形状为等边梯形 (equilateral trapezoid), 具有梯形凹陷底部 (trapezoid-hollowed base)。第二子像素电极 **190b** 基本上被第一子像素电极 **190a** 围绕。第一子像素电极 **190a** 由彼此的左边相连接的上部梯形 (upper trapezoid)、下部梯形 (lower trapezoid)、以及中间梯形 (middle trapezoid) 相连接。第一子像素电极 **190a** 具有切口 **95a**、**95b**、以及 **95c**, 其从上部梯形的顶边和下部梯形的底边延伸至它们的右边。栅极线 **121a** 在切口 **95a** 和 **95b** 之间延伸。第一子像素电极 **190a** 的中间梯形填充入第二子像素电极 **190b** 的凹陷底部。第一子像素电极 **190a** 具有沿着存储电极线 **131** 延伸的切口 **92**, 该切口 **92** 在第一子像素电极 **190a** 的左边具有入口 (entrance), 以及从该入口水平地延伸出水平部分。切口 **92** 的入口

具有一对相对于存储电极线 131 倾斜 45°的腿 (leg)。第一和第二子像素电极 190a 和 190b 之间的间隙 94 包括: 两对相对于栅极线 121a 和 121b 倾斜 45°的上和下倾斜部分, 并具有基本上相等的宽度; 以及三个宽度基本上相等的垂直部分。为了方便说明, 间隙 94 也可称之为切口。切口 92、94、95a、95b、和 95c 相对于存储电极线 131 镜面对称, 并相对于栅极线 121a 和 121b 倾斜 45°, 同时彼此垂直延伸。由于切口 92、94、95a、95b、和 95c 导致像素电极 190 被划分成多个区域。

因此, 像素电极 190 水平平分地围绕存储电极线 131, 分别通过切口 92、94、和 95a-95c 将像素电极 190 的上半部和下半部分成 4 个区域。划分的区域或切口的数量根据设计因素例如像素尺寸、像素电极 190 的水平边比垂直边的长度比、以及液晶层 3 的类型或特性而变化。

第一子像素电极 190a 被第一和第二栅极线 121a 和 121b 重叠, 第二子像素电极 190b 被第一栅极线 121a 重叠。第一栅极线 121a 在像素电极 190 的上半部的中心处延伸。

屏蔽电极 88 (88a) 具有沿着数据线 171 延伸的垂直部分, 以及沿着第二栅极线 121b 延伸的水平部分。

屏蔽电极 88 的垂直部分完全地重叠数据线 171, 其水平部分设置于栅极线 121b 的边界之内。屏蔽电极 88 通过接触孔 (未示出) 连接至存储电极线 131, 该接触孔穿过钝化层 180 和栅极绝缘层 140; 或连接至短路点 (short point), 用于将共电压 Vcom 从下面板 100 中继至上面板 200。

屏蔽电极 88 接收共电压 Vcom, 并屏蔽在数据线 171 与像素电极 190 之间以及在数据线 171 与共电极 270 之间形成的电场, 从而

防止像素电极 190 的电压畸变和数据线 171 所发送的数据电压的信号延迟。

此外，像素电极 190 和屏蔽电极 88 应该彼此分开，以防止它们彼此短路。因此，像素电极 190 离数据线 171 足够远，从而使它们之间的寄生电容减少。此外，由于液晶层 3 的介电常数高于钝化层 180 的介电常数，所以当没有屏蔽电极 88 时，数据线 171 与屏蔽电极 88 之间的寄生电容小于数据线 171 与共电极 270 之间的寄生电容。

此外，由于像素电极 190 和屏蔽电极形成于同一层上，它们之间的距离相等，因此它们之间的寄生电容基本上恒定。为了使开口率的缩小最小化，优选地使屏蔽电极 88 与像素电极 190 之间的距离最小化。

然而，当必要时，可以省略该屏蔽电极 88。

接触辅助件 81a、81b、和 82 分别通过接触孔 181a、181b、和 182 连接至栅极线 121a 和 121b 的端部（端子）129a 和 129b 以及数据线 171 的端部（端子）179。接触辅助件 81a、81b、和 82 用于增加栅极线 121a 和 121b 的端部（端子）129a 和 129b 与数据线 171 的暴露端部（端子）179 和外部器件之间的附着性，并用于保护它们。

在像素电极 190、屏蔽电极 88、接触辅助件 81a、81b、和 82、以及钝化层 180 上形成对准层 11，用于排列液晶层 3。对准层 11 可以是水平对准层。

下面将参照图 5 至图 8 详细说明第二基板（上面板）200。

挡光件 220 用于防止光的泄漏，其称之为黑底 (black matrix)，形成于用透明玻璃制成的绝缘基板 210 上。挡光件 220 具有多个形状相同和位置的开口部作为像素电极 190。可选地，挡光件 220 可形成于与数据线 171 相对应的部分之上，和形成于与薄膜晶体管 Qa 和 Qb 相对应的部分之上。然而，挡光件 220 可形成为各种形状，以防止像素电极 190 和薄膜晶体管 Qa 和 Qb 周围光的泄漏。

在绝缘基板 210 上形成多个滤色器 230。滤色器 230 大部分设置于挡光件 220 的开口部分（被挡光件围绕的区域）内，它们垂直地且纵向地沿着像素电极 190 延伸。滤色器 230 可表现三原色红、绿、和蓝中的一种。

在滤色器 230 之上和在挡光件 220 之上形成透明覆盖层 250，以防止滤色器 230 露出，以及提供平坦的表面。

在覆盖层 250 上用透明导电材料例如 ITO 和 IZO 形成共电极 270。

如图 5 所示，共电极 270 包括多组切口 73、74、75a、75b、76a、和 76b。

切口组 73-76b 面向一个像素电极 190，它们包括：中间切口 73 和 74，上部切口 75a 和 76a、以及下部切口 75b 和 76b。如图 6 所示，切口 73-76b 位于像素电极 190 的相邻切口 92-95c 之间，并位于像素电极 190 的角部与外围电极 95a-95c 之间。此外，各个切口 73-76b 包括至少一个平行于像素电极 190 的切口 92-95c 而延伸的倾斜部分。

上部和下部切口 75a-76b 包括：从像素电极 190 的右边延伸向其底边或顶边的倾斜部分，以及水平部分和垂直部分，其从倾斜部

分的各个端部沿着像素电极 190 的各条边延伸，同时与这些边相重叠并与倾斜部分成钝角。

第一中间切口 73 包括：一对倾斜部分，其从存储电极 133 倾斜地延伸向像素电极 190 的左边；以及垂直端部，其从倾斜部分的端部沿着像素电极 190 的左边延伸，同时与像素电极 190 的左边相重叠并与倾斜部分成钝角。第二中间切口 74 包括：垂直部分，其沿着像素电极 190 的右边延伸，同时被重叠在它们之间；一对倾斜部分，其从垂直部分的各个端部延伸向像素电极 190 的左边；以及垂直端部，其从倾斜部分的端部沿着子像素电极 190b 的左边延伸，同时与左边相重叠并与倾斜部分成钝角。

在切口 73-76b 的倾斜部分处形成三角形凹口。这些凹口可以形成为矩形、梯形、或半圆形形状，或者它们可以是凹形或者凸形的。这些凹口确定了位于对应于切口 73-76b 的局部边界处的液晶分子 3 的排列。

切口 73-76b 的数量可以根据设计因素而变化，挡光件 220 可以与切口 73-76b 相重叠，以防止切口 73-76b 周围光的泄漏。

由于向共电极 270 和屏蔽电极 88 施加相同的共电压，所以在这些电极之间不存在电场。因此，设置于共电极 270 与屏蔽电极 88 之间的液晶分子持续地保持其初始的垂直排列状态，入射至它的光被阻截。

在共电极 270 和覆盖 250 上形成对准层 21，以排列液晶层 3。对准层 21 可以是水平对准层。

在面板 100 和 200 的外表面上设置偏光器 12 和 22，典型地，这两个偏光片 12 和 22 的光透射轴相互垂直。这两个偏光器 12 和

**22** 的光透射轴（或者其光吸收轴）中的一个沿水平方向行进。当是反射型 LCD 时，可以省去这两个偏光器 **12** 和 **22** 中的一个。

液晶层 **3** 可具有负介电各向异性（negative dielectric anisotropy），液晶层 **3** 的液晶分子不施加电压（无电场）时可以相对于两个面板的表面垂直地排列。

当向共电极 **270** 施加共电压并向像素电极 **190** 施加数据电压时，在面板 **100** 与 **200** 之间的液晶层 **3** 上产生电场。电极 **190** 和 **270** 的切口 **92-95c** 和 **73-76b** 使该电场变形，并在切口 **92-95c** 与 **73-76b** 的侧（边）之间产生电场分量。

因此，该电场局部地相对于面板 **100** 和 **200** 的表面之上和之间的方向倾斜。因而，液晶分子响应于该变形电场而排列，使得其指向矢（director）沿向该变形电场。此时，围绕像素电极 **190** 的切口 **92-95c** 和 **73-76c** 以及多条边而形成的电场不是平行于液晶分子的指向矢而延伸，而是相对于指向矢倾斜预定的角度。因此，液晶分子以短运动距离的方向在液晶分子与电场之间的平面上旋转。从而，像素电极 **190** 的一组切口 **92-95c** 和 **73-76b** 以及多条边将设置于像素电极 **190** 上的液晶层 **3** 部分划分成多个区域，其中，液晶分子的倾斜方向彼此不同，因此使得参考视角扩大了。

可以用突起部或凹陷部代替至少一个切口 **92-95c** 和 **73-76b**，切口 **92-95c** 和 **73-76b** 的形状和排布可以改变。

下面将更详细地说明根据第一实施例的 LCD 的显示操作。

信号控制器 **600**（从外部图形控制器中，未示出）接收输入图像（彩色图像数据）信号 R、G 和 B 以及用于控制其显示的输入控制信号，例如垂直同步信号 Vsync、水平同步信号 Hsync、主时钟信号 MCLK、以及数据启动信号 DE。信号控制器 **600** 按照液晶面

板组件 300 的操作条件，适当地处理图像（彩色图像数据）信号 B、G、和 B。基于输入（彩色图像数据）图像信号 R、G、和 B 以及输入控制信号，信号控制器 600 产生栅极控制信号 CONT1 和数据控制信号 CONT2。信号控制器 600 发送栅极控制信号 CONT1 至栅极驱动器 400，以及发送数据控制信号 CONT2 和处理的图像信号 DAT 至数据驱动器 500。

栅极控制信号 CONT1 包括：扫描启动信号 STV，用于指令开始扫描“栅极导通”电压 Von；以及至少一个时钟信号，由于控制“栅极导通”电压 Von 的输出。

数据控制信号 CONT2 包括：水平同步启动信号 STH，用于向一行像素行通知数据发送；装载信号 LOAD，用于将相关数据电压施加于数据线 D1-Dm；以及数据时钟信号 HCLK。数据控制信号 CONT2 可包括反转信号 RVS，用于将数据电压相对于共电压 Vcom 的极性（以下称之为“数据电压的极性”）反转。

数据驱动器 500 根据来自于信号控制器 600 的数据控制信号 CONT2，接收用于一对子像素 PXa 和 PXb 的图像数据 DAT，并从来自于灰度电压发生器 800 的两组灰度电压中选择一组灰度电压。数据驱动器 500 还从所选组的灰度电压中选择对应于各个图像数据 DAT 的灰度电压，然后适当地将图像数据 DAT 转换成数据电压，以将它们发送至相关数据线 D1-Dm。

可选地，分离的外部选择电路（未示出）可从两组灰度电压中选择一组灰度电压，然后将它们发送至数据驱动器 500。此外，灰度电压发生器 800 可提供值变的参考电压，并且数据驱动器 500 可分解该参考电压，以生成灰度电压。

栅极驱动器 400 根据来自于信号控制器 600 的栅极控制信号 CONT1，将“栅极导通”电压施加于栅极线 G1a-Gnb，以导通连接至栅极线 G1a-Gnb 的开关元件 Qa 和 Qb，从而，将施加于数据线 D1-Dm 的数据电压经由导通的开关元件 Qa 和 Qb 施加于相关子像素 PXa 和 PXb。

施加于子像素 PXa 和 PXb 的数据电压与共电压 Vcom 之间的差异表现为液晶电容器  $C_{LC}$  的充电电压，即，表现为像素电压。液晶分子根据像素电压的大小取向，从而使通过液晶层 3 的光的偏振性改变。该偏振性变化通过附着至基板（面板）100 和 200 的偏振器（未示出）而表现为透光率的变化。

上述的两组灰度电压显示不同的伽马曲线（gamma curve），由于将其施加于两个子像素 PXa 和 PXb，所以一个像素 PX 的伽马曲线变成了它们的混合曲线。当确定了两组灰度电压时，使产生的混合伽马曲线更接近正面参考伽马曲线。例如，使正面混合伽马曲线对应于最优确定的正面参考伽马曲线，使产生的侧面混合伽马曲线最接近正面参考伽马曲线。这样，可增强侧面可视性。

如前面描述过的，可使创建的第二子像素电极 190b 的接收较高电压的区域小于第一子像素电极 190a 的该区域，以减少侧面伽马曲线的变形。例如，当第一子像素电极 190a 比第二子像素电极 190b 的面积比为 2:1 时，侧面伽马曲线变得接近于正面伽马曲线，从而可增强侧面可视性。

数据驱动器 500 和栅极驱动器 400 以 1/2 水平周期（或 1/2H，水平同步信号 Hsync 的半个周期）重复该同一操作。这样，将“栅极导通”电压依次地逐行地施加于一帧的所有栅极线 G1a-Gnb，从而将数据电压施加于所有像素 PX。当一帧终止时，下一帧开始，控制施加于数据驱动器 500 的反转信号，以使施加于对应像素 PX

的数据电压的极性与前一帧中的极性相反（“帧反转”）。此时，可根据反转信号 RVS 在一帧内平稳的特性将流过一条数据线的数据电压的极性反转（例如，行反转或点反转），或可使同时流过相邻数据线的数据电压的极性彼此相反（例如，列反转或点反转）。

同时，如图 3 所示，由于当将“栅极导通”电压 Von 转换成“栅极关断”电压 Voff 时开关元件 Q 的控制端和输出端之间的寄生电容 Cgd 导致的耦合，使得产生由下面的等式 1 限定的反冲电压（kickback voltage）V<sub>k</sub>，并降低施加于像素电极 PE 的电压。

### 等式 1

$$V_k = \frac{C_{gd}}{C_{LC} + C_{ST} + C_{gd}} \Delta V_g$$

其中， $\Delta V_g$  是“栅极导通”电压 Von 与“栅极关断”电压 Voff 之间的电压差。

对于根据本发明的第一实施例的 LCD，第一和第二子像素电极 PXa 和 PXb 的反冲电压 V<sub>ka</sub> 和 V<sub>kb</sub> 的大小基本上相同。第一和第二子像素电极 PXa 和 PXb 的液晶电容器 C<sub>LCa</sub> 和 C<sub>LCb</sub> 的电容值取决于第一子像素电极 190a 比第二子像素电极 190b 的面积比，寄生电容 C<sub>gda</sub> 和 C<sub>gdb</sub> 也取决于该设计因素。因此，适当地控制第一和第二漏电极 175a 和 175b 与存储电极 133 相重叠的面积，以使产生的第一和第二存储电容 C<sub>STA</sub> 和 C<sub>STB</sub> 的电容值能够使得反冲电压 V<sub>ka</sub> 和 V<sub>kb</sub> 相等。另外，可使施加于第一和第二子像素电极 PXa 和 PXb 的栅极信号互不相同。例如，使多个“栅极导通”电压的大小不相同，以控制  $\Delta V_g$  的值，从而使反冲电压 V<sub>ka</sub> 和 V<sub>kb</sub> 的大小相等。这样，将第一和第二子像素 PXa 和 PXb 的反冲电压 V<sub>ka</sub> 和 V<sub>kb</sub> 的大小控制为相等，从而防止显示屏闪烁。

下面将参照图 9 和图 10 详细说明根据本发明的第二实施例的 LCD。

图 9 是根据本发明的第二实施例的 LCD 的框图，图 10 是图 9 的根据本发明的第二实施例的 LCD 的像素 (PX) 的等效电路图。

根据本发明的第二实施例的 LCD 包括：液晶面板组件 301；连接至液晶面板组件 301 的栅极驱动器 403 和数据驱动器 501；连接至数据驱动器 501 的灰度电压发生器 801；以及用于控制它们的信号控制器 601。

液晶面板组件 301 包括：多条显示信号线 G1-Gn 和 D1-D2m；以及连接至这些信号线并排布成矩阵形式的多个（一个阵列的）像素 PX。

显示信号线 (G1-Gn, 和数据线 D1-D2m) 包括：多条栅极线 G1-Gn，用于发送栅极信号至像素 PX；以及多条数据线 D1-D2m，用于发送数据信号至像素 PX。栅极线 G1-Gn 沿基本上彼此平行的像素行方向（水平地）延伸，而数据线 D1-D2m 沿基本上彼此平行的像素列方向（垂直地）延伸。数据线 D1-D2m 设置于每列中每个像素 PX 的两边。除了栅极线 G1-Gn 和数据线 D1-D2m 之外，显示信号线还可包括平行于栅极线 G1-Gn 延伸的存储电极线。

图 10 示出了一个像素 PX 和连接至该像素的显示信号线的等效电路图。连接至每个像素 PX 的显示信号线包括标记为 GL 的栅极线、标记为 DL<sub>a</sub> 和 DL<sub>b</sub> 的数据线、以及平行于栅极线 GL 延伸的存储电极线 SL。

各像素 PX 中的每一个均包括一对子像素 PX<sub>c</sub> 和 PX<sub>d</sub>。各子像素 PX<sub>c</sub> 和 PX<sub>d</sub> 包括：开关元件 Q<sub>c</sub> 和 Q<sub>d</sub>，其连接至共用栅极线 GL

并连接至数据线 DL<sub>a</sub> 和 DL<sub>b</sub>，以及连接至液晶电容器 C<sub>LCc</sub> 和 C<sub>LCd</sub> 和连接至它们的存储电容器 C<sub>STc</sub> 和 C<sub>STD</sub>。

各子像素 PX<sub>c</sub> 和 PX<sub>d</sub> 基本上相同于图 3 中所示的各子像素，因此这里不再赘述。

灰度电压发生器 801 产生两组与子像素 PX<sub>c</sub> 和 PX<sub>d</sub> 的透光率相关的灰度电压。两组灰度电压中的一组相对于共电压是正值，另一组是负值。

栅极驱动器 403 连接至液晶面板组件 301 的栅极线 G<sub>1-Gn</sub>，以将来自于外部的“栅极导通”和“栅极关断”电压 V<sub>on</sub> 和 V<sub>off</sub> 施加于栅极线 G<sub>1-Gn</sub>。

数据驱动器 501 连接至液晶面板组件 301 的数据线 D<sub>1-D2m</sub>，以从灰度电压发生器 801 中选择灰度电压，然后将它们施加于每个像素 PX 的子像素 PX<sub>c</sub> 和 PX<sub>d</sub> 作为数据信号。

信号控制器 601 控制栅极驱动器 403 和数据驱动器 501 的操作。

下面将参照图 11 和图 12 详细说明液晶面板组件 301 的结构。

图 11 是根据本发明的第二实施例（图 9）的液晶面板组件 301 中的各像素 PX 的平面图，图 12 是图 11 的液晶面板组件 301 中的像素 PX 取剖线 XII-XII 的剖视图。

如图 11 和图 12 所示，液晶面板组件包括：第一基板（下面板）101；第二基板（上面板）201，面向第一基板（下面板）101；以及液晶层 3，设置于这些基板（面板 101 和 201）之间。

首先来详细说明第一基板（下面板）101。

在（例如，由透明玻璃制成的）绝缘基板 110 上形成多条栅极线 121 和多条存储电极线 131a。

栅极线 121 水平地延伸并彼此分开，它们发送栅极信号。每条栅极线 121 包括：多个突起，其形成多个栅电极 124c 和 124d；以及宽端部 129，用于与其他层或外部器件连接。

每条存储电极线 131a 水平地延伸，并包括多个形成存储电极 133a 和 133b 的突起。存储电极 133a 和 133b 相对于存储电极线 131a 为矩形形状对称。第一存储电极 133a 的面积大于第二存储电极 133b 的面积。

由硅氮化物（SiNx）在栅极线 121 之上和在存储电极线 131a 之上形成栅极绝缘层 140。

在栅极绝缘层 140 上由氢化非晶硅或多晶硅形成多个半导体岛 154c、154d、156b、和 157b。在栅电极 124c 和 124d 上分别形成半导体岛 154c 和 154d。

在半导体岛 154c、154d、156b、和 157b 上，由硅化物或其中以高浓度掺杂 n 型杂质例如磷的 n+氢化非晶硅形成多个欧姆接触 163c、163d、165c、165d、166b、和 167。在第一和第二半导体岛 154c 和 154d 上设置一对第一和第三欧姆接触 163c 和 163d 以及一对第二和第四欧姆接触 163d 和 165d，以及在第三和第四半导体岛 156b 和 157b 上设置第五和第六欧姆接触 166b 和 167。

在栅极绝缘层 140 和欧姆接触 163c、163d、165c、165d、166b、和 167 上形成与这些数据线分离的多条数据线 171a 和 171b 以及多个漏电极 175c 和 175d。

数据线 171a 和 171b 垂直地延伸, 越过栅极线 121 和存储电极线 131, 以发送数据电压。数据线 171a 和 171b 包括多个延伸向栅电极 124c 和 124d 的源电极 173c 和 173d, 以及宽度扩大的端部 179a 和 179b, 以与其他层或与外部器件进行连接。

第一和第二漏电极 175c 和 175d 与数据线 171a 和 171b 分开, 分别面向围绕着栅电极 124c 和 124d 的源电极 173c 和 173d。第一和第二漏电极 175c 和 175d 具有设置于半导体岛 154c 和 154d 上的条带状端部, 并具有宽区域延长部 177c 和 177d, 其分别从条带状端部伸出, 并与存储电极 133a 和 133b 相重叠。条带状端部被 U 形源电极 173c 和 173d 部分地围绕。第二漏电极 175d 的延长部 177d 的面积比第一漏电极 175c 的延长部 177c 的面积小。

第一和第二薄膜晶体管 Qc 和 Qd 由以下形成: 第一和第二栅电极 124c 和 124d、第一和第二源电极 173c 和 173d、以及第一和第二漏电极 175c 和 175d 与半导体岛 154c 和 154d。薄膜晶体管 Qc 和 Qd 的通道分别形成于第一和第二源电极 173c 和 173d 与第一和第二漏电极 175c 和 175d 之间的半导体岛 154c 和 154d 处。

欧姆接触 163c、163d、165c、165d、166b、和 167 仅位于下层半导体岛 154c、154d、156b、和 157b 与上层数据线 171a 和 171b 和漏电极 175c 和 175d 之间, 以降低接触电阻。岛形的半导体岛 154c 和 154d 具有透过源电极 173c 和 173d 以及漏电极 175c 和 175d 暴露的部分。半导体岛 156b 和 157b 使栅极线 121 以及存储电极线 131a 的表面轮廓光滑, 从而防止数据线 171a 和 171b 和漏电极 175c 和 175d 被切割。

在数据线 171a 和 171b、漏电极 175c 和 175d、以及半导体岛 154c 和 154d 的暴露部分上形成钝化层 180。

在钝化层 180 处形成多个接触孔 185c、185d、182a、和 182b，以使它们分别暴露漏电极 175c 和 175d 的延长部 177c 和 177d，以及数据线 171a 和 171b 的端部（端子）179a 和 179b。在钝化层 180 和栅极绝缘层 140 处形成多个接触孔 181，以使它们暴露栅极线 121 的端部（端子）129。

在钝化层 180 上形成多个具有第一和第二子像素电极 191a 和 191b 的像素电极 191、屏蔽电极 88b、以及多个接触辅助件 81、82a、和 82b。第一和第二子像素电极 191a 和 191b 通过接触孔 185c 和 185d 物理连接且电连接至第一和第二漏电极 175c 和 175d，以接收来自于第一和第二漏电极 175c 和 175d 的数据电压。将相对于一个输入图像（数据）信号不同的预定数据电压施加于每对子像素电极 191a 和 191b，并且其大小取决于子像素电极 191a 和 191b 的大小和形状。此外，子像素电极 191a 和 191b 的面积可互不相同。例如，第二子像素电极 191b 可以接收比施加于第一子像素电极 191a 的电压高的电压，且面积可小于第一子像素电极 191a。

子像素电极 191a 和 191b 收到数据电压，同时共电极 270 产生电场，该电场确定两个电极 191 和 270 之间的液晶层的液晶分子的排列。

正如前面说明过的，各子像素电极 191a 和 191b 与共电极 270 形成液晶电容器  $C_{LCc}$  和  $C_{LCD}$ ，以在薄膜晶体管  $Qc$  和  $Qd$  关断之后维持施加电压平稳。通过将第一和第二子像素电极 191a 和 191b 以及与其连接的漏电极 175c 和 175d 的延长部 177c 和 177d 与存储电极 133a 和 133b 相重叠，以将存储电容器  $C_{STc}$  和  $C_{STD}$  与液晶电容器  $C_{LCc}$  和  $C_{LCD}$  并联连接，以增强电压存储能力。

由于第一子像素电极 191a 面积比第二子像素电极 191b 大，所以第一液晶电容器  $C_{LCc}$  的电容大于第二液晶电容器  $C_{LCD}$  的电容。

由于存储电极 133a 和与其重叠的第一漏电极 175c 的延长部 177c 在面积上大于存储电极 133b 和与其重叠的第二漏电极 175d 的延长部 177d, 所以第一存储电容器  $C_{STc}$  的电容大于第二存储电容器  $C_{STD}$  的电容。因此, 第一薄膜晶体管  $Q_c$  的电流驱动能力应该大于第二薄膜晶体管  $Q_d$  的电流驱动能力, 因此第一薄膜晶体管  $Q_c$  的 W/L 值可以高于第二薄膜晶体管  $Q_d$  的 W/L 值。

形成一个像素电极 191 的一对第一和第二子像素电极 191a 和 191b 彼此结合, 同时在它们之间插有间隙 93, 像素电极 191 的外形基本上为矩形形状。第二子像素电极 191b 形状为旋转的等边梯形, 具有梯形凹陷底部。第二子像素电极 191b 基本上被第一子像素电极 191a 围绕。第一子像素电极 191a 由彼此的左边相连接的上部梯形、下部梯形、以及中间梯形形成。第一子像素电极 191a 的中间梯形填充入第二子像素电极 191b 的凹陷底部。第一和第二子像素电极 191a 和 191b 之间的间隙 93 包括: 两对相对于栅极线 121a 和 121b 倾斜 45° 的上和下倾斜部, 并具有基本上相等的宽度; 以及三个宽度基本上相等的垂直部分。为了方便说明, 间隙 93 也可称之为切口。

第一子像素电极 191a 具有切口 96a、96b、97a、和 97b, 其从上部梯形的顶边和下部梯形的底边延伸向其右边。第一子像素电极 191a 具有沿着存储电极线 131a 延伸的切口 91 和 92a, 切口 91 和 92a 具有沿水平方向从中心伸出的水平部分, 一对相对于存储电极线 131a 倾斜 45° 的腿。第二子像素电极 191b 具有从其左边延伸向右边的切口 94a 和 94b。切口 91、92a、94a、96a、96b、97a、和 97b 相对于存储电极线 131 基本上镜面对称, 并且它们彼此垂直延伸, 同时相对于栅极线 121 倾斜 45°。像素电极 191 的上半部和下半部分别被切口 91-97b 划分成 8 个区域。

屏蔽电极 **88b** 具有沿着数据线 **171a** 和 **171b** 延伸的垂直部分，以及沿着栅极线 **121** 延伸的水平部分。屏蔽电极 **88b** 的垂直部分完全地覆盖数据线 **171a** 和 **171b**，并且其水平部分也完整地覆盖栅极线 **121**。

屏蔽电极 **88b** 屏蔽形成于数据线 **171a** 和 **171b** 与像素电极 **191** 之间以及数据线 **171a** 和 **171b** 与共电极 **270** 之间形成的电场，从而减少像素电极 **191** 的电压失真以及数据线 **171a** 和 **171b** 所发送的数据电压的信号延迟。为了防止像素电极 **191** 与屏蔽电极 **88b** 之间的短路，它们被彼此分开，因此，像素电极 **191** 远离数据线 **171a** 和 **171b**，从而使它们之间的寄生电容减少。

接触辅助件 **81**、**82a**、和 **82b** 分别通过接触孔 **181**、**182a**、和 **182b** 连接至栅极线 **121** 的端部(端子)**129** 以及数据线 **171a** 和 **171b** 的端部(端子)**179a** 和 **179b**。

在像素电极 **191**、接触辅助件 **81**、**82a**、和 **82b**、以及钝化层 **180** 上形成对准层 **11**，用于排列液晶层 **3**。

下面将参照图 11 和图 12 详细说明第二基板(上面板) **201**。

在(例如，用透明玻璃制成的)绝缘基板 **210** 上依次地形成挡光件 **200**、多个滤色器 **230**、覆盖层 **250**、以及共电极 **270**。

共电极 **270** 对应于(重叠于)一个像素的部分包括多组切口 **71**、**72**、**73a**、**74a**、**75c**、**75d**、**76c**、**76d**、**77a**、**77b**、**78a**、和 **78b**。从而，共电极 **270** 具有多组切口 **71-78b**。

切口组 **71-78b** 面向一个像素电极 **191**，并包括：中间切口 **71**、**72**、**73a**、和 **74a**；上部切口 **75c**、**76c**、**77a**、和 **78a**；以及下部切口 **75d**、**76d**、**77b**、和 **78b**。切口 **71-78b** 排布于像素电极 **191** 的左

边的中心处，像素电极 191 的相邻切口 91-97b 之间，并位于外围切口 97a 和 97b 与像素电极 191 的多个角部之间。此外，各个切口 72-78b 包括至少一个平行于像素电极 191 的切口 91-97b 的倾斜部分。

下部和上部切口 75c-78b 包括：从像素电极 191 的右边延伸向其底边或顶边的倾斜部分；以及水平部分和垂直部分，其从倾斜部分的各个端部沿着像素电极 191 的各条边延伸，同时与这些边相重叠并与倾斜部分成钝角。

第一中间切口 71 包括：垂直端部，其沿着像素电极 191 的左边延伸，同时与其相重叠；以及水平部分，其从垂直部分沿着存储电极线 131a 延伸。第二和第三中间切口 72 和 73a 包括：水平部分，其沿着存储电极线 131a 延伸；一对倾斜部分，其从水平部分延伸向像素电极 191 的左边，相对于存储电极线 131a 倾斜；以及垂直端部，其从倾斜部分的端部沿着子像素电极 191 的左边延伸，同时与左边相重叠，并与倾斜部分成钝角。第四中间切口 74a 包括：垂直部分，其沿着像素电极 191 的右边延伸，同时与其相重叠；一对倾斜部分，其从垂直部分的各个端部延伸向像素电极 191 的左边；以及垂直端部，其从倾斜部分的端部沿着第二子像素电极 191b 的左边延伸，同时与左边相重叠，并与倾斜部分成钝角。

在切口 72-77b 的倾斜部分处形成三角形凹口。这些凹口可以形成为矩形、梯形、或半圆形形状，或者它们可以是凹形或者凸形的。

在共电极 270 和覆盖层 250 上形成对准层 21，以排列液晶层 3。

在面板 101 和 201 的外表面上设置偏光器 12 和 22。

根据本发明的 LCD 的显示操作基本上与前面实施例的有关显示操作相同，因此这里不再赘述。

相同于根据第二实施例的 LCD，可将第一和第二子像素 PXc 和 PXd 的反冲电压调节为基本上相同。第一和第二子像素电极 PXc 和 PXd 的液晶电容器  $C_{LCc}$  和  $C_{LCd}$  的电容值取决于第一子像素电极 191a 比第二子像素电极 191b 的面积比，寄生电容  $C_{gda}$  和  $C_{gdb}$  也取决于该设计因素。因此，适当地控制第一和第二漏电极 175a 和 175b 与存储电极 133a 和 133b 相重叠的面积，以使产生的第一和第二存储电容  $C_{STc}$  和  $C_{STD}$  的电容值能够使得反冲电压  $V_{kc}$  和  $V_{kd}$  相等。这样，将第一和第二子像素 PXc 和 PXd 的反冲电压  $V_{kc}$  和  $V_{kd}$  的大小控制至相等，从而防止显示屏闪烁。

此外，使创建的第二子像素电极 191b 接收较高电压的面积小于第一子像素电极 191a 的该面积，从而减少侧面伽马曲线的畸变。例如，可使创建的第一子像素电极 191a 比第二子像素电极 191b 的面积比为约 2:1，从而增强侧面可视性。

图 1 至图 8 所示的 LCD 的很多特征也是图 9 至图 12 所示的 LCD 的特征。

下面将参照图 13 详细说明根据本发明的第三实施例的 LCD 的像素 PX。

图 13 是根据本发明的第三实施例的 LCD 的像素阵列中的像素 PX 的等效电路图。

图 13 示出了显示信号线 (GL、DL、SLa、SLb) 和一个像素 PX 的两个子像素的等效电路图。显示信号线包括：标记为 GL 的栅极线；标记为 DL 的数据线；以及一对第一和第二存储电极线 SLa 和 SLb，其基本上平行于栅极线 GL 而延伸。

各像素 PX 包括一对子像素 PXe 和 PXf。子像素 PXe 和 PXf 分别包括：开关元件 Qe 和 Qf，连接至栅极线 GL 和数据线 DL；液晶电容器  $C_{LCe}$  和  $C_{LCf}$ ，连接至这些开关元件；以及存储电容器  $C_{STe}$  和  $C_{STf}$ ，其连接至开关元件 Qe 和 Qf 以及存储电极线 SLa 和 SLb。

第一和第二存储电极线 SLa 和 SLb 接收第一和第二共电压  $V_{com1}$  和  $V_{com2}$ 。第一和第二共电压  $V_{com1}$  和  $V_{com2}$  在相差  $180^\circ$  的高电压与低电压之间振荡 (swing)。将一个数据电压施加于对应的子像素 PXe，然后通过栅极信号启动该像素，然后对其充电。根据施加于各存储电极线 SLa 和 SLb 的第一和第二共电压  $V_{com1}$  和  $V_{com2}$ ，将子像素 PXe 和 PXf 处充电的像素电压转换成高电压和低电压 (或者低电压和高电压)，使它们彼此产生差异。这样，子像素 PXe 和 PXf 收到不同的像素电压，从而增强了侧面可视性。

在具有根据第三实施例的结构的实施例中，使第一和第二子像素电极 PXe 和 PXf 的反冲电压  $V_{ke}$  和  $V_{kf}$  的大小基本上相等。可以使第一和第二子像素 PXe 和 PXf 的液晶电容器  $C_{LCe}$  和  $C_{LCf}$  的电容值彼此不同，也可根据该设计因素使寄生电容  $C_{gde}$  和  $C_{gdf}$  彼此不同。因此，可适当地将第一和第二存储电容器  $C_{STe}$  和  $C_{STf}$  的电容值控制至使反冲电压  $V_{ke}$  和  $V_{kf}$  的大小相同。这样，将第一和第二子像素 PXe 和 PXf 的反冲电压  $V_{ke}$  和  $V_{kf}$  的大小控制至相等，从而防止显示屏闪烁。

根据本发明的各实施例，将一个像素分成两个子像素，将不同的数据电压分别地施加给 (或提供给 (evolved in)) 这两个子像素，从而增强侧面可视性。此外，两个子像素具有彼此不同的面积大小，从而减少侧面伽马曲线的畸变。例如，可将两个子像素的存储电容设计为使每个子像素的反冲电压相等，从而防止显示图像质量受损例如闪烁。

---

以上所述仅为本发明的优选实施例而已，并不用于限制本发明，对于本领域的技术人员来说，本发明可以有各种更改和变化。凡在本发明的精神和原则之内，所作的任何修改、等同替换、改进等，均应包含在本发明的保护范围之内。

图 1A

图 1B

图 1C

图2

图3

图4

图 5

图6

图 7

图8

图9

图 10

图11

图12

图 13

|                |                                                            |         |            |

|----------------|------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                      |         |            |

| 公开(公告)号        | <a href="#">CN1847964A</a>                                 | 公开(公告)日 | 2006-10-18 |

| 申请号            | CN200610066784.3                                           | 申请日     | 2006-04-13 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                   |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                   |         |            |

| 当前申请(专利权)人(译)  | 三星显示有限公司                                                   |         |            |

| [标]发明人         | 金东奎                                                        |         |            |

| 发明人            | 金东奎                                                        |         |            |

| IPC分类号         | G02F1/136 G02F1/133                                        |         |            |

| CPC分类号         | G02F1/136277 G02F1/136213 G02F1/13624 H01L27/124 H01L27/13 |         |            |

| 代理人(译)         | 李伟                                                         |         |            |

| 优先权            | 1020050030678 2005-04-13 KR                                |         |            |

| 其他公开文献         | CN100573282C                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>             |         |            |

### 摘要(译)

一种液晶显示器包括一个阵列的像素。每个像素分成第一子像素和第二子像素，向这两个子像素分别地施加(提供)不同的数据电压，从而增强侧面可视性。每个子像素包括与子像素的存储电极相重叠的子像素电极(连接至子像素的开关元件的漏电极)。向第一子像素施加第一预定电压，向第二子像素施加第二预定电压，从而使第一子像素电极可接收低于第二子像素电极的电压的电压。第一子像素面积可大于第二子像素电极。第一漏电极与第一子像素的存储电极之间的重叠面积可大于该漏电极与第二子像素的存储电极之间的重叠面积。从而使第一子像素的反冲电压基本上等于第二子像素的反冲电压。