[12] 发明专利说明书

专利号 ZL 02828780.0

[45] 授权公告日 2008 年 4 月 2 日

[11] 授权公告号 CN 100378547C

[22] 申请日 2002.6.21 [21] 申请号 02828780.0

[30] 优先权

[32] 2002.5.9 [33] KR [31] 2002/25535

[86] 国际申请 PCT/KR2002/001187 2002.6.21

[87] 国际公布 WO2003/096113 英 2003.11.20

[85] 进入国家阶段日期 2004.10.19

[73] 专利权人 三星电子株式会社

地址 韩国京畿道

[72] 发明人 田尚益 朴云用

[56] 参考文献

CN 1252532 A 2000.5.10

US 5,608,556 A 1997.3.4

KR 10 - 2001 - 0039261 A 2001.5.15

KR 2001 - 0048491 A 2001.6.15

KR 10 - 0345961 B1 2002.8.1

审查员 钟杰

[74] 专利代理机构 北京市柳沈律师事务所

代理人 李晓舒 魏晓刚

权利要求书 3 页 说明书 15 页 附图 34 页

[54] 发明名称

垂直排列模式的液晶显示装置

[57] 摘要

在第一绝缘基底上形成彼此交叉的多条栅极线和多条数据线，并在由数据行和栅极行限定的各个象素区上形成具有多个第一切口的多个象素电极。薄膜晶体管连结到每个象素电极。在与第一基底相对的第二基底上形成具有多个第二切口的参考电极。在关于一条数据线彼此相对的两个相邻象素区中的第一切口和第二切口具有关于该数据线的镜面对称性。

1. 一种液晶显示器的薄膜晶体管阵列板，其包括：

绝缘基底；

形成在绝缘基底上的栅极线；

形成在栅极线上的栅极绝缘层；

形成在栅极绝缘层上的数据线；

形成在数据线上的钝化层；和

形成在钝化层上并具有多个切口的多个像素电极，

其中，在薄膜晶体管阵列板的俯视图中，关于数据线彼此相对的两个相邻像素电极的切口具有金刚石形状的镜面对称性。

2. 如权利要求 1 所述的薄膜晶体管阵列板，其中，每个像素电极的切口包括基本上在横向延伸以将像素电极分成上、下两个半部的横向切口，以及在斜向延伸并位于像素电极的上下两个半部内的两个斜向切口，斜向切口基本上相互垂直。

3. 如权利要求 1 所述的薄膜晶体管阵列板，还包括多条存储电极布线，该存储电极布线包含平行于栅极线的存储电极线和连接到存储电极线的存储电极。

4. 如权利要求 3 所述的薄膜晶体管阵列板，还包括连接两个关于栅极线彼此相对的相邻存储电极布线的存储桥。

5. 如权利要求 1 所述的薄膜晶体管阵列板，其中，任一个切口相对于任一条平行于数据线的线不具有自身对称性。

6. 一种液晶显示器，包括：

第一绝缘基底；

形成在第一绝缘基底上的多条栅极线；

与栅极线相交并绝缘的多条数据线；

位于由栅极线和数据线限定的各个像素区上的多个像素电极；

多个薄膜晶体管，每个薄膜晶体管具有分别连接到其中一条栅极线、其中一条数据线和其中一个像素电极的栅电极、源电极和漏电极；

与第一绝缘基底相对的第二绝缘基底；

形成在第二绝缘基底上的参考电极；

形成在第一绝缘基底和第二绝缘基底其中之一上的多个第一畴分隔件；和

形成在第一绝缘基底和第二绝缘基底其中之一上的多个第二畴分隔件，

其中，在液晶显示器的俯视图中，关于一条数据线彼此相对的两个相邻像素电极的第一和第二畴分隔件具有金刚石形状的镜面对称性。

7. 如权利要求 6 所述的液晶显示器，其中，像素电极的第一畴分隔件包括多个切口，一个像素电极的所述多个切口包括：基本上在横向延伸、以将像素电极分隔成上、下两个半部的横向切口；以及两个在斜向延伸并位于像素电极的上、下两个半部中的斜向切口，并且斜向切口基本上彼此垂直，和

斜向切口夹置在参考电极的第二畴分隔件之间，每个第二畴分隔件包括平行于斜向切口的斜向部分和与像素电极的边缘重叠的重叠部分。

8. 如权利要求 6 所述的液晶显示器，其中，每个像素电极的第一畴分隔件包括基本上沿像素电极的横向中心线延伸并分叉成倾斜发散的上、下分支的中心切口、以及两个在倾斜方向延伸并分别位于像素电极的上半部和下半部中的两个斜向切口，并且参考电极的第二畴分隔件中的一个夹置在第一畴分隔件的斜向切口之间并包括平行于斜向切口的斜向部分和与至少一个像素电极和至少一个数据线的边缘重叠的重叠部分。

9. 如权利要求 8 所述的液晶显示器，其中，所述重叠部分与其中一条数据线以及关于一条数据线彼此相对的两个相邻像素电极重叠。

10. 如权利要求 6 所述的液晶显示器，其中，第二畴分隔件包括介电突起。

11. 如权利要求 6 所述的液晶显示器，其中，任一个第一和第二畴分隔件相对于平行于数据线的任一条线不具有自身对称性。

12. 一种制造薄膜晶体管板的方法，包括：

形成一条栅极布线，该栅极布线包括多个栅极线，多个连接到栅极线的栅电极和连接到绝缘基底上的栅极线的多个栅极焊点；

形成栅极绝缘层；

形成半导体层；

通过沉积并构图导电材料形成数据布线，该数据布线包括与栅极线相

交的多个数据线，连接到数据线的多个数据焊点，与栅电极相邻的多个源电极和与源电极相对设置的多个漏电极；

形成钝化层；

通过和栅极绝缘层一起构图钝化层而形成多个暴露栅极焊点、数据焊点和漏电极的接触孔；和

通过沉积并构图透明导电层形成功能分别经接触孔连接到栅极焊点、数据焊点和漏电极的多个辅助栅极焊点、多个辅助数据焊点和多个像素电极，

其中，所述像素电极具有至少一个畴分隔件，

其中，在薄膜晶体管板的俯视图中，多个像素电极的形式使得关于其中一个数据线彼此相对的两个相邻像素电极具有金刚石形状的镜面对称性。

13. 如权利要求 12 所述的方法，其中，通过利用光致抗蚀剂图案的一次光刻工艺一起形成数据布线和半导体层，其中光致抗蚀剂图案具有第一部分、薄于第一部分的第二部分以及薄于第二部分的第三部分。

14. 如权利要求 13 所述的方法，其中，第二部分位于其中一个源电极和其中一个漏电极之间，并且在一次光刻工艺中第一部分位于数据布线上。

15. 如权利要求 12 所述的方法，其中，任一个像素电极相对于平行于数据线的任一条线都不具有自身对称性。

## 垂直排列模式的液晶显示装置

### 技术领域

本发明涉及一种垂直排列模式的液晶显示装置，并尤其涉及一种包括带切口的电极以确保宽视角的垂直排列模式的液晶显示装置。

### 背景技术

典型的液晶显示器（“LCD”）包括带有参考电极和彩色滤光片的上基板和带有薄膜晶体管（“TFT”）和像素电极的下基板以及夹置在两基板之间的具有介电各向异性的液晶层，通过对参考电极和像素电极施加不同的电压、以在液晶层中产生电场而显示图像，电场改变液晶分子的取向，从而控制光的透射率。

在这些 LCD 中，垂直排列模式的 LCD（以下称作“VALCD”）由于其较高的对比度和宽视角而具有应用较好前景，在这种 VALCD 中，在没有电场时将其液晶分子的主轴排列成垂直于上下基板。

为了在 VALCD 中实现宽视角，在电极上设置切口图案或凸起。切口和凸起均产生边缘电场以将液晶分子的倾斜方向规律地分布为四个方向，由此增宽视角。

同时，在 LCD 的带有 TFT 的基板（以下称作“TFT 阵列板”）上设置多条信号布线(signal wire)，如传递扫描信号的栅极线(gate line)和传递图像信号的数据线(data line)。这些信号布线有其自身的电阻并与周围的信号布线或上基板的参考电极耦接，产生耦合电容。由各个布线的电阻和电容所致的负载对经信号布线传递的信号产生失真、如 RC 延迟。特别是，数据线和参考电极之间的电容性耦合驱动设置在其间的液晶分子，造成数据线附近的光泄漏，由此衰减图像质量，并且该光泄漏反过来扩大黑色矩阵(black matrix)，降低孔隙比。

### 发明内容

本发明的一个目的在于通过降低数据布线的负载而提高图像质量。

本发明的另一目的在于通过减小数据线和参考电极之间的耦合电容而减少数据线附近的光泄漏。

为了实现上述各项目的，本发明在关于数据线彼此相对的位置处形成具有镜面对称性的切口。

具体地说，提供一种液晶显示器的薄膜晶体管阵列板，其包括：绝缘基底；形成在绝缘基底上的栅极线；形成在栅极线上的栅极绝缘层；形成在栅极绝缘层上的数据线；形成在数据线上的钝化层；和形成在钝化层上并具有多个切口的多个像素电极，其中，关于数据线彼此相对的两个相邻像素电极的切口具有镜面对称性。

优选每个像素电极的切口包括基本上在横向延伸以将像素电极分成上下两半部的横向切口，和在斜向延伸并位于像素电极的上下两半部内的两个斜向切口，斜向切口基本上相互垂直。此外，TFT 阵列板还可以包括多条存储电极布线，该存储电极布线包括平行于栅极线的存储电极线和连接到存储电极线的存储电极，并且 TFT 阵列板还可以包括连接两个关于栅极线彼此相对的相邻存储电极布线的存储桥。

提供了一种液晶显示器，包括：第一绝缘基底；形成在第一绝缘基底上的多条第一布线；与第一布线相交并与之绝缘的多条第二布线；位于由第一布线和第二布线限定的各个像素区上的多个像素电极；多个薄膜晶体管，每个薄膜晶体管具有分别连接到其中一条第一布线、其中一条第二布线和其中一个像素电极上的栅电极、源电极和漏电极；与第一绝缘基底相对的第二绝缘基底；形成在第二绝缘基底上的参考电极；形成在第一绝缘基底和第二绝缘基底其中之一上的多个第一畴分隔件；和形成在第一绝缘基底和第二绝缘基底其中之一上的多个第二畴分隔件，其中，关于一个数据线彼此相对的两个相邻像素电极的第一和第二畴分隔件具有镜面对称性。

优选像素电极的第一畴分隔件包括多个切口，一个像素电极的多个切口包括基本上在横向延伸、以将像素电极分隔成上下两半部的横向切口和两个在斜向延伸并位于像素电极的上下两半部中的两个斜向切口，并且斜向切口基本上彼此垂直。优选斜向切口夹置在参考电极的第二畴分隔件之间，而每个第二畴分隔件包括平行于斜向切口的斜向部分和与像素电极的边缘重叠的重叠部分。优选每个像素电极的第一畴分隔件包括基本上沿象

素电极的横向中心线延伸并分叉成倾斜发散的上、下分支的中心切口；以及两个在倾斜方向延伸并分别位于象素电极的上、下两半部中的两个斜向切口，并且参考电极的第二畴分隔件中的一个夹置在第一畴分隔件的斜向切口之间并包括平行于斜向切口的斜向部分和与至少一个象素电极和至少一个数据线的边缘重叠的重叠部分。优选该重叠部分与其中一个数据线以及关于一个数据线彼此相对的两个相邻象素电极重叠。

制造此种薄膜晶体管板的方法包括：形成一条栅极布线，该栅极布线包括多个栅极线，多个连接到栅极线的栅电极和连接到绝缘基底上的栅极线的多个栅极焊点；形成栅极绝缘层；形成半导体层；通过沉积并构图导电材料形成数据布线，该数据布线包括与栅极线相交的多个数据线，连接到数据线的多个数据焊点，与栅电极相邻的多个源电极和与源电极相对设置的多个漏电极；形成钝化层；通过将钝化层和栅极绝缘层一起构图而形成多个暴露栅极焊点、数据焊点和漏电极的接触孔；和通过沉积并构图透明导体层形成多个辅助栅极焊点、多个辅助数据焊点和多个象素电极，它们分别经接触孔连接到栅极焊点、数据焊点和漏电极，其中，多个象素电极的形式使得关于其中一个数据线彼此相对的相邻两个象素电极基本上镜面对称。

优选通过利用光致抗蚀剂图案的一次光刻工艺一起形成数据布线和半导体层，其中光致抗蚀剂图案具有第一部分、薄于第一部分的第二部分以及薄于第二部分的第三部分。优选第二部分位于其中一个源电极和其中一个漏电极之间，并且在一次光刻工艺中第一部分位于数据布线上。

#### 附图说明

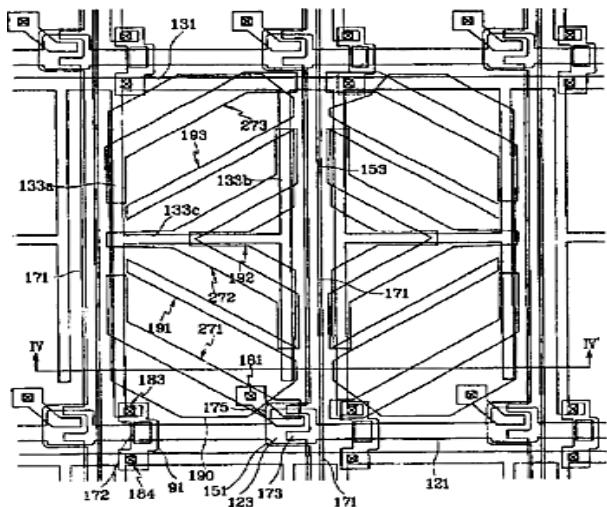

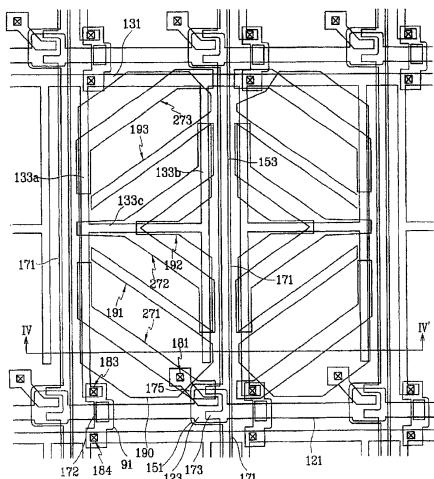

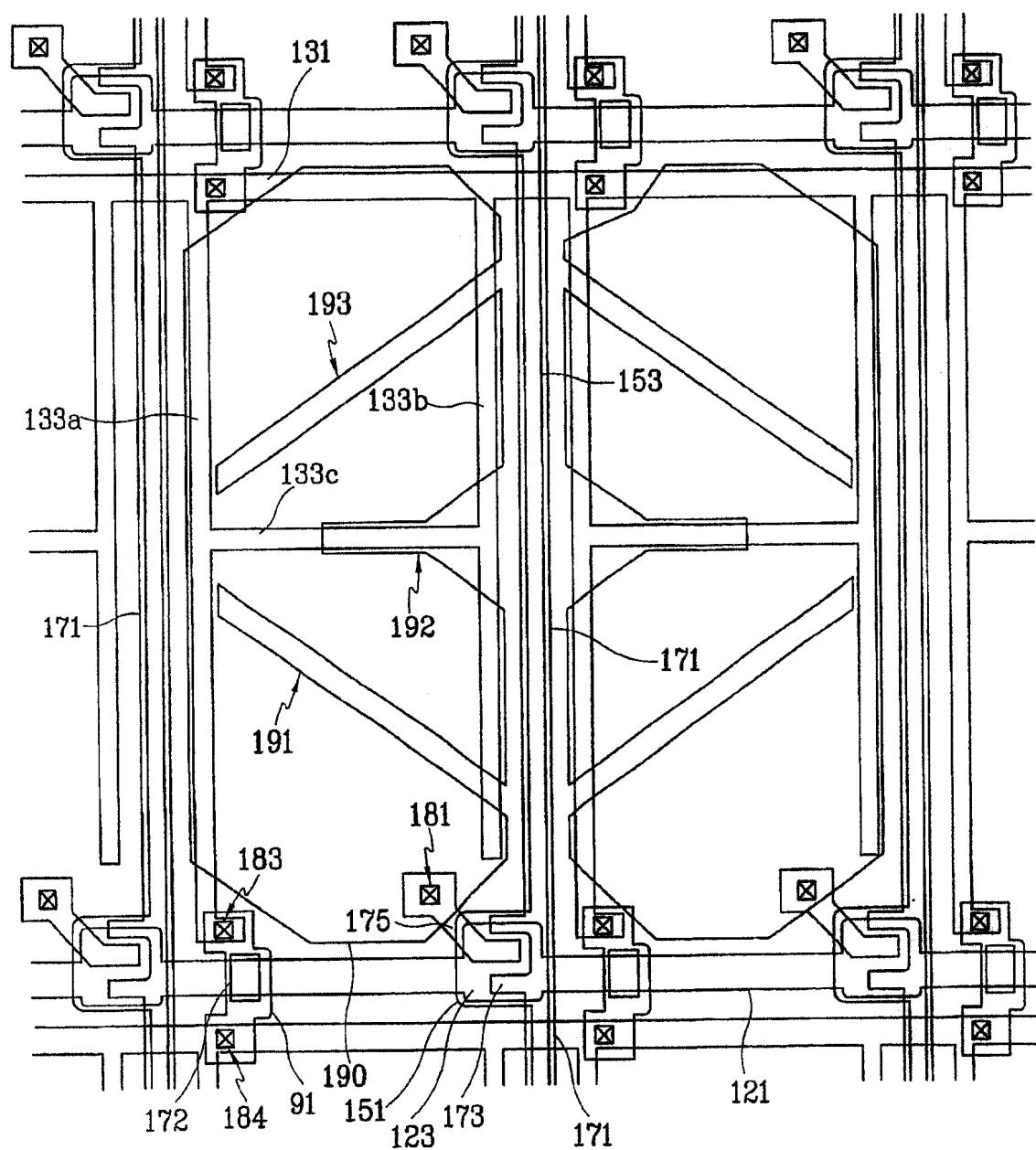

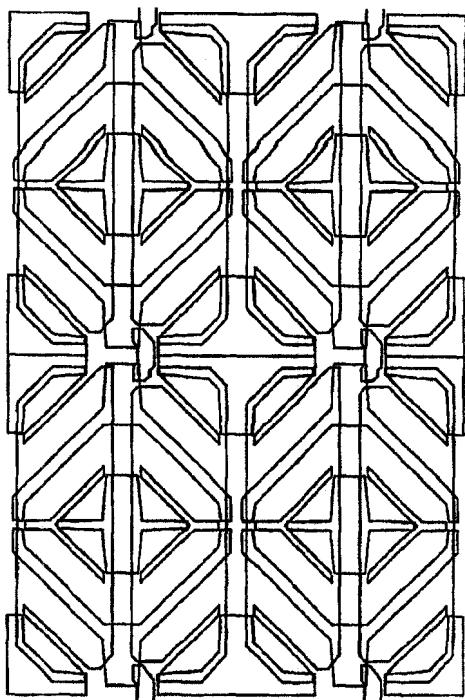

图 1 是根据本发明第一实施例的 LCD 的 TFT 阵列板简图；

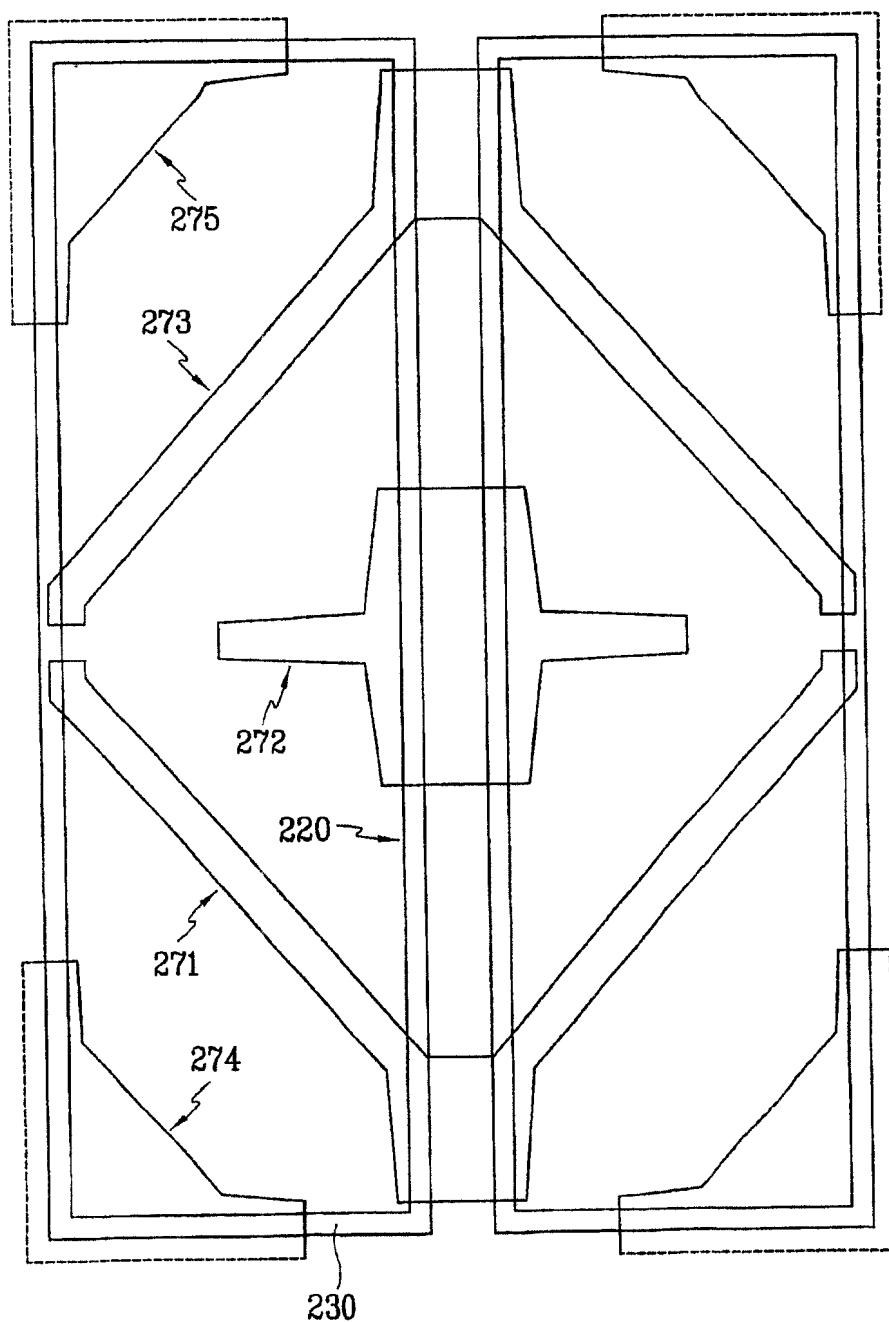

图 2 是根据本发明第一实施例的 LCD 的彩色滤光片板简图；

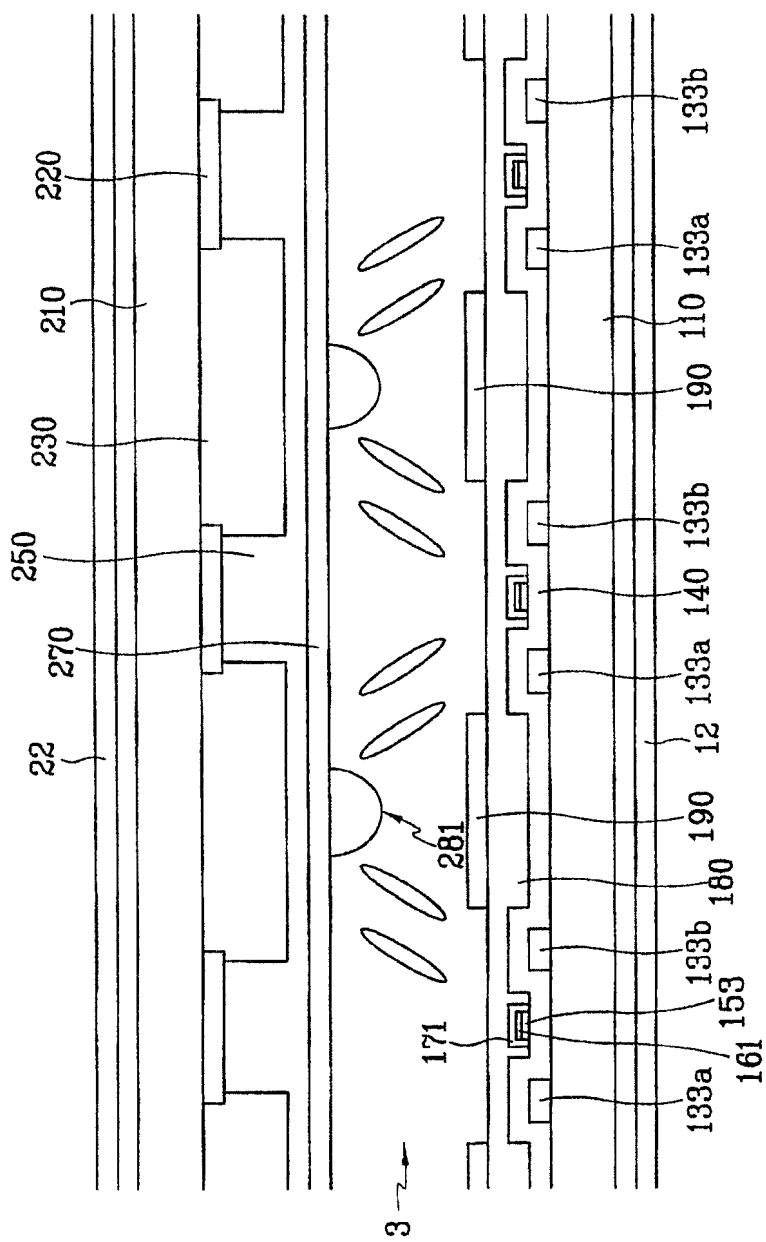

图 3 是根据本发明第一实施例的 LCD 简图；

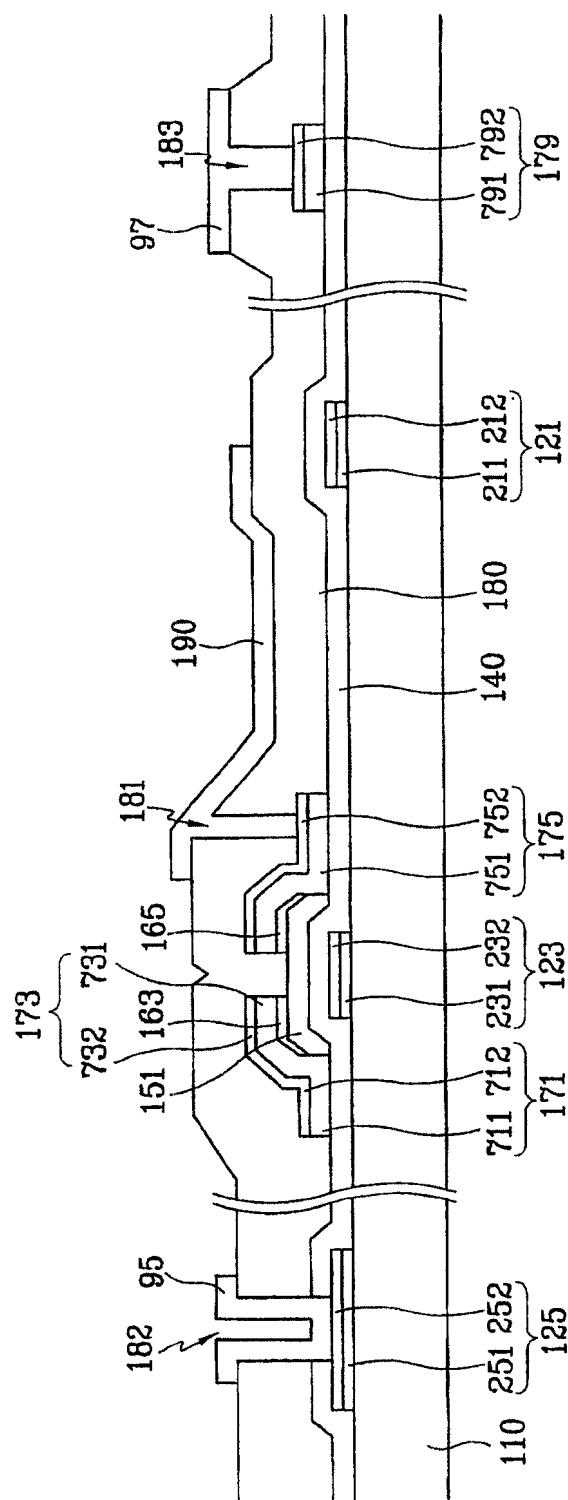

图 4 是沿图 3 中 IV - IV' 线的剖面图；

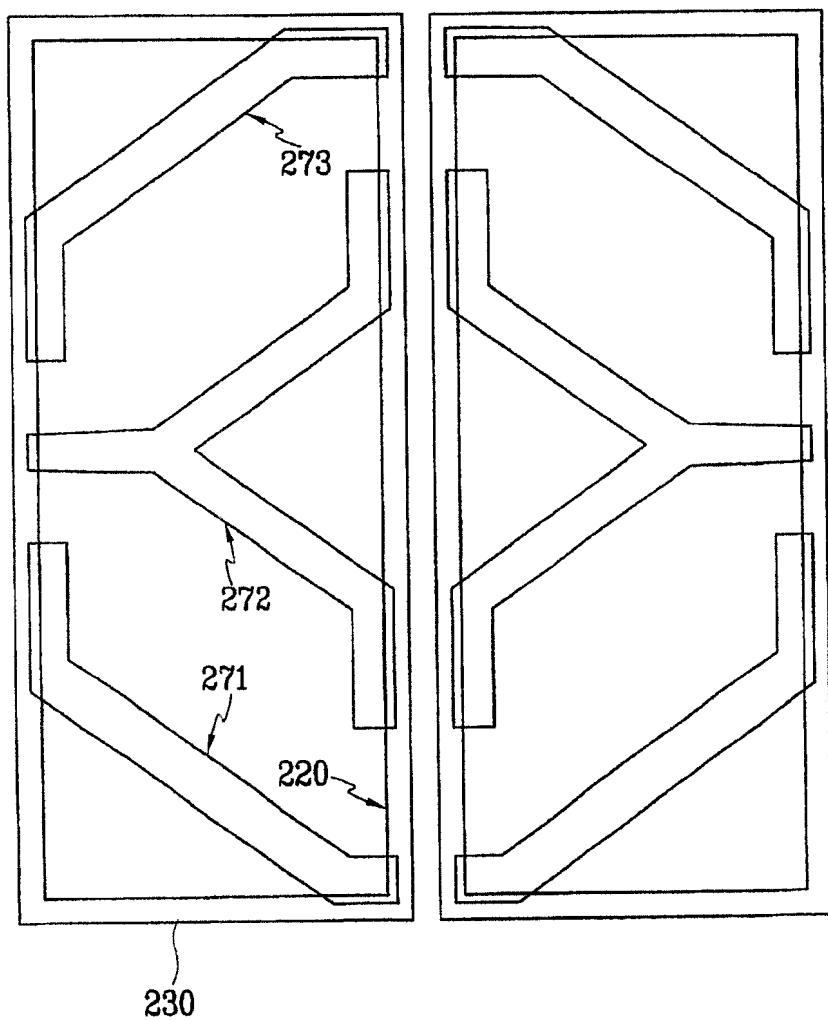

图 5A 是根据本发明第一实施例的 LCD 的象素电极和八个象素 (4 × 2) 的切口的简图；

图 5B 是图 5A 中所示的具有黑色矩阵的简图；

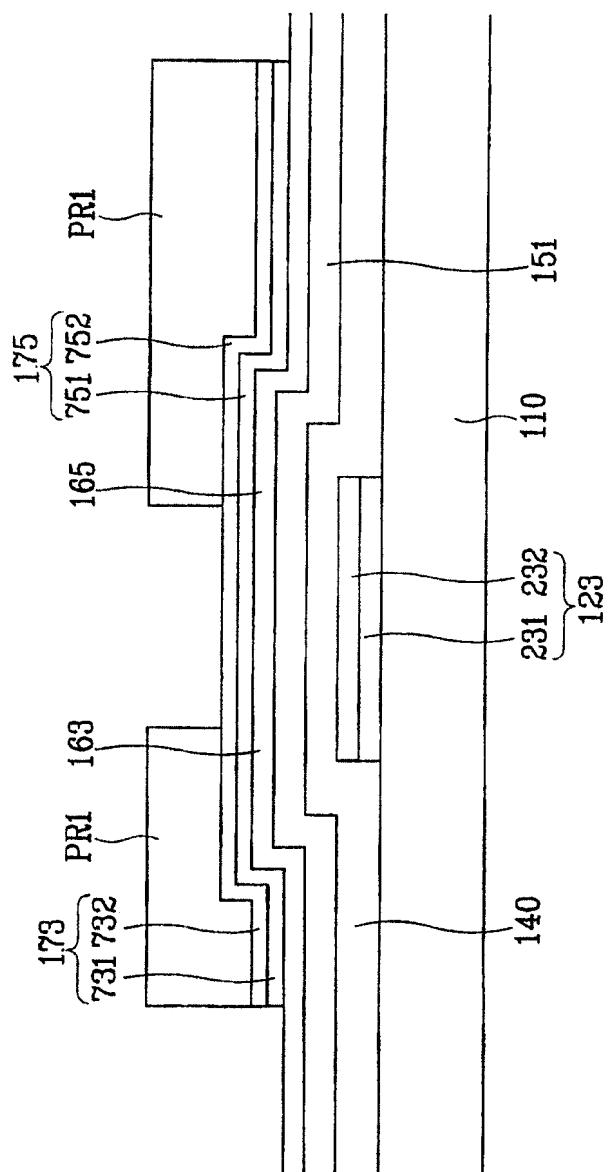

图 6 是根据本发明第二实施例的 LCD 剖面图；

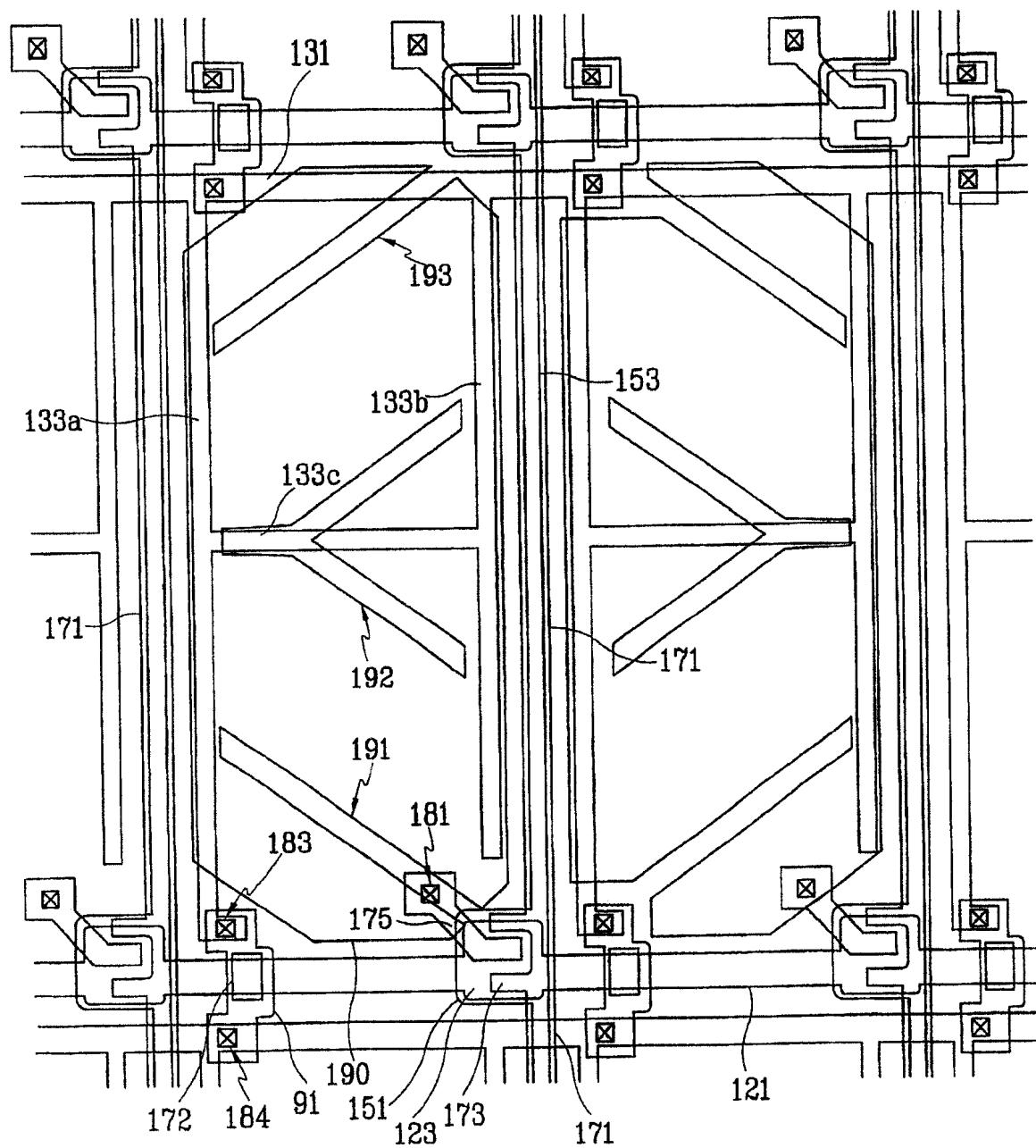

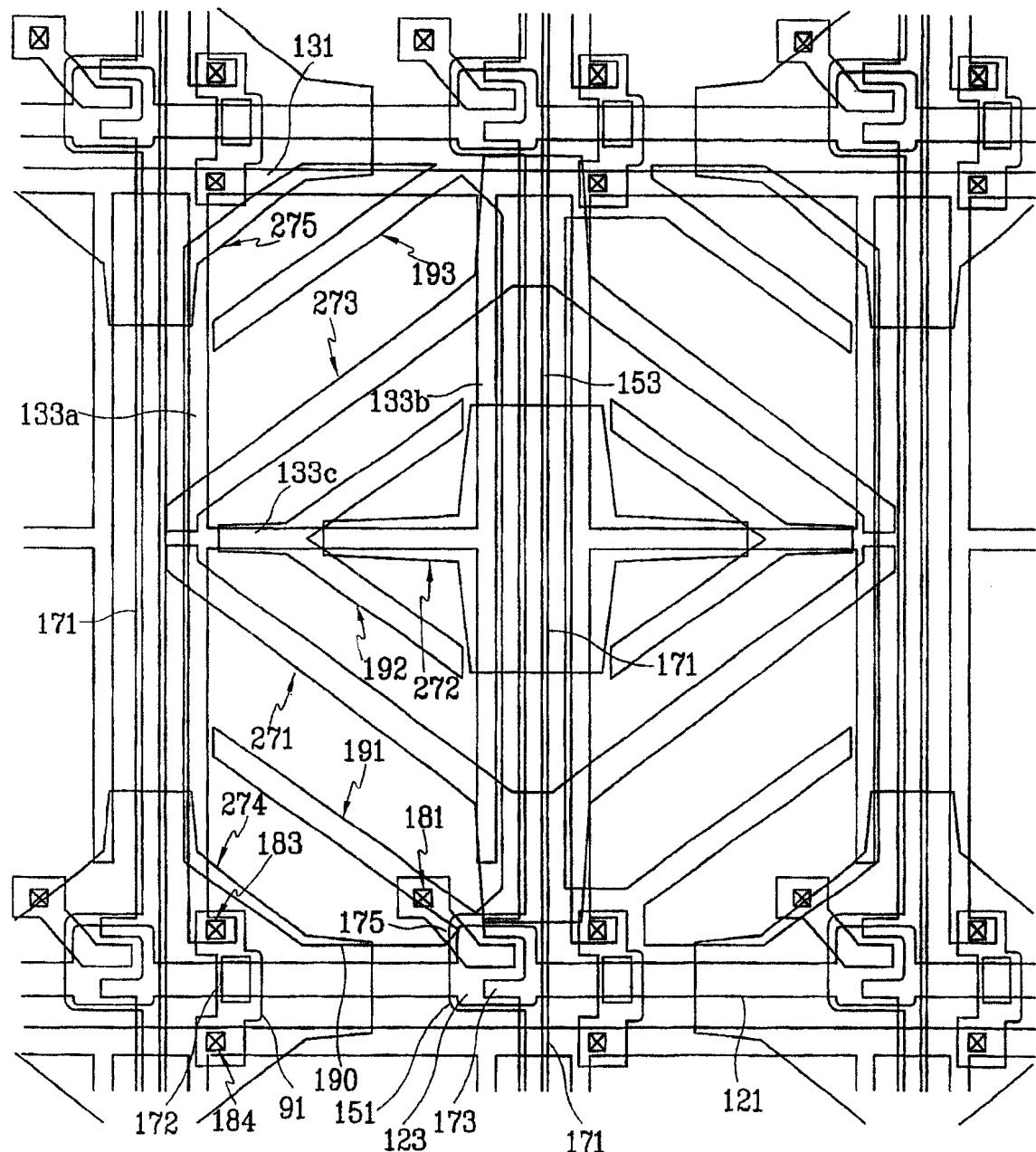

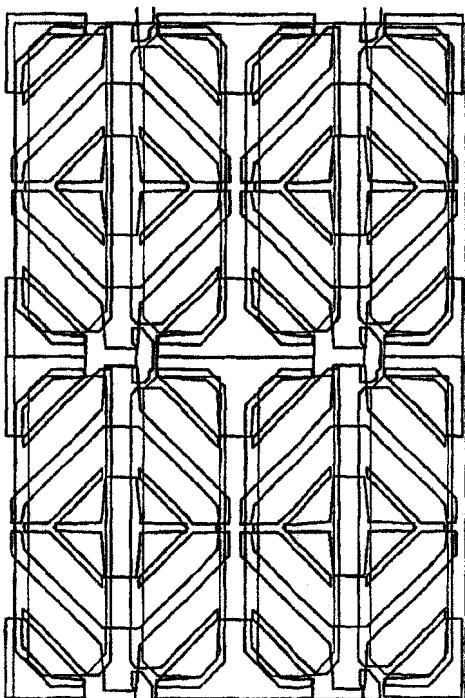

图 7 是根据本发明第三实施例的 LCD 的 TFT 阵列板简图；

图 8 是根据本发明第三实施例的彩色滤光片板简图；

图 9 是根据本发明第三实施例的 LCD 简图；

图 10A 是根据本发明第三实施例的 LCD 的像素电极和八个像素 ( $4 \times 2$ ) 的切口的简图；

图 10B 是图 10A 中所示的具有黑色矩阵的简图；

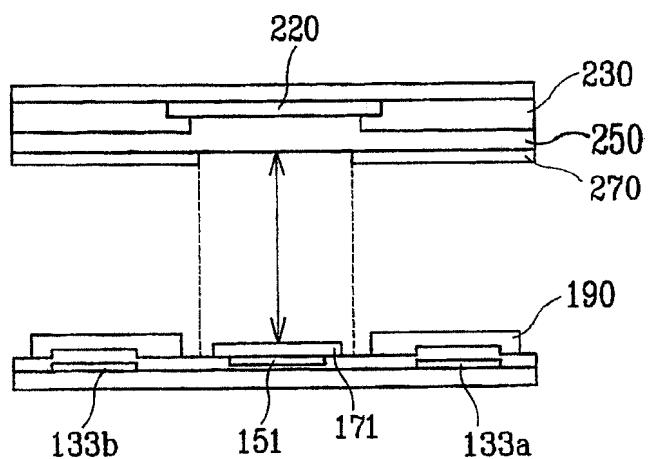

图 11 是表示参考电极的切口和数据线之间重叠的剖面图；

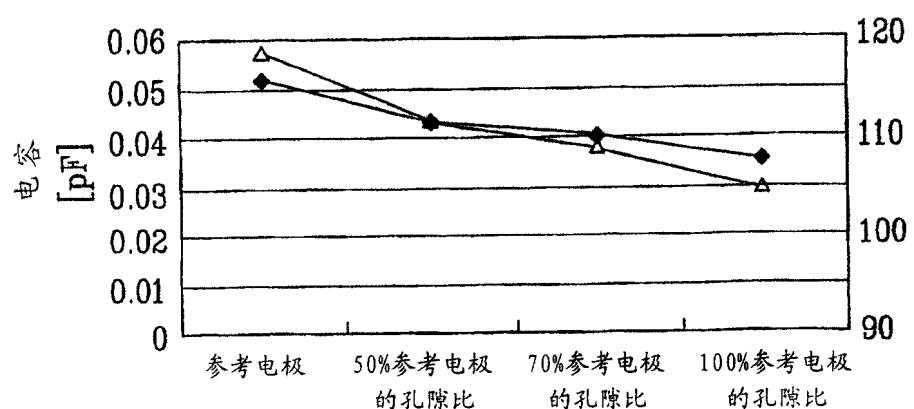

图 12 是作为参考电极的与数据线重叠的部分中去除面积比的函数的施加到数据线的寄生电容曲线；

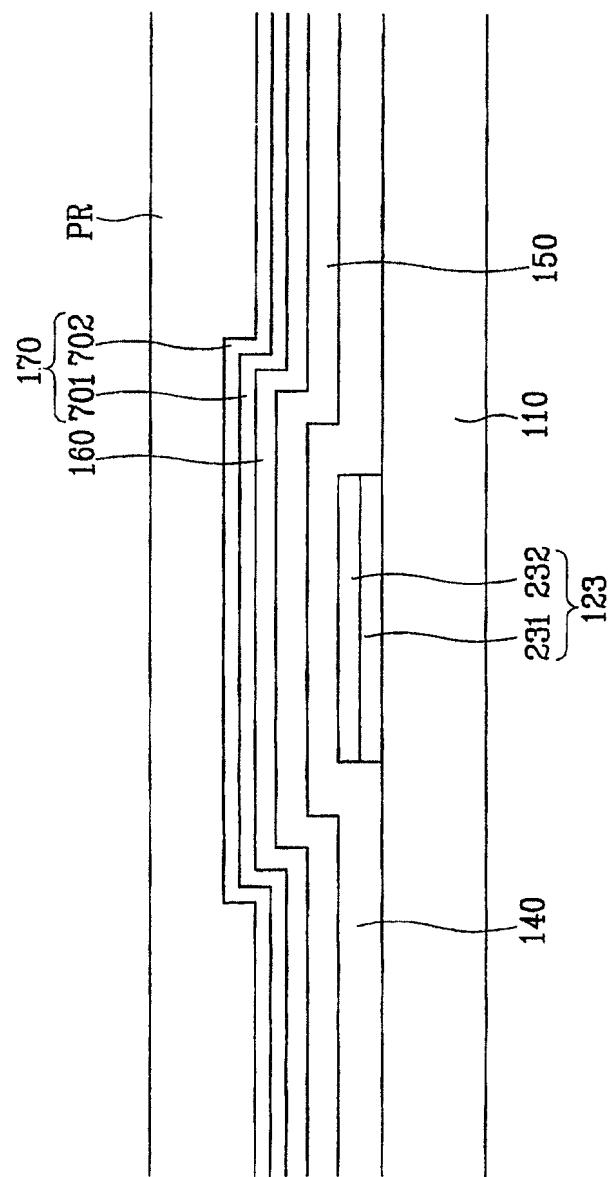

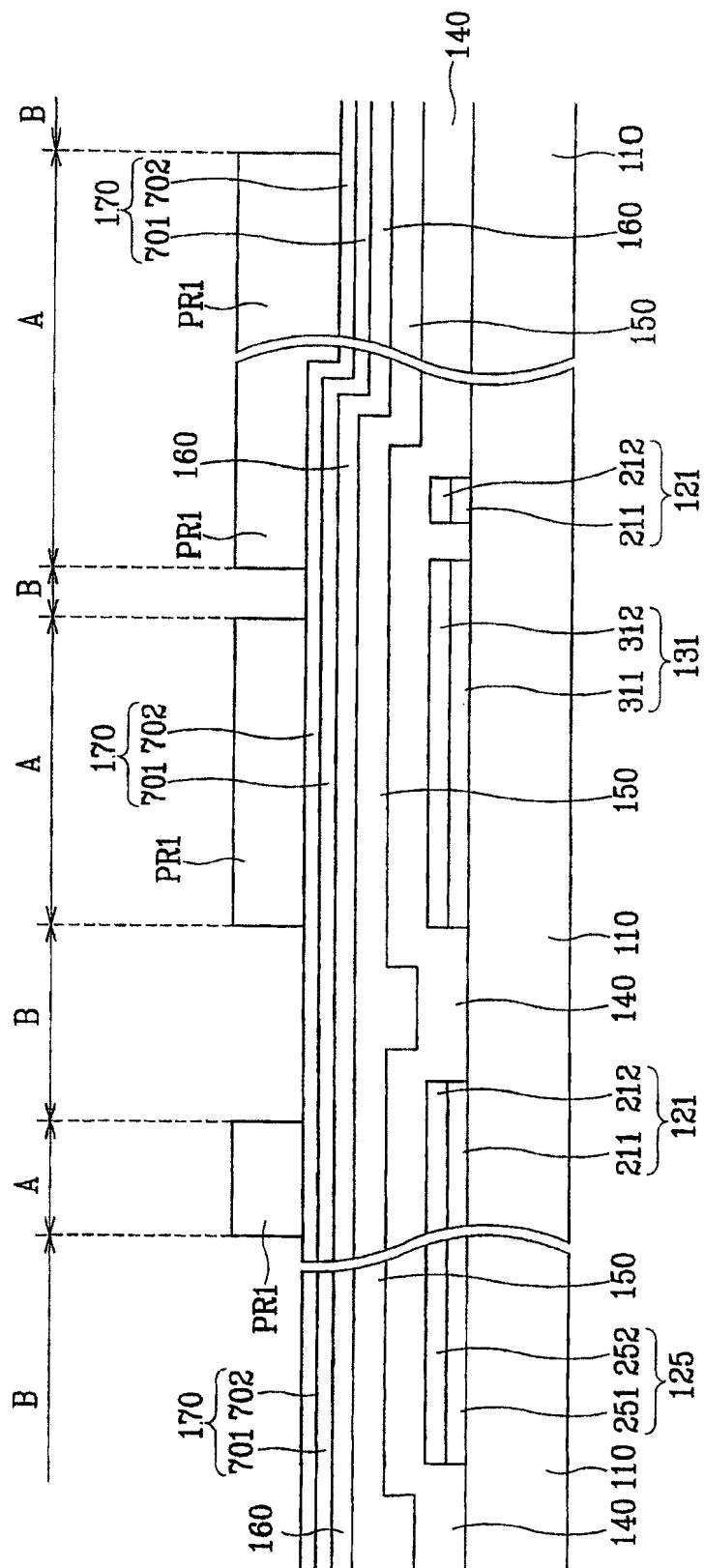

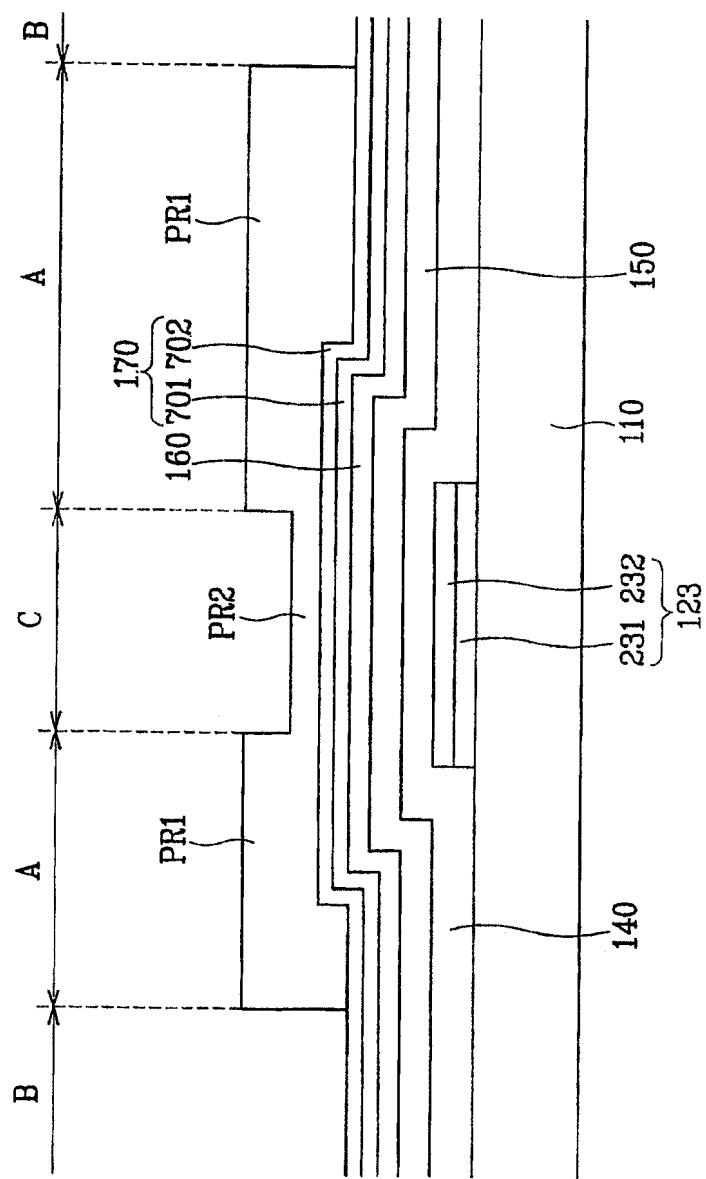

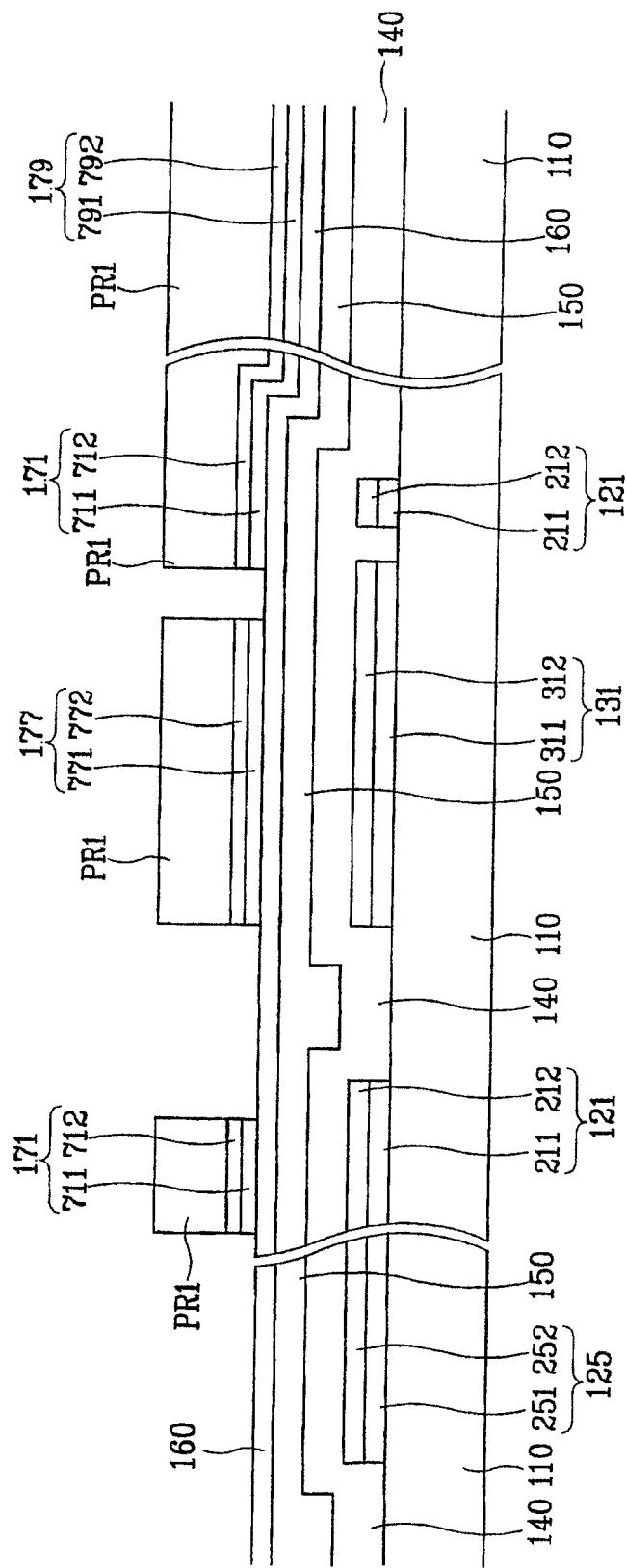

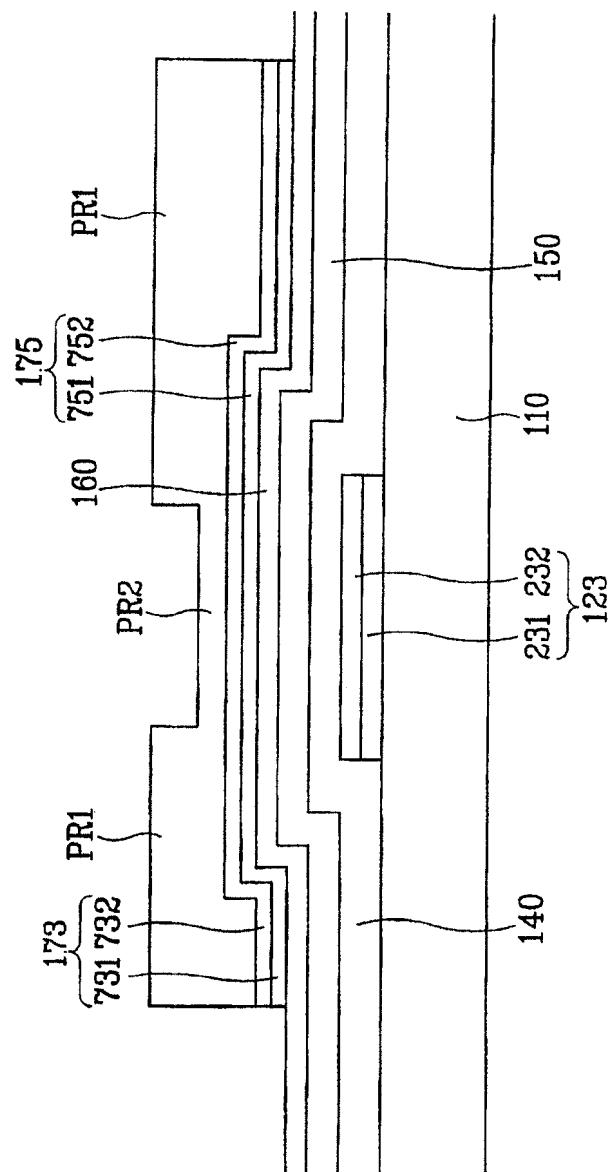

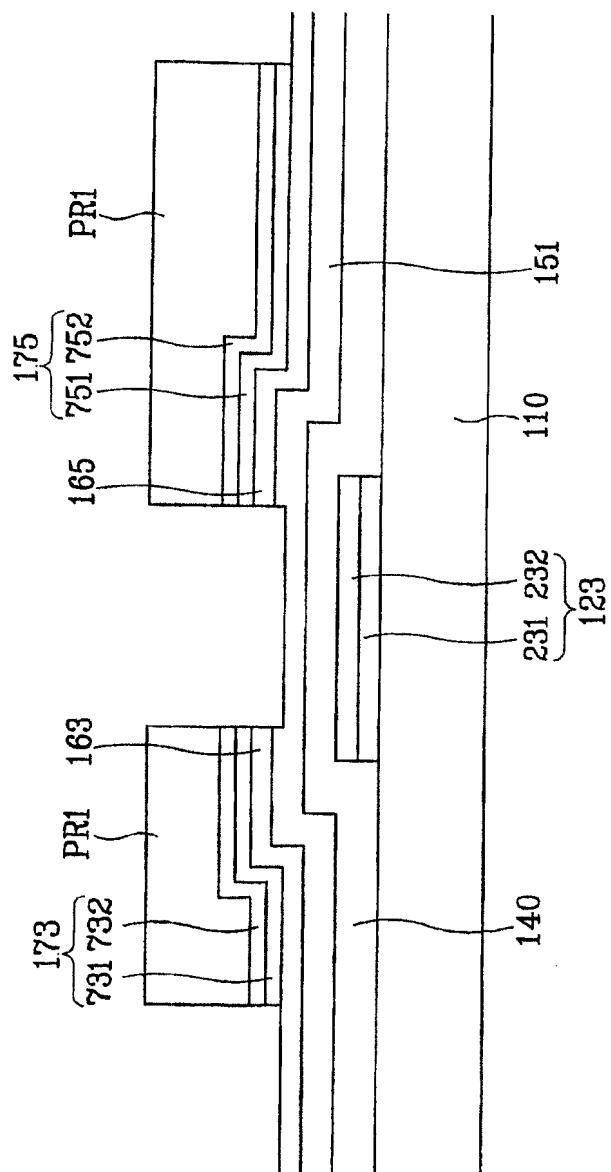

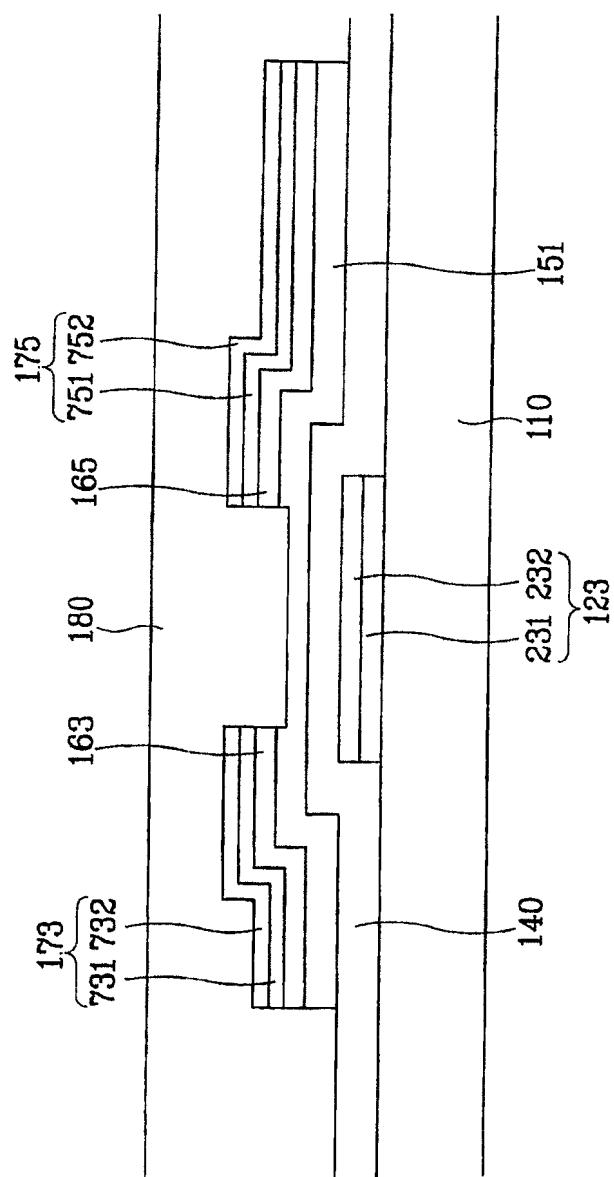

图 13 ~ 17 是依次表示利用五个掩模的制作方法步骤的 LCD 板的 TFT 阵列板剖面图；以及

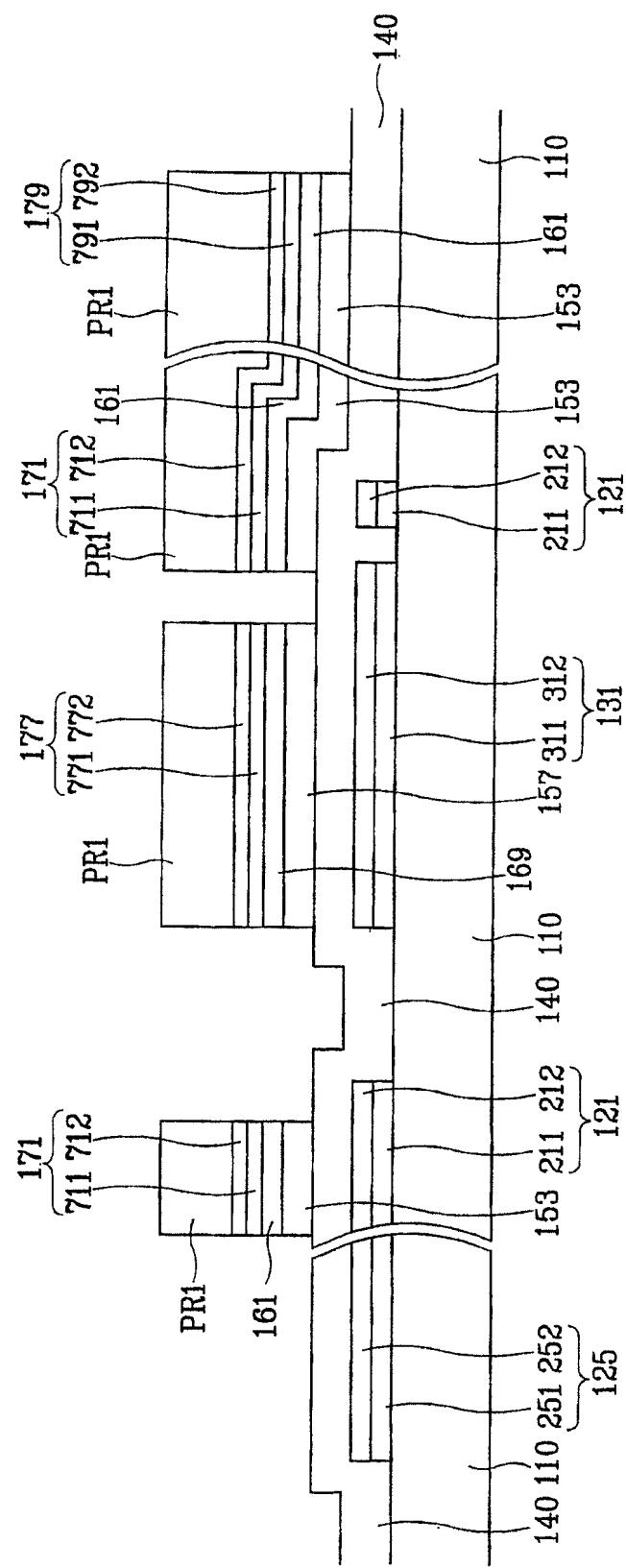

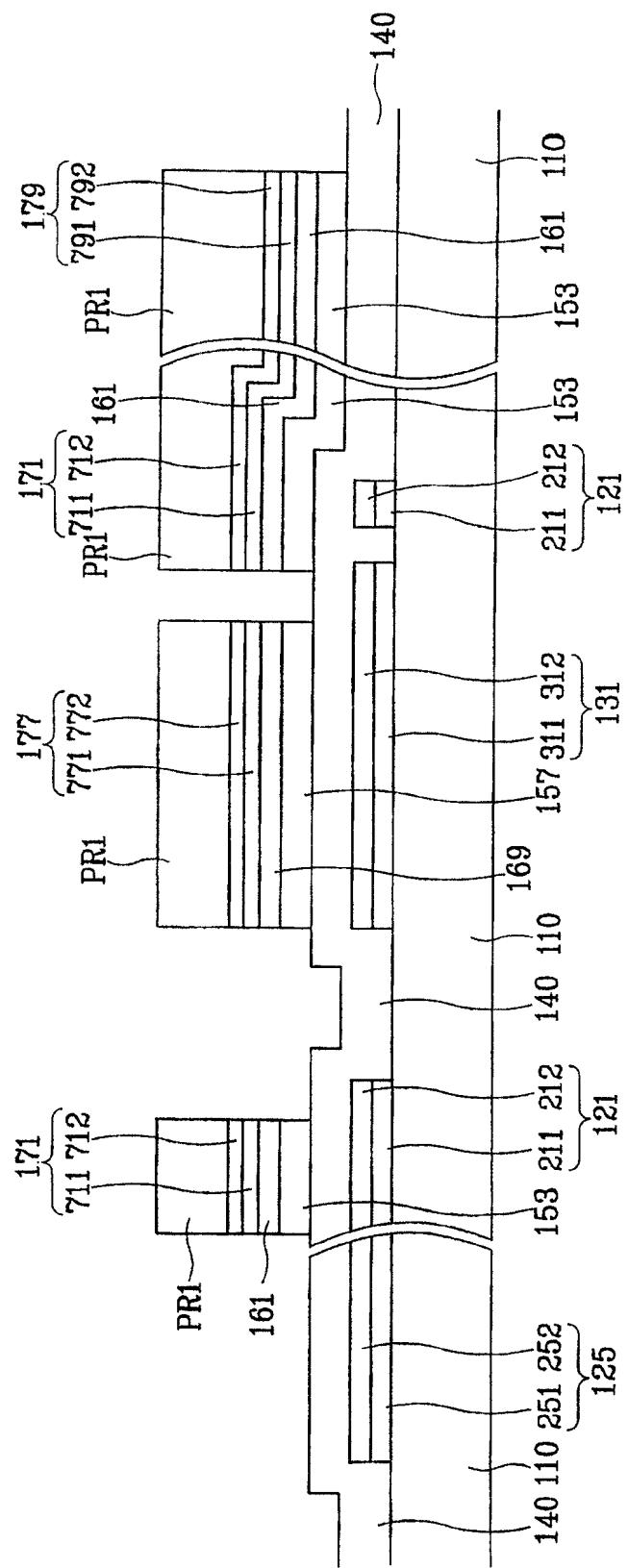

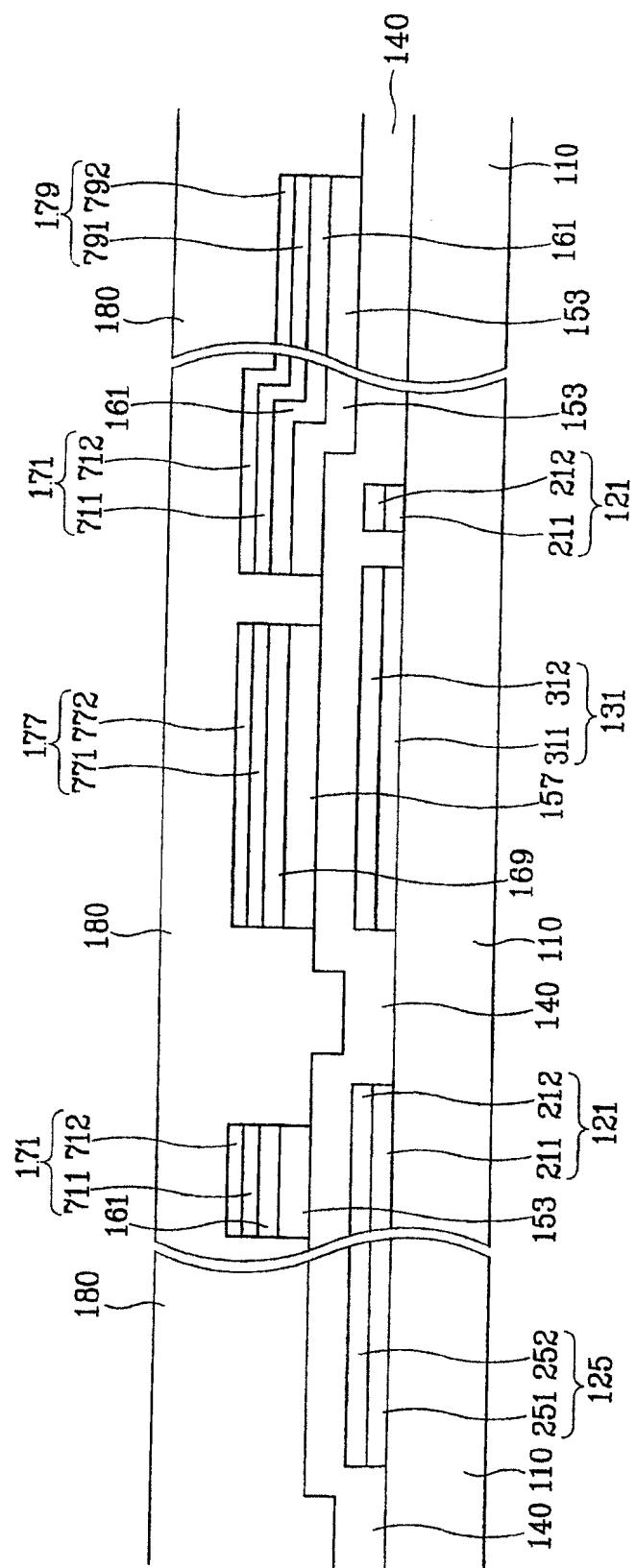

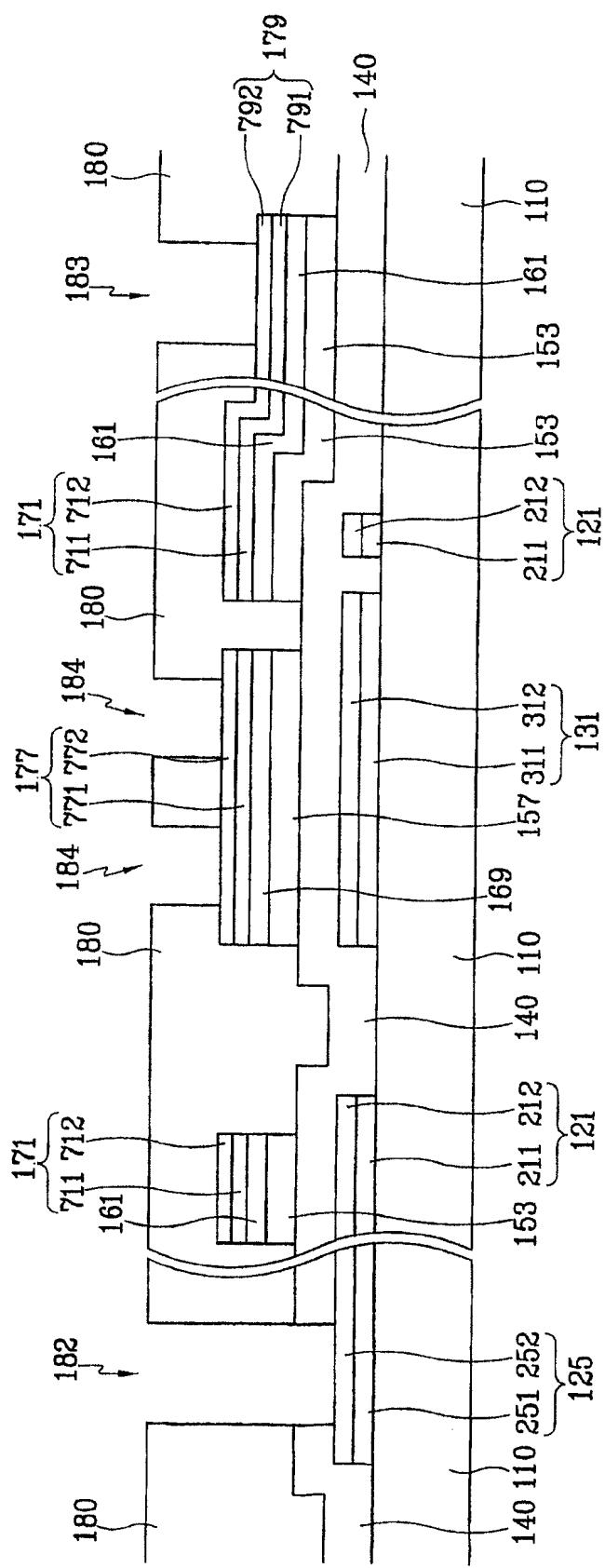

图 18A 和 18B ~ 图 26A 和 26B 是依次表示利用四个掩模的制作方法步骤的 LCD 板的 TFT 阵列板剖面图。

### 具体实施方式

下面通过参考对于本领域技术人员易于实施的附图详细描述本发明的实施例。但本发明可以以不同的形式实施，并应该不限于在此给出的实施例。

附图中，为了清楚起见夸大了层和区域的厚度。在整个附图中用相同的附图标记表示相同的元件。应该知道，当称层、膜、区域、基底或板这些元件处于另一个元件“上”时，可以指直接在其他元件上，也可以是存在中间元件。相反，当称一个元件“直接”处于其他元件上时，则不存在中间元件。

下面参考附图描述根据本发明实施例的液晶显示器的薄膜晶体管阵列板。

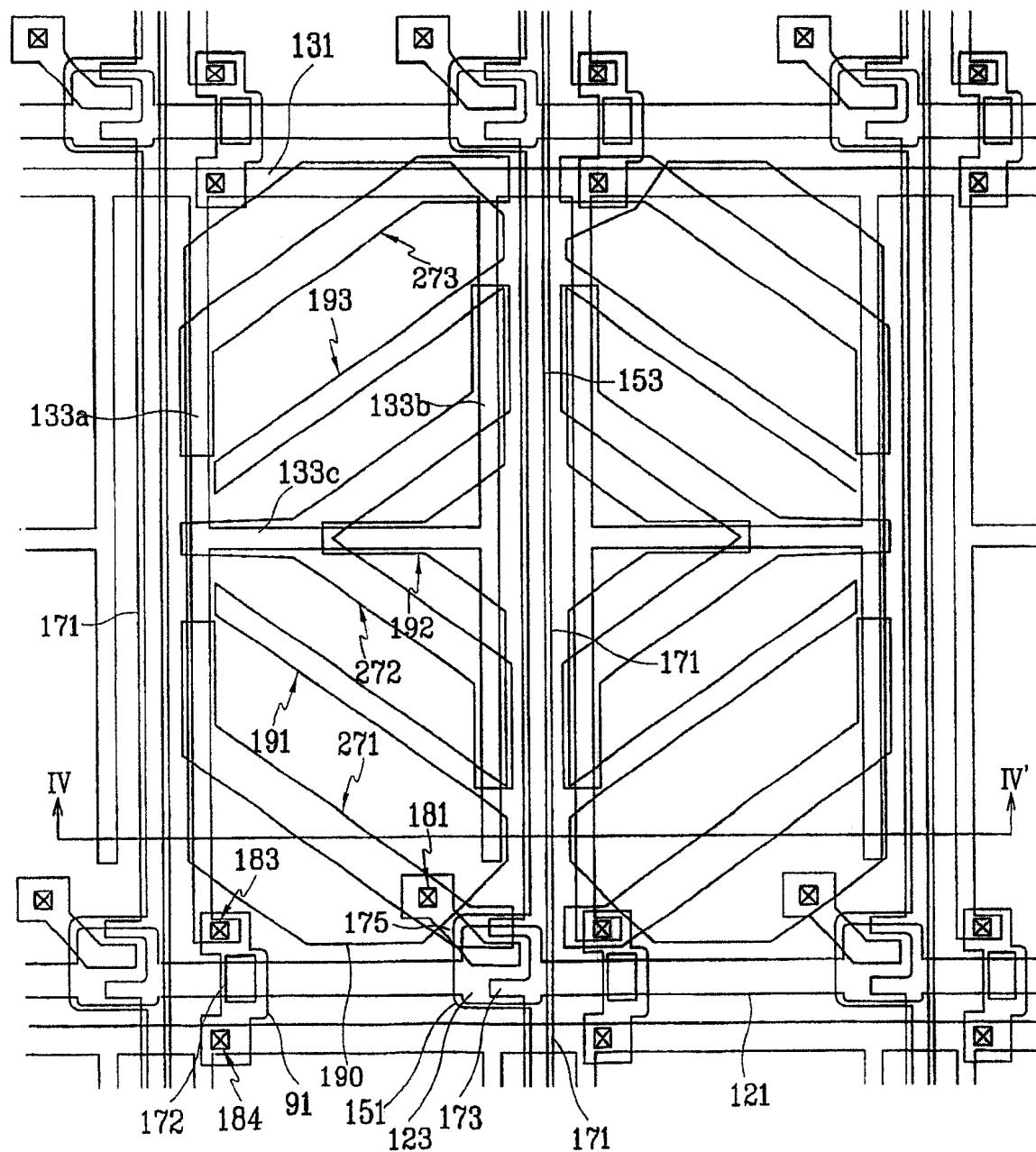

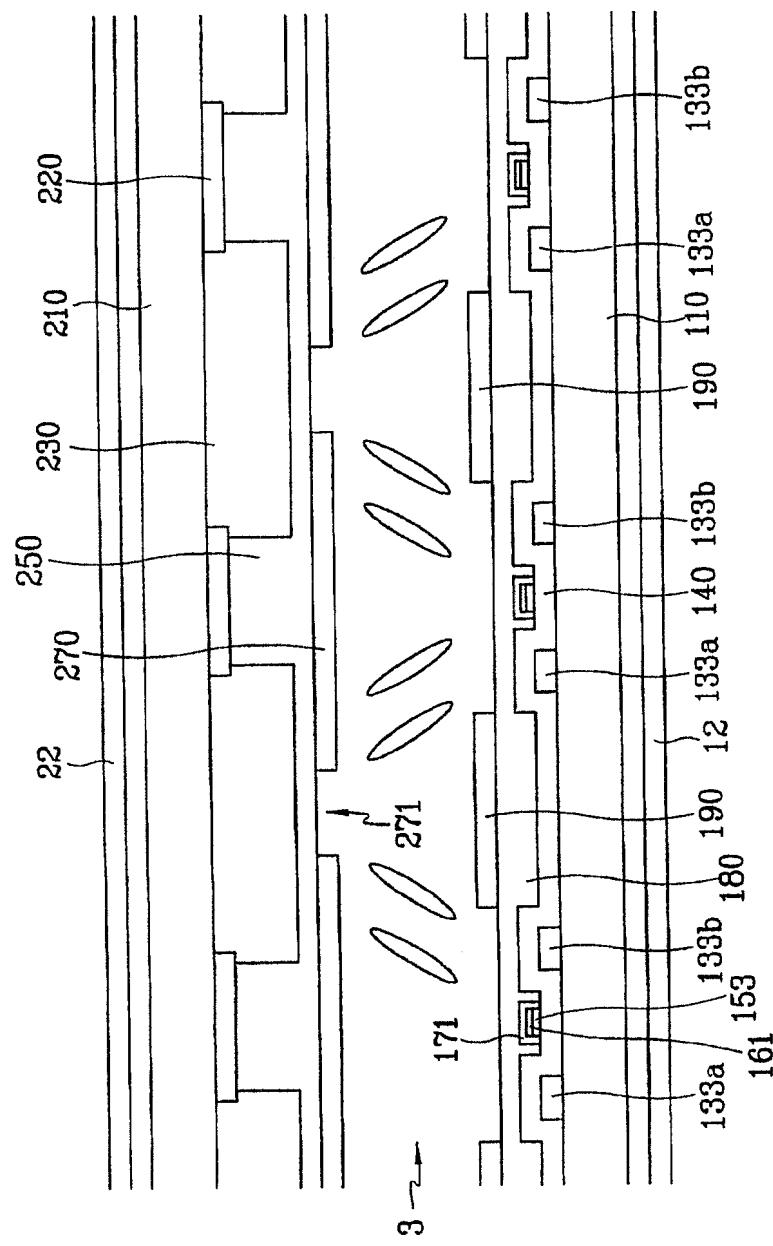

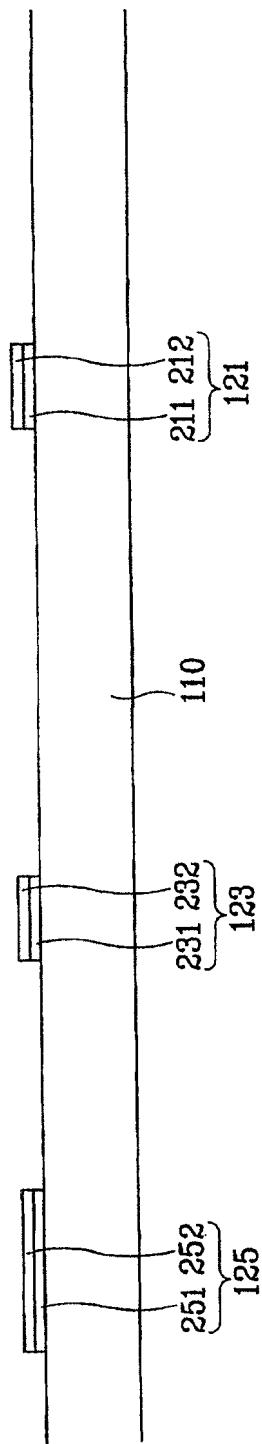

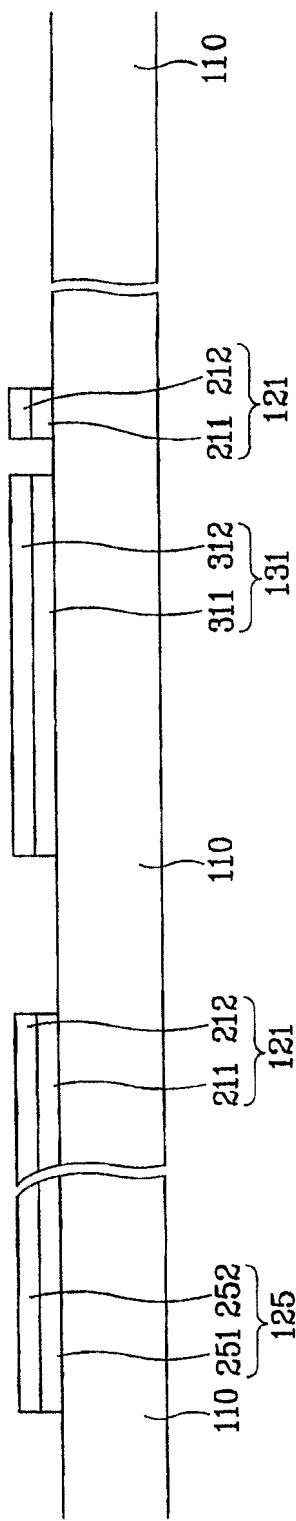

图 1 是根据本发明第一实施例的 LCD 的 TFT 阵列板简图，图 2 是根据本发明第一实施例的 LCD 的彩色滤光片板简图，图 3 是根据本发明第一实施例的 LCD 简图，并且图 4 是沿图 3 中 IV-IV' 线截取的剖面图。

LCD 包括下基底 110、与下基底相对的上基底 210 以及夹置在基底 110 和 210 之间的包含液晶分子的液晶层 3，液晶层 3 包括垂直于基底 110 和 210 排列的液晶分子。

在优选由透明绝缘材料如玻璃制成的下基底 110 内表面上形成多个像素电极 190。优选像素电极 190 由透明导电材料如 ITO (氧化铟锡) 和 IZO (氧化铟锌) 制成，并具有多个切口 191、192 和 193。各个像素电极连接到被施加以图像信号电压的 TFT。TFT 连接到传递扫描信号的多个栅极线 121 和传递图像信号的多个数据线 171，响应于扫描信号而被开关。下偏振片 12 附贴在下基底 110 的外表面上。对于反射式 LCD，像素电极 190 不用透明材料制作，下偏振片 121 不是必需的。

在优选由透明绝缘材料如玻璃制成的上基底 210 的内表面上形成用于阻挡光泄漏的黑色矩阵 220、多个红、绿、蓝彩色滤光片 230 和优选由透明导电材料如 ITO 或 IZO 制成的参考电极 270。在参考电极 270 上设置多个切口 271、272 和 273。虽然黑色矩阵 220 与像素区的边界重叠，但黑色矩阵 220 还可以与参考电极的切口 271、272 和 273 重叠，以便阻挡切口 271、272 和 273 产生的光泄漏。

下面更详细地描述第一实施例的 LCD。

在绝缘下基底 110 上形成多个基本上横向延伸的栅极线 121。每个栅极线 121 的多个扩展部(expansion)形成多个栅电极 123。在绝缘基底 110 上还形成基本上平行于栅极线 121 延伸的多个存储电极线 131。在纵向延伸的、从每个存储电极线 131 分叉的多对存储电极 133a 和 133b 经横向延伸的存储电极 133c 彼此连接。存储电极线 131 的数量可以是二个或多个。优选栅极线 121、栅电极 123、存储电极线 131 和存储电极 133 由金属如 Al 或 Cr 制成。它们既可以包含单层，也可以包含依次沉积 Cr 和 Al 层的双层。或者，它们包含各种金属。

在栅极线 121、存储电极线 131 和存储电极 133 上形成优选由 SiNx 制成的栅极绝缘层 140。

在栅极绝缘层 140 上形成纵向延伸的多个数据线 171。每个数据线 171 的多个分叉形成多个源电极 173，并且邻近于各个源电极 173 形成多个漏电极 175。此外，在栅极绝缘层 140 上形成与栅极线 121 重叠的多个桥下金属件(under-bridge metal piece)172。优选数据线 171、源电极 173 和漏电极 175 如同栅极布线一样由 Cr 或 Al 制成。它们也可以有单层结构或多层结构。

在源电极 173 和漏电极 175 之下形成用作 TFT 的通道部分的半导体层

151 和 153 的多个通道部分 151， 并且在数据线 171 之下形成在纵向延伸并与半导体通道部分 153 连接的半导体层 151 和 153 的多个数据部分 153。 在半导体层 151 和 153 上形成用于减小源电极和漏电极 173 和 175 与半导体通道部分 151 之间接触电阻的接触层 161。 优选半导体层 151 和 153 由重掺杂 N 型杂质的非晶硅制成。

在数据线 171 等上形成优选由无机绝缘物如 SiNx 或有机绝缘物如树脂制成的钝化层 180。 在钝化层 180 中设置暴露漏电极 175 的多个接触孔 181。

在钝化层 180 上形成多个象素电极 190， 每个象素电极有多个切口 191、 192 和 193。 优选象素电极 190 由透明导体如 ITO 或 IZO 或具有良好的光反射特性的不透明导体如 Al 制成。 每个象素电极 190 上的切口 191、 192 和 193 包括横向延伸的并位于将象素电极 190 分隔成在纵向分布的上、 下两半部的位置上的横向切口 192， 以及在斜向延伸并分别位于象素电极 190 的上下两半部中的两个斜向切口 191 和 193。 斜向切口 191 和 193 的延伸部(extension)彼此垂直， 以便将边缘场的场方向规律地分配为四个方向。

关于数据线 171 彼此相对的两个相邻象素电极 190 的切口 191、 192 和 193 基本上具有关于数据线 171 的镜面对称性。

此外，在钝化层 180 上形成多个存储连接件或桥 91， 它将存储电极 133a 连接到关于栅极线 121 与其相对的存储电极线 131 上。 存储桥 91 经均设置在钝化层 180 和栅极绝缘层 140 中的多个接触孔 183 和 184 接触存储电极 133a 和存储电极线 131。 存储桥 91 与桥下金属件 172 重叠。 存储桥 91 电连接下基底 110 上的所有存储布线。 如果需要， 这些存储布线可以用于修复栅极线 121 和/或数据线 171 的缺陷，并且当辐射激光束以进行这种修复时， 桥下金属件 172 可以用于增强栅极线 121 和存储桥 91 之间的电连接。

在上基底 210 上形成用于阻挡光泄漏的黑色矩阵 220。 在黑色矩阵 220 上形成多个红、 绿、 蓝彩色滤光片 230。 在彩色滤光片 230 上形成具有多组切口 271 的参考电极 270。 优选参考电极 270 由透明导体如 ITO 或 IZO 制成。

参考电极 270 的每组切口 271、 272 和 273 在两个相邻切口 271、 272

和 273 之间插入像素电极 190 的斜向切口 191 和 193。每个切口 271、272 和 273 包括斜向部分或平行于斜向切口 191 和 193 的部分以及与像素电极 190 的边缘重叠的横向和纵向部分。

关于两相邻像素区之间的边界线（即，沿数据线延伸的线）彼此相对的参考电极 270 的切口 271、272 和 273 具有基本上关于边界线的镜面对称性。

通过对齐并组合具有上述结构的 TFT 阵列板与彩色滤光片板、且在两板之间注入垂直排列的液晶材料而制备根据本发明的 LCD 的基本结构。当 TFT 阵列板和彩色滤光片板对齐时，像素电极 190 的切口 191、192 和 193 以及参考电极的切口 271、273 和 273 将各个像素区划分成几个小的畴。基于畴中的液晶分子的主轴的平均方向，这些小畴分为四种类型。关于数据线 171 彼此相对的两相邻像素区的小畴具有基本上关于数据线 171 的镜面对称性，这是由于像素电极 190 的切口 191、192 和 193 与参考电极 270 的切口 271、273 和 273 的镜面对称性所致。在此情况下，术语“基本的镜面对称性”意味着允许由于上下基底 110 和 210 的对准误差所致的对称变形。

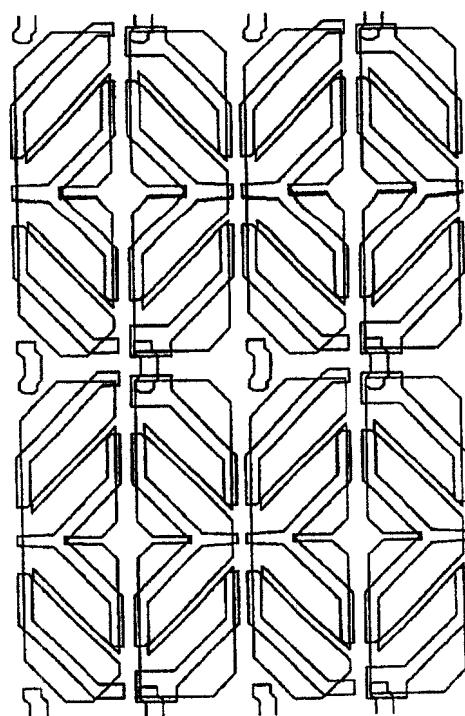

图 5A 是根据本发明第一实施例的 LCD 的像素电极和八个像素 ( $4 \times 2$ ) 的切口的简图，图 5B 是图 5A 中所示的具有黑色矩阵的简图。

如图 5A 所示，根据本发明第一实施例的 LCD 具有一种包含八边形的切口图案，包括一对相邻像素的切口并在四个方向上重复排列。

考虑到黑色矩阵的分布，如图 5B 所示，除了位于像素区中心的横向部分以外，横向和纵向部分被黑色矩阵遮挡。具有此种结构的 LCD 的孔隙比达到 41%。

图 6 是根据本发明第二实施例的 LCD 简图。

根据本发明第二实施例的 LCD 与第一实施例的 LCD 的不同之处在于设置多个突起 281 作为畴分隔装置以代替参考电极的切口。或者，在多个像素电极 190 上设置多个突起 281，或用多个突起代替像素电极 190 的切口 191、192 和 193。

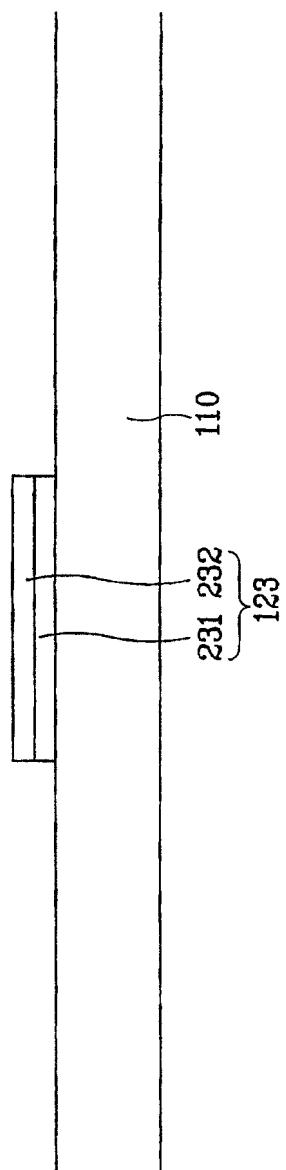

图 7 是根据本发明第三实施例的 LCD 的 TFT 阵列板简图，图 8 是根据本发明第三实施例的彩色滤光片板简图，图 9 是根据本发明第三实施例的 LCD 简图。

根据本发明第三实施例的 LCD 的 TFT 阵列板基本上具有与图 1 所示第一实施例相同的结构，除了象素电极的切口分布之外。下面将只描述切口 191、192 和 193 的分布。第三实施例 LCD 的 TFT 阵列板的每个象素电极 190 的切口 191、192 和 193 包括基本上沿象素电极 190 的横向中心线延伸并然后倾斜发散地分叉成上、下分支的中心切口 192 和两个在斜向延伸并分别位于象素电极 190 的上、下两半部中的斜向切口 191 和 193。

彩色滤光片板有一个黑色矩阵 220 和多个彩色滤光片 230，它们基本上具有与第一实施例相同的结构。但是，彩色滤光片阵列板上的参考电极带有的多个第一至第五切口 271-275 具有与第一实施例中不同的形状。下面只描述切口 271-275 的分布。

每个第一切口 271 和每个第三切口 273 在斜向横穿象素区，两个相邻象素区中的切口 271 和 273 彼此连结。切口的每个连结占据两相邻象素区之间边界区的相当大部分。每个第二切口 272 横穿象素区，两个相邻象素区中的切口 272 彼此连结。切口的每个连结占据两个相邻象素区之间边界区的相当大部分。每个第四切口 274 和每个第五切口 275 斜切象素区的角部以占据象素区相当大的角部。两个相邻象素区中的第四和第五切口 274 和 275 彼此连结。此外，在纵向分布的两个相邻象素区中的第四和第五切口 274 和 275 彼此连结。如上所述，虽然连结相邻象素区之间切口的部分被认作连结，但也可以认作重叠，从而强调该部分与数据线重叠。提出这个旁注是为了着重强调切口和数据线的重叠减小施加到数据线的电容性负载，从而减小图象信号的变形这样一种功能。

根据本发明第三实施例的 LCD 的特征在于由于相邻象素之间参考电极 270 的切口 271-275 的连结，去除了接近象素区边界的参考电极的大片区域。象素区边界附近参考电极的去除减小了施加到数据线 171 的电容性负载，减少了由 RC 延迟所致的信号失真。后面将详细描述这一点。

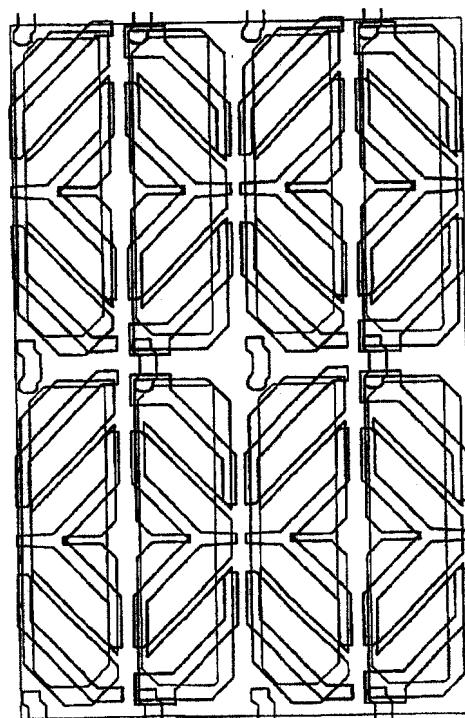

图 10A 是根据本发明第三实施例的 LCD 的象素电极和八个象素（4×2）的切口的简图，图 10B 是图 10A 中所示的具有黑色矩阵的简图。

首先，如图 10A 所示，根据本发明第三实施例的 LCD 具有包含金刚石形状的切口图案，该图案包括一对相邻象素的切口并在四个方向上重复分布。此外，在四个金刚石形状的中心分布十字形状的图案。

考虑黑色矩阵的分布，如图 10B 所示，除了位于象素区中心的横向部

分之外，横向和纵向部分被黑色矩阵遮挡。

考虑黑色矩阵的分布，如图 10B 所示，位于像素区边界附近的第一至第五切口的大部分连结被黑色矩阵阻挡。

这种分布可以减小施加到数据线的电容性负载，并增大 LCD 的孔隙比。在此布局中孔隙比达到 42%。

下面将对根据第三实施例的 LCD 中施加到数据行的电容性负载的减小做详细的描述。

图 11 是表示参考电极的切口和数据行之间重叠的截面图，图 12 是作为与数据行重叠的部分参考电极中去除面积比的函数的施加到数据线的寄生电容曲线。

如图 11 所示，参考电极 270 的切口 171 与数据线 171 重叠。参考电极 270 的对应于切口 171 的去除部分是参考电极 270 距离数据线 171 的最接近部分。因为参考电极 270 的所有部分与数据线 171 共同形成电容器，并且去除了参考电极 270 的最接近部分，所以二者之间由于 RC 延迟而造成沿数据线 171 走向的图象信号失真的负面影响的电容被减小。因此，参考电极 270 的切口与数据线 171 的重叠减小了图象信号的失真。

图 12 是作为数据线 171 上参考电极 270 中去除面积比的函数的数据线 171 和参考电极 270 之间的电容大小。相对于重叠部分的整个面积都保留的情况，参考电极 270 的与数据线 171 重叠的重叠部分整个面积的去除减少了二者之间电容的大约 10%，而大约 50% 的去除减少电容大约 5%。因为本发明的第二实施例去除参考电极 270 重叠部分的大约 50%，所以寄生电容减小大约 5%。寄生电容的减小减少了沿数据线传递的图象信号的延迟。表 1 表示利用示波器的实际板的测量结果。

表 I

|                 |         | 参考电极无去除 | 参考电极 50%去除 |

|-----------------|---------|---------|------------|

| 电阻( $k\Omega$ ) |         | 44.9    | 46         |

| 延迟( $\mu s$ )   | 60 级灰度  | 5.724   | 5.513      |

|                 | 256 级灰度 | 6.443   | 6.123      |

下面将详细描述制造本发明实施例中 LCD 的提供上述结构和效果的

TFT 阵列板的方法。

首先，参见图 13~17，下面将描述利用五个光掩模的方法。

如图 13 所示，在基底 110 上沉积优选由具有优良的物理和化学特性的 Cr 或 Mo 合金制备的第一栅极布线层 211、231 和 251 和优选由具有低电阻性的 Al 或 Ag 合金制备的第二栅极布线层 212、232 和 252，并对它们构图以形成包括多个栅极线 121、多个栅电极 123 和多个栅极焊点 125 的并基本上在横向延伸的栅极布线。此时，虽然未示出，但还形成存储电极线（第一掩模）。

对于 Mo 合金的第一栅极布线层 211、231 和 251 以及 Ag 合金的第二栅极布线层 212、232 和 252，两层通过对 Al 合金的蚀刻剂如磷酸、硝酸、醋酸和去离子水的混合物蚀刻。由此通过利用单个的蚀刻过程完成包含双层的栅极布线 121、123 和 125 的形成。因为对于 Ag 合金的磷酸、硝酸、醋酸和去离子水的混合物的蚀刻率高于对 Mo 合金的蚀刻率，所以可以获得栅极布线所需的 30° 的楔角。

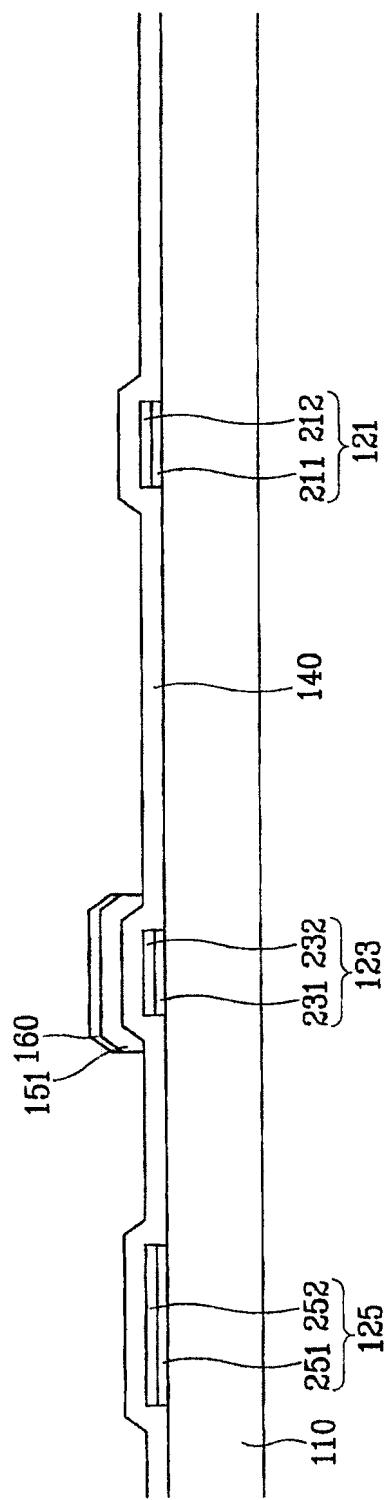

接下来，如图 14 所示，依次沉积三层，即优选由 SiNx 制备的栅极绝缘层 140、非晶硅层和掺杂的非晶硅层，并且一起光蚀刻非晶硅层和掺杂的非晶硅层以在栅极绝缘层 140 上形成与栅电极 123 相对的半导体层 151 和欧姆接触层 160（第二掩模）。

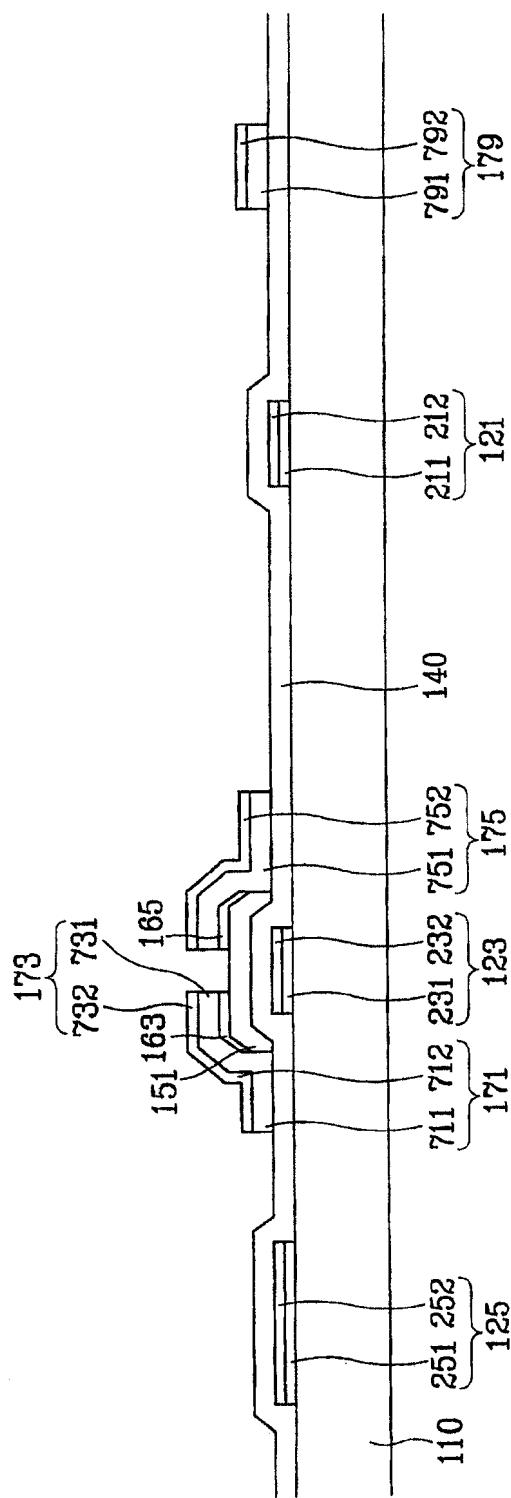

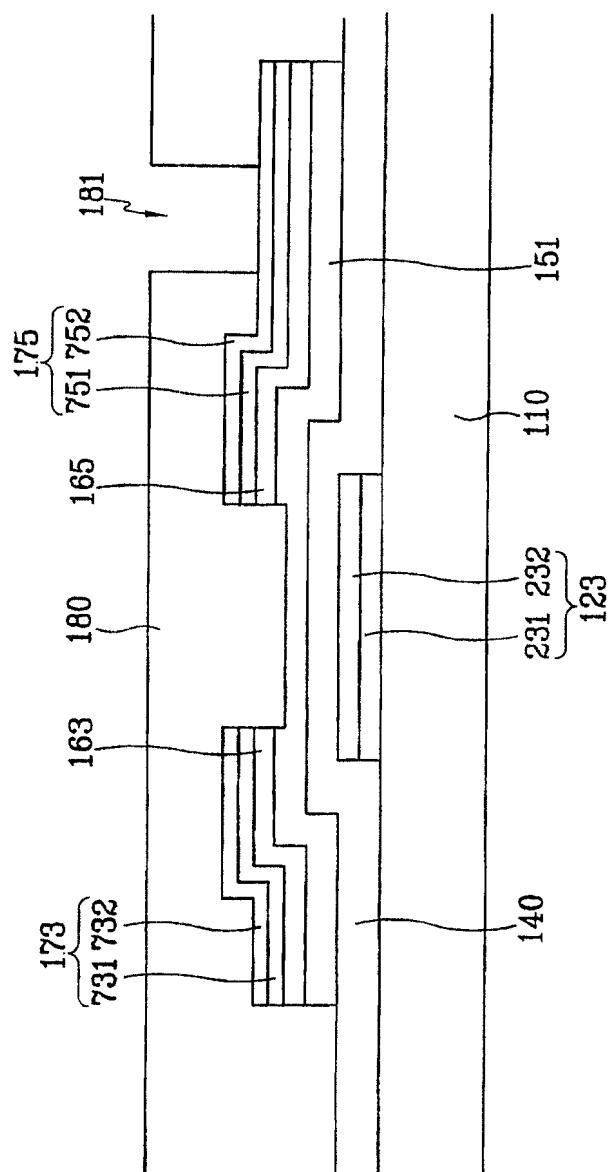

随后，如图 15 所示，沉积并光蚀刻优选由 Cr 或 Mo 合金制备的第一数据布线层 711、731、751 和 791 以及优选由 Al 或 Ag 合金制备的第二数据布线层 712、732、752 和 792，形成数据布线。数据布线包括与栅极线 121 相交的多个数据线 171、连结到数据线 171 并延伸到栅电极 121 的多个源电极 173、连结到数据线 171 的一端的多个数据焊点 179 和多个与源电极 173 分开并与源电极 173 关于栅电极 121 相对的漏电极 175（第三掩模）。

之后，蚀刻掺杂非晶硅层图案 160 的不被数据布线 171、175 和 179 覆盖的部分，使得掺杂非晶硅层图案 160 分成关于栅电极 123 彼此相对的两个部分 163 和 165，从而暴露半导体图案 151 的处于掺杂非晶硅层 163 和 165 两个部分之间的部分。最好进行氧等离子处理，以便稳定半导体层 151 的暴露面。

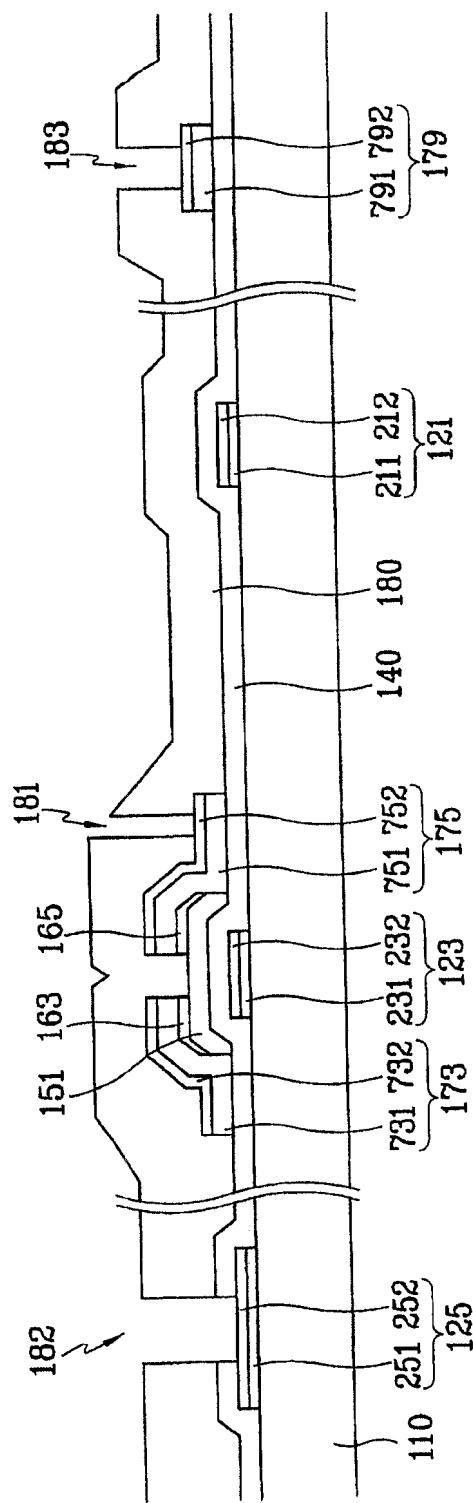

接下来，如图 16 所示，通过化学气相沉积（“CVD”）生长 a-Si:C:O

膜或 a-Si:O:F、通过沉积无机绝缘膜如 SiNx 或通过涂覆有机绝缘膜如丙稀基材料，形成钝化层 180。通过利用在气体状态下 SiH(CH<sub>3</sub>)<sub>3</sub>、SiO<sub>2</sub>(CH<sub>3</sub>)<sub>4</sub>、(SiH)<sub>4</sub>O<sub>4</sub>(CH<sub>3</sub>)<sub>4</sub>、Si(C<sub>2</sub>H<sub>5</sub>O)<sub>4</sub> 等作为基本源并且流动氧化物的气体混合物如 N<sub>2</sub>O 和 O<sub>2</sub> 以及 Ar 或 He 进行 a-Si:C:O 的沉积。在 O<sub>2</sub> 和 SiH<sub>4</sub>、SiF<sub>4</sub> 等的混合气体的流动中进行 a-Si:O:F 的沉积。可以加入 CF<sub>4</sub> 作为氟的辅助源（第二掩模）。

通过光蚀刻过程对钝化层 180 和栅极绝缘层 140 一起进行构图，来形成多个暴露栅极焊点 125、漏电极 175 和数据焊点 179 的接触孔 181、182 和 183。此处，接触孔 181、182 和 183 的平面形状为多边形或圆形。优选暴露焊点 125 和 179 的每个接触孔 181 和 183 的面积等于或大于 0.5mm × 0.5μm，并等于或小于 2mm × 60μm。虽然图中未示出，但在此步骤中还形成用于将存储桥与存储电极线及存储电极相接触的多个接触孔（第四掩模）。

最后，如图 17 所示，对多个像素电极 190、多个辅助栅极焊点 95 和多个辅助数据焊点 97 沉积并光蚀刻 ITO 层或 IZO 层。每个像素电极 190 经第一接触孔 181 连结到漏电极 175，并且辅助栅极焊点 95 和辅助数据焊点 97 经第二和第三接触孔 182 和 183 连结到栅极沉淀 95 和数据焊点 97。在沉积 ITO 或 IZO 之前优选利用氮气进行预热过程。这是为防止在经接触孔 181、182 和 183 暴露的金属层部分上形成金属氧化物所需的。虽然图中未示出，在此步骤中还形成多个存储桥，并且将光掩模设计成像素电极 190 的切口具有关于数据行 171 的镜面对称性（第五掩模）。

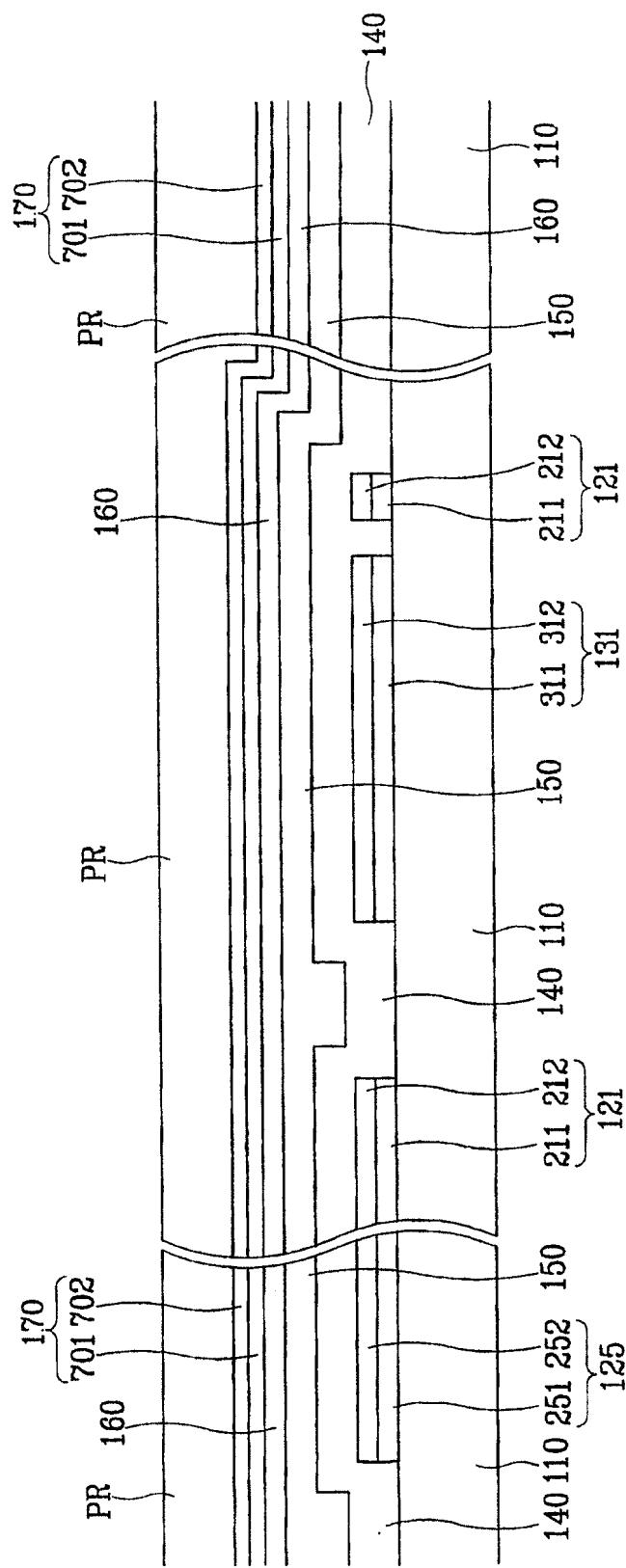

下面将描述利用根据本发明实施例的第四光掩模制造 TFT 阵列板的方法。

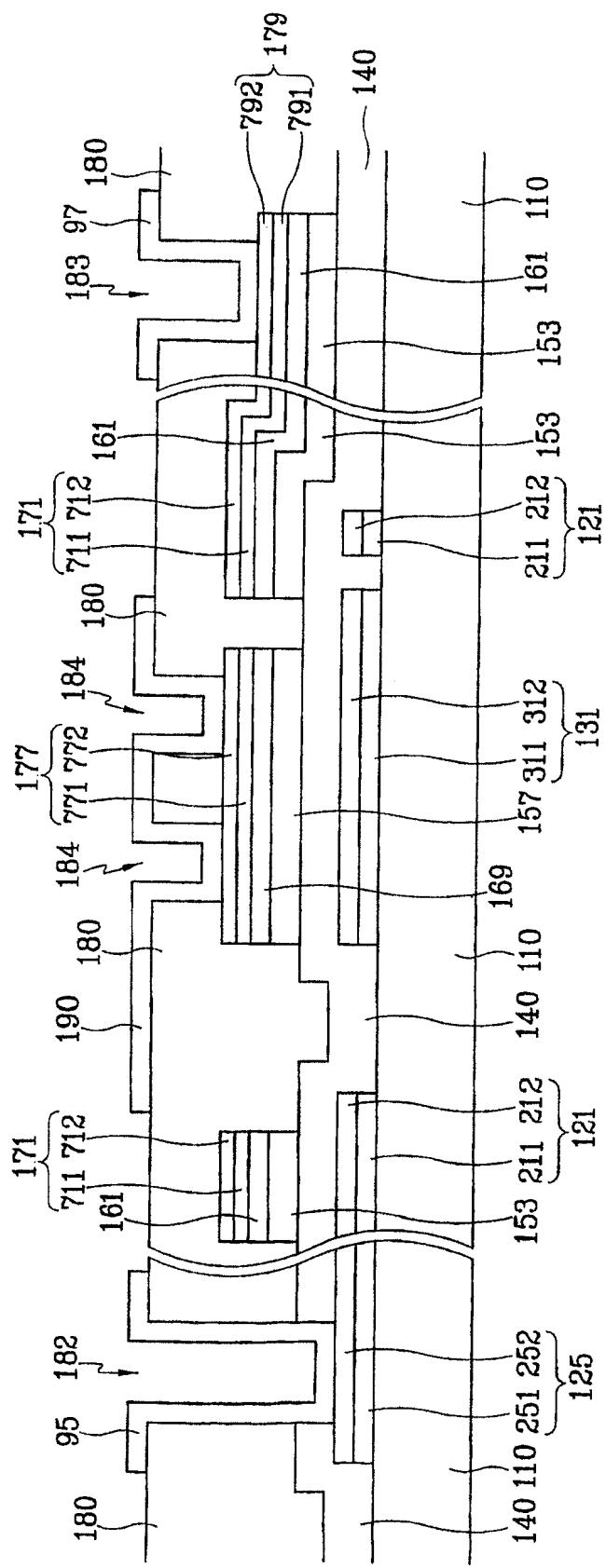

图 18A 和 18B 到图 26A 和 26B 是依次表示利用四个掩模的制作方法步骤的 LCD 板的 TFT 阵列板截面图。

首先，如图 18A 和 18B 所示，与第一实施例相似，在基底 110 上沉积优选由具有优良的物理和化学特性的 Cr 或 Mo 合金制备的第一栅极布线层 211、231 和 251 和优选由具有低电阻性的 Al 或 Ag 合金制备的第二栅极布线层 212、232 和 252，并对它们构图以形成包含多个栅极线 121、多个栅电极 123 和多个栅极焊点 125 的栅极布线和存储电极布线（第一掩模）。

接下来，如图 19A 和 19B 所示，通过 CVD 法依次沉积 SiNx 制成的

栅极绝缘层 140、半导体层 150 和接触层 160，使得层 30、40 和 50 分别具有 1500-5000Å、500-2000Å 和 300-600Å 的厚度。通过溅射沉积优选由 Cr 或 Mo 合金制成的第一导电膜 70 和优选由 Al 或 Ag 合金制成的第二导电膜 70，从而形成导电层 170。之后，在其上涂覆厚度为 1-2μm 的光致抗蚀剂膜 PR。

随后，经掩模对光致抗蚀剂膜 PR 曝光并显影以形成如图 20A 和 20B 所示的光致抗蚀剂图案 PR2 和 PR1。建立起位于源电极和漏电极 173 和 175 之间的 TFT 的通道区 C 上的光致抗蚀剂图案 PR2 和 PR1 的第二部分 PR2，使其厚度小于其上形成有数据布线的数据区 A 上的第一部分 PR1。去除其余区域 B 上的光致抗蚀剂膜部分。根据后述蚀刻步骤中的蚀刻条件调节通道区 C 上第二部分 PR2 与数据区 A 上第一部分 PR1 的厚度比。优选第二部分 PR2 的厚度等于或小于第一部分 PR1 的厚度一般，尤其是等于或小于 4000Å。

通过几项技术获得光致抗蚀剂膜的与位置有关的厚度。为了调节区域 C 中的曝光量，在掩模上设置狭缝图案、格栅图案或半透膜。

当使用狭缝图案时，优选狭缝之间的部分的宽度或两部分之间的间距、即狭缝的宽度小于用于光刻法的曝光机的分辨率。在利用半透膜的情况下，可以用不同透射率或不同厚度的薄膜调节掩模的透射率。

当经此掩模用光辐射光致抗蚀剂膜时，直接暴露于光的部分的聚合物几乎完全分解，并且由于曝光量较小，那些面对狭缝图案或半透明膜的部分的聚合物不完全分解。被挡光膜阻挡的部分的聚合物很难分解。光致抗蚀剂膜的显影使得具有未分解的聚合物的部分剩下，并使得暴露于较少光辐射的部分薄于不经受曝光的部分。此处不需要曝光时间长到足以分解所有的分子。

光致抗蚀剂图案的较薄部分 PR2 可以通过在对光致抗蚀剂膜曝光和显影之后进行回流过程、以使可回流的光致抗蚀剂膜流到没有光致抗蚀剂膜的区域、并利用具有完全透光的透射区和完全遮光的遮挡区的普通掩模而获得。

之后，蚀刻光致抗蚀剂图案 PR2 和底层、即导电层 170、接触层 150 和半导体层 150，使得数据布线和底层遗留在数据区 A 上，在通道区上只剩下半导体层，从其余的区域 B 中去除所有的三层 170、160 和 150 以暴

露栅极绝缘层 140。

如图 21A 和 21B 所示，去除区域 B 上的导电层 170 的曝光部分以暴露接触层 150 的底部。在此步骤中，选择利用干蚀刻和湿蚀刻，并且干蚀刻和湿蚀刻优选在导电层 170 被选择性蚀刻而光致抗蚀剂图案 PR1 和 PR2 几乎不蚀刻的条件下进行。但是，能够蚀刻光致抗蚀剂图案 PR1 和 PR2 以及导电层 170 的蚀刻条件将适于干蚀刻，因为很难找到只选择性蚀刻导电层 170 而不蚀刻光致抗蚀剂图案 PR1 和 PR2 的条件。在此情况下，第二部分 PR2 应该有比用于湿蚀刻更厚的厚度，以便防止下部的导电层 170 经蚀刻曝光。

因此，如图 21A 和 21B 所示，通道区 C 和数据区 A 上导电层的部分 171、173、175 和 179 以及存储电容器电极 177 被剩下，而剩余区 B 上的导电层 170 部分被去除，从而暴露接触层 150 的底部。剩余的导体图案 171、173、175 和 179 具有基本上与数据布线 171、173、175 和 179 相同的形状，除了源电极和漏电极 173 和 175 仍然没有分离地连结之外。当利用干蚀刻时，光致抗蚀剂图案 PR1 和 PR2 也蚀刻到预定的厚度。

接下来，如图 21A 和 21B 所示，通过干蚀刻与第二光致抗蚀剂部分 PR2 一起同时去除区域 B 上接触层 150 的曝光部分和半导体层 150 的底部。优选在光致抗蚀剂图案 PR1 和 PR2、接触层 150 和半导体层 150 被同时蚀刻而栅极绝缘层 140 不被蚀刻的条件下进行蚀刻。（注意，半导体层和中间层没有蚀刻选择性）。特别是，优选光致抗蚀剂图案 PR1 和 PR2 以及半导体层 150 的蚀刻率彼此相等。例如，利用 SF<sub>6</sub> 和 HCL 的混合气体或 SF<sub>6</sub> 和 O 的混合气体将膜和层蚀刻到基本上相同的厚度。为了光致抗蚀剂图案 PR1 和 PR2 以及半导体层 150 的相同蚀刻率，优选第二部分 PR2 的厚度等于或小于半导体层 150 和接触层 150 的厚度之和。

通过这种方式，如图 22A 和 22B 所示，去除通道区 C 上的第二部分 PR2 以暴露源/漏导体图案 173 和 175，并且去除区域 B 上的接触层 150 和半导体层 150 的各部分以暴露栅极绝缘层 140 的底部。同时，还蚀刻数据区 A 上的第一部分 PR1，以减小厚度。在此步骤中，完成半导体图案 151、153 和 157 的形成。在半导体图案 151、153 和 157 上形成接触层 161、163 和 165 及 169。

然后通过灰化去除通道区 C 上的源/漏导体图案 173 和 175 表面的残

余光致抗蚀剂。

随后，如图 23A 和 23B 所示，蚀刻去除通道区 C 上源/漏导体图案 173 和 175 的暴露部分和源/漏接触层图案 163 和 165 的底部。可以对源/漏导体图案 173 和 175 以及源/漏接触层图案 163 和 165 实施干蚀刻。或者，对源/漏导体图案 173 和 175 实施湿蚀刻而对源/漏接触层图案 163 和 165 实施干蚀刻。在前一种情况下，优选以较大的蚀刻选择性蚀刻导体图案 173 和 175 以及接触层图案 1631 和 165，因为如果蚀刻选择性不大，则不容易找到蚀刻的结束点，进而不容易调节在通道区 C 上遗留的半导体图案 151 的厚度。在后一种情况下，交替地执行干蚀刻和湿蚀刻，对经历湿蚀刻的源/漏导体图案 173 和 175 的横侧进行蚀刻，而几乎不对经历干蚀刻的源/漏接触层图案 163 和 165 的横侧进行蚀刻，由此获得阶梯状横侧。用于蚀刻导体图案 173 和 175 以及接触层 163 和 165 的蚀刻气体的例子有 CF<sub>4</sub> 和 HCl 的混合气体以及 CF<sub>4</sub> 和 O<sub>2</sub> 的混合气体。CF<sub>4</sub> 和 O<sub>2</sub> 的混合气体使半导体图案 151 有均匀的厚度。此时，如图 23B 所示，可以去除半导体图案 151 的顶部以使厚度减小，并且将光致抗蚀剂图案的第一部分 PR1 蚀刻到预定的厚度。蚀刻是在栅极绝缘层 140 几乎不被蚀刻的条件下进行，并且优选光致抗蚀剂膜的厚度达到防止第一部分 PR1 被蚀刻，而暴露底部的数据布线 171、173、175 和 179 以及底部存储电容电极 177。

通过这种方式，源电极和漏电极 173 和 175 彼此分开，同时完成数据布线 171、173、175 和 179 以及底部接触层图案 161、163 和 165 的形成。

最后，去除剩留在数据区 A 上的第一部分 PR1。但是，可以在通道区 C 上源电极/漏电极 173 和 175 的各部分的去除和接触层图案 163 和 165 的底部的去除之间进行第一部分 PR1 的去除。

如上所述，交替执行干蚀刻和湿蚀刻或只利用干蚀刻。虽然只利用一类蚀刻的后一过程较简单，但很难找到适当的蚀刻条件。相反，前一过程能够找到恰当的蚀刻条件但较为复杂。

接下来，如图 24A 和 24B 所示，通过化学气相沉积（“CVD”）生长 a-Si:C:O 膜或 a-Si:O:F、通过沉积无机绝缘膜如 SiNx、或通过涂覆有机绝缘膜如丙稀基材料形成钝化层 180。通过利用在气体状态下的 SiH(CH<sub>3</sub>)<sub>3</sub>、SiO<sub>2</sub>(CH<sub>3</sub>)<sub>4</sub>、(SiH)<sub>4</sub>O<sub>4</sub>(CH<sub>3</sub>)<sub>4</sub>、Si(C<sub>2</sub>H<sub>5</sub>O)<sub>4</sub> 等作为基本源并且流动氧化剂如

$N_2O$  和  $O_2$  以及 Ar 或 He 的气体混合物进行 a-Si:C:O 膜的沉积。在  $O_2$  和  $SiH_4$ 、 $SiF_4$  等的混合气体的流动中进行 a-Si:O:F 膜的沉积。可以加入  $CF_4$  作为氟的辅助源（第二掩模）。

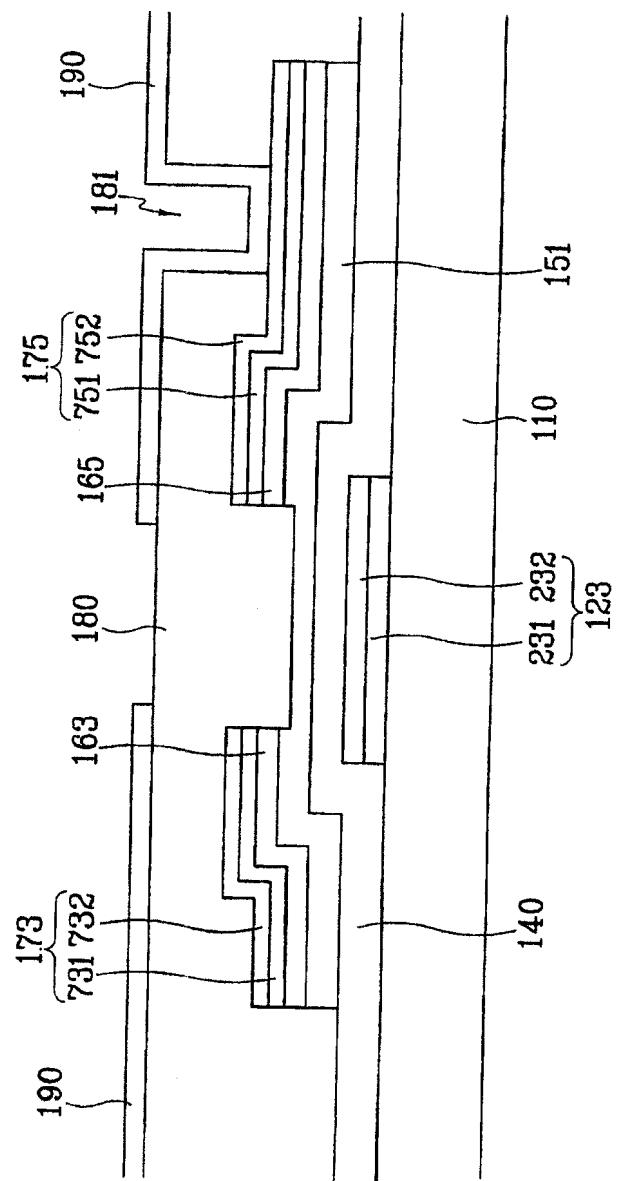

随后，如图 25A 和 25B 所示，与栅极绝缘层 140 一起光蚀刻钝化层 180 以形成暴露漏电极 175、栅极焊点 125 和数据焊点 179 以及存储电容电极 177 的多个接触孔 181、182、183 和 184。优选暴露焊点 125 和 179 的每个接触孔 181 和 183 的面积等于或大于  $0.5mm \times 15\mu m$ ，并等于或小于  $2mm \times 60\mu m$ 。虽然图中未示出，但在此步骤中还形成用于将存储桥与存储电极线及存储电极连接的多个接触孔（第三掩模）。

最后，如图 26A 和 26B 所示，对多个像素电极 190、多个辅助栅极焊点 95 和多个辅助数据焊点 97 沉积并光蚀刻 ITO 层或 IZO 层。每个像素电极 1901 连结到漏电极 175 和存储电容电极 177，并且每个辅助栅极焊点 95 和辅助数据焊点 97 连结到栅极沉淀 95 和数据焊点 97。虽然图中未示出，在此步骤中还形成多个存储桥，并且将光掩模设计成使得像素电极 190 的切口具有关于数据行 171 的镜面对称性（第四掩模）。

因为通过利用 Cr 蚀刻剂形成由 IZO 制备的像素电极 190、辅助栅极焊点 95 和辅助数据焊点 97，所以可以防止在形成像素电极 190、辅助栅极焊点 95 和辅助数据焊点 97 的光蚀刻步骤中经接触孔腐蚀数据线或栅极线的暴露部分。这种蚀刻剂的例子有  $HNO_3/(NH_4)_2Ce(NO_3)_6/H_2O$ 。优选在室温和大约  $200^{\circ}C$  的温度范围内沉积 IZO 以使接触的接触电阻降为最小。优先用于形成 IZO 膜的靶包括  $In_2O_3$  和  $ZnO$ ，包含其中的  $ZnO$  量处于 15-29 at % 的范围内。

优选在沉积 ITO 或 IZO 之前利用氮气执行预热过程。这是防止经接触孔 181、182、183 和 184 在金属层的暴露部分上形成金属氧化物所需的。

虽然以上详细描述了本发明的优选实施例，但应该清楚地知道，可以对本发明的基本原理做各种改型和变化，这些改型和变化对本领域的技术人员来说仍落在本发明由权利要求限定的范围和实质内。尤其是可以对设置于像素电极及参考电极处的切口分布做各种改型。

上述结构提高了 LCD 的孔隙比并减少了图象信号的失真。

图 1

图 2

图 3

图 4

图 5A

图 5B

图 6

图 7

图 8

图 9

图 10A

图 10B

图 11

◆ 数据线和参考电极之间的电容

▲ 数据线的总寄生电容

图 12

图 13

图 14

图 15

图 16

图 17

图 18A

图 18B

图 19A

图 19B

图 20A

图 20B

图 21A

图 21B

图 22A

图 22B

图 23A

图 23B

24A

四

图 24B

25A

图 25B

图 26A

图 26B

|                |                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 垂直排列模式的液晶显示装置                                                               |         |            |

| 公开(公告)号        | <a href="#">CN100378547C</a>                                                | 公开(公告)日 | 2008-04-02 |

| 申请号            | CN02828780.0                                                                | 申请日     | 2002-06-21 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                    |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                    |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                                                    |         |            |

| [标]发明人         | 田尚益<br>朴云用                                                                  |         |            |

| 发明人            | 田尚益<br>朴云用                                                                  |         |            |

| IPC分类号         | G02F1/1337 G02F1/1333 G02F1/1343 G02F1/1368 G02F1/139 H01L21/336 H01L29/786 |         |            |

| CPC分类号         | G02F1/133707 G02F1/1393                                                     |         |            |

| 代理人(译)         | 李晓舒<br>魏晓刚                                                                  |         |            |

| 审查员(译)         | 钟杰                                                                          |         |            |

| 优先权            | 1020020025535 2002-05-09 KR                                                 |         |            |

| 其他公开文献         | <a href="#">CN1625714A</a>                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                              |         |            |

#### 摘要(译)

在第一绝缘基底上形成彼此交叉的多条栅极线和多条数据线，并在由数据行和栅极行限定的各个象素区上形成具有多个第一切口的多个象素电极。薄膜晶体管连结到每个象素电极。在与第一基底相对的第二基底上形成具有多个第二切口的参考电极。在关于一条数据线彼此相对的两个相邻象素区中的第一切口和第二切口具有关于该数据线的镜面对称性。