[12] 发明专利申请公开说明书

[21] 申请号 00137010.3

[43]公开日 2001年7月18日

[11]公开号 CN 1304055A

[22] 申请日 2000.11.6 [21] 申请号 00137010.3

### [30] 优先权

[32]1999.11.5 [33]KR [31]48842/1999

[32]2000.9.28 [33]KR [31]57036/2000

[71] 申请人 三星电子株式会社

地址 韩国京畿道

〔72〕发明人 朴云用

[74]专利代理机构 柳沈知识产权律师事务所

代理人 陶凤波

权利要求书 2 页 说明书 14 页 附图页数 18 页

[54]发明名称 用于液晶显示器的薄膜晶体管阵列面板

[57] 摘要

一种用于液晶显示器的薄膜晶体管阵列，包括：栅极线路，该栅极线路包括在水平方向形成的栅极线；数据线路，该数据线路包括在垂直方向形成的数据线，其中数据线路与栅极线路相交叉并与所述栅极线路绝缘；像素电极，该像素电极是在通过该栅极线和数据线相交叉限定的像素中形成，用于通过数据线接收图像信号；存储线路，该存储线路，包括存储电极线和连接存储电极线的存储电极，其中，存储线路通过重叠像素电极形成存储电容；和存储线路连接线，至少连接该存储线路到一邻近像素。

# 权 利 要 求 书

---

1. 一种用于液晶显示器的薄膜晶体管阵列面板，包括：

5 棚极线路(wire)，该棚极线路包括在水平方向形成的棚极线；

数据线路(wire)，该数据线路包括在垂直方向形成的数据线，其中所说

数据线路与所说棚极线路相交叉(intersect)并与所说棚极线路绝缘；

象素电极，该象素电极是在通过该棚极线和数据线相交叉限定的象素

中形成，用于通过数据线接收图像信号；

10 存储线路，该存储线路(wire)，包括存储电极线和连接存储电极线的存

储电极，其中，该存储线路通过重叠所说象素电极形成存储电容；和

存储线路连接线，至少连接该存储线路到一邻近象素。

2. 如权利要求 1 的薄膜晶体管阵列面板，其中还包括冗余修复线，其

各端重叠一邻近象素的该存储线路。

15 3. 如权利要求 2 的薄膜晶体管阵列面板，其中，该存储线路连接线是

在与所说象素电极相同的层上形成的。

4. 如权利要求 1 的薄膜晶体管阵列面板，其中，所说的冗余修复线是

在与所说数据线路相同的层上形成的。

5. 如权利要求 1 的薄膜晶体管阵列面板，其中所说存储线路是在与所

说棚极线路相同的层上形成的。

20 6. 如权利要求 1 的薄膜晶体管阵列面板，其中所说存储线路重叠该象

素电极的一边沿部分。

7. 如权利要求 1 的薄膜晶体管阵列面板，其中该象素电极具有多个用

圆角相连接的矩形，矩形、锯齿形或十字形的开口图形，以便按多畴结构

调整液晶分子。

25 8. 一种用于液晶显示器的薄膜晶体管阵列面板，包括：

一绝缘衬底；

一在绝缘衬底上形成的棚极线路，其中所说棚极线路包括：在水平方

向形成的棚极线用于传送扫描信号，和连接棚极线的棚电极；

30 一在该绝缘层上形成的存储线路，其中所说存储线路包括：在水平方

向形成的存储电极线，和连接到该存储电极线的存储电极；

一棚绝缘层，用于覆盖所说棚极线路和所说存储线路；

一半导体层，该半导体层在栅绝缘层上形成并且是由半导体材料制作的；

5 一数据线路，包括：在垂直方向形成的数据线，一连接数据线并在半导体层延伸的源电极，一相对于该栅电极在半导体层上延伸并与该源电极相分开的漏电极，其中该数据线通过相交叉(intersecting)该栅极线限定一矩阵阵列的象素；

一钝化层(passivation layer)用于覆盖所说半导体层；

一在象素中的电连接该漏电极的象素电极，其中所说象素电极通过重叠该存储线路形成存储电容；和

10 一存储线路连接线，至少连接邻近象素的该存储线路。

9. 如权利要求 8 的薄膜晶体管阵列面板，其中该象素电极和该存储线路连接线是在彼此相同的层上形成的。

10. 如权利要求 8 的薄膜晶体管阵列面板，其中该象素电极和该存储线路连接线是在所说钝化层上形成的。

15 11. 如权利要求 8 的薄膜晶体管阵列面板，其中还包括一冗余修复线，其各端重叠邻近象素的存储线路并且该冗余修复线是在与该数据线路相同的层上形成的。

# 说 明 书

---

## 用于液晶显示器的薄膜 晶体管阵列面板

5

本发明涉及用于液晶显示器的薄膜晶体管阵列面板，特别是涉及一种具有用于形成存储电容的单独存储线路的液晶显示薄膜晶体管阵列面板。

液晶显示器(LCDs)是一种最广泛使用的平板显示(FPD)结构。液晶显示器具有两个含电极的板，用于产生一电场，和在该两板之间插入的液晶层。10 利用加到该液晶层的电场强度可控制入射光的透射率。

在该最广泛使用的液晶显示器中，两个板上分别形成场产生电极(公共和象素电极)，其中的一个板具有薄膜晶体管开关元件，用来控制加到该象素电极的图像信号。

典型的液晶显示器使用薄膜晶体管作为开关元件，在设置了薄膜晶体管的板上形成彼此跨越的数据线和栅极线，并限定了一矩阵阵列的各象素。此外，在各象素中形成的象素电极通过薄膜晶体管从数据线接收图像信号和与一公共电极一起产生电场。15

在用于液晶显示器的薄膜晶体管阵列面板中，形成的存储电极线用于经过绝缘层重叠象素电极和与该象素电极一起提供存储电容以增加液晶电容的容量。通常，把加到另一板公共电极上的公共信号，或加到栅极线的20 棚极信号加到该存储电极线。

但是，在该液晶显示器运行期间，由于传送到该数据线的图像信号连续变化，使加到存储电极的电压改变，由于存储电容的电阻而改变了该存储电极线的电位。这将导致液晶电容变化和 LCD 图像质量的全面降低，其25 结果是使串扰和闪烁发生。

本发明的一个目的是提供一种用于 LCD 的薄膜晶体管阵列面板，从而使加到存储电极线的电压变化减少以便使串扰和闪烁降至最低。

本发明的另一目的是提供具有线路结构的用于 LCD 的薄膜晶体管阵列面板，从而使线路的断开/短路缺陷容易修复。

30 根据本发明，通过形成一至少连接相互邻近象素的存储线路的冗余线和形成一冗余修复线，该冗余线两端重叠邻近象素的该存储线路而实现上

述目的。

在本发明的液晶显示器薄膜晶体管阵列面板中，包括了栅极线的栅极线路(gate wire)是在水平方向形成，包括了数据线的数据线路(data wire)是在垂直方向形成，该数据线与该栅极线相交叉并相互绝缘，经数据线接收图像信号的象素电极是在由栅极线和数据线相交叉定义的象素中形成。以及形成包括存储电极线和连接该存储电极线并通过重叠所说象素电极产生存储电容的存储线路，和形成至少连接邻近象素的该存储线路的存储线路连接线。

还可形成重叠邻近象素的存储线路的冗余修复线端。

最好是使该存储线路连接线在与该象素电极相同的层上形成和使该冗余修复线在与该数据线相同的层上形成，而该存储线路是在与栅极线路相同的层上形成。

此外，最好使该存储线路叠加该象素电极的边沿部分，和使象素电极具有多个周角(rounded corner)相连接的矩形形状，矩形开口图形(opening pattern)，锯齿形或十字形以便按多畴结构，调整液晶分子。

具体地说，在绝缘层衬底上形成了包括在水平方向传送扫描信号的栅极线和形成了连接栅极线的栅电极。形成了覆盖所说栅极线路和所说存储线路的栅绝缘层以及由半导体材料制作的半导体层。形成了数据线路；源电极；漏电极，其中该数据线路包括在垂直方向构成的数据线，和通过引入的栅极线定义矩阵阵列的象素；该源电极连接数据线并在半导体层上延伸；该漏电极在该半导体层上延伸并相关于该栅电极与源电极分开。构成一覆盖半导体层的钝化层。构成一象素电极和存储线路连接线，其中该象素电极电连接该象素中的漏电极并通过叠加存储线路形成一存储电容；该存储线路连接线至少连接邻近象素的存储线路部分。

最好使象素电极与存储线路连接线在彼此相同的层上形成并形成在钝化层上。此外，可增加一冗余修复线共两端重叠的邻近象素的存储线路它在与数据线路相同的层上形成。

附图构成该说明书的一部分用以和说明书一起说明本发明以解释本发明的原理。

图1是本发明第一实施例液晶显示薄膜晶体管阵列面板线路图；

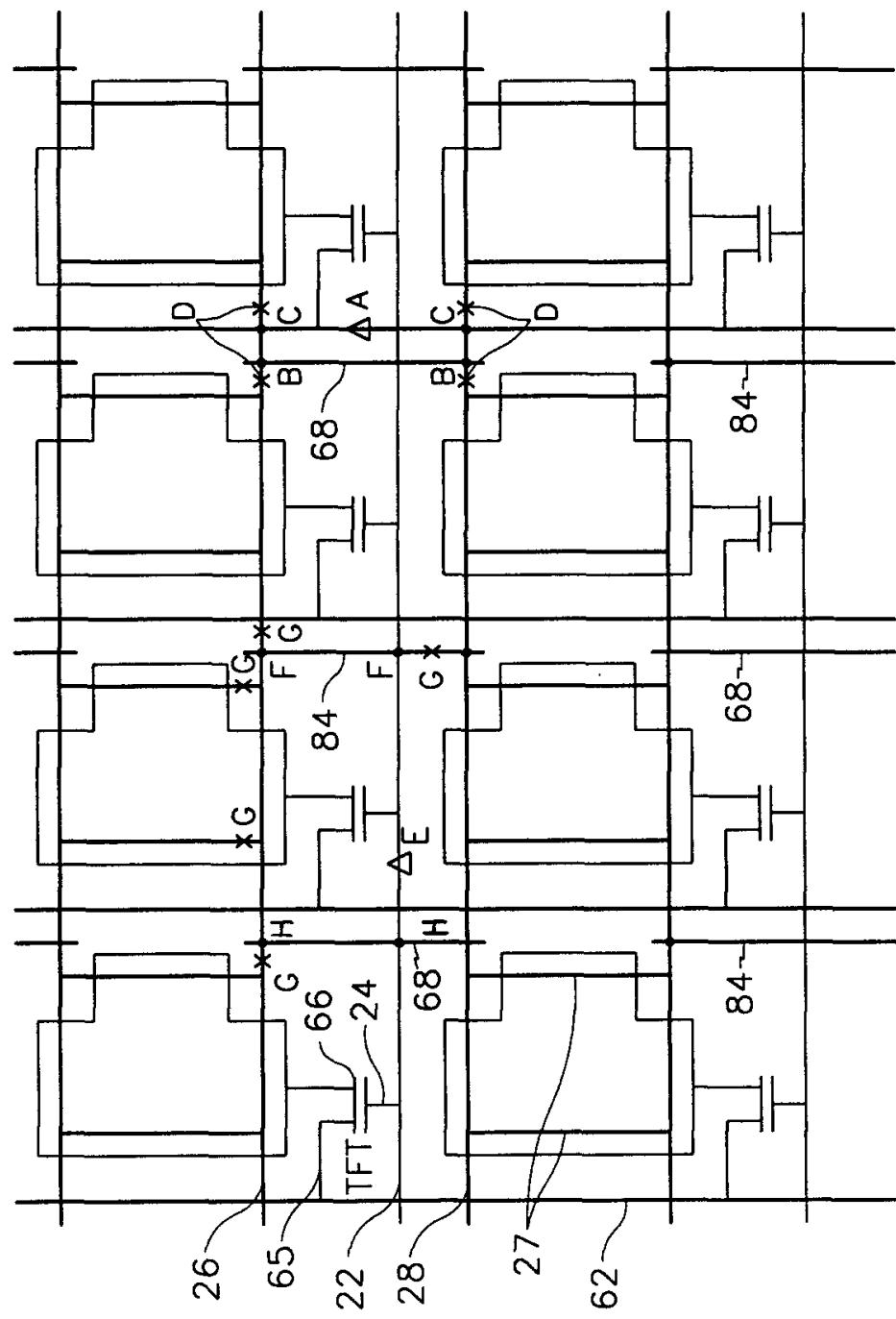

图2是本发明第一实施例液晶显示薄膜晶体管阵列面板的布局方案图；

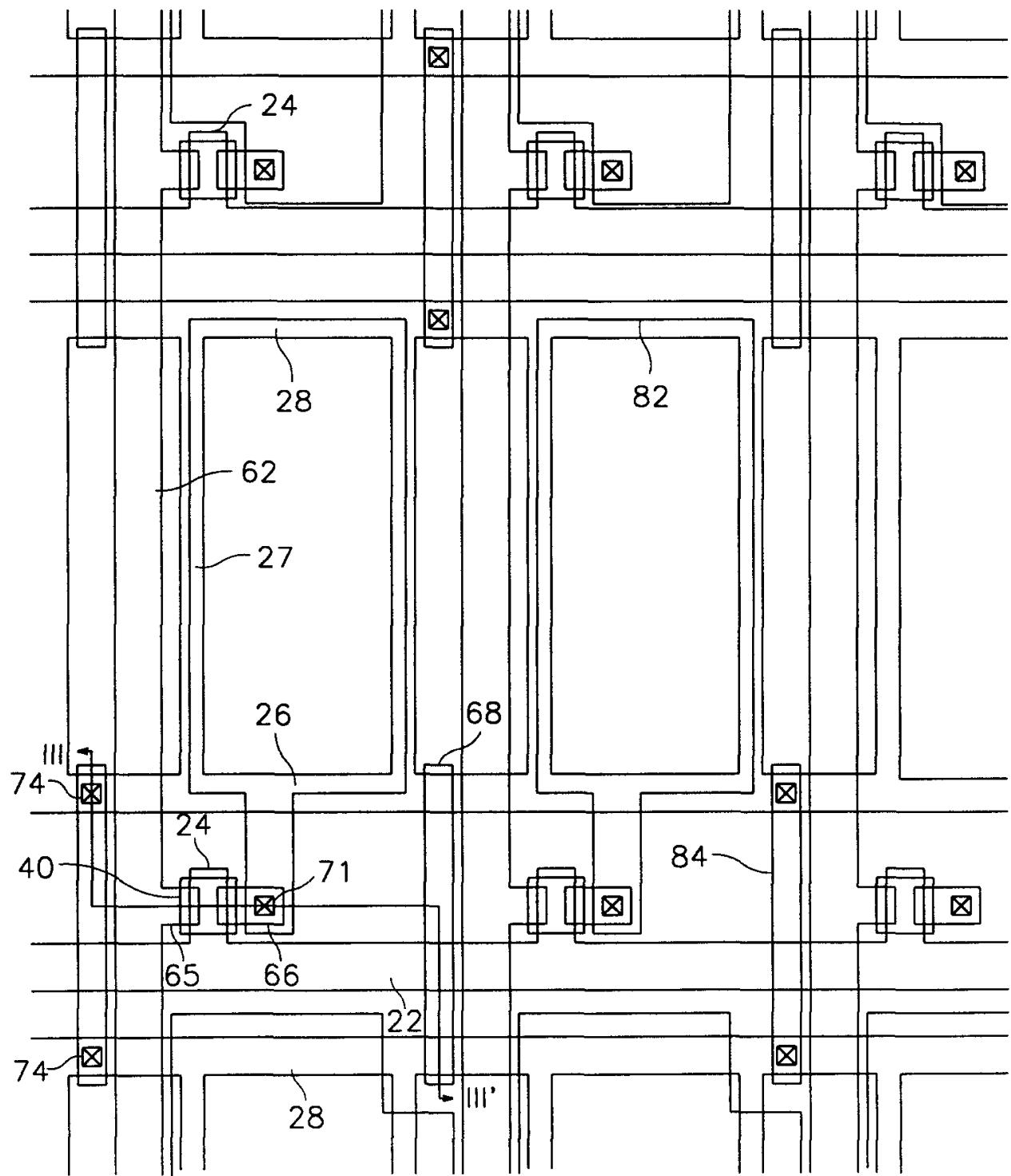

图 3 是图 2 沿线 III-III' 获取的截面图；

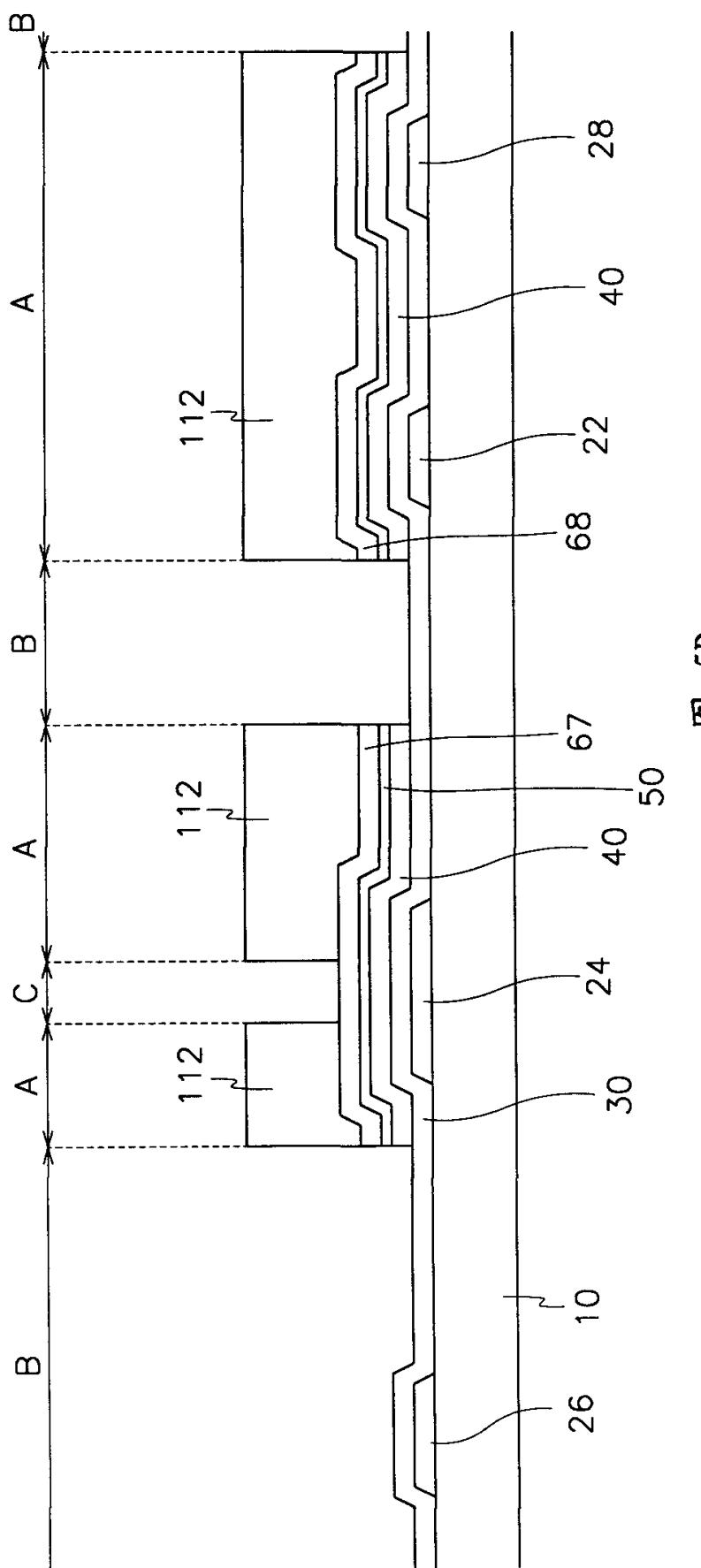

图 4A 到 4D 是依据本发明第一实施例方法制作的液晶显示薄膜晶体管阵列面板的截面图；

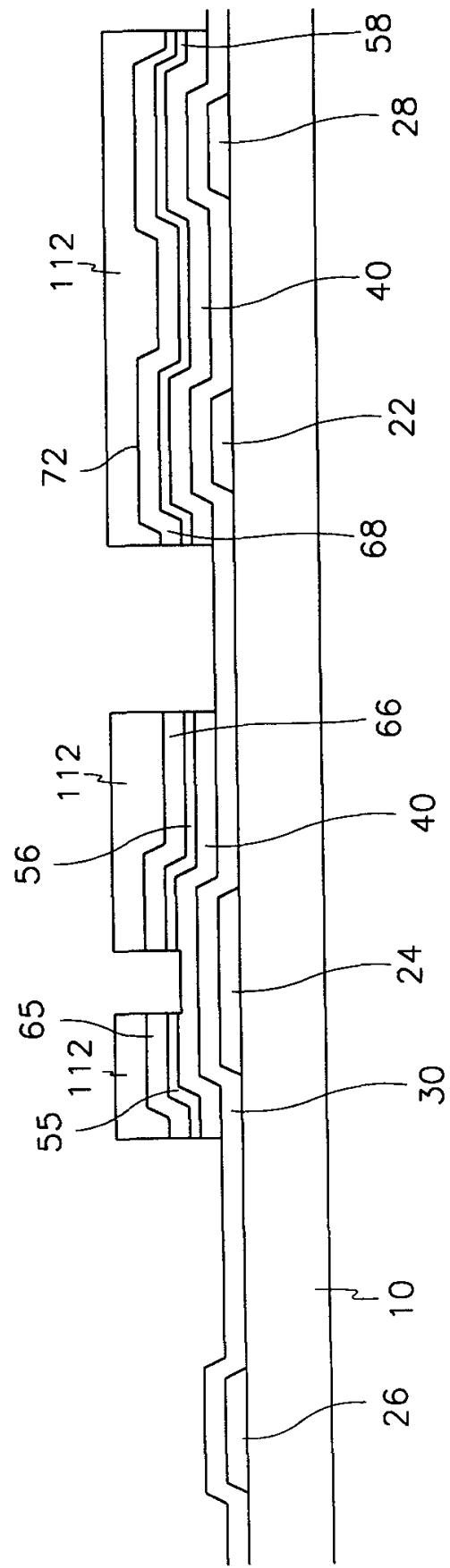

图 5A 到 5G 是依据本发明第一实例方法制作的另一液晶显示薄膜晶体管阵列面板的截面图；

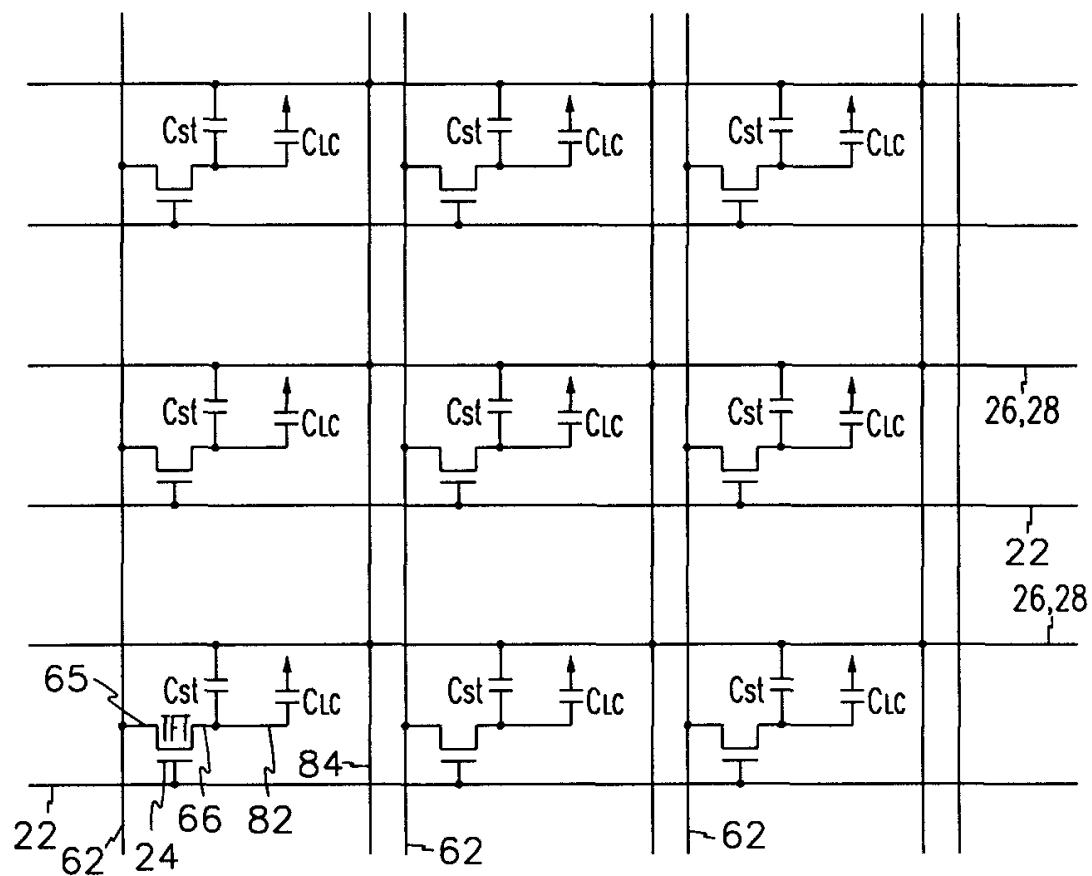

图 6 是本发明第一实施例液晶显示薄膜晶体管阵列面板电路图；

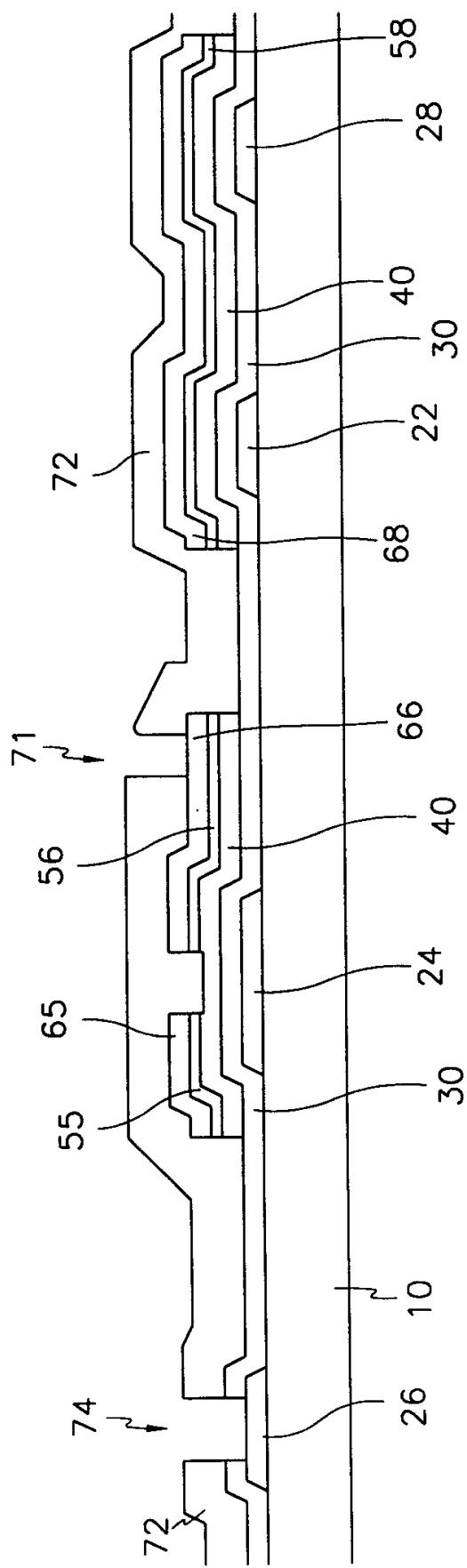

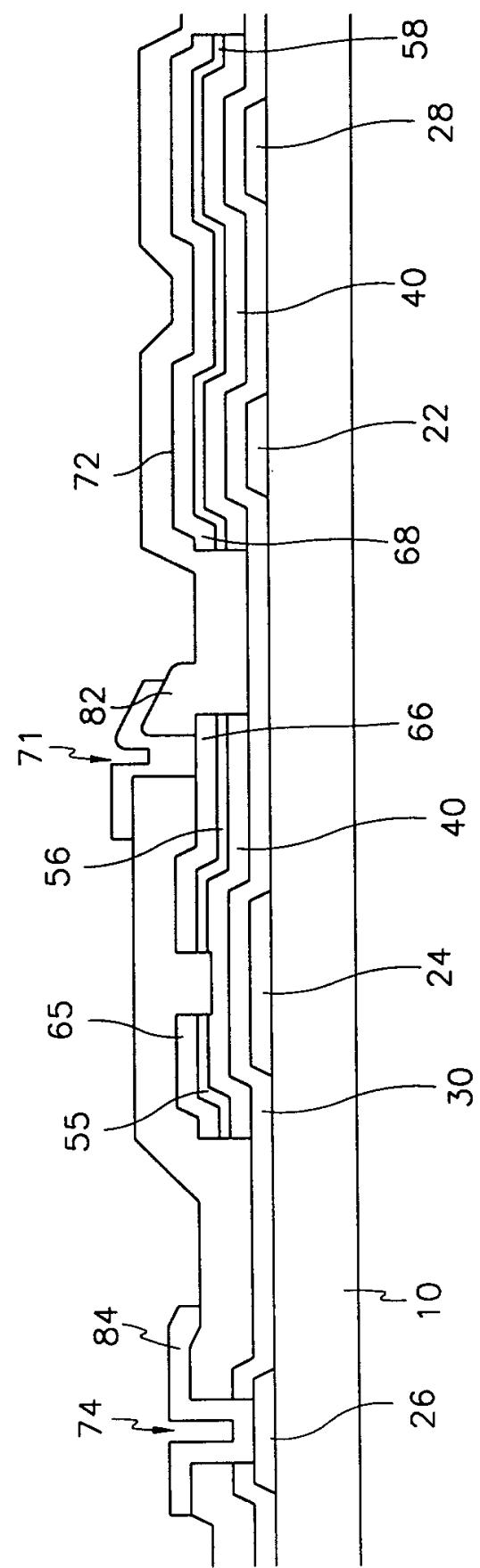

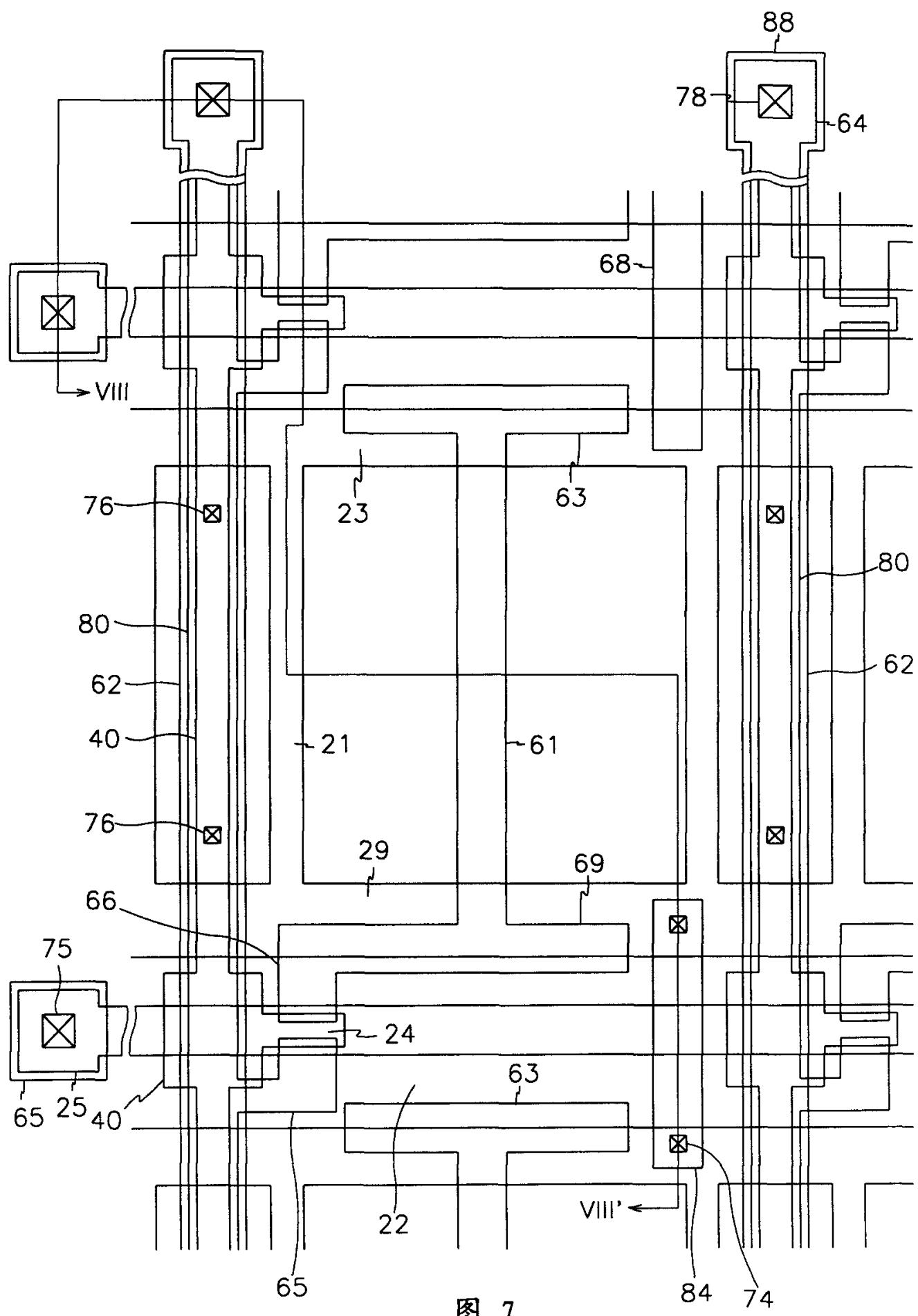

图 7 本发明第二实施例液晶显示薄膜晶体管阵列面板布线图；

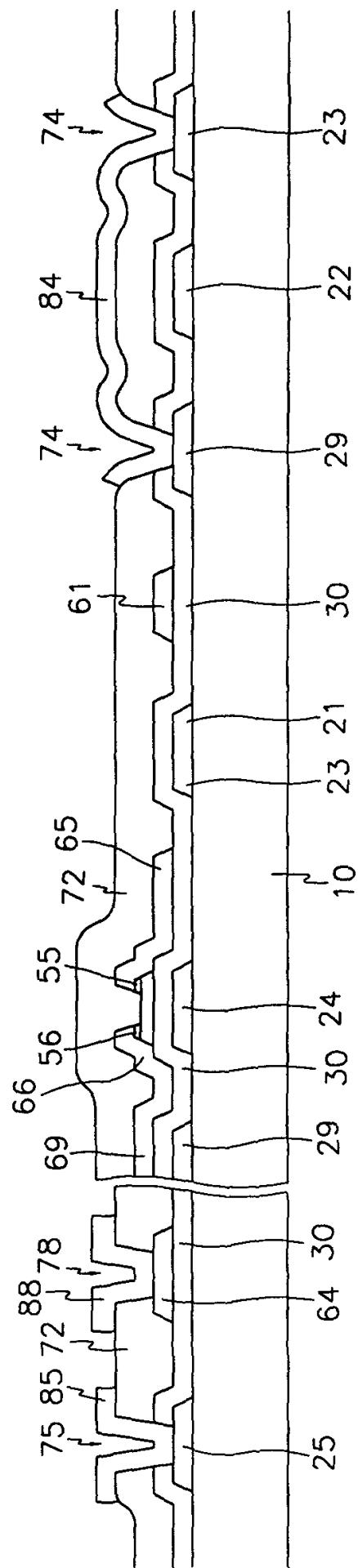

图 8 是图 2 沿 VIII-VIII' 获取的截面图；

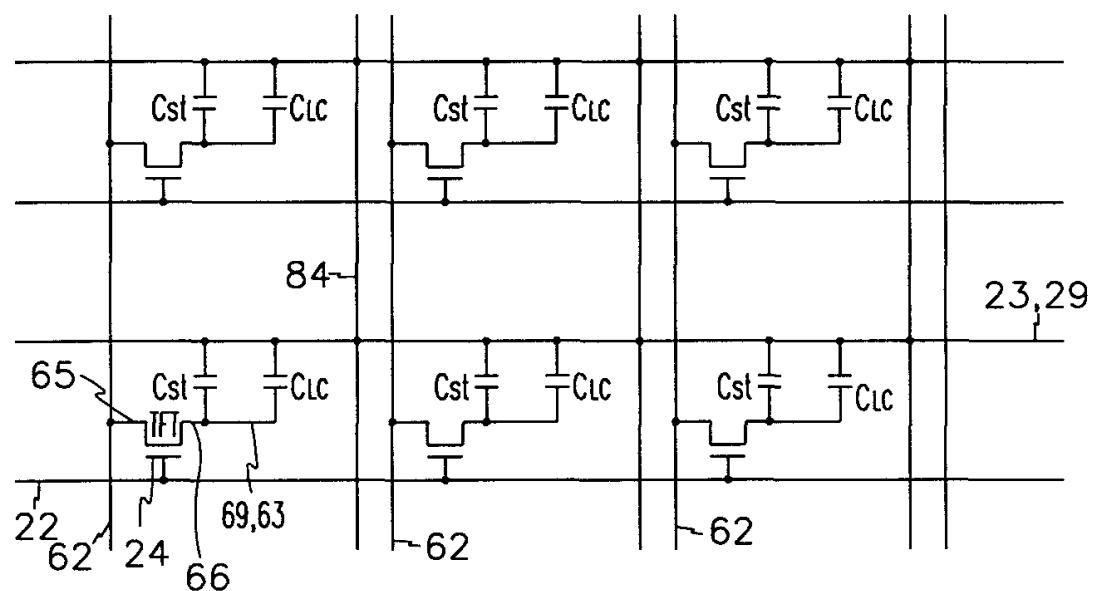

图 9 是本发明第二实施例液晶显示薄膜晶体管面板阵列电路图。

下面将接合附图对本发明作更详细的描述，附图示出了本发明的优选实施例。然而本发明可以以多种不同形式来实施，而不能理解为局限于下面的实施例。在附图中，层和区域的厚度夸大表示。全文中类似的标号表示类似的元件。可以理解，当提到某元件，例如层、区域、或基底，位于另一元件之上时，此元件可能直接处于此另一元件上，或者可以存在中间的元件。相反，当提到某元件“直接位于”另一元件上时，则没有中间元件。

图 1 是本发明第一实施例的用于液晶显示器的薄膜晶体管阵列面板线路图。

如图 1 所示，在本发明第一实施例用于液晶显示器的薄膜晶体管阵列面板中，多个栅极线 22 传输扫描信号和多个数据线 62 传送显示信号或图像信号，它们彼此相交叉。该栅极线 22 和数据线 62 定义了一个矩阵阵列中的多个象素。每个象素包括象素电极 82，通过数据线和薄膜晶体管 TFT 将图像信号加于该象素电极 82。该薄膜晶体管 TFT 的栅和源和漏电极分别连接到栅极线 22，数据线 62，和象素电极 82。此外，形成多个存储电极线 26 和 28，它们与栅极线 22 平行并且接收一电压例如是加到液晶显示器上面板的公共电极(未示出)的公共电压。该存储电极线 26 和 28 为双线结构，通过存储电极 27 彼此相连接，并且它们平行于该数据线 62。通过重叠该象素电极 82，存储线路 26, 27 和 28 提供存储电容。在垂直方向形成的存储线路连接线 84 至少电连接邻近象素的存储线路 26, 27 和 28，而冗余修复线 68，它的两端重叠存储线路 26, 27 和 28 以及形成邻近象素。

在本发明的用于液晶显示器的薄膜晶体管阵列面板中，因为邻近象素

的存储线路 26, 27 和 28 至少是通过存储线路连接线 84 彼此相连接，从而使加到存储线路 26, 27 和 28 的存储电容的电压变化可降至最低，这将导致减少它的畸变，从而使串扰和闪烁减至最少。

此外，在本发明的用于液晶显示器的薄膜晶体管阵列面板中，如果栅极线 22 或数据线 62 分别断开时，断开的线路可通过使用冗余修复线 68，存储线路 26, 27 和 28 以及存储线路连接线 84 修复。这将参考图 1 在下面讨论。

例如，如果数据线 62 在 A 部断开，重叠数据线 62 的 C 部和 A 部两侧的存储电极线用激光短路，而重叠存储电极线 26 和 28 的 B 部和 A 部左侧的冗余修复线用激光短路。因此传送到断开数据线 62 的图像信号通过冗余修复线 68 以及存储电极线 26 和 28 重新布线。此时，在 B 和 C 之间的两侧部分外存储电极线 26 和 28 的 D 部(用 X 表示)被切断从而防止图像信号传送到所有的存储线路 26, 27 和 28 中。

作为另一个例子，如果栅极线 22 在 E 部损坏，重叠栅极线 22 的 F 部和 E 右侧上的存储线路连接线 84，和重叠冗余修复线 68 的 H 部和 E 部左侧上的存储电极线 26 分别使用激光短路。因此，传送到断开栅极线 22 的扫描信号通过该冗余修复线 68，存储电极线 26 和存储连接线 84 改变路线。此时，在 H 部和 F 部之间的两侧部分之外，存储电极线 26 的 G 部(用 X 表示)；连接 F 部和 H 部间的存储电极线 26 的存储电极线 27；和在 F 部与存储电极线 28 之间的存储线路连接线 84 均断开，从而防止扫描信号传送到该存储线路 26, 27 和 28。冗余修复线可只用于修复栅极线 22 的断开而不使用存储线路连接线 84。

其中，该冗余修复线 68 和该存储线路连接线 84 可以在彼此相同的层和与该象素电极 82 或数据线路 62 相同的层上形成，或在不相同的层上形成。在本发明该实施例中，该存储线路 26, 27 和 28 是在与栅极线 22 相同的层上形成，该冗余修复线 68 是在与该数据线 62 相同层上形成，而该存储线路连接线 84 是在与该象素电极 82 的相同层上形成。这将参考图 2 和 3 详细讨论。

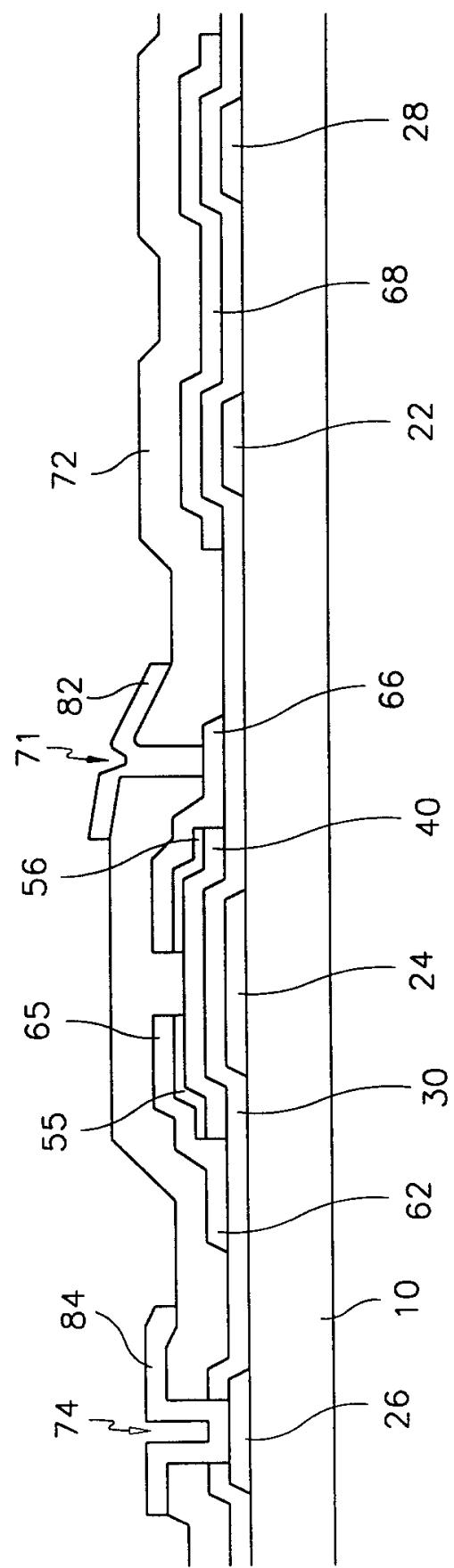

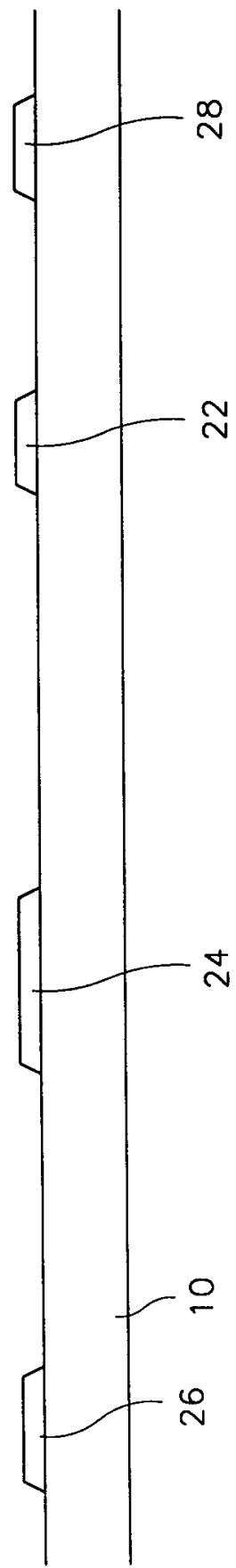

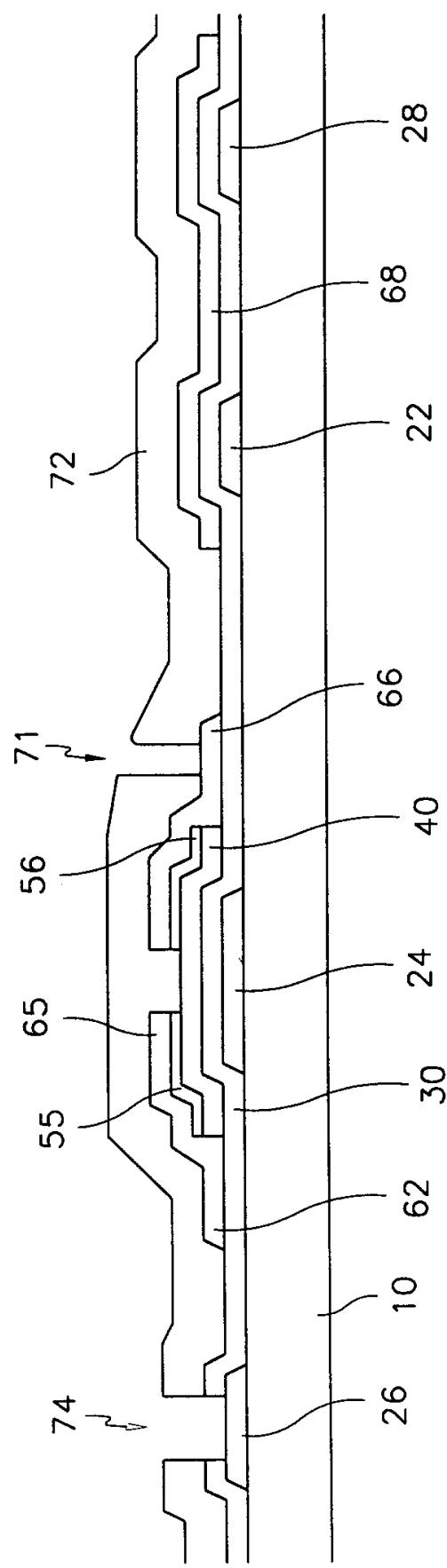

图 2 是本发明第一实施例的用于液晶显示器的薄膜晶体管阵列面板示意图，而图 3 是沿图 2 III-III 线形成的截面图。

如图 2 和 3 所示，金属或例如铝(Al)或铝合金，钼(Mo)或钼-钨(MoW)，

铬(Cr), 和钽(Ta)导电材料的栅极线路和存储线路是在绝缘衬底 10 上形成。5 棚极线路包括沿图 1 水平方向延伸并且传送扫描信号的棚极线(或扫描线)22 以及包括棚电极 24, 它是棚极线的一部分和是薄膜晶体管的一个端点。棚极线路(gate wire)还包括连接到棚极线 22 一端。棚极线路和把外部电路的

10 扫描信号传送到棚极线 22 的衬垫。存储线路(storage wire)包括与棚极线 22 平行地构成的存储电极线 26 和 28, 并且它具有双结构(dual structure)以及包括将存储电极线 26 和 28 彼此连接的存储电极 27。把例如公共电压的电

15 压加到该液晶显示的上面板的公共电极(未示出)。存储线路 26, 27 和 28 与象素电极 82 一并提供存储电容以提高液晶显示电容的容量, 这将在后面描述。

当棚极线路部分 22, 24 和存储线路部分 26, 27 和 28 是用多层构成时, 棚极线路部分 22 和 24 以及存储线路部分 26, 27 和 28 可具有多层结构以及单层结构, 最好是相对于象素电极用低电阻率的材料制造一个层和用良好接触特性的另一材料, 特别是 ITO(铟锡氧化物)制造另一层。这是因为该线路与用于象素电极的 ITO 一起使用时, 增强衬垫部分与外部的电连接。

15

在棚极线路部分 22 和 24 以及存储线路部分 26, 27 和 28 上形成硅氮化物( $\text{SiN}_x$ )的棚隔离层 30 并且将它们覆盖。

半导体图形 40(例如氢化物非晶硅半导体制作的)在棚绝缘层 30 上形成。欧姆接触层图形 55 和 56(象用磷杂质重掺杂的非晶硅材料制造的)是在

20 半导体图形 40 上形成。

由例如钼或钼钨、铬、铝或铝合金、以及钽导电材料制作的源和漏电

25 极 65 和 66 是在欧姆接触层图形 55 和 56 上形成。数据线 62 在棚绝缘层 30 上形成, 沿图 2 垂直方向延伸, 数据线 62 连接到源电极 65 并且和棚极线 22 一起定义一象素。数据线路部分 62, 65 和 66 还包括连接到数据线 62 一端的数据衬垫。数据衬垫把来自外部的图像信号传送到数据线。此外与数据

25 线路部分 62, 65 和 66 相同层的冗余修复线 68 其各端重叠邻近象素列的存储电极线 26 和 28, 该冗余修复线 68 是在绝缘层 30 上沿图 2 垂直方向形成的。如上所述, 存储线路连接线 84(参考图 1)也可与冗余修复线 68 一并在

和数据线路部分 62, 65 和 66 的相同层的绝缘层 30 上形成。

30 数据线路部分 62, 65, 和 66 以及冗余修复线 68 也可象棚极线路部分 22 和 24 以及存储线路 26, 27 和 28 一样具有多层结构。当然, 在数据线具有

多层结构时，最好是，用低电阻率材料制作一个层和用良好接触特性的另一材料制作另一层。

钝化层(passivation layer)72 是在数据线路部分 62, 65 和 66 以及半导体图案 40 上形成，它没有被数据线路部分 62, 65, 和 66 覆盖。钝化层 72 具有露出漏电极 66 的接触孔 71 以及含有与栅绝缘层一起露出的该存储电极线 26 和 28 的接触孔 74。钝化层 72 可用例如  $\text{SiN}_x$ ，丙烯有机材料，其它透明有限光材料或其他有机材料制成。

接收图像信号并与上面板公共电极一起产生电场的象素电极 82 是在钝化层 72 上形成，象素电极 82 是由例如铟锡氧化物(ITO)或铟锌氧化物(IZO)的透明导电材料制作的并通过接触孔 71 连接到漏电极 66。此外，通过钝化层 72 和栅绝缘层 30 的接触孔 74 用于连接邻近存储线路 26, 27, 和 28 的存储线路连接线 84 是在与象素电极 82 相同层上形成。另一方面钝化层还可具有接触孔用于露出栅衬垫和数据衬垫，和通过接触孔连接栅极和数据衬垫的冗余栅和数据衬垫可在与象素电极 82 相同的层上形成。

同时，如图 2 所示，使用存储线路 26, 27 和 28 作为光阻挡层以便阻止在邻近象素电极 82 的边沿部分上泄露光。为了增大 LCD 的宽视角，最好使液晶分子以多畴结构(multi-domain configuration)排列。为了获得这样一种结构，象素电极可具有不同的象素分配图形(pixel division pattern)。其中，象素电极通过提供一个条纹区(fringe field)可具有用圆角(rounded corners)连接的多个矩形，矩形开口图形，矩齿形或十字形以便按多畴结构排列液晶分子。为了实现最佳视角，最好是把单元象素分为四个范畴。为了实现稳定的分配顺序，最好是除了在多畴边界外不产生不受欢迎或不均匀的纹理，和最好是使由该形状限定的邻近范畴中的液晶分子的方位(director)按 90 口角排列。此时，泄漏光是由于不受欢迎和不均匀的纹理产生的，以及存储线路 26, 27 和 28 可具有各种图形。当然，相对于象素电极 82 的公共电极(未示出)依据该象素电极 82 的图形可具有各种开口图形(opening pattern)。

在本发明的这种结构中，冗余修复线路 68 或存储线路连接线 84 定位在各象素区，并且也可定位在许多象素区的每个中。

在该实施例中，采用透明的 ITO 作为象素电极 82 的样品材料，但是，不透光的导电材料也可用在反射型液晶显示中。

下面，相关于本发明第一实施例的用于液晶显示器的薄膜晶体管阵列

面板的制造方法将参考附图进行描述。

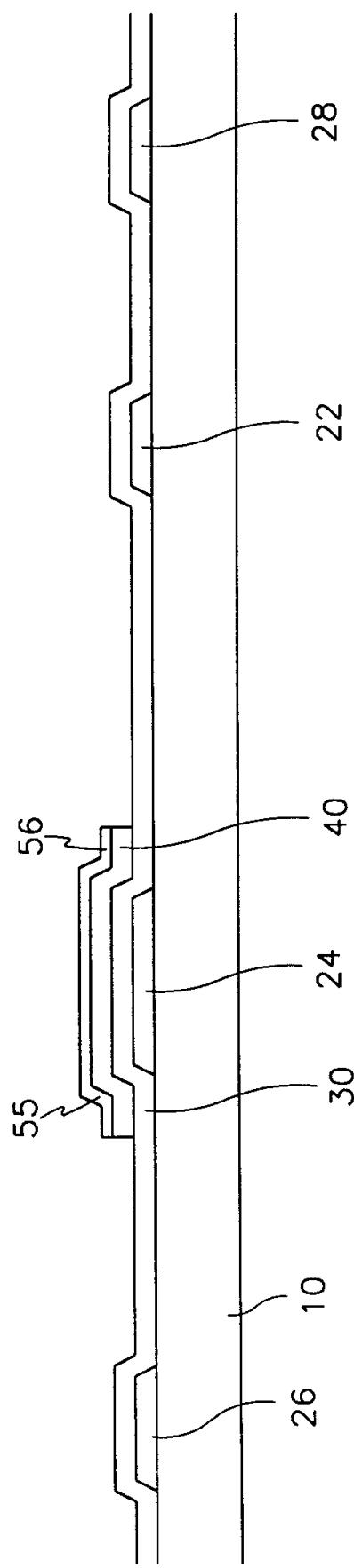

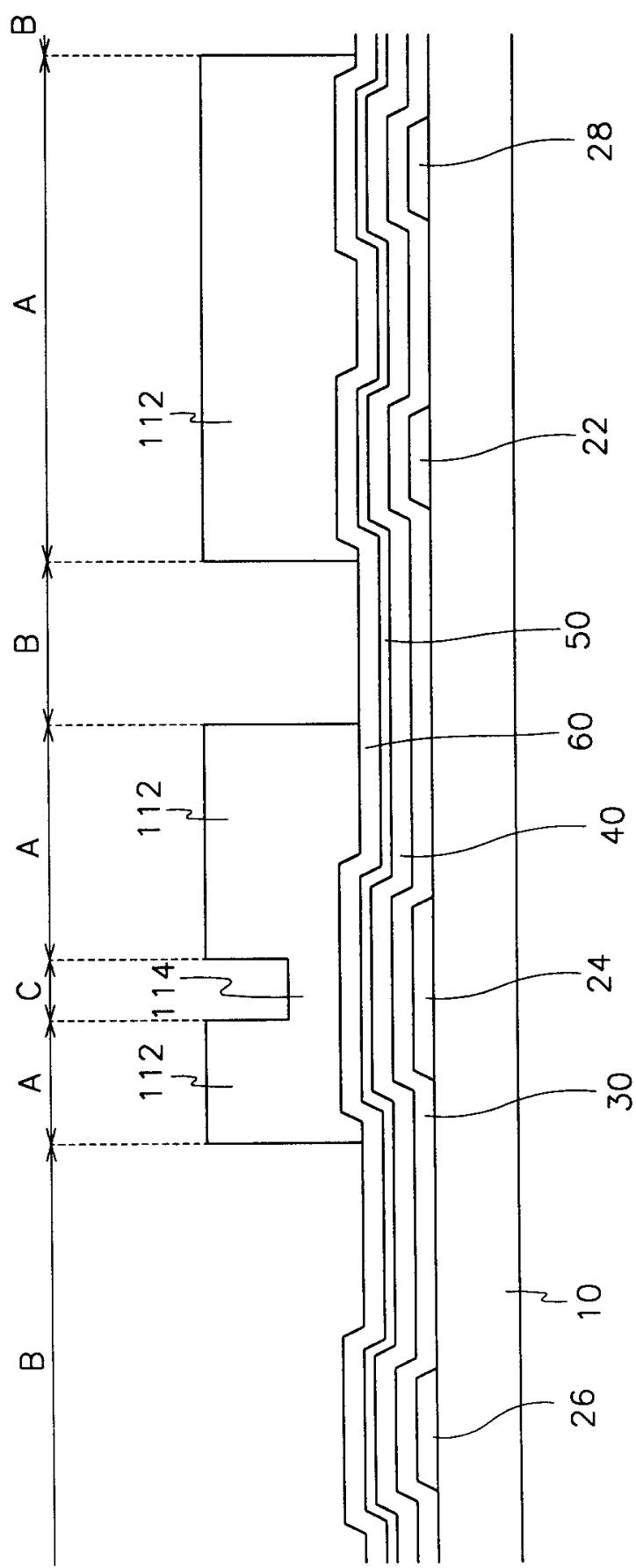

图 4A 到 4D 是根据本发明第一实施例制造的用于液晶显示器的薄膜晶体管阵列面板的截面图。

首先，如图 4A 所示，设置一含有低电阻率的导电层并且构图，从而在 5 绝缘衬底 10 上用掩模通过光刻法形成包括栅极线 22 和栅电极 24 的栅极线路部分以及包括存储电极线 26, 28 和存储电极(参考图 2)的存储线路部分。

接着，如图 4B 所示，由例如硅氮化物绝缘材料制造的栅极绝缘层 30，又如非晶硅半导体材料制造的半导体层 40，和如掺杂非晶硅导电材料制造的欧姆接触层 50 是通过化学汽相沉积法顺序形成的层，使用掩模图案法在 10 栅电极 24 顶部并对应栅绝缘层 30 形成两个成岛形的半导体层 40 和欧姆接触层 50。

再如图 4C 所示，用掩模通过光刻法由溅射和构图沉积低电阻率的导电层，以便形成数据线路 62, 65 和 66(参考图 2)和冗余修复线 68。

然后，通过利用数据线路 62, 65 和 66 作掩模蚀刻欧姆接触层 50 以便 15 分开欧姆接触层图案 55 和 56，并使源电极 65 和漏电极之间的半导体层 40 露出。

再如图 4D 所示，通过沉积如硅氮化物( $\text{SiN}_x$ )，或硅氧化物的无机绝缘材料或有机绝缘材料和与栅绝缘层 30 一并构图形成钝化层 72，从而各形成接触孔 71 和 74 用以露出漏电极和存储线路 26, 27 和 28(参考图 2)。

接着如图 2 和 3 所示，用掩模通过光刻沉积和蚀刻透明导电层 IZO 或 20 ITO，从而形成像素电极 82 和存储线路连接线 84。

另一方面，参考附图将描述本发明一实施例利用四种掩模制造液晶显示薄膜晶体管阵列面板的方法。

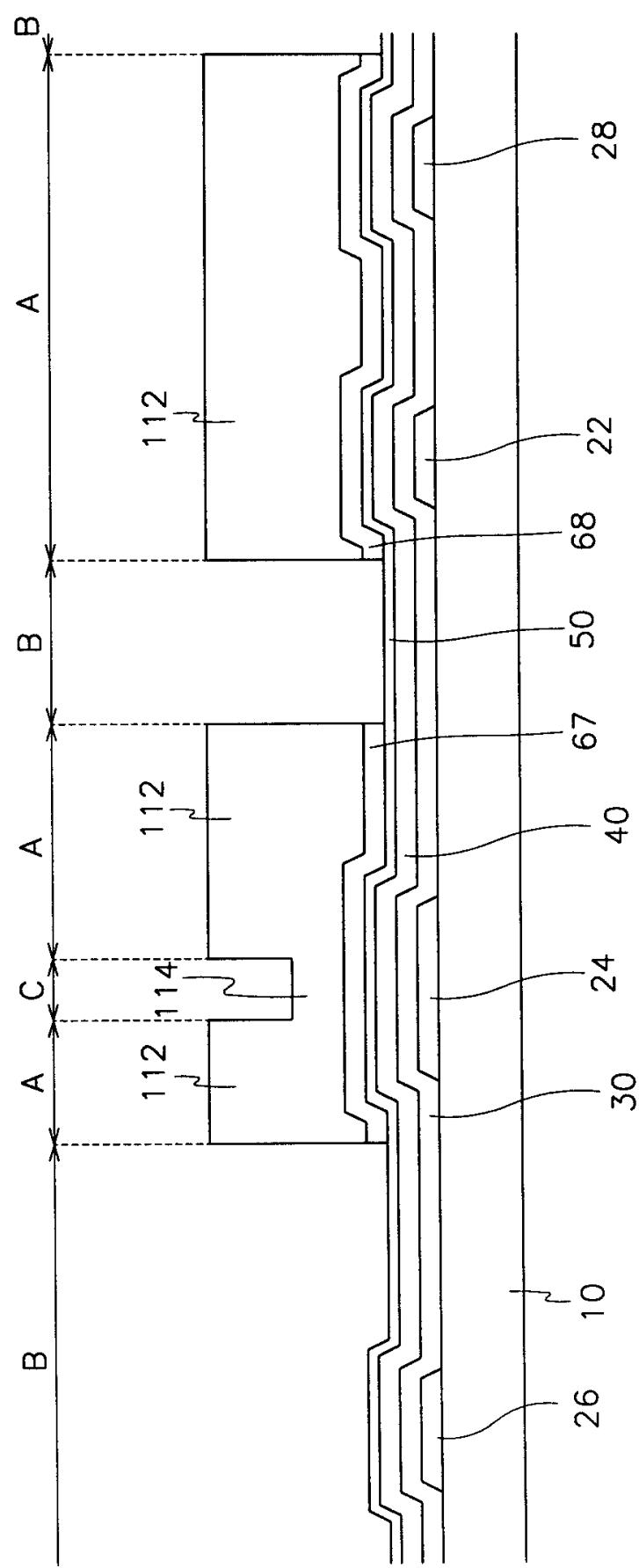

图 5A 到 5G 是根据本发明第一实施例用另一种方法制造的用于液晶显示 25 器的薄膜晶体管阵列面板的截面图。

首先，如图 5A 所示，通过光刻法用干或湿蚀刻导电层沉积和构图含有低电阻率的导电层从而形成栅极线路部分 22 和 24，以及存储线路部分 26, 27 和 28。

再，如图 5A 所示，通过如化学汽相沉积法(CVD)分别顺序沉积栅绝缘 30 层 30，半导体层 40，和欧姆层 50。然后，通过例如溅射法沉积导电层 60 并且将具有  $1\mu\text{m}$  到  $2\mu\text{m}$  厚度的光刻胶层涂在导电层 60 上。

之后，通过第二掩模曝光该光刻胶层并显影从而形成图 5B 所示光刻图案 112 和 114。此时，定位在源电极 65 和漏电极 66 之间即，薄膜晶体管沟道部分 C 的光刻图案第一部分 114 薄于定位在将形成数据线路部分 62, 65, 66 和冗余修复线 68 的 A 部的光刻图案第二部分 112 如图 5B 所示。因此，

5 定位在 B 部分的光刻图案第三部分或保留部分薄于第一部分。该第三部分可具有随蚀刻法而变化的厚度。例如，当使用湿蚀刻时第三部分实际为零厚度，但是，当使用干蚀刻时第三部分可为非零厚度。此时第一部分 114 和第二部分 112 之间厚度比取决于后面将要讨论的蚀刻条件。然而，最好是使第一部分 114 的厚度等于或小于第二部分 112 厚度的一半。

10 有许多方法可使光刻胶层厚度随位置变化，通过例如形成缝隙或格子图案，或在掩模上提供部分透射光层，可以控制部分入射光量。

此时，最好使缝隙大小和缝隙之间的不透光部分小于曝光器件的分辨率。当采用部分透光(partly-transparent)层时，减少曝光量，可采用包括具有不同透射率或含有各种厚度的膜的掩模。

15 当通过该掩模曝光光刻胶层时，光刻胶层的聚合物通过光蜕变。当直接曝光的部分聚合物全部蜕变时，曝光步骤完成。然而，因为入射光量小于直接曝光部分的光量，通过缝隙图案曝光的光刻胶层部分的聚合物没有全部蜕变。通过阻挡层没有曝光的光刻胶层的聚合物难于蜕变。当显影该光刻胶层时，难于蜕变的光刻胶层部分几乎被保留，和在以小于接受全曝

20 光该部分的光量曝光该部分时，保留一薄的部分，但是，如果该曝光时间太长，光刻胶层全部聚合物蜕变。因此，这种过曝光应避免。

通过形成由光敏材料和回流(reflowable)材料制作的光刻胶层或形成薄部分 114，以便经过分别具有实质透光部分和实质不透光部分的掩模对光刻胶层曝光从而形成具有零和非零厚度部分的光刻图案，和回流光刻胶以使

25 流入零厚度部分从而形成新光刻图案。

再回到图 5C，接着对光刻图案 114 和包括导电层 60，欧姆接触层 50，和半导体层 40 的各层进行蚀刻处理。当完成该处理时，除沟道 C 部分半导体层外可保留数据线路和冗余修复线以及 A 部下的各层。另外，在其余的 B 部中有三个层 60, 50, 和 40 从该栅绝缘层 30 去除。

30 如图 5C 所示，通过去除其上的导电层 60 露出 B 部的欧姆接触层 50。此时，可采用湿和干的两种蚀刻，和最好是在使导电层 60 被蚀刻而光刻胶

层 112 和 114 不蚀刻条件下完成蚀刻。然而，因为在干蚀刻时难于实现它，所以可以在光刻图案 112 和 114 也被蚀刻的条件下完成蚀刻。在该情况下，第一部分 114 可比湿蚀刻时厚以使导电层 60 不露出。

如果导电层是由钼或钼钨合金，铝或铝合金或钽制作，可采用干或湿蚀刻。但是，如果导电层 60 是由铬制作，最好采用湿蚀刻，因为铬不易通过干蚀刻去除。可用  $\text{CeNHO}_3$  作为用于蚀刻铬导电层 60 的湿腐蚀剂。可用  $\text{CF}_4$  和  $\text{HCl}$  或  $\text{CF}_4$  和  $\text{O}_2$  的混合气体系统来干蚀刻钼或钼钨导电层 60 并且在该情况下，在光刻胶层上后者系统的蚀刻速度类似于导电层 60 的蚀刻速度 (etch rate)。

参考图 5C，相关于源/漏电极在沟道 C 部和 A 部分保留了光刻胶层 112 和 114 下面的导电体 67 的部分，而 B 部分的其余导电层 60 全部被去除以露出其下面的欧姆接触层 50。此时除了源电极 65 和漏电极 66 彼此连接外导电体图案 67 和 68 与数据线路部分 62, 65 和 66 以及冗余修复部分 68 具有相同的层。当采用干蚀刻时，还将光刻胶层 112 和 114 蚀刻到一定厚度。

其次，在 B 部分露出的欧姆接触层 50 的部分和半导体层 40，在图 5D 可看出通过干蚀刻它们与光刻胶层的第一部分 114 一起被去除。蚀刻条件可以是这样的即，光刻图案 112 和 114，欧姆接触层 50 以及半导体层全部被蚀刻(半导体层和欧姆接触层几乎具有同样的蚀刻速度)，但，栅绝缘层 30 必须不能蚀刻。最好使光刻图案 112 和 114 与半导体层 40 的蚀刻速度几乎相同。例如用  $\text{SF}_6$  和  $\text{HCl}$  或  $\text{SF}_6$  和  $\text{O}_2$  的混合气体系统产生上述蚀刻。此时，如果光刻图案 112 和 114 以及半导体层 40 几乎具有相同的蚀刻速度，第一部分 114 的厚度是等于或小于半导体层 40 和欧姆接触层 50 的总和厚度。

然后，如图 5D 所示，通过去除沟道 C 部分的第一部分 114 露出导电体图案 67，通过去除 B 部分的欧姆接触层 50，和半导体层 40 露出栅绝缘层 30。此时，A 部上的第二部分 112 的厚度通过蚀刻被减少。另外，在该步骤获得完整的半导体图案 40。

然后在导电体图案 67 上的其余光刻胶层通过消失(ashing)或等离子区蚀刻被去除。

下面，如图 5E 所示，在沟道部分 C 相对于源/漏电极的导电体图案 67 和图 5E 中相对于源/漏电极的欧姆接触层通过蚀刻被去除。此时，有可能通过干蚀刻方法来蚀刻导电体图案 67 和欧姆接触层 50 或通过湿蚀刻方法

来蚀刻导电体图案 67 和通过干蚀刻法来蚀刻欧姆接触层 50。在前者情况下最好在导电体图案 67 和欧姆接触层图案 50 之间采用蚀刻选择性大的蚀刻条件。这是因为如果蚀刻选择性不足够大时难于检测到蚀刻端点和难于控制围绕沟道 C 部的半导体图案 40 的厚度。这可通过使用例如  $SF_6$  和  $O_2$  的 5 混合气体系统实现。在后者顺序进行湿蚀刻和干蚀刻的情况下，尽管干蚀刻的这些欧姆接触层图案 50 难于被全部蚀刻，经过湿蚀刻的导电体图案 67 的横向侧也被蚀刻。因此该两个图案 67 和 50 的轮廓形成阶梯形。该  $CF_4$  和  $O_2$  或  $CF_4$  和  $HCl$  的混合气体系统是用于蚀刻欧姆接触层图案 50 和半导体图案 40 的蚀刻气体系统的一个例子。半导体图案 40 通过用  $CF_4$  和  $O_2$  混 10 合气体系统的蚀刻也可再形成具有均匀厚度的图案。此时，如图 5E 所示，半导体图案 40 的厚度可减少并且光刻图案的第二部分 112 可被蚀刻到一定厚度。蚀刻条件也可不用来设定蚀刻该栅绝缘层 30，但最好是使光刻图案足够厚以使不露出数据线路部分 62, 65, 66 兀余修复线 68。

其结果，是将源电极 65 和漏电极 66 分开和获得其下面的全部数据线路部分 62, 65, 66 和冗余线 68 以及全部接触层图案 55 和 56。 15

接着，去除数据线路上的光刻胶层其余第二部分 112。但是该第二部分 112 的去除是在关于沟道 C 部分上的源/漏电极，去除导电体图案 67 的步骤之后和在去除导电体图案 67 下的欧姆接触层图案 50 的步骤之前进行。

总之，该处理能够通过依次使用湿蚀刻和干蚀刻两种或只使用干蚀刻 20 实现。

在前者情况下，通过湿蚀刻首先去除 B 部分的导电层，然后通过干蚀刻去除其下面的欧姆接触层和半导体层。此时，C 部的光刻胶层被消耗一定厚度，和 C 部可以有或可以没有任何留下的残余光刻胶，这实际上取决于 C 部光刻胶层原来的厚度。当 C 部有留下的残余光刻胶时，该残余光刻胶可通过消失(ashing)取消。最后，湿蚀刻该 C 部导电层以将源和漏电极分开并通过使用干蚀刻去除 C 部的欧姆接触层。 25

在后者情况下，通过干蚀刻去除 B 部欧姆接触层和半导体层。如同在前者的情况下 C 部可以有或可以没有任何留下的残余光刻胶，当 C 部有残余光刻胶时，通过消失(ashing)去除残余光刻胶。最后干蚀刻 C 部导电层从而使源和漏电极分开，并通过使用干蚀刻去除 C 部欧姆接触层。 30

此外，如果蚀刻数据线路，半导体图案，接触层图案，和数据线部可

在同一时间实现相同阶梯。这就是说，最好是干蚀刻 C 部下面的光刻图案 114 和接触层 50，和在干蚀刻 B 部的导电层和欧姆接触层及半导体层期间干蚀刻 A 部光刻图案 112 的部分。

5 因为，后者的处理只使用一种干蚀刻法所以尽管它难于实现合适的蚀刻条件，但它比较简单。另一方面，后者的处理尽管更复杂但它具有容易实现合适的蚀刻条件的优点。

在通过上述步骤形成数据线路部分 62, 65, 66 和冗余修复线 68 之后，通过如图 5F 所示的化学汽相淀积(CVD)法形成钝化层 70。

10 接着，用掩模通过光刻处理沿栅绝缘层 30 来构图钝化层 70 从而形成接触孔 71 和 74 用于分别露出漏电极 66 和存储线路，如图 5G 所示。

其次，如上所述，淀积 IZO 层或 ITO 层并使用掩模蚀刻从而形成连接漏电极的像素电极 82。此时，通过接触孔 74 存储线路连接线 84 电连接邻近像素的存储线路 26, 27 和 28。

15 在该实施例中，具有与第一实施例相同的效果，通过一种光刻处理形成数据线路部分 62, 65, 66 和冗余修复线 68，欧姆接触层图案 55 和 56 以及半导体图案 40，使薄膜晶体管阵列面板的制造方法可以简化。

20 在该情况下，依据数据线路 62, 65, 66 形成的半导体层 40，欧姆接触层图案 55 和 56 不同于图 2 和 3 中的结构。欧姆接触层图案 55 和 56 具有与数据线路部分 62, 65, 66 相同的图案。除了源电极 65 和漏电极 66 之间的三道部分外的半导体层 40 具有与数据线路部分 62, 65 和 66 以及欧姆接触层图案 55 和 56 相同的图案。当然，半导体层和欧姆接触层可在冗余修复线下面保留。

25 依据含有存储线路连接线的第一实施例的薄膜晶体管阵列面板可以用作为双扭式向列相(TN)模式液晶显示的一面板或用作为垂直对准(VA)模式的液晶显示的一面板。

图 6 是本发明第一实施例的液晶显示薄膜晶体管阵列面板电路图。

如图 6 所示，多个栅极线 22 传送扫描信号以及多个数据线传送显示信号或图像信号，多个栅极线 22 与多个数据线彼此跨越。栅极线 22 和数据线 62 定义了一矩阵阵列中多个像素。每个像素包括一薄膜晶体管 TFT，该薄膜晶体管含有连接栅极线 22 的栅电极 24；连接数据线 62 的源电极 65；和连接像素电极的漏电极 66。此外，各像素电极包括存储电容器  $C_{st}$  和液晶

电容器  $C_{LC}$ ，该存储电容器  $C_{st}$  产生成储电容并含有两个象素电极端 82 以及存储电极线 26 和 28，该液晶电容器  $C_{LC}$  产生液晶电容并含有两个象素电极端 82 以及一个公共电极(未示出)，该公共电极在液晶显示的上面板形成。在垂直方向形成多个存储线路连接线 84 至少电连接邻近象素的存储线路 26, 5 27 和 28。这里，存储线路连接线 84 是在各象素中形成的。

另一方面，共面交换模式(in-plane switching mode (IPS))液晶显示薄膜晶体管阵列面板含有象素电极和公共电极，它们由相同面板形成，从而构成重排液晶分子的电场，该液晶显示薄膜晶体管面板阵列可具有至少电连接邻近象素的存储线路的存储线路连接线，下面参考图 7 和 8 描述该液晶 10 显示薄膜晶体管面板阵列。

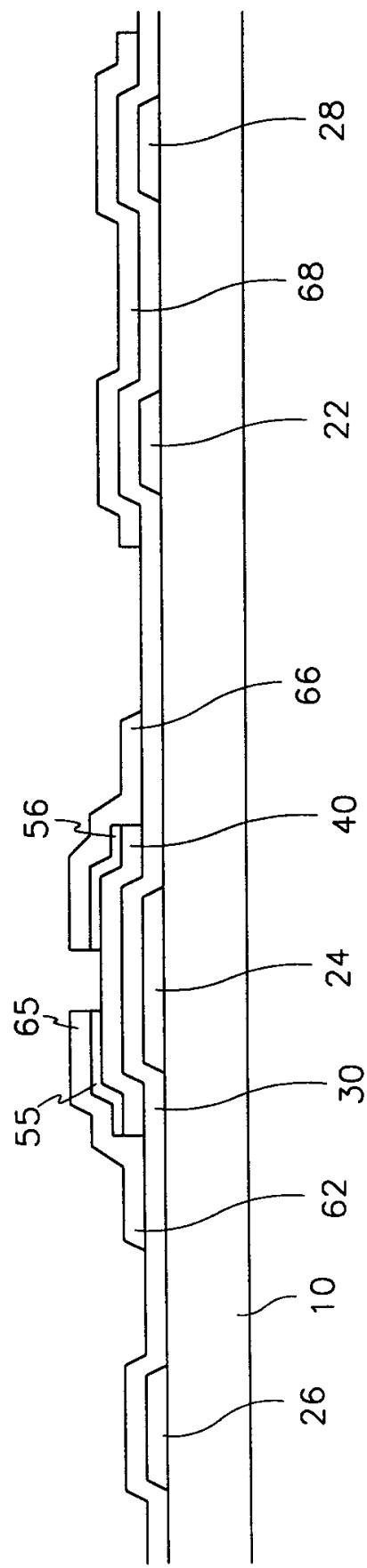

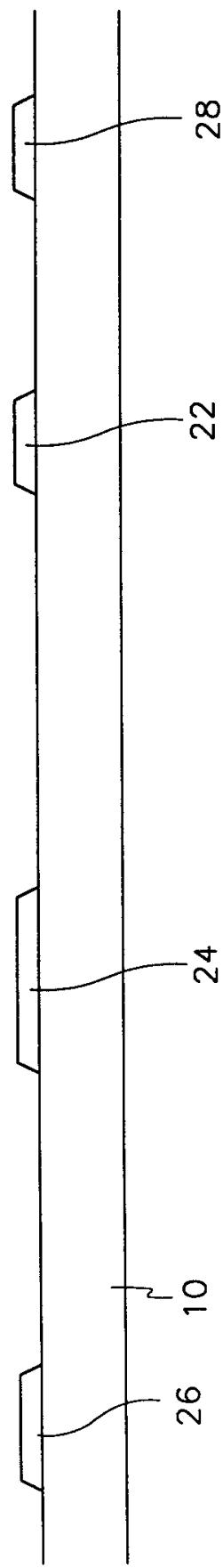

图 7 是本发明第二实施例的用于液晶显示器的薄膜晶体管阵列面板略图和图 8 是沿图 7 线 VIII-VIII'获得的截面图。

如图 7 和 8 所示，在绝缘衬底 10 上形成金属或导电材料的栅极线路和公共线路。栅极线路包括了沿图 7 水平方向延伸的栅极线(或扫描线)22，该 15 栅极线用于传送扫描信号，和包括栅电极 24，它是栅极线的一部分并且是薄膜晶体管的一端点，还包括连到栅极线 22 一端的栅极衬垫，它向栅极线 22 传送来自外部电路的扫描信号。公共线路包括公共电极线 23 和 29，它们平行于栅极线 22 构成并具有双结构，以及包括连接两个存储电极线 23 和 29 的公共电极 21。存储线路 23 和 29 与象素电极电极线 63 和 69 一并提供存储电容。以提高液晶显示电容的容量，下面将进行讨论。

在栅极线路部分 22, 24 和 25 以及存储线路部分 21, 23 和 29 上形成硅 20 氮化物( $SiN_x$ )的栅绝缘层 30，并且将上述该些部分覆盖。

在栅绝缘层 30 上形成半导体图案 40(由例如氢化非晶硅半导体制作)。在半导体图案 40 上形成欧姆接触层图案 55 和 56(如用磷杂质重掺杂的非晶 25 硅材料制作)。此处，半导体图案 40 随数据线 62 在垂直方向延伸，下面将对其进行描述，在半导体图案 40 上彼此重叠了栅极线 22 和数据线 62 的半导体图案 40 的部分宽余半导体图案 40 的不同部分以使减少数据线 62 的断开。

在欧姆接触层图案 55 和 56 上形成用导电材料制作的源和漏电极 65 和 30 66。图 7 中沿垂直方向延伸的数据线 62 形成在栅绝缘层 30 上，该数据线 62 连接源电极 65 和与栅极线 22 一并限定了一象素。数据衬垫向数据线 62 传

送来自外部电路的图像信号。此外，在栅绝缘层 30 上形成的象素线路部分包括沿水平方向延伸的象素电极线 63 和 69 以及通过叠加公共电极线 23 和 29 它提供存储电容；还包括连接象素电极线 63 和 69 的象素电极 61 它与公共电极 21 一并产生几乎平行于衬底 10 的电场从而控制液晶分子。象素线路部分 61, 63 和 69 连接漏电极 66。在图 7 垂直方向在栅绝缘层 30 上和在与数据线路部分 62, 64, 65 和 66 相同层上可形成的冗余修复线 68，它的两端重叠邻近象素列的公共电极线 22 和 29。如上所述，存储线路连接线 84(参考图 1)也可在栅绝缘层 30 上和在与数据线路部分 62, 64, 65 和 66 相同的层上形成。

在数据线路部分 62, 64, 65, 和 66 以及未被数据线路部分 62, 64, 65 和 66 覆盖的半导体图案 40 上形成钝化层 72。钝化层 72 有用于露出公共电极线 23 和 29 的接触孔 74；和用于露出栅极衬垫 25 和数据衬垫 64 的接触孔 75 和 78 以及与栅绝缘层 30 一起的接触孔 76。

在钝化层 72 上形成例如用金属的导电材料制作的冗余数据线路部分。冗余数据线路包括通过接触孔 76 连接数据线的冗余数据线 80；和通过接触孔 78 连接数据衬垫 64 的冗余数据衬垫 88。此外，在钝化层 72 上形成冗余栅极衬垫 85 和公共线路连接线 84，其中，冗余栅极衬垫 85 通过接触孔 75 连接栅极衬垫 25；公共线路连接线 84 通过钝化层 72 和栅绝缘层 30 的接触孔 74 连接邻近公共线路 21, 23, 和 29。冗余数据线路 80 和 88，和冗余栅极衬垫可以是由例如铟锡氧化物(ITO)或铟锌氧化物(IZO)的透明导电材料形成的，以提高衬垫部分的可靠性。

其次，本发明第二实施例的制造液晶显示薄膜晶体管阵列面板的方法将参考附图对其描述。

本发明第二实施例的大部分制造方法与第一实施例的方法相同。然而，当形成栅极线路 22, 24 和 25 时，形成公共线路 21, 23 和 29，以及当形成数据线路 62, 64, 65 和 66 时形成象素线路 61, 63 和 69。然后，在钝化层 72 上形成冗余数据线路 80, 85, 和 88。

图 9 是本发明第二实施例的用于液晶显示器的薄膜晶体管阵列面板的电路图。

第二实施例的大部分结构与图 6 第一实施例的结构相同。但是，存储电容器  $C_{st}$  和液晶电容器  $C_{LC}$  的两端是分别连接到象素线路 63 和 69 以及公

共线路 23 和 29 的。

在本发明中，通过至少连接彼此邻近象素的存储线路形成的存储线路连接线，可以使存储电容的电压变化减至最低，这将导致减少畸变，从而使串扰和闪烁减至最少。此外，通过使用冗余修复线和存储线路连接线可以容易修复栅极线和数据线断开的缺陷。

在附图和说明书中已经公开本发明典型的最佳实施例并且，虽然采用了具体的术语他们只用于描述本发明而不是对本发明的限制，本发明的范围陈述在下面的权利要求中。

# 说 明 书 附 图

图 1

图 2

图 3

图 4A

图 4B

图 4C

图 4D

图 5A

图 5B

图 5C

图 5E

图 5F

图 5G

图 6

图 7

图 8

9

|                |                                                                                                 |         |            |

|----------------|-------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于液晶显示器的薄膜晶体管阵列面板                                                                               |         |            |

| 公开(公告)号        | <a href="#">CN1304055A</a>                                                                      | 公开(公告)日 | 2001-07-18 |

| 申请号            | CN00137010.3                                                                                    | 申请日     | 2000-11-06 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                        |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                                                                        |         |            |

| [标]发明人         | 朴云用                                                                                             |         |            |

| 发明人            | 朴云用                                                                                             |         |            |

| IPC分类号         | G02F1/136 G02F1/1362 G02F1/1368 H01L21/77 H01L21/84 H01L27/12 H01L27/13 H01L29/786 G02F1/133    |         |            |

| CPC分类号         | H01L27/1214 G02F1/136213 H01L27/13 H01L27/1288 H01L27/12 G02F2001/136272 H01L27/124 H01L27/1255 |         |            |

| 优先权            | 1019990048842 1999-11-05 KR<br>1020000057036 2000-09-28 KR                                      |         |            |

| 其他公开文献         | CN1163964C                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                  |         |            |

### 摘要(译)

一种用于液晶显示器的薄膜晶体管阵列,包括:栅极线路,该栅极线路包括在水平方向形成的栅极线;数据线路,该数据线路包括在垂直方向形成的数据线,其中数据线路与栅极线路相交叉并与该栅极线路绝缘;象素电极,该象素电极是在通过该栅极线和数据线相交叉限定的象素中形成,用于通过数据线接收图像信号;存储线路,该存储线路,包括存储电极线和连接存储电极线的存储电极,其中,存储线路通过重叠象素电极形成存储电容;和存储线路连接线,至少连接该存储线路到一邻近象素。