[12] 发明专利申请公开说明书

G02F 1/133 H01L 29/786

[21] 申请号 200410047727.1

[43] 公开日 2004 年 10 月 27 日

[11] 公开号 CN 1540426A

[22] 申请日 2004.4.5

[74] 专利代理机构 北京市柳沈律师事务所

[21] 申请号 200410047727.1

代理人 陶凤波 侯 宇

[30] 优先权

[32] 2003.4.4 [33] KR [31] 0021311/2003

[71] 申请人 三星电子株式会社

地址 韩国京畿道

[72] 发明人 金东奎

权利要求书 3 页 说明书 16 页 附图 9 页

[54] 发明名称 液晶显示器、所用的薄膜晶体管阵列板及其制造方法

[57] 摘要

本发明公开了一种液晶显示器、所用的薄膜晶体管阵列板及其制造方法，该薄膜晶体管阵列板包括：形成在绝缘衬底上的栅极线；在栅极线上的栅极绝缘层；在栅极绝缘层上的半导体层；形成在栅极绝缘层上的数据线；至少部分地形成在半导体层上的漏极电极；形成在数据线和漏极电极上的第一钝化层；形成在数据线和漏极电极上的滤色器；形成在滤色器上的第二钝化层；以及形成在滤色器上的像素电极，其与漏极电极连接，与第二钝化层交叠，并且由第一钝化层封闭。

1. 一种薄膜晶体管阵列板，包括：

形成在绝缘衬底上的栅极线；

5     在栅极线上的栅极绝缘层；

在栅极绝缘层上的半导体层；

形成在栅极绝缘层上的数据线；

至少部分地形成在半导体层上的漏极电极；

形成在数据线和漏极电极上的滤色器；

10    形成在滤色器上的第一钝化层；以及

形成在滤色器上的像素电极，其与漏极电极连接，与第一钝化层交叠，

并且由第一钝化层封闭。

2. 如权利要求 1 所述的薄膜晶体管阵列板，其中第一钝化层与像素电极的交叠部分设置在数据线上。

- 15    3. 如权利要求 1 所述的薄膜晶体管阵列板，其中像素电极的边缘与第一钝化层交叠，并且第一钝化层具有开口，该开口具有位于像素电极边缘附近的边缘。

4. 如权利要求 1 所述的薄膜晶体管阵列板，其中数据线包括一对彼此相连且形成大约 45 度角的直线部分。

- 20    5. 如权利要求 1 所述的薄膜晶体管阵列板，还包括存储电极线，其形成在衬底上，并包括与像素电极交叠以形成存储电容器的展开部分。

6. 如权利要求 5 所述的薄膜晶体管阵列板，其中漏极电极包括与存储电极线的展开部分交叠的展开部分。

7. 如权利要求 1 所述的薄膜晶体管阵列板，其中第一钝化层包括有机绝缘体和无机绝缘材料中的至少一种。

- 25    8. 如权利要求 1 所述的薄膜晶体管阵列板，其中第一钝化层由光敏材料构成。

9. 如权利要求 1 所述的薄膜晶体管阵列板，还包括设置在滤色器与数据线之间的第二钝化层。

- 30    10. 如权利要求 1 所述的薄膜晶体管阵列板，其中第二钝化层具有露出至少部分漏极电极的接触孔，滤色器具有设置在漏极电极上的开口，像

素电极通过该开口和该接触孔连接漏极电极。

11. 如权利要求 1 所述的薄膜晶体管阵列板，还包括形成在部分栅极线或部分数据线上、由与像素电极相同的材料构成的辅助接触部分。

5 12. 如权利要求 1 所述的薄膜晶体管阵列板，其中数据线和漏极电极的整个底表面基本上设置在半导体层上，数据线和漏极电极具有与半导体层基本相同的平面形状，并且该半导体层包括未由数据线和漏极电极覆盖并且设置在源极电极与漏极电极之间的部分。

13. 如权利要求 1 所述的薄膜晶体管阵列板，其中第一钝化层和像素电极覆盖滤色器的整个表面。

10 14. 一种液晶显示器，包括：

第一衬底；

设置在衬底上的第一信号线；

设置在衬底上并且与第一信号线相交的第二线；

连接至第一和第二信号线的薄膜晶体管；

15 设置在第一衬底上的滤色器；

设置在滤色器上的绝缘层，其与第一和第二信号线及薄膜晶体管相对，并具有露出滤色器的开口；

设置在滤色器上的像素电极，其连接薄膜晶体管，与绝缘层交叠，并且基本上位于绝缘层的开口中；

20 第二衬底，其面对第一衬底，并且与第一衬底间隔开一间隙；

形成在第二衬底上的公共电极；

设置在公共电极上的光阻挡件；以及

填充在第一衬底与第二衬底之间的间隙中的液晶层。

25 15. 如权利要求 14 所述的液晶显示器，其中绝缘层和像素电极覆盖滤色器的整个表面。

16. 如权利要求 14 所述的液晶显示器，其中光阻挡件包括保持第一衬底与第二衬底之间间隙的第一部分以及比第一部分的厚度薄的第二部分。

17. 如权利要求 14 所述的液晶显示器，还包括设置在第一衬底与第二衬底之间并且保持第一衬底与第二衬底之间间隙的间隔体。

30 18. 如权利要求 17 所述的液晶显示器，其中该间隔体位于薄膜晶体管上。

19. 如权利要求 14 所述的液晶显示器，其中液晶层具有负介电各向异性，并且处于垂直排列。

20. 如权利要求 14 所述的液晶显示器，其中公共电极具有切去部分。

21. 一种薄膜晶体管阵列板的制造方法，该方法包括：

5 在衬底上形成多条栅极线；

在栅极线上形成第一绝缘层；

在第一绝缘层上形成半导体层；

至少在半导体层上形成多条数据线和漏极电极；

形成多个滤色器，每个滤色器包括红、绿和蓝色素中的一种；

10 至少在滤色器边缘上形成第二绝缘层，第二绝缘层与数据线相对设置；

以及

在滤色器上形成多个像素电极，使得像素电极和第二绝缘层覆盖滤色器的整个表面。

22. 如权利要求 21 所述的方法，还包括：

15 在数据线和漏极电极上形成第三绝缘层。

23. 如权利要求 21 所述的方法，其中第二绝缘层包括多个与栅极线相对设置的部分。

## 液晶显示器、所用的薄膜晶体管阵列板及其制造方法

### 5 技术领域

本发明涉及一种液晶显示器、用于该液晶显示器的薄膜晶体管阵列板及其制造方法。

### 背景技术

10 液晶显示器 (LCD) 是最广泛使用的平板显示器中的一种。LCD 用于笔记本或者膝上型计算机、台式计算机监控器和电视机中。LCD 比传统的阴极射线管 (CRT) 显示器重量轻且占用空间小。

15 LCD 的通常结构由液晶 (LC) 层构成，该液晶层位于一对包括场发生电极和偏振器的面板之间。LC 层受到由电极产生的电场的作用，并且场强的变化使 LC 层的分子排列方向发生了改变。例如，当施加电场时，LC 层的分子改变其排列方向，从而改变穿过 LC 层的光的偏振。恰当定位的偏振滤光片选择地阻挡了偏振光，产生出表现所需图像的暗区。

20 LCD 还包括设置在面板或覆盖滤色器的有机绝缘层中的任意一个之上，用来表现彩色图像的多个滤色器。有机绝缘层通常足够厚以使面板表面平滑，使得其上的场发生电极具有均匀的平坦表面。

然而，厚有机层减少了光透射率，尤其是对于蓝光，因此引起所谓的发黄(yellowish)现象。另外，厚有机层和同样非常厚的滤色器使得难以得到截面光滑的接触孔，设置该接触孔用于滤色器上下的导电层与有机层之间的接触。

25

### 发明内容

提供一种薄膜晶体管阵列板，其包括：形成在绝缘衬底上的栅极线；在栅极线上的栅极绝缘层；在栅极绝缘层上的半导体层；形成在栅极绝缘层上的数据线；至少部分地形成在半导体层上的漏极电极；形成在数据线和漏极电极上的第一钝化层；形成在数据线和漏极电极上的滤色器；形成在滤色器上的第二钝化层；以及形成在滤色器上的像素电极，其与漏极电

极连接，与第二钝化层交叠，并且由第二钝化层封闭(enclose)。

数据线包括一对彼此相连且形成大约45度角的直线部分。

薄膜晶体管阵列板还可包括存储电极线，其形成在衬底上，并包括与像素电极交叠以形成存储电容器的展开部分。漏极电极可包括与存储电极5线的展开部分交叠的展开部分。

第二钝化层可包括有机绝缘体和无机绝缘材料中的至少一种。第二钝化层可由光敏材料或丙烯酸树脂构成。

第一钝化层可具有露出至少部分漏极电极的接触孔，滤色器可具有设置在漏极电极上的开口，像素电极通过该开口和该接触孔连接漏极电极。

10 薄膜晶体管阵列板还可包括形成在部分栅极线或部分数据线上、由与像素电极相同的材料构成的辅助接触部分。

数据线和漏极电极的整个底表面可基本上设置在半导体层上，数据线和漏极电极可具有与半导体层基本相同的平面形状，并且该半导体层可包括未由数据线和漏极电极覆盖并且设置在源极电极与漏极电极之间的部分15分。

第二钝化层和像素电极可覆盖滤色器的整个表面。

提供一种液晶显示器，包括：第一衬底；设置在衬底上的第一信号线；设置在衬底上并且与第一信号线相交的第二线；连接至第一和第二信号线的薄膜晶体管；设置在第一衬底上的滤色器；设置在滤色器上的绝缘层，其与第一和第二信号线及薄膜晶体管相对，并具有露出滤色器的开口；设置在滤色器上的像素电极，其连接薄膜晶体管，与绝缘层交叠，并且基本上位于绝缘层的开口中；第二衬底，其面对第一衬底，并且与第一衬底间隔开一间隙；形成在第二衬底上的公共电极；设置在公共电极上的光阻挡件；以及填充在第一衬底与第二衬底之间的间隙中的液晶层。

25 绝缘层和像素电极可覆盖滤色器的整个表面。

光阻挡件可包括保持第一衬底与第二衬底之间间隙的第一部分以及比第一部分的厚度薄的第二部分。

液晶层可具有负介电各向异性，并且可处于垂直排列。

公共电极可具有切去部分。

30 提供一种制造薄膜晶体管阵列板的方法，该方法包括：在衬底上形成多条栅极线；在栅极线上形成第一绝缘层；在第一绝缘层上形成半导体层；

至少在半导体层上形成多条数据线和漏极电极；在数据线和漏极电极上形成第二绝缘层；形成多个滤色器，每个滤色器包括红、绿和蓝色素中的一种；至少在滤色器边缘上形成第三绝缘层，第三绝缘层与栅极线和数据线相对设置；以及在滤色器上形成多个像素电极，使得像素电极和第三绝缘层覆盖滤色器的整个表面。

5 第三绝缘层可由光敏材料或丙烯酸树脂构成。

第二绝缘层可具有露出至少部分漏极电极的接触孔，滤色器可具有设置在漏极电极上的开口，像素电极通过该开口和该接触孔连接漏极电极。

## 10 附图说明

通过参照附图对本发明的优选实施例进行描述，将使本发明变得更加明显易懂，附图中：

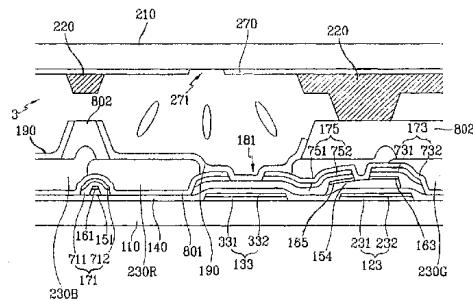

15 图 1 是根据本发明实施例的 LCD 的布局图；

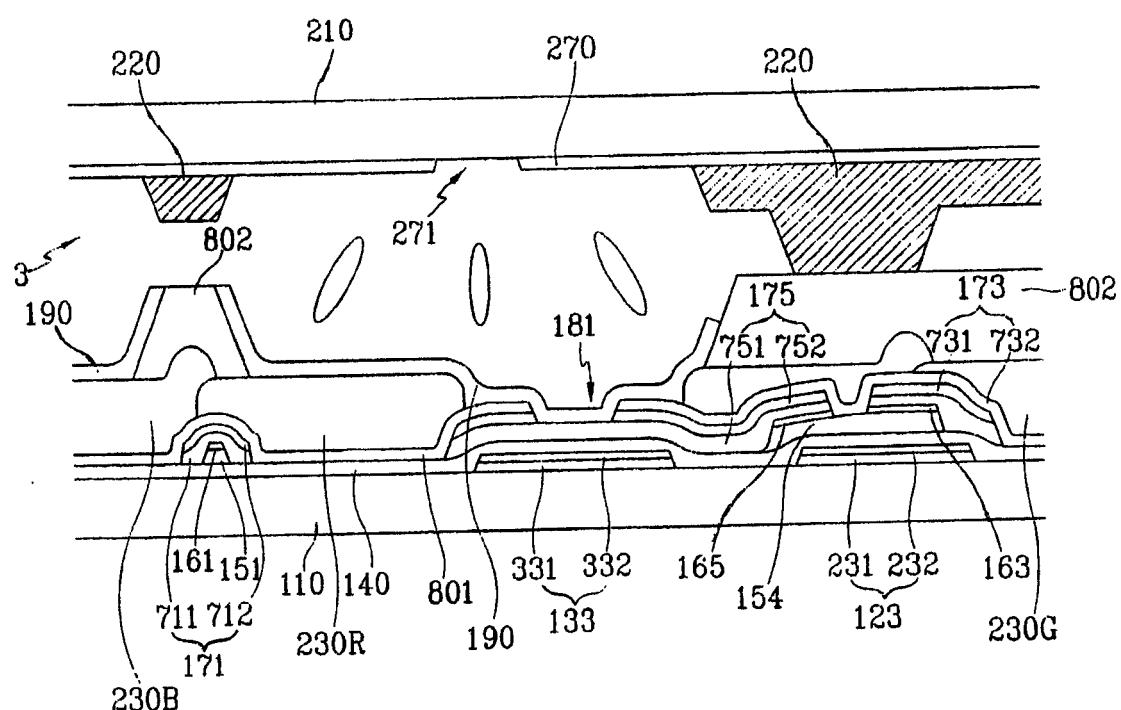

图 2 是沿线 II-II' 截取的图 1 所示 LCD 的截面图；

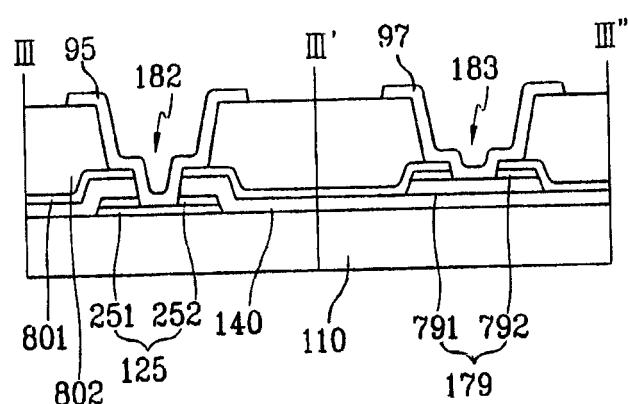

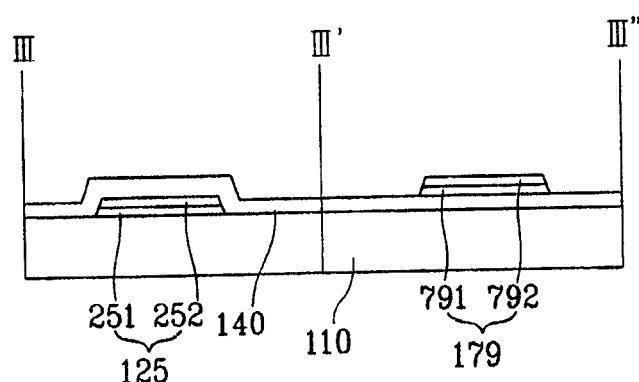

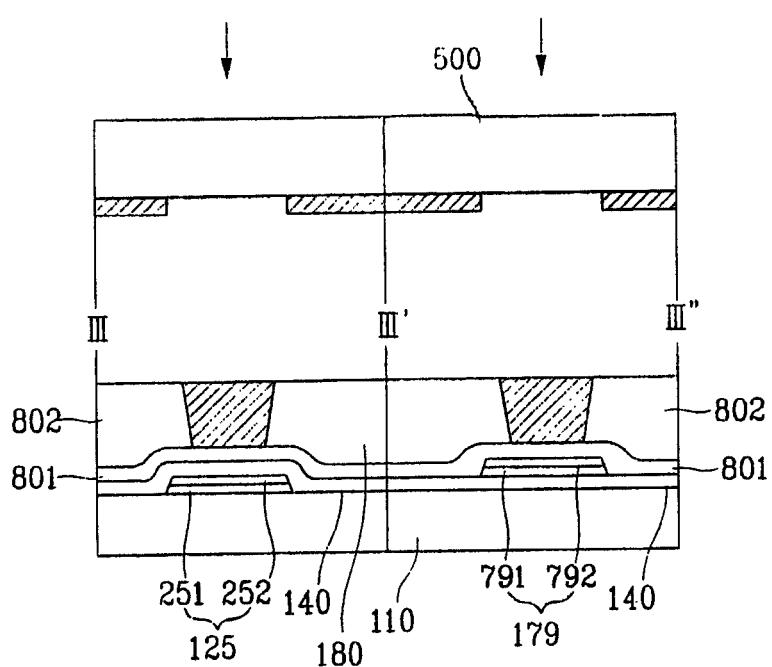

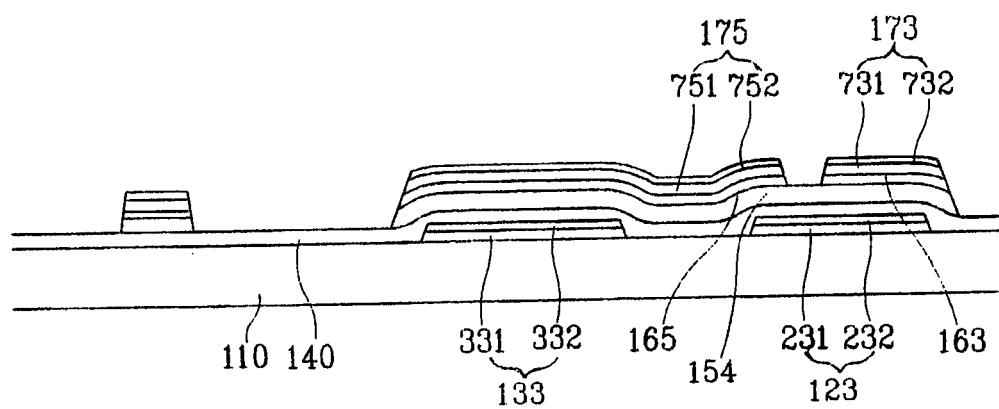

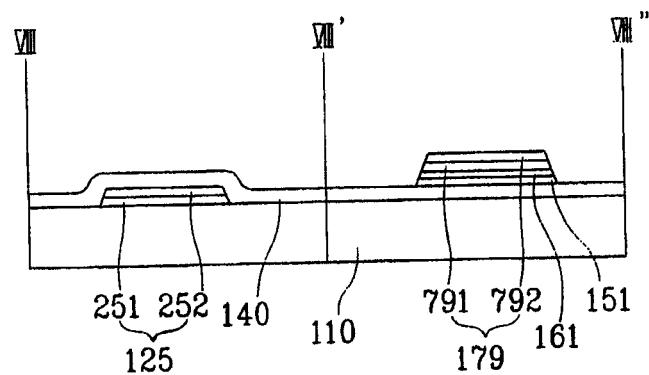

图 3 是沿线 III-III' 和 III'-III" 截取的图 1 所示 LCD 的截面图；

图 4A 和 4B 是根据本发明的实施例，在其制造方法的中间步骤中，分别沿线 II-II' 及线 III-III' 和 III'-III" 截取的图 1 至 3 所示 TFT 阵列板的截面图；

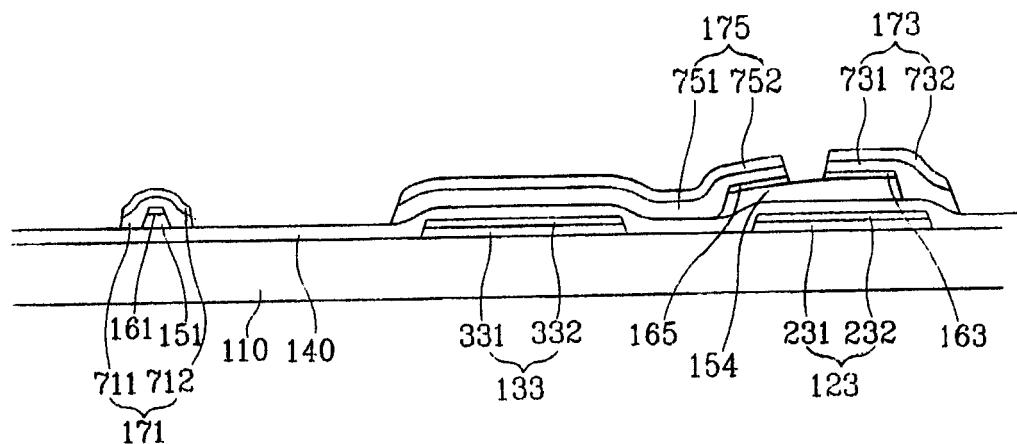

图 5A 和 5B 是该制造方法在图 4A 和 4B 所示步骤之后的步骤中，分别沿线 II-II' 及线 III-III' 和 III'-III" 截取的图 1 至 3 所示的 TFT 阵列板的截面图；

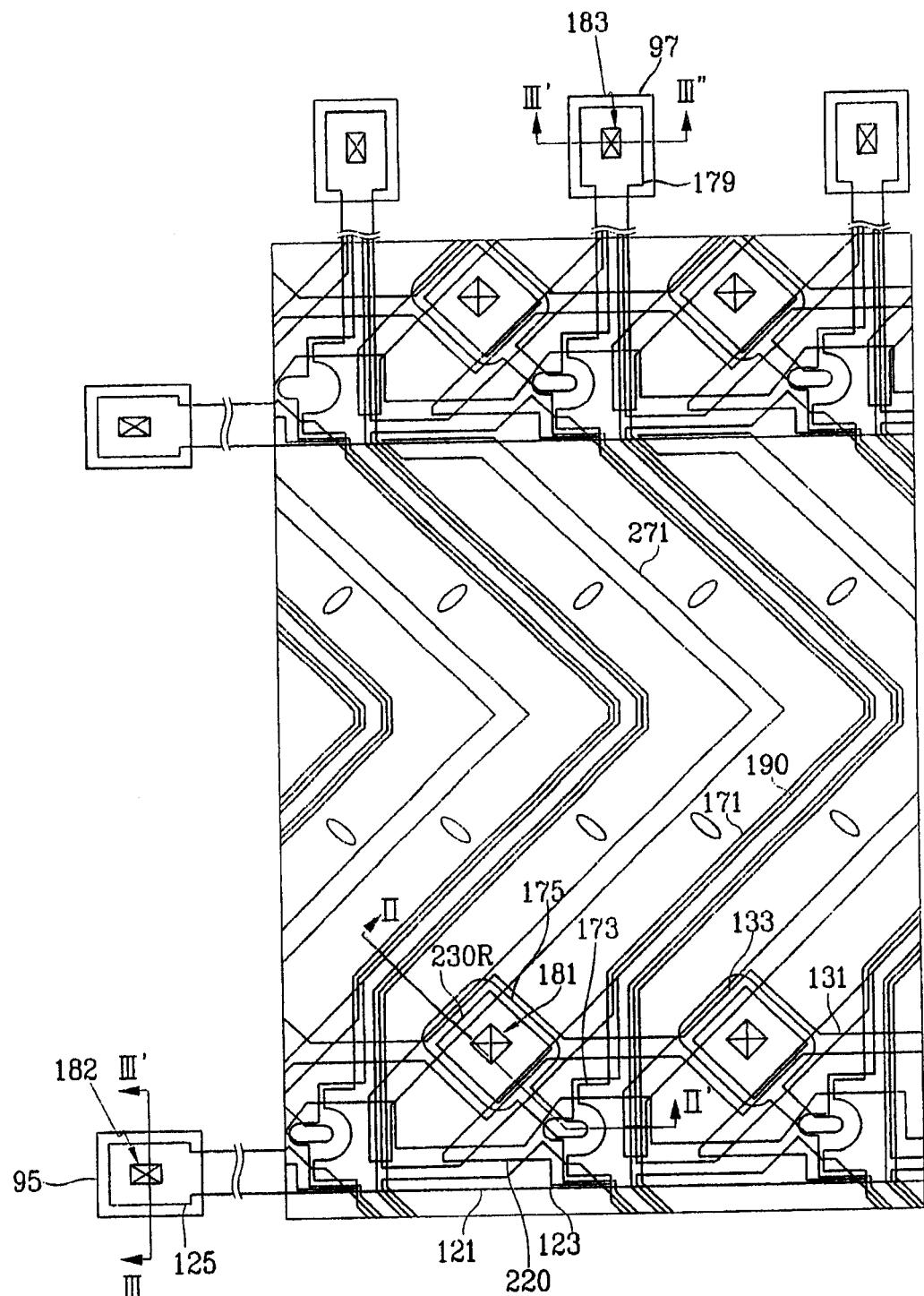

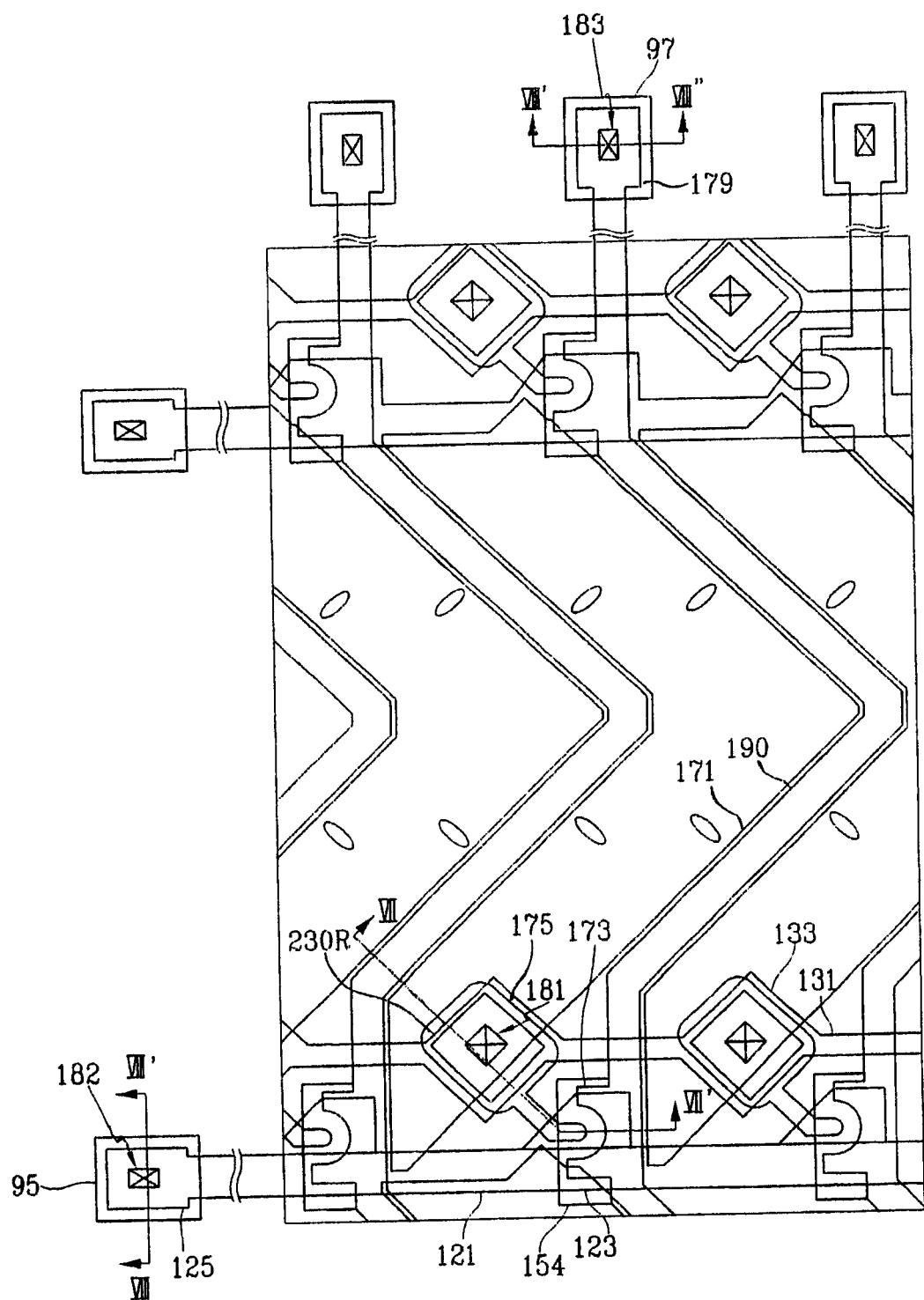

20 图 6 是根据本发明另一实施例的 LCD 的布局图；

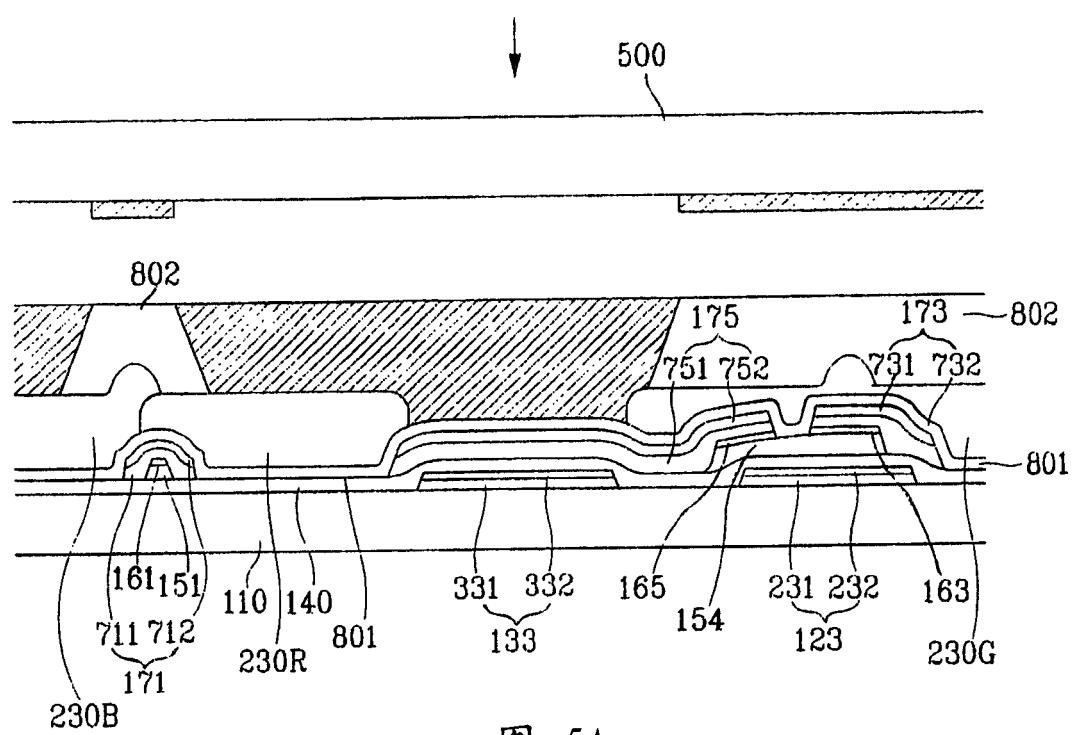

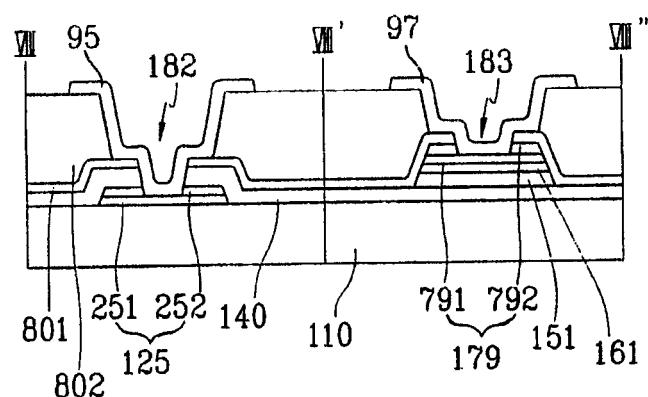

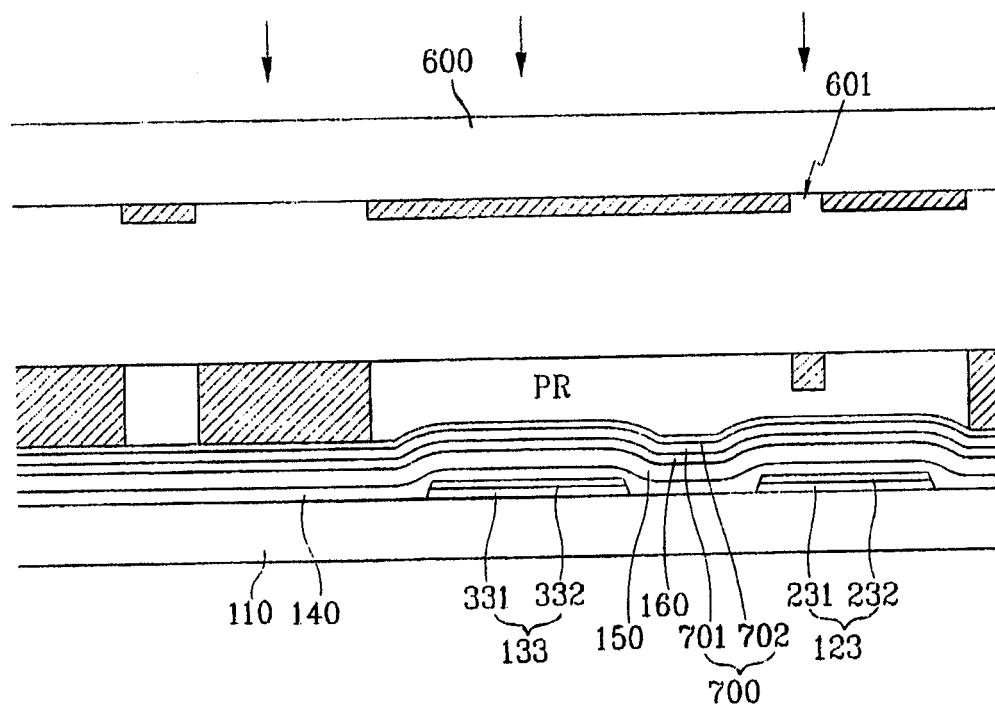

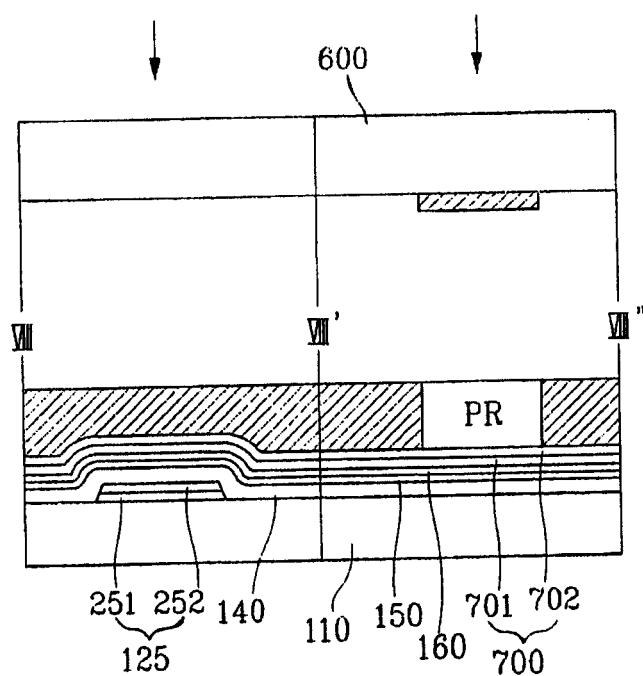

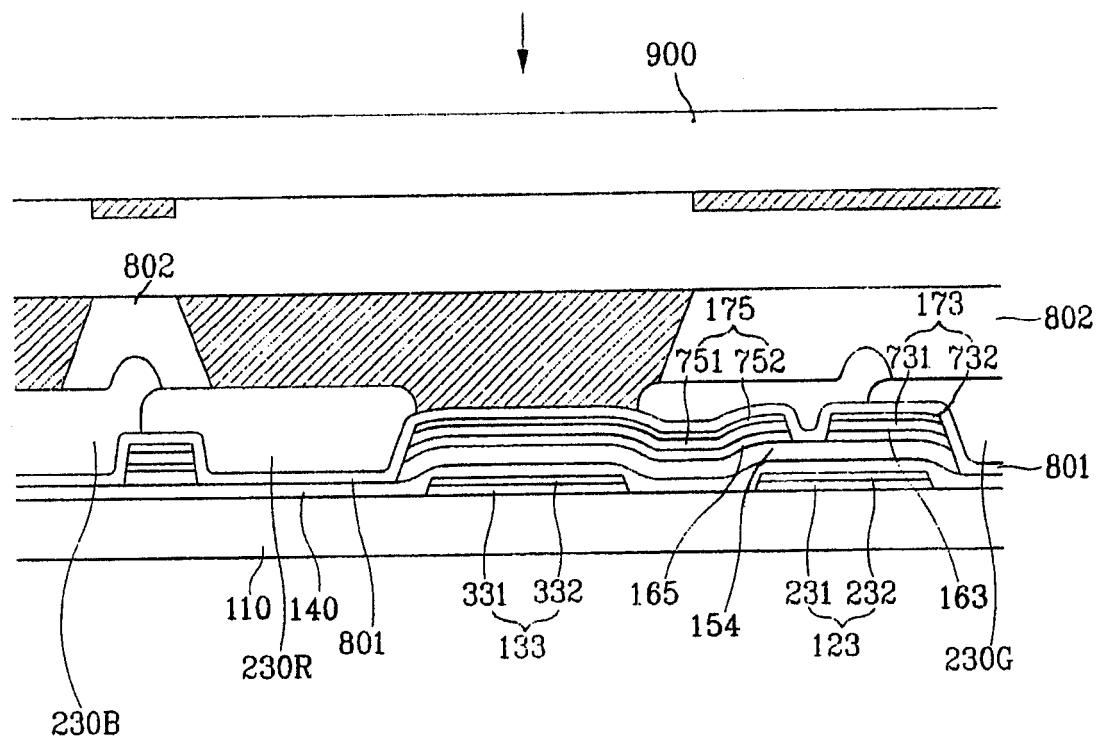

图 7 是沿线 VII-VII' 截取的图 6 所示 LCD 的截面图；

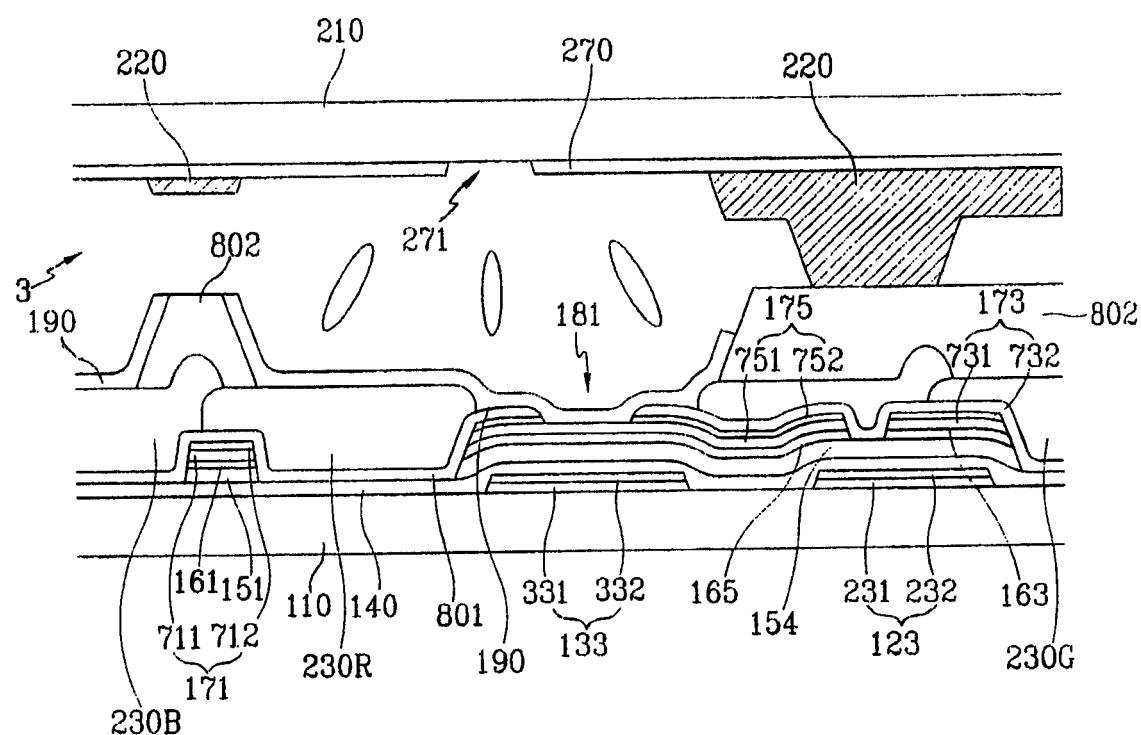

图 8 是沿线 VIII-VIII' 和 VIII'-VIII" 截取的图 6 所示 LCD 的截面图；

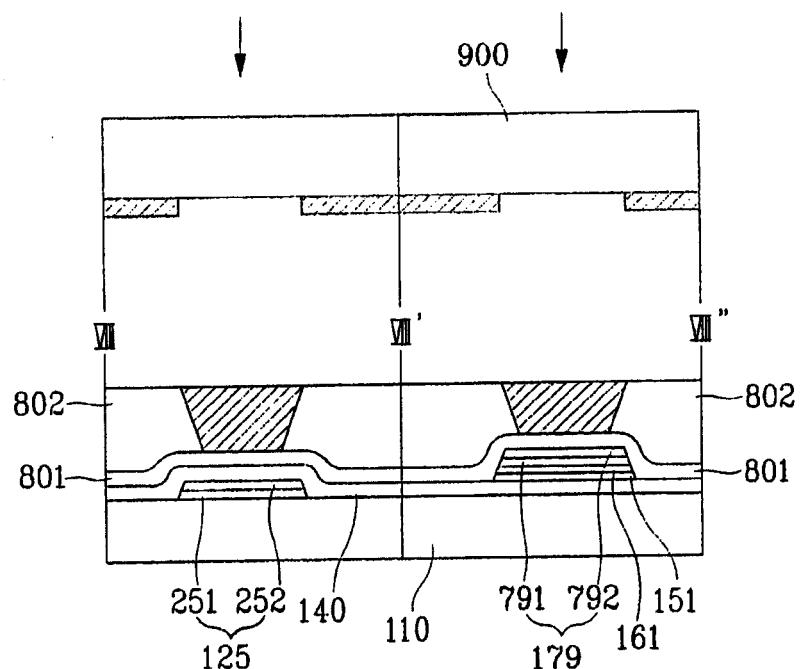

图 9A 和 9B 是根据本发明的实施例，在其制造方法的中间步骤中，分别沿线 VII-VII' 及线 VIII-VIII' 和 VIII'-VIII" 截取的图 6 至 8 所示 TFT 阵列

25 板的截面图；

图 10A 和 10B 是该制造方法在图 9A 和 9B 所示步骤之后的步骤中，分别沿线 VII-VII' 及线 VIII-VIII' 和 VIII'-VIII" 截取的图 6 至 8 所示 TFT 阵列板的截面图；以及

30 图 11A 和 11B 是该制造方法在图 10A 和 10B 所示步骤之后的步骤中，分别沿线 VII-VII' 及线 VIII-VIII' 和 VIII'-VIII" 截取的图 6 至 8 所示的 TFT 阵列板的截面图。

### 具体实施方式

随后将参照表现本发明优选实施例的附图对本发明进行更充分地描述。然而，本发明可以以多种不同的形式实施，且不应将本发明解释为仅限于此处提出的实施例。

附图中，为了清楚起见，放大了层、膜和区域的厚度。相同的附图标记始终表示相同的元件。可以理解，当称诸如层、膜、区域或衬底的元件在另一元件“上”时，该元件可以直接在该另一元件上或也可以存在有中间元件。相比，当称元件“直接”在另一元件“上”时，则不存在中间元件。

现在将参照附图介绍根据本发明的实施例的液晶显示器和用于 LCD 的薄膜晶体管 (TFT) 阵列板。

图 1 是根据本发明实施例的 LCD 的布局图，图 2 是沿线 II-II' 截取的图 1 所示 LCD 的截面图，图 3 是沿线 III-III' 和 III'-III" 截取的图 1 所示 LCD 的截面图。

根据本发明实施例的 LCD 包括 TFT 阵列板、面对该 TFT 阵列板的公共电极板、以及设置在 TFT 阵列板和公共电极板之间的 LC 层 3。

现在详细说明该 TFT 阵列板。

多条栅极线 121 和多条存储电极线 131 形成在绝缘衬底 110 上。

20 栅极线 121 基本上沿横向方向延伸且彼此隔开，并传输栅极信号。每条栅极线 121 包括形成多个栅极电极 123 的多个突起以及具有较大面积、用于与另一层或外部设备接触的端部 125。

每条存储电极线 131 基本上沿横向方向延伸，并包括形成存储电极 133 的多个突起。每个存储电极 133 具有菱形或旋转大约 45 度的矩形形状，并且其靠近栅极线 121。对存储电极线 131 施加预定电压，如公共电压，该电压施加于 LCD 的公共电极板上的公共电极 270。

30 栅极线 121 及存储电极线 131 具有多层结构，该多层结构包括具有不同物理特性的两层膜，下部膜和上部膜。上部膜优选地由低电阻率金属构成，其包括诸如 Al 和 Al 合金的含 Al 金属、诸如 Ag 和 Ag 合金的含 Ag 金属、或诸如 Cu 和 Cu 合金的含 Cu 金属，用来降低栅极线 121 和存储电极线 131 中的信号延迟或电压降。另一方面，下部膜优选由诸如 Cr、Mo、

Mo 合金、Ta、或 Ti 的材料构成，这些材料具有与诸如氧化铟锡 (ITO) 或氧化铟锌 (IZO) 的其它材料的良好的物理、化学及电性连接特性。下部膜材料和上部膜材料的良好典型组合是 Cr 与 Al-Nd 合金。图 4 中，栅极电极 123 的下部和上部膜分别由附图标记 231 和 232 来表示，端部 125 的下部和上部膜分别由附图标记 251 和 252 来表示，存储电极 133 的下部和上部膜分别由附图标记 331 和 332 来表示。部分除去栅极线 121 的端部 125 的上部膜 252，以露出下面的部分下部膜 251。

栅极线 121 和存储电极线 131 可以具有单层结构，或者可以包括三层或多层。

此外，栅极线 121 和存储电极线 131 的侧面相对于衬底 110 的表面倾斜，并且其倾斜角度大约为 30 至 80 度的范围。

优选由氮化硅 (SiNx) 构成的栅极绝缘层 140 形成在栅极线 121 和存储电极线 131 上。

优选由氢化非晶硅 (简写成“a-Si”) 或多晶硅构成的多个半导体带 151 形成在栅极绝缘层 140 上。每个半导体带 151 基本上沿纵向方向延伸，同时其周期性地弯曲。每个半导体带 151 具有多个朝着栅极电极 123 分支的突起 154。每个半导体岛 150 与栅极电极 123 相对。

在半导体带 151 上形成多个欧姆接触带和岛 161 和 165，其优选由硅化物或以 n 型杂质重掺杂的 n+ 氢化非晶硅 (a-Si) 构成。每个欧姆接触带 161 具有多个突起 163，并且突起 163 和欧姆接触岛 165 成对地位于半导体带 151 的突起 154 上。

半导体带 151 及欧姆接触 161 和 165 的侧面相对于衬底 110 的表面倾斜，并且其倾斜角度优选在大约 30 至 80 度之间的范围内。

彼此隔开的多条数据线 171 和多个漏极电极 175 形成在欧姆接触 161 和 165 以及栅极绝缘层 140 上。

用于传输数据电压的数据线 171 基本上沿纵向方向延伸，并且与栅极线 121 和存储电极线 131 相交。每条数据线 171 具有端部 179，端部 179 具有较大的面积，用于与另一层或外部器件的接触，每条数据线 171 包括多对倾斜部分和多个纵向部分，使其周期性弯曲。一对倾斜部分彼此连接以形成人字纹，并且该对倾斜部分的相对端连接至各自的纵向部分。数据线 171 的倾斜部分与栅极线 121 形成大约 45 度的角度，并且纵向部分跨过栅

极电极 123。一对倾斜部分的长度是纵向部分长度的大约 1 至 9 倍，即其占该对倾斜部分和该纵向部分的总长度的大约 50 至 90%。

每个漏极电极 175 包括与存储电极 133 交叠的矩形展开部分。漏极电极 175 展开部分的边缘基本上平行于存储电极 133 的边缘。数据线 171 的每个纵向部分包括多个突起，使得包括突起的纵向部分形成部分封闭漏极电极 175 端部的源极电极 173。每组栅极电极 123、源极电极 173 和漏极电极 175、以及半导体带 151 的突起 154 一起形成 TFT，该 TFT 具有形成在源极电极 173 和漏极电极 175 之间设置的半导体突起 154 中的沟道。

数据线 171 和漏极电极 175 还包括优选由 Mo、Mo 合金或 Cr 构成的下部膜 711 和 751 以及位于其上并且优选由含 Al 金属构成的上部膜 712 和 752。图 4 和图 5 中，源极电极 173 的下部和上部膜分别由附图标记 731 和 732 表示，数据线 171 端部 179 的下部和上部膜分别由附图标记 791 和 792 来表示。部分除去数据线 171 展开部分 179 和漏极电极 175 的上部膜 792、752 以露出下面的部分下部膜 791 和 751。

与栅极线 121 及存储电极线 131 相同，数据线 171 和漏极电极 175 具有倾斜的侧面，并且其倾斜角度大约为 30 至 80 度的范围。

欧姆接触 161 和 165 仅在下面的半导体带 151 与其上的上覆数据线 171 和上覆漏极电极 175 之间插入，减少了其间的接触电阻。

第一钝化层 801 优选由无机绝缘体如 SiNx 构成，其形成在数据线 171 和漏极电极 175、以及未由数据线 171 和漏极电极 175 覆盖的部分半导体带 151 之上。

第一钝化层 801 具有多个接触孔 181 和 183，其分别露出漏极电极 175 和数据线 171 的端部 179。第一钝化层 801 和栅极绝缘层 140 具有多个露出栅极线 121 端部 125 的接触孔 182。接触孔 181、182 和 183 可以具有不同的形状如多边形或圆形。每个接触孔 182 或 183 的面积优选等于或大于  $0.5\text{mm} \times 15\mu\text{m}$ ，并且不大于  $2\text{mm} \times 60\mu\text{m}$ 。接触孔 181、182 和 183 的侧壁以大约 30 至 85 度的角度倾斜，或具有阶梯式的轮廓。

多个红、绿和蓝色滤色器 230R、230G 和 230B 形成在第一钝化层 801 上，并且其基本上设置在数据线 171 之间。在相邻两条数据线 171 中并以纵向方向设置的滤色器 230R、230G 和 230B 可以彼此连接以形成周期性弯曲的带。相邻的滤色器 230R、230G 和 230B 彼此在数据线 171 上交叠形成

小丘。滤色器 230R、230G 和 230B 具有多个开口，其露出接触孔 181 和第一钝化层 801 的顶表面，并且未设置在设置有栅极线 121 和数据线 179 的展开部分 125 和 179 的外围区域上。

优选由光敏有机材料如丙烯酸光敏树脂构成的第二钝化层 802 形成在 5 滤色器 230R、230G 和 230B 上。第二钝化层 802 与栅极线 121、数据线 171 和 TFT 相对设置，具体地，其覆盖滤色器 230R、230G 和 230B 的边缘以避免由随后的蚀刻和清理工艺所破坏。然而，在栅极线 121 和数据线 171 封闭的大部分区域上未设置第二钝化层 802，从而不会减少该些区域中的光透射率。第二钝化层 802 具有平坦的均匀表面，从而平滑了由滤色器 230R、10 230G 和 230B 形成的小丘而产生的阶梯型差异。第二钝化层 802 可以由无机绝缘体如 SiNx 和 SiO<sub>2</sub> 构成。

多个像素电极 190 和优选由 ITO 或 IZO 构成的多个辅助接触部分 95 和 97 形成在滤色器 230R、230G 和 230B 以及第二钝化层 802 上。

每个像素电极 190 基本上位于由数据线 171 和栅极线 121 封闭的区域 15 内，因此也形成人字纹。像素电极 190 覆盖包括存储电极 133 的存储电极线 131 和漏极电极 175 的展开部分，并且其具有基本上平行于存储电极 133 边缘的削边，该存储电极 133 边缘靠近该削边。

像素电极 190 和第二钝化层 802 覆盖滤色器 230R、230G 和 230B 的整个表面，从而避免后续工艺破坏滤色器 230R、230G 和 230B，并且避免污染上覆层和 LC 层 3。然而，第二钝化层 802 仅在像素电极 190 的边界附近 20 与像素电极 190 交叠，并且大部分像素电极 190 直接设置在滤色器 230R、230G 和 230B 上，从而第二钝化层 802 不会减少穿过像素电极 190 的光透射率。

像素电极 190 通过接触孔 181 物理且电性连接至漏极电极 175，使得像素电极 190 接收来自漏极电极 175 的数据电压。提供有数据电压的像素电极 190 配合公共电极 270 产生电场，对设置在其间的液晶分子重新定向。 25

像素电极 190 和公共电极形成称为“液晶电容器”的电容器，TFT 关断后其存储所施加的电压。设置称为“存储电容器”的附加电容器用来增加电压存储容量，其与液晶电容器并联连接。通过像素电极 190 与存储电极线 131 交叠来实现存储电容器。通过在存储电极线 131 上设置突起（即 30 存储电极）133、拉长连接于像素电极 190 的漏极电极 175、并在与存储电

极线 131 的存储电极 133 交叠的漏极电极 175 处设置用以减少端子之间的间距并增大交叠面积的展开部分来增加存储电容器的电容即存储电容器。

像素电极 190 与数据线 171 及栅极线 121 交叠，以增加孔径比。

5 辅助接触部分 95 和 97 通过接触孔 181 和 182 分别连接栅极线 121 露出的端部 125 和数据线 171 露出的端部 179。辅助接触部分 95 和 97 保护露出部分 125 和 179，并补充露出部分 125 和 179 与外部器件的粘附性。

最后，对准层（未示出）形成在像素电极 190、辅助接触部分 95 和 97、以及第二钝化层 802 上。

下面对公共电极板进行描述。

10 公共电极 270 优选由透明导电材料如 ITO 和 IZO 构成，其形成在如透明玻璃的绝缘衬底 210 上。公共电极 270 提供有公共电压并具有多个人字纹状切去部分 271。每个切去部分 271 包括一对彼此连接的倾斜部分、连接其中一个倾斜部分的横向部分、以及连接其它倾斜部分的纵向部分。该切去部分 271 的倾斜部分基本上平行于数据线 171 的倾斜部分延伸，并与像素电极 190 对置，使得可以将像素电极 190 截成左右两半。该切去部分 271 的横向和纵向部分分别与像素电极 190 的横向和纵向边对齐，并且与切去部分 271 的倾斜部分形成钝角。设置切去部分 271 用于控制 LC 层中 LC 分子的倾斜方向。该切去部分 271 可以用优选由有机材料构成的突起来代替。

20 称为黑矩阵的光阻挡件 220 形成在公共电极 270 上。该光阻挡件 220 包括面对数据线 171 倾斜部分的多个倾斜部分以及面对 TFT 和数据线 171 纵向部分的多个直角三角形部分，使得该光阻挡件 220 避免了像素电极 190 之间的光泄露，并限定了面对像素电极 190 的开放区域。光阻挡件 220 的每个三角形部分具有平行于像素电极 190 削边的斜边。该三角形部分比倾斜部分厚，以用作限定 TFT 阵列板与公共电极板之间的间隙的柱状间隔体，该间隙由液晶层 3 填充。与 TFT 上没有厚第二钝化层的情况相比，该三角形部分的厚度相对较低。

同面或同向性的对准层（未示出）涂覆在公共电极 270 和光阻挡件 220 上。

30 一对偏振器（未示出）设置在板的外表面上，使得它们的透射轴相交，并且其中一个透射轴平行于栅极线 121。

LCD 还可以包括至少一个用来补偿 LC 层 3 的延迟的延迟膜和用来为

LCD 提供光的背光单元。

LC 层 3 具有负介电各向异性，并且排列 LC 层 3 中的 LC 分子使其长轴在没有电场时垂直于面板表面。

在向公共电极 270 施加公共电压，向像素电极 190 施加数据电压时，5 产生基本上垂直于面板表面的主电场。LC 分子响应该电场倾向于改变其排列方向，使得其长轴垂直于场方向。同时，公共电极 270 的切去部分 271 和像素电极 190 的边缘使主电场变形，从而具有确定 LC 分子倾斜方向的水平分量。主电场的水平分量垂直于切去部分 271 边缘和像素电极 190 边缘。

因此，在 LC 层 3 的像素区域中形成了四个具有不同倾斜方向且由像素10 电极 190 的边缘、将像素电极 190 分为两分的切去部分 271、以及穿过切去部分 271 倾斜部的交汇点的假想横向中心线隔开的子区域，都位于像素电极 190 上。每个子区域具有分别由切去部分 271 和像素电极 190 的倾斜边15 限定的两条主边。通过改变公共电极 270 的切去部分 271 的数量、通过在像素电极 190 上设置切去部分、或者通过改变像素电极 190 边缘的曲点的数量能够改变子区域的数量。将该子区域基于倾斜方向分成多个域，优选为四个域。

同时，由像素电极 190 之间的电压差产生的次级电场的方向垂直于切去部分 271 的边缘。因此，次级电场的场方向与主电场的水平分量的一致。因此，像素电极 190 之间的次级电场加强了 LC 分子的倾斜方向的确定。

20 由于 LCD 进行诸如点变换、列变换之类的变换，因此向邻近的像素电极施加相对于公共电压具有相反极性的数据电压，因此在邻近像素电极 190 之间几乎总是产生次级电场，从而提高域的稳定性。

由于所有域的倾斜方向与平行或垂直于面板边缘的栅极线 121 形成大25 约 45 度的角度，并且该倾斜方向与该偏振器的透射轴相交 45 度提供了最大透射率，因此能够附装这些偏振器，使偏振器的透射轴平行或垂直于面板边缘，并且降低了生产成本。

可以通过拓宽数据线 171 来补偿由于弯曲导致的数据线 171 阻抗的增加，因为可以通过使像素电极 190 的尺寸最大化及调整厚的有机钝化层 803 来补偿由于数据线 171 宽度的增加导致的电场变形及寄生电容的增加。

30 由于滤色器 230R、230G 和 230B 及像素电极 190 设置在 TFT 阵列板上，因此减少了滤色器 230R、230G 和 230B 和像素电极 190 之间的对准误差。

此外，在公共电极板上没有附着物。

现在，参照图 4A、4B、5A 和 5B 以及图 1 至 3，对根据本发明实施例在图 1 至 3 中所示的 TFT 阵列板的制造方法进行详细说明。

图 4A 和 4B 是根据本发明的实施例，在其制造方法的中间步骤中，分别沿 II-II' 及线 III-III' 和 III'-III'' 截取的图 1 至 3 所示 TFT 阵列板的截面图，图 5A 和 5B 该制造方法在图 4A 和 4B 所示步骤之后的步骤中，分别沿 II-II' 及线 III-III' 和 III'-III'' 截取的图 1 至 3 所示 TFT 阵列板的截面图。

参照图 1、4A 和 4B，对优选由 Cr、Mo、或 Mo 合金构成的下部导电膜和优选由含 Al 金属或含 Ag 金属构成的上部导电膜按顺序溅镀在绝缘衬底 110 上，并且按顺序湿法或干法蚀刻，以形成每一条都包括多个栅极电极 123 和展开部分 125 的多条栅极线 121 以及包括多个存储电极 133 的多条存储电极线 131。图 4A 和 4B 中，栅极电极 123 的下部和上部膜分别由附图标记 231 和 232 表示，展开部分 125 的下部和上部膜分别由附图标记 251 和 252 表示，存储电极 133 的下部和上部膜分别由附图标记 331 和 332 表示。

在依次沉积厚度为约 1500 至 5000 Å 的栅极绝缘层 140、厚度为约 500 至 2000 Å 的本征 a-Si 层、厚度为约 300 至 600 Å 的非本征 a-Si 层之后，光蚀刻该非本征 a-Si 层和本征 a-Si 层以在栅极绝缘层 140 上形成具有多个突起 154 的多个非本征半导体带和多个本征半导体带 151。

接着，顺序溅镀包括下部导电膜和上部导电膜并具有 1500 至 3000 Å 厚度的两个导电膜，并构图以形成每一条都包括多个源极电极 173 和展开部分 179 的多条数据线 171 和多个漏极电极 175。下部导电膜优选由 Cr、Mo、或 Mo 合金构成，上部导电膜优选由含 Al 金属或含 Ag 金属构成。图 4A 和 4B 中，漏极电极 171 的下部和上部膜分别由附图标记 711 和 712 表示，源极电极 173 的上部和下部膜分别由附图标记 731 和 732 表示，漏极电极 175 的下部和上部膜分别由附图标记 751 和 752 表示，数据线 171 端部 179 的下部和上部膜分别由附图标记 791 和 792 表示。

随后，除去没有被数据线 171 和漏极电极 175 覆盖的部分非本征半导体带，以完成包括多个突起 163 的多个欧姆接触带 161 和多个欧姆接触岛 165，并露出部分本征半导体带 151。为了稳定半导体带 151 的露出表面，随后优选进行氧等离子体处理。

参照附图 1、5A 及 5B，沉积由无机绝缘体如氮化硅构成的第一钝化层 801。

在除去栅极绝缘层 140 的露出部分以露出下面的部分栅极线 121 展开部分 125 后，除去漏极电极 175、数据线 171 展开部分 179、以及栅极线 121 展开部分 125 的上部导电膜 752、792 和 252 的露出部分，从而露出下面的漏极电极 175、数据线 171 的展开部分 179、以及栅极线 121 的展开部分 125 的部分下部导电膜 751、791 和 251。

接着，在第一钝化层 801 上涂覆分别含有红、绿和蓝色素的光敏有机膜，并通过光刻法构图，从而以顺序方式形成具有多个开口的多个滤色器 230R、230G 和 230B。

随后，涂覆由低电阻率丙烯酸有机绝缘体构成的第二钝化层 802，并通过具有多个透射区域和光阻挡区域的光刻掩模 500 对其曝光。然后对该第二钝化层 802 进行显影以露出下面的滤色器 230R、230G 和 230B 及滤色器 230R、230G 和 230B 的开口。

在其上形成光致抗蚀剂（未示出），然后使用作为蚀刻掩模的光致抗蚀剂对第一钝化层 801 和栅极绝缘层 140 构图以形成分别露出部分漏极电极 175、栅极线 121 的展开部分 125、以及部分数据线 171 的展开部分 179 的多个接触孔 181、182 和 183。由于滤色器 230R、230G 和 230B 可以伴随着光致抗蚀剂一起消耗，因此优选考虑到在该步骤中消耗的厚度来确定滤色器 230R、230G 和 230B 的厚度。

最后，如图 1 至 3 所示，通过溅镀和光蚀刻厚度约为 400 至 500Å 的 IZO 或 ITO 层，在滤色器 230R、230G 和 230B 及第二钝化层 802 上、以及在漏极电极 175、栅极线 121 的展开部分 125、以及数据线 171 的展开部分 179 的下部导电膜 751、791 和 251 上形成多个像素电极 190 和多个辅助接触部分 92 和 97。

现在，详细介绍根据本发明实施例如图 1 至 3 所示的公共电极板。

沉积 IZO 或 ITO 层以形成公共电极 270，并对公共电极 270 构图以形成多个切去部分 271。

涂覆含黑色素的光敏有机绝缘层（未示出）。然后通过光刻掩模（未示出）对该光敏层曝光，该光刻掩模具有多个透射区域、多个面对栅极线 121 和数据线 171 及 TFT 阵列板上的 TFT 的狭缝区域、以及多个面对 TFT 的光

阻挡区域。因此，面对透射区域的光敏层部分吸收充足的光能，同时面对狭缝区域的部分光敏层部分地吸收光能。然后对光敏层显影以形成具有取决于位置的厚度的光阻挡件 220。

参照附图 6 至 8 对根据本发明另一实施例的 LCD 进行详细说明。

5 图 6 是根据本发明另一实施例的 LCD 的布局图，图 7 是沿线 VII-VII' 截取的图 6 所示 LCD 的截面图，图 8 是沿线 VIII-VIII' 和 VIII'-VIII" 截取的图 6 所示 LCD 的截面图。

参照附图 6 至 8，根据此实施例的 LCD 也包括 TFT 阵列板、公共电极板、以及设置在其间的 LC 层 3。

10 对于 TFT 阵列板，包括多个栅极电极 123 的多条栅极线 121 以及包括多个存储电极 133 的多条存储电极线 131 形成在衬底 110 上，栅极绝缘层 140、包括多个突起 154 的多个半导体带 151、以及包括多个突起 163 的多个欧姆接触带 161 和多个欧姆接触岛 165 依次在其上形成。包括多个源极电极 173 的多条数据线 171 和多个漏极电极 175 形成在欧姆接触 161 和 165 上，第一钝化层 801 在其上形成。多个红、绿和蓝滤色器 230R、230G 和 230B 形成在第一钝化层 801 上，第二钝化层 802 在其上形成。第一钝化层 801 和栅极绝缘层 140 处设置有多个接触孔 181、182 和 183，多个像素电极 190 和多个辅助接触部分 95 和 97 形成在第二钝化层 802 的滤色器 230R、230G 和 230B 上。

20 对于公共电极板，公共电极 270 和光阻挡件 220 形成在绝缘衬底 210 上。

与图 1 至 3 所示的 LCD 不同，半导体带 151 具有与数据线 171 和漏极电极 175、以及下面的欧姆接触 161 和 165 几乎相同的平面形状。然而，半导体带 151 的突起 154 包括一些露出部分，这些露出部分没有为数据线 171 和漏极电极 175 所覆盖，如位于源极电极 173 与漏极电极 175 之间的部分。

图 1 至 3 所示的 LCD 的许多上述特征对于图 6 至 8 所示的 LCD 也是合适的。

现在，将详细说明根据本发明实施例的图 6 至 8 所示 TFT 阵列板的制造方法。

30 图 9A 和 9B 是根据本发明的实施例，在其制造方法的中间步骤中，分别沿线 VII-VII' 及线 VIII-VIII' 和 VIII'-VIII" 截取的图 6 至 8 所示 TFT 阵列

板的截面图；图 10A 和 10B 是该制造方法在图 9A 和 9B 所示步骤之后的步骤中，沿线 VII-VII' 及线 VIII-VIII' 和 VIII'-VIII'' 截取的图 6 至 8 所示 TFT 阵列板的截面图；以及图 11A 和 11B 是该制造方法在图 10A 和 10B 所示步骤之后的步骤中，沿线 VII-VII' 及线 VIII-VIII' 和 VIII'-VIII'' 截取的图 6 至 8 所示的 TFT 阵列板的截面图。

参照图 9A 和 9B，依次在绝缘衬底 110 上溅镀两层导电膜，即下部导电膜和上部导电膜，并依次对其进行湿法或干法蚀以形成每一条都包括多个栅极电极 123 和展开部分 125 的多条栅极线 121 和包括多个存储电极 133 的多条存储电极线 131。图 9A 和 9B 中，栅极电极 123 的下部和上部膜分别由附图标记 231 和 232 表示，展开部分 125 的下部和上部膜分别由附图标记 251 和 252 表示，存储电极 133 的下部和上部膜分别由附图标记 331 和 332 表示。

接着，通过 CVD 依次沉积栅极绝缘层 140、本征 a-Si 层 150、以及非本征 a-Si 层 160，使得层 140、150 和 160 分别具有约 1500 至 5000Å、约 500 至 2000Å、以及约 300 至 600Å 的厚度。通过溅镀沉积包括下部膜 701 和上部膜 702 的导电层 170，并且在导电层 170 上涂覆厚度约 1 至 2 微米的光致抗蚀剂膜 PR。

通过包括狭缝区域 601 的曝光掩模 600 曝光光致抗蚀剂膜 PR，并对其显影使得显影后的光致抗蚀剂 PR 具有取决于位置的厚度。图 9A 和 9B 所示的光致抗蚀剂 PR 包括多个厚度减小的第一至第三部分。分别地，第一部分位于第一区域（以下称为“配线区域”）上，第二部分位于第二区域（以下称为“沟道区域”），而位于剩余第三区域上的第三部分未在图中表示，因为其具有基本为零的厚度从而露出下面的部分导电层 170。

光致抗蚀剂 PR 不同的厚度使得当使用合适的工艺条件时可以选择地蚀刻下面的层。因此，通过图 10A 和 10B 所示的一系列蚀刻步骤得到包括多个源极电极 173 的多条数据线 171、多个漏极电极 175、包括多个突起 163 的多个欧姆接触带 161、多个欧姆接触岛 165、以及包括多个突起 154 的多个半导体带 151。图 10A 和 10B 中，漏极电极 171 的下部和上部膜分别由附图标记 711 和 712 表示，源极电极 173 的上部和下部膜分别由附图标记 731 和 732 表示，漏极电极 175 的下部和上部膜分别由附图标记 751 和 752 表示，数据线 171 端部 179 的下部和上部膜分别由附图标记 791 和 792 表

示。

为了说明的目的，导电层 170、非本征 a-Si 层 160 和本征 a-Si 层 150 在配线区域上的部分称为第一部分，沟道区域上的导电层 170、非本征 a-Si 层 160 和本征 a-Si 层 150 在沟道区域上的部分称为第二部分，导电层 170、

5 非本征 a-Si 层 160 和本征 a-Si 层 150 在第三区域上的部分称为第三部分。

以下是形成这种结构的典型顺序。

(1) 除去配线区域上的导电层 170、非本征 a-Si 层 160 和本征 a-Si 层 150 的第三部分；

(2) 除去光致抗蚀剂的第二部分；

10 (3) 除去沟道区域上的导电层 170 和非本征 a-Si 层 160 的第二部分；以

及

(4) 除去光致抗蚀剂的第一部分。

以下是另一种典型顺序。

(1) 除去导电层 170 的第三部分；

15 (2) 除去光致抗蚀剂的第二部分；

(3) 除去非本征 a-Si 层 160 和本征 a-Si 层 150 的第三部分；

(4) 除去导电层 170 的第二部分；

(5) 除去光致抗蚀剂的第一部分；以及

(6) 除去非本征 a-Si 层 160 的第二部分。

20 详细描述第一实例。

首先，通过湿法或干法蚀刻除去第三区域上导电层 170 露出的第三部分，以露出下面非本征 a-Si 层 160 的第三部分。干法蚀刻可以蚀去光致抗蚀剂 PR 的顶部。

接着，优选通过干法蚀刻除去第三区域上的非本征 a-Si 层 160 和本征 a-Si 层 150 的第三部分，并且除去光致抗蚀剂 PR 的第二部分以露出导电层 170 的第二部分。与除去非本征 a-Si 层 160 和本征 a-Si 层 150 的第三部分同时或分别地进行光致抗蚀剂 PR 第二部分的除去。SF<sub>6</sub>和 HCl 的混合气体或者 SF<sub>6</sub>和 O<sub>2</sub>混合气体可以以几乎相同的蚀刻比对 a-Si 层 150 和 160 以及光致抗蚀剂 PR 进行蚀刻。通过抛光除去余留在沟道区域上的光致抗蚀剂 PR 第二部分的残余。

在此步骤中完成半导体带 151。

接着，除去沟道区域上导电层 170 和非本征 a-Si 层 160 的第二部分以及光致抗蚀剂 PR 的第一部分。

可以对导电层 170 和非本征 a-Si 层 160 进行干法蚀刻。

或者，可以对导电层 170 进行湿法蚀刻，而对非本征 a-Si 层 160 进行干法蚀刻。由于湿法蚀刻蚀除了导电层 170 的侧面，而干法蚀刻几乎很难蚀除非本征 a-Si 层 160 的侧面，因此可以得到阶梯式的侧面轮廓。混合气体的示例如上所述为  $CF_4$  和  $HCl$  及  $CF_4$  和  $O_2$ 。后一种混合气体使本征半导体带 151 具有均匀的厚度。

这样，每个导电层 170 分成将完成的数据线 171 和多个漏极电极 175，

非本征 a-Si 层 160 分成将完成的欧姆接触带 161 和多个欧姆接触岛 165。

参照图 11A 和 11B，沉积并构图由无机绝缘体如氮化硅构成的第一钝化层 801 及栅极绝缘层 140，以形成分别露出部分漏极电极 175、栅极线 121 展开部分 125、部分数据线 171 展开部分 179 的多个接触孔 181、182 和 183。

在除去栅极绝缘层 140 的露出部分以露出下面的部分栅极线 121 展开部分 125 后，除去漏极电极 175、数据线 171 展开部分 179、以及栅极线 121 展开部分 125 的上部导电膜 752、792 和 252 的露出部分，从而露出下面的部分漏极电极 175、数据线 171 展开部分 179、以及栅极线 121 展开部分 125 的下部导电膜 751、791 和 251。

接着，在第一钝化层 801 上涂覆分别包括红、绿和蓝色素的光敏有机膜，并通过光刻法构图，从而以顺序方式形成具有多个开口的多个滤色器 230R、230G 和 230B。

随后，涂覆由低电阻率丙烯酸有机绝缘体构成的第二钝化层 802，并通过具有多个透射区域和光阻挡区域的光刻掩模 900 对其曝光。然后显影以完成第二钝化层 802。

第二钝化层 802 可以由非光敏有机绝缘体或具有小于 4 的低介电常数无机绝缘体构成。这样，需要用于构图第二钝化层 802 的附加蚀刻步骤。

最后，如图 6 至 8 所示，通过溅镀和光刻厚度约 400 至 500Å 的 IZO 或 ITO 层，在滤色器 230R、230G 和 230B 及第二钝化层 802 上、以及在漏极电极 175、栅极线 121 展开部分 125、及数据线 171 展开部分 179 的下部导电膜 751、791 和 251 上形成多个像素电极 190 和多个辅助接触部分 92 和 97。

IZO 膜的蚀刻可以包括使用 Cr 蚀刻剂如  $\text{HNO}_3/(\text{NH}_4)_2\text{Ce}(\text{NO}_3)_6/\text{H}_2\text{O}$  的湿法蚀刻，其不会通过接触孔 181、182 和 183 侵蚀漏极电极 175、栅极线 121 和数据线 171 露出的 Al 部分。用于使接触电阻最小的优选沉积温度在室温至大约 200℃ 的范围。用于沉积 IZO 的溅射靶优选包括  $\text{In}_2\text{O}_3$  和  $\text{ZnO}$ ，

5 并且  $\text{ZnO}$  的含量优选在大约 15 至 20 原子百分比的范围。

优选将氮用于 ITO 膜或 IZO 膜沉积之前的预热工艺，氮能避免通过接触孔 181、182 和 183 在漏极电极 175、栅极线 121、以及数据线 171 的露出部分上形成金属氧化物。

如上所述，第二钝化层 802 覆盖滤色器 230R、230G 和 230B 的边缘，

10 从而避免后续工艺破坏 230R、230G 和 230B，并避免污染上覆层及 LC 层 3。然而，第二钝化层 802 并没有设置在大部分像素电极 190 上，使得不会减少 LCD 的光透射率。

尽管参照优选实施例已经对本发明进行了详细地说明，但是本领域技术人员可以理解在不脱离所附权利要求中阐述的本发明精神和范围的基础上，可以对其进行各种改变和替代。

图 1

图 2

图 3

图 4A

图 4B

图 5A

图 5B

图 6

图 7

图 8

图 9A

图 9B

图 10A

图 10B

图 11A

图 11B

|                |                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器、所用的薄膜晶体管阵列板及其制造方法                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">CN1540426A</a>                                                                                                           | 公开(公告)日 | 2004-10-27 |

| 申请号            | CN200410047727.1                                                                                                                     | 申请日     | 2004-04-05 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                             |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                                                                                                             |         |            |

| [标]发明人         | 金东奎                                                                                                                                  |         |            |

| 发明人            | 金东奎                                                                                                                                  |         |            |

| IPC分类号         | G02F1/1335 G02F1/1339 G02F1/136 G02F1/1362 G02F1/1368 G02F1/139 G09F9/00 G09F9/30 H01L21/77 H01L21/84 H01L27/12 G02F1/133 H01L29/786 |         |            |

| CPC分类号         | G02F2001/136222 H01L27/1248 G02F1/1393 G02F1/136227 G02F1/13394 H01L27/1214 G02F1/133512 G02F1/133707 H01L27/124 H01L27/12           |         |            |

| 代理人(译)         | 侯宇                                                                                                                                   |         |            |

| 优先权            | 1020030021311 2003-04-04 KR                                                                                                          |         |            |

| 其他公开文献         | CN100378555C                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                                       |         |            |

#### 摘要(译)

本发明公开了一种液晶显示器、所用的薄膜晶体管阵列板及其制造方法，该薄膜晶体管阵列板包括：形成在绝缘衬底上的栅极线；在栅极线上的栅极绝缘层；在栅极绝缘层上的半导体层；形成在栅极绝缘层上的数据线；至少部分地形成在半导体层上的漏极电极；形成在数据线和漏极电极上的第一钝化层；形成在数据线和漏极电极上的滤色器；形成在滤色器上的第二钝化层；以及形成在滤色器上的像素电极，其与漏极电极连接，与第二钝化层交叠，并且由第一钝化层封闭。