(12)发明专利

(10)授权公告号 CN 102456334 B

(45)授权公告日 2016.08.03

(21)申请号 201110329203.1

1-5段,第6页第2段,图3A.

(22)申请日 2011.10.24

CN 1577013 A,2005.02.09,说明书第2页第1-5段,第6页第2段,图3A.

(30)优先权数据

10-2010-0105654 2010.10.28 KR

CN 1959480 A,2007.05.09,全文.

(73)专利权人 三星显示有限公司

US 6483494 B1,2002.11.19,说明书第4页第1-5段,第5页第1-5段,第6页第1-4段.

地址 韩国京畿道

US 2007/0229430 A1,2007.10.04,说明书[0038]、[0049]段,图5B.

(72)发明人 李丞珪 李东勳 金皓镐 朴晋佑

US 2008/0042957 A1,2008.02.21,说明书第[0025]段,图3.

(74)专利代理机构 北京英赛嘉华知识产权代理

有限责任公司 11204

审查员 庄怡倩

代理人 余朦 王艳春

(51)Int.Cl.

G09G 3/36(2006.01)

G02F 1/133(2006.01)

(56)对比文件

CN 1577013 A,2005.02.09,说明书第2页第

权利要求书3页 说明书16页 附图18页

(54)发明名称

液晶显示面板、液晶显示装置及液晶显示装

置的驱动方法

(57)摘要

本发明涉及液晶显示面板,包括:像素,以矩阵形式排列;第一子栅线,与所述像素中下侧相邻的第一行像素连接;第二子栅线,与上侧相邻的第二行像素连接;栅线,位于所述第一子栅线和所述第二子栅线之间,分别与相邻上侧的第二行像素和下侧的第一行像素以之字形连接;偶数数据线,与相邻的第一列像素连接;奇数数据线,与相邻的第二列像素连接。所述液晶显示面板可防止水平及垂直串扰,同时可有效减少功耗。

1. 一种液晶显示面板，包括：

多个像素，以矩阵形式排列；

第一子栅线，在所述像素中与下侧相邻的第一行像素连接；

第二子栅线，在所述像素中与上侧相邻的第二行像素连接；

多个栅线，位于所述第一子栅线和所述第二子栅线之间，每个栅线与上侧相邻的第二行像素和下侧相邻的第一行像素分别连接；

多个偶数数据线，在所述像素中与相邻的第一列像素连接；以及

多个奇数数据线，在所述像素中与相邻的第二列像素连接，

其中所述第一列像素与排列在同一列的所述像素中的奇数行的像素相应，并且所述第二列像素与排列在同一列的所述像素中的偶数行的像素相应；或者其中所述第一列像素与排列在同一列的所述像素中的偶数行的像素相应，并且所述第二列像素与排列在同一列的所述像素中的奇数行的像素相应，以及

其中所述第一行像素与排列在同一行的所述像素中的奇数列的像素相应，并且所述第二行像素与排列在同一行的所述像素中的偶数列的像素相应；或者其中所述第一行像素与排列在同一行的所述像素中的偶数列的像素相应，并且所述第二行像素与排列在同一行的所述像素中的奇数列的像素相应。

2. 根据权利要求1所述的液晶显示面板，其特征在于，在奇数帧期间，

向所述奇数数据线施加第一极性的数据信号、

向所述偶数数据线施加与所述第一极性相反的第二极性的数据信号。

3. 根据权利要求2所述的液晶显示面板，其特征在于，

在偶数帧期间，

向所述奇数数据线施加所述第二极性的数据信号、

向所述偶数数据线施加所述第一极性的数据信号。

4. 根据权利要求3所述的液晶显示面板，其特征在于，

所述第一极性以公共电压为基准是正极性，

所述第二极性以所述公共电压为基准是负极性。

5. 根据权利要求3所述的液晶显示面板，其特征在于，

所述第一极性以公共电压为基准是负极性，

所述第二极性以所述公共电压为基准是正极性。

6. 根据权利要求1所述的液晶显示面板，其特征在于，还包括：

电荷共享控制电路，以电荷共享控制信号为基础，使所述奇数数据线之间相互共享电荷，使所述偶数数据线之间相互共享电荷。

7. 根据权利要求6所述的液晶显示面板，其特征在于，所述电荷共享控制电路包括：

多个第一开关，以所述电荷共享控制电路为基础相互连接所述奇数数据线；以及

多个第二开关，以所述电荷共享控制信号为基础相互连接所述偶数数据线。

8. 根据权利要求7所述的液晶显示面板，其特征在于，

所述第一开关及所述第二开关以所述第一子栅线、所述第二子栅线、所述栅线为单位分别在像素充电之前导通。

9. 根据权利要求7所述的液晶显示面板，其特征在于，

所述第一开关及所述第二开关以所述第一子栅线、所述第二子栅线、所述栅线为单位分别在像素充电之后导通。

10. 根据权利要求1所述的液晶显示面板，其特征在于，所述像素分别包括：

开关器件，以所述第一子栅线、第二子栅线和所述栅线输出的栅信号为基础执行开关工作；以及

液晶电容器，以所述奇数数据线及偶数数据线输出的数据信号为基础调节液晶层的光透过率。

11. 根据权利要求10所述的液晶显示面板，其特征在于，

所述开关器件是薄膜晶体管，所述薄膜晶体管包括接收所述栅信号的栅电极、接收所述数据信号的源电极以及向所述液晶电容器输出数据信号的漏电极。

12. 根据权利要求11所述的液晶显示面板，其特征在于，每个所述像素还包括维持所述液晶电容器充电电压的储能电容器。

13. 一种液晶显示装置，包括：

液晶显示面板，间隔一水平周期的时差，向行方向将极性相同的数据信号施加至奇数列的像素和偶数列的像素，间隔一水平周期的时差，向列方向将极性相反的数据信号依次施加至排列于同一列的像素；

源驱动器，以数据控制信号为基础，将数据信号施加至所述液晶显示面板；

栅驱动器，以栅控制信号为基础，向所述液晶显示面板施加相应于扫描脉冲的栅信号；以及

时序控制器，生成所述数据控制信号及所述栅控制信号，

其中，所述液晶显示面板包括：

多个像素，以矩阵形式排列；

第一子栅线，在所述像素中与下侧相邻的第一行像素连接；

第二子栅线，在所述像素中与上侧相邻的第二行像素连接；

多个栅线，位于所述第一子栅线和所述第二子栅线之间，每个栅线与相邻上侧的第二行像素和下侧的第一行像素分别连接；

多个偶数数据线，在所述像素中与相邻的第一列像素连接；以及

多个奇数数据线，在所述像素中与相邻的第二列像素连接，

其中所述第一列像素与排列在同一列的所述像素中的奇数行的像素相应，并且所述第二列像素与排列在同一列的所述像素中的偶数行的像素相应；或者其中所述第一列像素与排列在同一列的所述像素中的偶数行的像素相应，并且所述第二列像素与排列在同一列的所述像素中的奇数行的像素相应，以及

其中所述第一行像素与排列在同一行的所述像素中的奇数列的像素相应，并且所述第二行像素与排列在同一行的所述像素中的偶数列的像素相应；或者其中所述第一行像素与排列在同一行的所述像素中的偶数列的像素相应，并且所述第二行像素与排列在同一行的所述像素中的奇数列的像素相应。

14. 根据权利要求13所述的液晶显示装置，其特征在于，所述液晶显示面板还包括：

电荷共享控制电路，以电荷共享控制信号为基础，使所述奇数数据线之间相互共享电荷，使所述偶数数据线之间相互共享电荷。

15. 根据权利要求13所述的液晶显示装置,其特征在于,

在奇数帧期间,向所述奇数数据线施加第一极性的数据信号,向所述偶数数据线施加与所述第一极性相反的第二极性的数据信号。

16. 根据权利要求15所述的液晶显示装置,其特征在于,

在偶数帧期间,向所述奇数数据线施加所述第二极性的数据信号,向所述偶数数据线施加所述第一极性的数据信号。

17. 一种液晶显示装置的驱动方法,所述液晶显示装置包括如权利要求1所述的液晶显示面板,所述方法包括:

向行方向,间隔一水平周期的时差,将极性相同的数据信号施加至奇数列的像素和偶数列的像素;

向列方向,间隔一水平周期的时差,将极性相反的数据信号依次施加至排列在同一列的像素;以及

针对每帧,变更供给到所述液晶显示面板的数据信号的极性。

## 液晶显示面板、液晶显示装置及液晶显示装置的驱动方法

### 技术领域

[0001] 本发明涉及显示装置,具体地说涉及液晶显示面板、液晶显示装置及液晶显示装置的驱动方法。

### 背景技术

[0002] 针对各个像素,液晶显示装置通过在液晶电容器的像素电极和公用电极之间形成电势差,以调节位于像素电极和公用电极之间的液晶层的光透过率的方式来显示影像。近来,广泛应用以薄膜晶体管作为像素内部开关器件的薄膜晶体管液晶显示装置。

[0003] 通常,液晶显示装置为防止像素内部的液晶电容器劣化,每隔一定周期反转数据信号的极性,采用如点(dot)反转方式、行(line)反转方式、列(column)反转方式、帧(frame)反转方式、Z反转方式、有源电位移(Active Level Shift,简称为:ALS)方式等现有的方式。然而,现有的方法产生如水平串扰、垂直串扰、多余的功耗等多种问题。

### 发明内容

[0004] 本发明的目的是提供防止水平串扰(horizontal crosstalk)及垂直串扰(vertical crosstalk)的同时还能有效减少功耗的液晶显示面板。

[0005] 本发明的另一目的是提供通过包括所述液晶显示面板以低功耗输出高品质影像的液晶显示装置。

[0006] 本发明的另一目的是提供在液晶显示面板中防止水平串扰及垂直串扰的同时还能有效减少功耗的液晶显示装置的驱动方法。

[0007] 为达到上述的本发明的目的,根据本发明实施例的液晶显示装置包括:多个像素,以矩阵形式排列;第一子栅线,在所述像素中与下侧相邻的第一-行像素连接;第二子栅线,在所述像素中与上侧相邻的第二-行像素连接;多个栅线,位于所述第一子栅线和所述第二子栅线之间,每个栅线与上侧相邻的第二-行像素和下侧相邻的第一-行像素分别连接;多个偶数数据线,在所述像素中与相邻的第一-列像素连接;以及多个奇数数据线,在所述像素中与相邻的第二-列像素连接。

[0008] 根据示例性的实施例,所述第一-行像素与排列在同一行的所述像素中的奇数列的像素相应,所述第二-行像素与排列在同一行的所述像素中的偶数列的像素相应。

[0009] 根据示例性的实施例,所述第一-列像素与排列在同一列的所述像素中的奇数行的像素相应,所述第二-列像素与排列在同一列的所述像素中的偶数行的像素相应。

[0010] 根据示例性的实施例,所述第一-列像素与排列在同一列的所述像素中的偶数行的像素相应,所述第二-列像素与排列在同一列的所述像素中的奇数行的像素相应。

[0011] 根据示例性的实施例,所述第一-行像素与排列在同一行的所述像素中的偶数列的像素相应,所述第二-行像素与排列在同一行的所述像素中的奇数列的像素相应。

[0012] 根据示例性的实施例,所述第一-列像素与排列在同一列的所述像素中的偶数行的像素相应,所述第二-列像素与排列在同一列的所述像素中的奇数行的像素相应。

- [0013] 根据示例性的实施例,所述第一-列像素与排列在同一列的所述像素中的奇数行的像素相应,所述第二-列像素与排列在同一列的所述像素中的偶数行的像素相应。

- [0014] 根据示例性的实施例,奇数帧期间,向所述奇数数据线施加第一极性的数据信号、向所述偶数数据线施加与所述第一极性相反的第二极性的数据信号。

- [0015] 根据示例性的实施例,偶数帧期间,向所述奇数数据线施加所述第二极性的数据信号、向所述偶数数据线施加所述第一极性的数据信号。

- [0016] 根据示例性的实施例,所述第一极性以公共电压为基准是正极性,所述第二极性以所述公共电压为基准是负极性。

- [0017] 根据示例性的实施例,所述第一极性以公共电压为基准是负极性,所述第二极性以所述公共电压为基准是正极性。

- [0018] 根据示例性的实施例,液晶显示面板还包括:电荷共享控制电路,所述电荷共享控制电路以电荷共享控制信号为基础,使所述奇数数据线之间相互共享电荷,使所述偶数数据线之间相互共享电荷。

- [0019] 根据示例性的实施例,所述电荷共享控制电路包括:多个第一开关,以所述电荷共享控制电路为基础相互连接所述奇数数据线;以及多个第二开关,以所述电荷共享控制信号为基础相互连接所述偶数数据线。

- [0020] 根据示例性的实施例,所述电荷共享控制信号与前电荷共享信号相应,所述第一开关及所述第二开关以所述第一子栅线、所述第二子栅线、所述栅线为单位分别在像素充电之前导通。

- [0021] 根据示例性的实施例,所述电荷共享控制信号与前电荷共享信号相应,所述第一开关及所述第二开关以所述第一子栅线、所述第二子栅线、所述栅线为单位分别在像素充电之后导通。

- [0022] 根据示例性的实施例,所述像素分别包括:开关器件,以所述第一子栅线、第二子栅线和所述栅线输出的栅信号为基础执行开关工作;以及液晶电容器,以所述奇数数据线及偶数数据线输出的数据信号为基础调节液晶层的光透过率。

- [0023] 根据示例性的实施例,所述开关器件是薄膜晶体管,所述薄膜晶体管包括接收所述栅信号的栅电极、接收所述数据信号的源电极以及向所述液晶电容器输出数据信号的漏电极。

- [0024] 根据示例性的实施例,每个所述像素还包括维持所述液晶电容器充电电压的储能电容器。

- [0025] 根据示例性的实施例的液晶显示装置,包括:液晶显示面板,间隔一水平周期的时差,向行方向将极性相同的数据信号施加至奇数列的像素和偶数列的像素,间隔一水平周期的时差,向列方向将极性相反的数据信号依次施加至排列于同一列的像素;源驱动器,以数据控制信号为基础,将数据信号施加至所述液晶显示面板;栅驱动器,以栅控制信号为基础,向所述液晶显示面板施加相应于扫描脉冲的栅信号;以及时序控制器,生成所述数据控制信号及所述栅控制信号。

- [0026] 根据示例性的实施例,所述液晶显示面板包括:多个像素,以矩阵形式排列;第一子栅线,在所述像素中与下侧相邻的第一-行像素连接;第二子栅线,在所述像素中与上侧相邻的第二-行像素连接;多个栅线,位于所述第一子栅线和所述第二子栅线之间,每个栅

线与相邻上侧的第二-行像素和下侧的第一-行像素分别连接；多个偶数数据线，在所述像素中与相邻的第一-列像素连接；以及多个奇数数据线，在所述像素中与相邻的第二-列像素连接。

[0027] 根据示例性的实施例，所述液晶显示面板还包括：电荷共享控制电路，以电荷共享控制信号为基础，使所述奇数数据线之间相互共享电荷，使所述偶数数据线之间相互共享电荷。

[0028] 根据示例性的实施例，所述第一-行像素相应于排列在同一行的所述像素中的奇数列的像素，所述第二-行像素相应于排列在同一行的所述像素中的偶数列的像素。

[0029] 根据示例性的实施例，所述第一-列像素相应于排列在同一列的所述像素中的奇数行的像素，所述第二-列像素相应于排列在同一列的所述像素中的偶数行的像素。

[0030] 根据示例性的实施例，所述第一-列像素相应于排列在同一列的所述像素中的偶数行的像素，所述第二-列像素相应于排列在同一列的所述像素中的奇数行的像素。

[0031] 根据示例性的实施例，所述第一-行像素相应于排列在同一行的所述像素中的偶数列的像素，所述第二-行像素相应于排列在同一行的所述像素中的奇数列的像素。

[0032] 根据示例性的实施例，所述第一-列像素相应于排列在同一列的所述像素中的奇数行的像素，所述第二-列像素相应于排列在同一列的所述像素中的偶数行的像素。

[0033] 根据示例性的实施例，所述第一-列像素相应于排列在同一列的所述像素中的偶数行的像素，所述第二-列像素相应于排列在同一列的所述像素中的奇数行的像素。

[0034] 根据示例性的实施例，在奇数帧期间，向所述奇数数据线施加第一极性的数据信号，向所述偶数数据线施加与所述第一极性相反的第二极性的数据信号。

[0035] 根据示例性的实施例，在偶数帧期间，向所述奇数数据线施加所述第二极性的数据信号，向所述偶数数据线施加所述第一极性的数据信号。

[0036] 为实现本发明另一目的，根据本发明实施例的液晶显示装置的驱动方法包括：向行方向，间隔一水平周期的时差，将极性相同的数据信号施加至奇数列的像素和偶数列的像素；向列方向，间隔一水平周期的时差，将极性相反的数据信号依次施加至排列在同一列的像素；以及针对每帧，变更供给到液晶显示面板的所述数据信号的极性。

[0037] 根据本发明实施例的液晶显示面板，针对在一帧期间的极性相同的数据信号按照每个数据线进行反转，并供给至液晶显示面板，从而可以减少功耗；间隔一水平周期的时差将极性相同的数据信号施加至构成一个行(row)的奇数列像素和偶数列像素，从而可以防止水平串扰；间隔一水平周期时差将极性相反的数据信号依次施加至构成一个列(column)的像素，从而可以防止垂直串扰。

[0038] 根据本发明实施例的液晶显示装置，通过包括所述液晶显示面板，可以以低功耗输出高品质影像。

[0039] 根据本发明实施例的液晶显示装置的驱动方法，在液晶显示面板内能够防止水平串扰及垂直串扰的同时还能够有效地减少功耗。

[0040] 但是，本发明的效果不限于此，在不脱离本发明的思想及领域的范围内可进行多种扩展。

## 附图说明

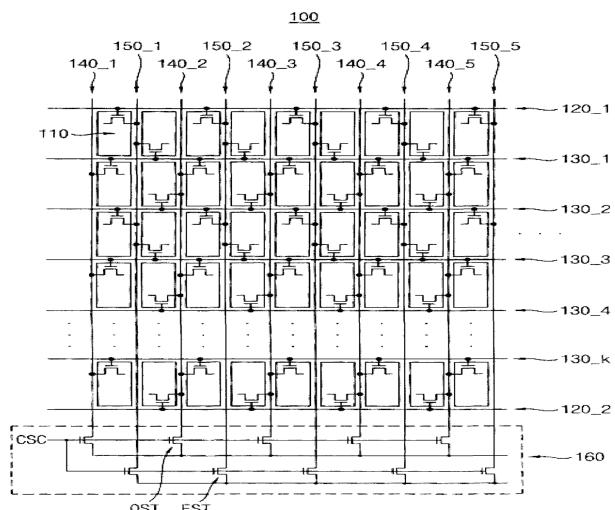

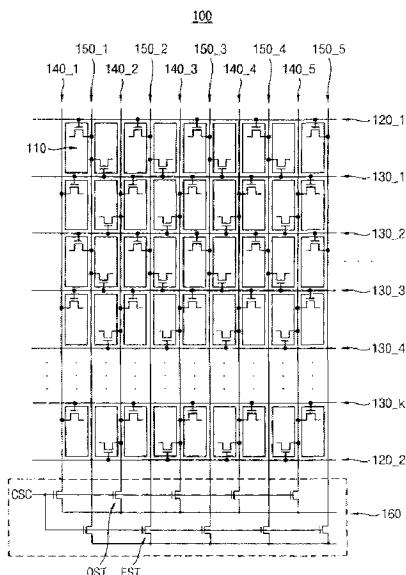

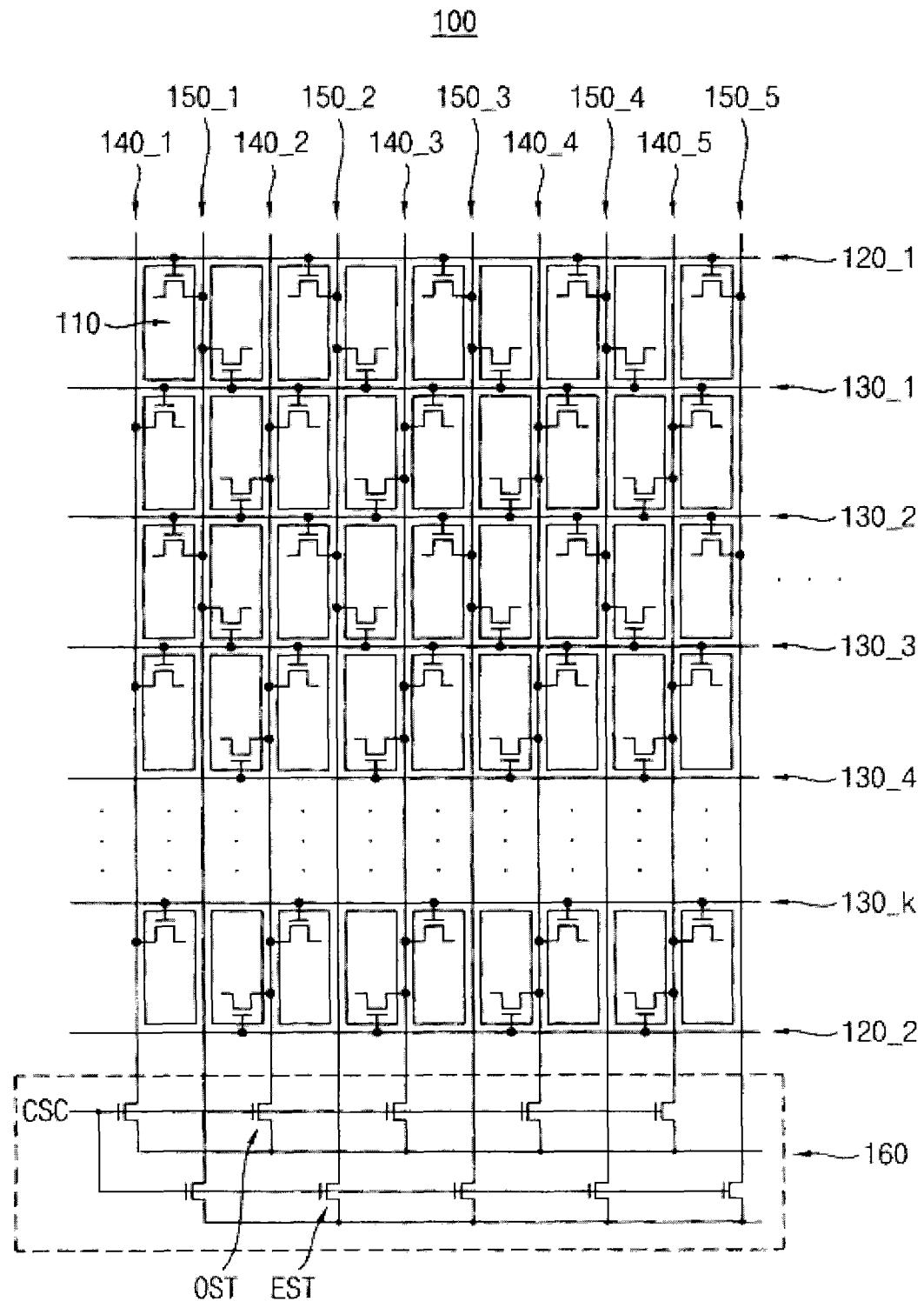

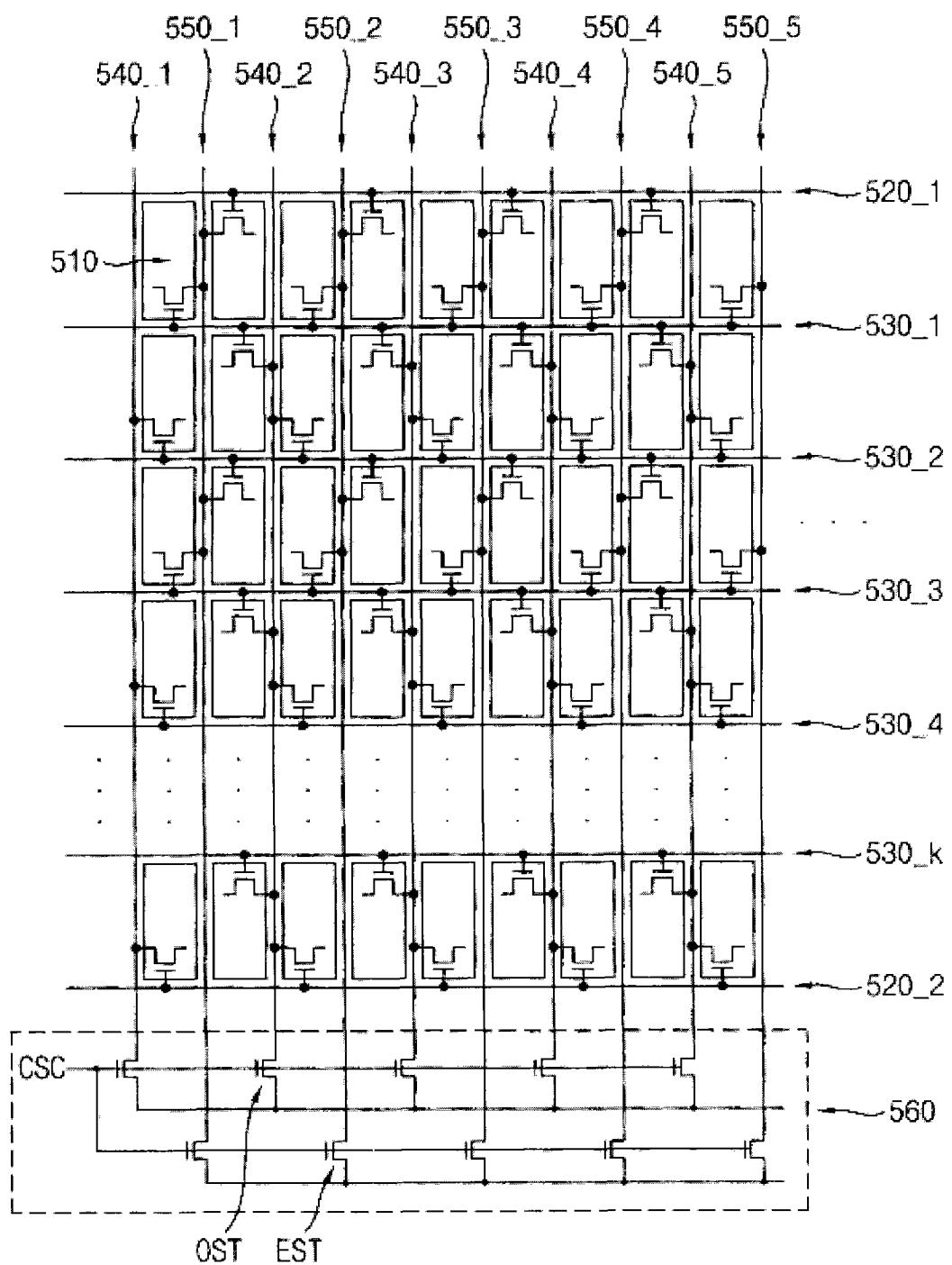

- [0041] 图1是根据本发明一实施例的液晶显示面板的示意图；

- [0042] 图2是显示图1中液晶显示面板上排列的像素结构的示意图；

- [0043] 图3是根据供给到图1液晶显示面板的数据信号的极性提供公共电压的时序图；

- [0044] 图4是在奇数帧期间供给到图1液晶显示面板的数据信号极性的示意图；

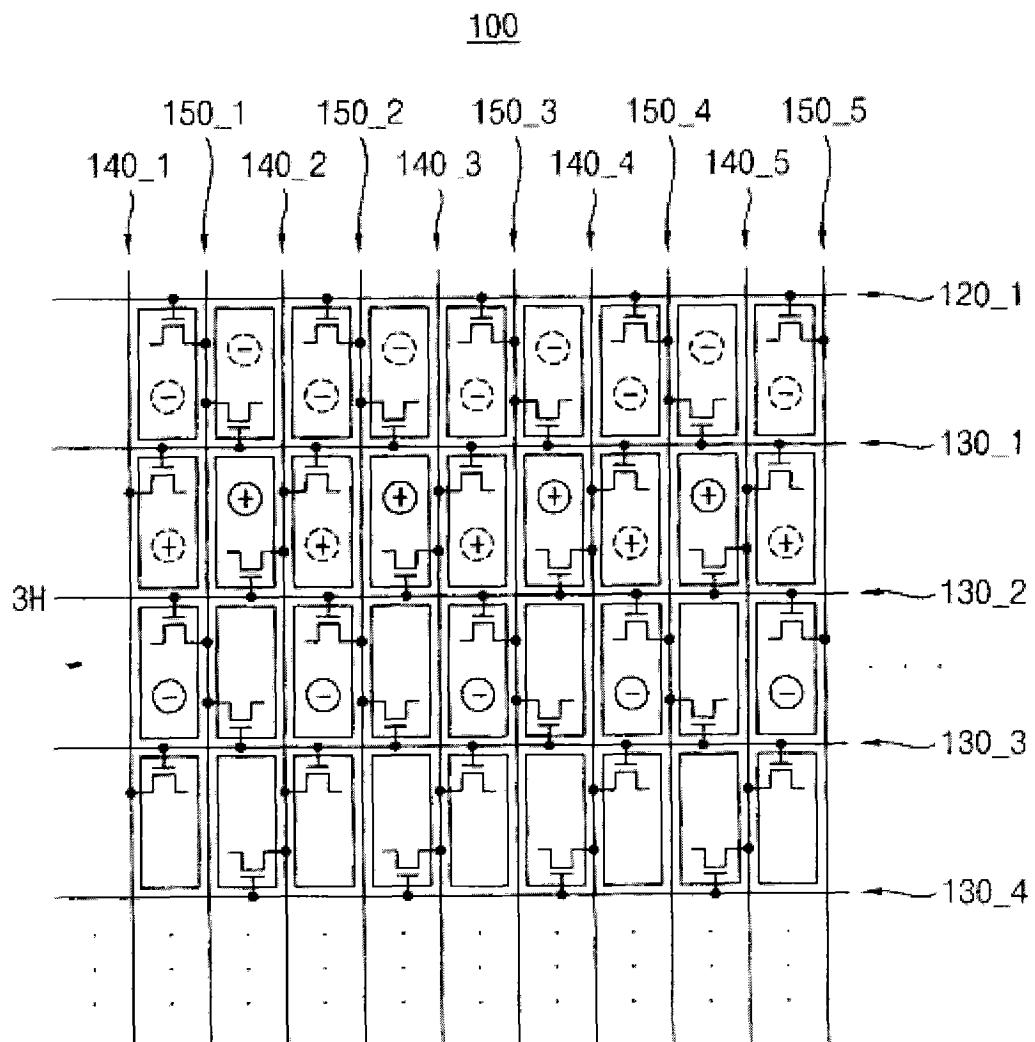

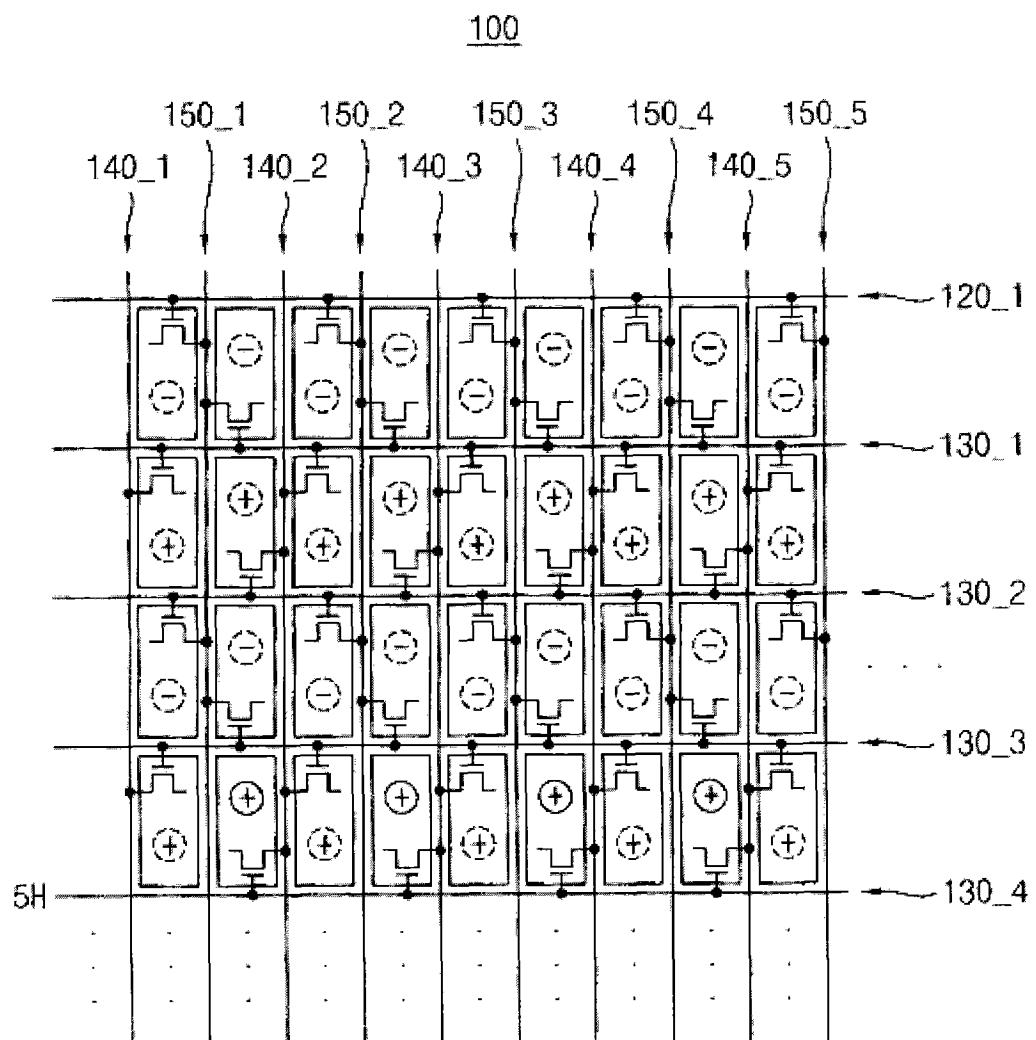

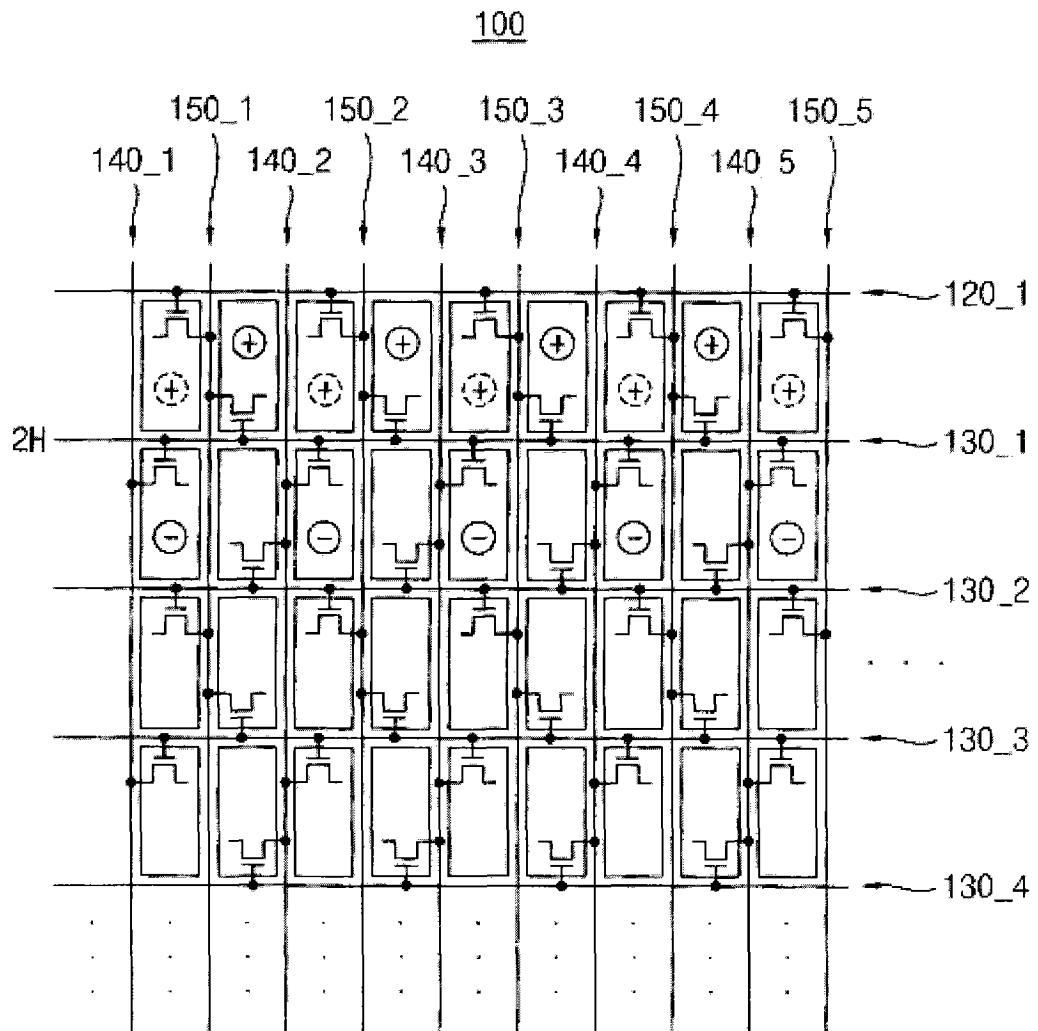

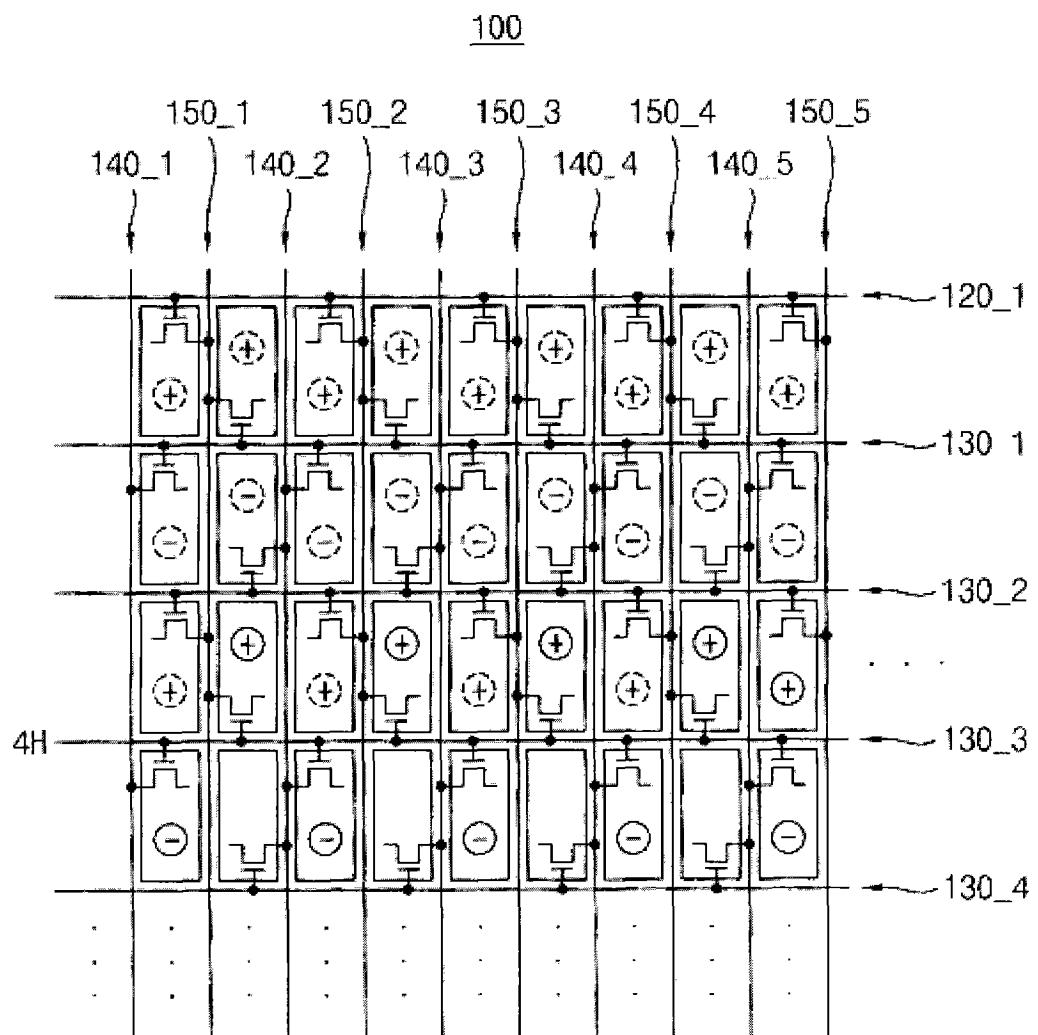

- [0045] 图5a至5e是在奇数帧期间数据信号施加至图1液晶显示面板上的像素的过程的示意图；

- [0046] 图6是在偶数帧期间向图1液晶显示面板供给的数据信号的极性的示意图；

- [0047] 图7a至7e是在偶数帧期间数据信号施加至图1液晶显示面板上的像素的过程的示意图；

- [0048] 图8是根据本发明的另一实施例的液晶显示面板的示意图；

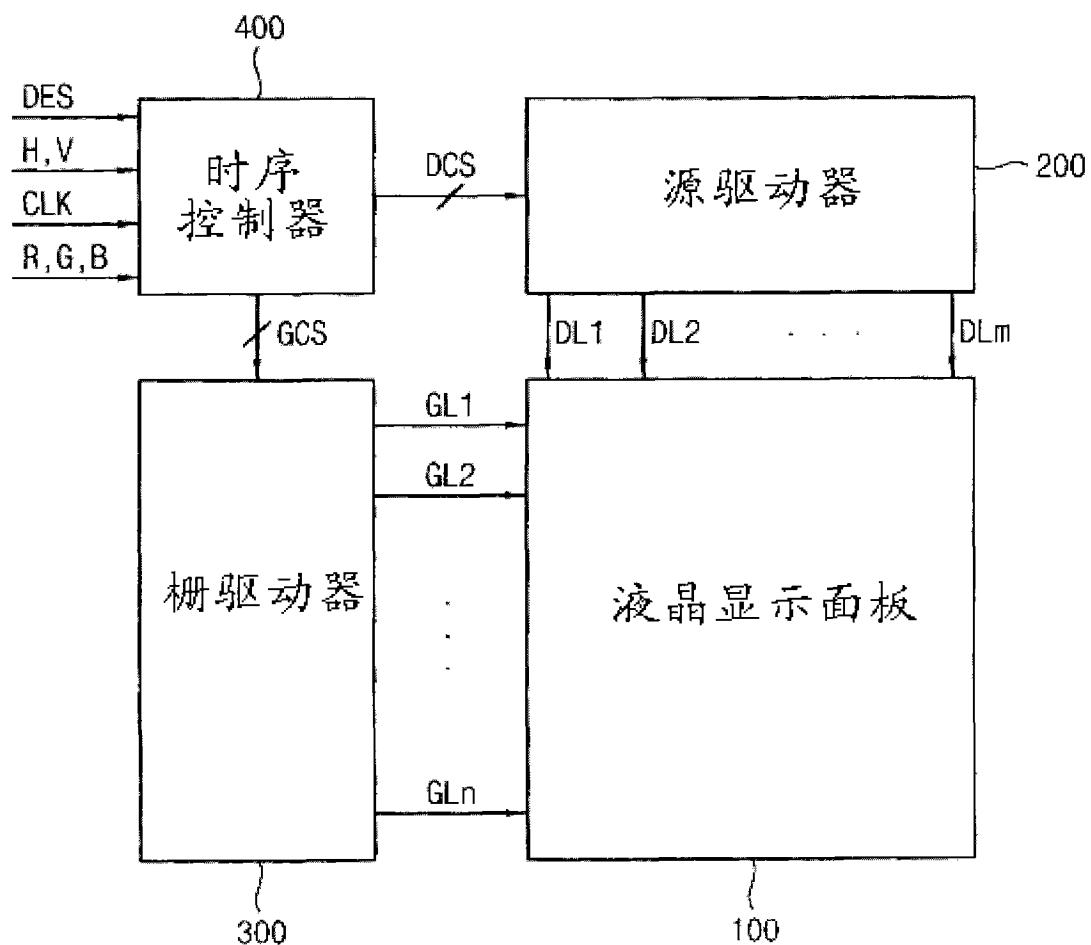

- [0049] 图9是具有根据本发明实施例的液晶显示面板的液晶显示装置的模块图；

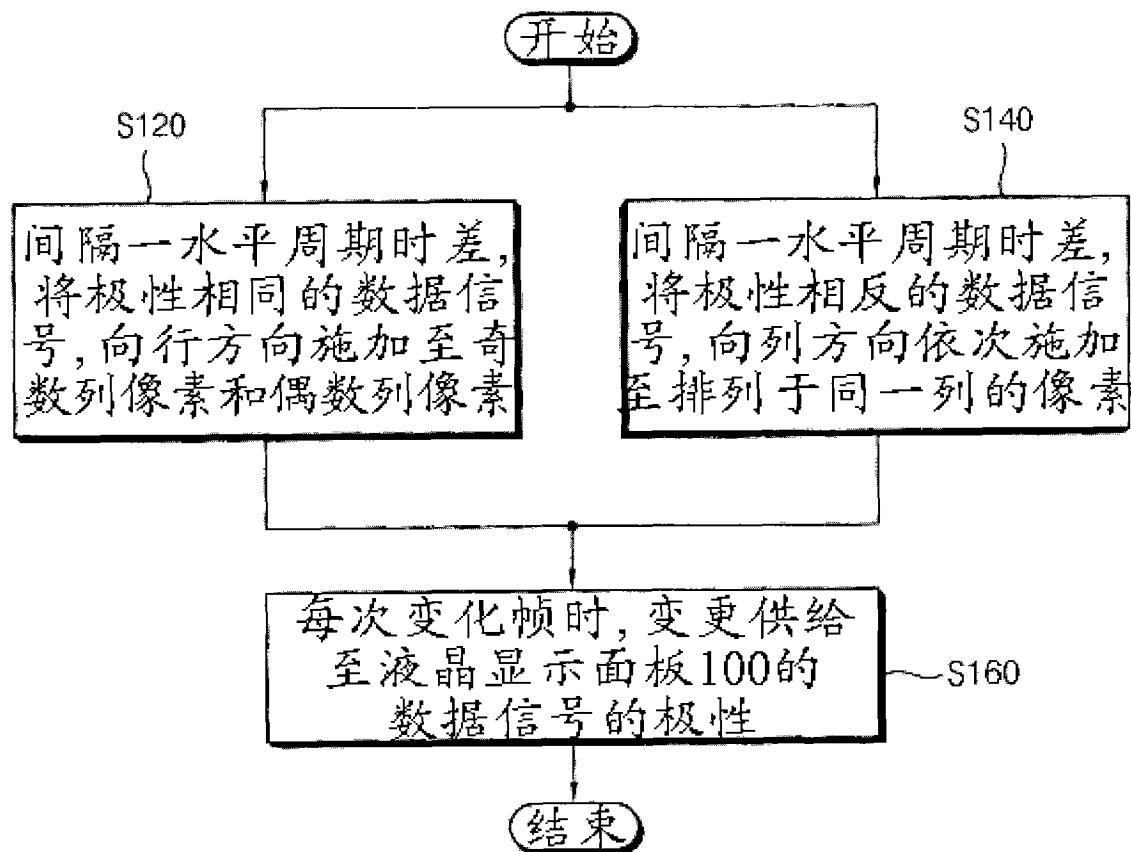

- [0050] 图10是驱动图9液晶显示装置的方法顺序图；

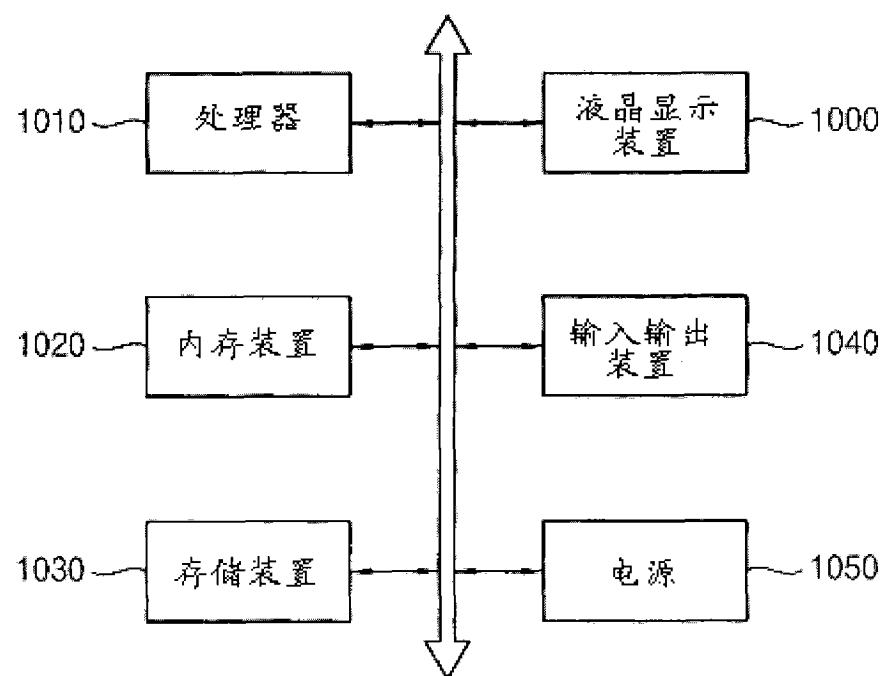

- [0051] 图11是包括图9的液晶显示装置的电子装置的框示图。

- [0052] 附图标记说明

- [0053] 100:液晶显示面板； 110:像素；

- [0054] 120\_1:第一子栅线； 120\_2:第二子栅线；

- [0055] 130:栅线； 140:奇数数据线；

- [0056] 150:偶数数据线； 160:电荷共享控制电路。

## 具体实施方式

[0057] 就本发明所公开的实施例，其特定的结构或功能性说明仅以示例性地说明本发明的实施例为目的，本发明的实施例能够以多种形式实施，不能解释为仅限于本文中说明的实施例。

[0058] 本发明可进行多种变化并具有多种形态，在此仅将特定实施例图示在附图中并在本文中进行详细说明。但是本发明不限定在特定的公开形态，在不脱离本发明的思想及技术范围的情况下应理解为包括所有变更、等同物以及替代物。

[0059] 虽然第一、第二等术语可以用于说明多种组成要素，但所述组成要素不限于所述术语。使用所述术语的目的在于区别一个组成要素与另一个组成要素。例如，在不脱离本发明的保护范围下，第一组成要素可以命名为第二组成要素，类似地，第二组成要素也可以命名为第一组成要素。

[0060] 某种组成要素与另外的组成要素描述为“连接”或“接触”，表示其与另外的组成要素直接连接或接触，也应理解为中间还可以存在其它组成要素。相反，某种组成要素与另外组成要素“直接连接”或“直接接触”，应理解为中间不存在其它组成要素。说明组成要素之间关系的其他表述方式，即“…之间”、“就在…之间”或者“与…相邻”和“…直接相邻”也应进行相同的解释。

[0061] 本申请所使用的术语仅以说明特定实施例而使用，并不用于限定本发明。单数表述在上下文中其含义有明显的以外，包括复数含义。本申请中“包括”、“具备”或“具有”等术语，应理解为仅用于阐明存在着所述的特定数字、步骤、动作、组成要素、部件或者其结合，并不是预先排除一个或一个以上的其它特征、数字、步骤、动作、组成要素、部件或其结

合的存在或附加的可能性。

[0062] 没有其他定义时,包括技术或科学术语,在此使用的所有术语,具有与本发明所属领域的普通技术人员通常理解的相同的含义。通常使用的词典所定义的相同的术语,应理解为与相关技术上下文所具有的含义一致,除本发明明确定义以外,不应解释成理想或过于形式的含义。

[0063] 以下结合附图,对本发明的具体实施例进行详细说明。附图中同一组成要素使用相同的附图标记,并省略对同一组成要素的重复说明。

[0064] 图1是根据本发明一实施例的液晶显示面板的示意图。

[0065] 如图1所示,液晶显示面板100可以包括多个像素110、第一子栅线120\_1、第二子栅线120\_2、栅线130\_1……130\_k、奇数数据线140\_1……140\_5及偶数数据线150\_1……150\_5。根据示例性的实施例,液晶显示面板100还可以包括电荷共享控制电路160。

[0066] 通常,液晶显示装置通过对各个像素,在液晶电容器的像素电极和公共电极施加电压而形成电场(即,电位差),调节位于像素电极和公共电极之间的液晶层的光透过率的方式能够显示影像。此时,在对液晶电容器的液晶层向一方向长时间施加电场时,会劣化液晶电容器。鉴于此,液晶显示装置为防止液晶电容器劣化,可按照一定极性周期反转数据信号的极性。例如,液晶显示装置可采用以下反转方式:按照每预定的行(row)和每预定的列(column)反转数据信号的极性的点反转方式;按照每栅线反转数据信号的极性的行(line)反转方式;按照每数据线反转数据信号的极性的列反转方式;按照每帧(frame)反转数据信号的极性的帧反转方式;在数据线方向以之字形排列像素,以列反转方式供给数据信号来实现点反转方式的Z反转方式;在行反转方式中,减少施加至公共电极的电压变位幅度的ALS反转方式等。

[0067] 但是,点反转方式虽然可以通过防止垂直串扰或水平串扰来提高画质,但是需要按照每预定的行和每预定的列反转数据信号的极性,因此具有数据信号的变位频率(即,数据信号的变动量)大从而导致功耗大的缺点。行反转方式相比点反转方式,虽然可以通过减小数据信号的变位频率来减少功耗,但是由于按照每栅线反转数据信号的极性,因此具有会发生水平串扰的缺点。列反转方式相比点反转,虽然可以通过减小数据信号的变位频率来减少功耗,但是由于按照每数据线反转数据信号的极性,因此具有会发生垂直串扰的缺点。由于帧反转方式是在每帧反转数据信号的极性,因此帧变更时,具有会发生闪烁(flicker)的缺点。Z反转方式相比点反转方式,虽然可减少功耗,但是具有在特定数据信号的模式(pattern)下会发生纵向条纹的缺点。ALS反转方式相比行反转,虽然可以通过减少施加至公共电极的电压变位幅度来减少功耗,但是与行反转方式相同,具有会发生水平串扰的缺点。

[0068] 在本发明的实施例中,液晶显示面板100的像素110能够以矩阵(matrix)形式排列在第一子栅线120\_1、第二子栅线120\_2及栅线130\_1…130\_k与奇数数据线140\_1…140\_5及偶数数据线150\_1…150\_5交叉的位置上。像素110可以通过内部的开关器件(即,薄膜晶体管)的栅(gate)电极连接到第一子栅线120\_1、第二子栅线120\_2及栅线130\_1…130\_k,可以通过所述薄膜晶体管的源(source)电极连接到奇数数据线140\_1…140\_5及偶数数据线150\_1…150\_5。例如,第一子栅线120\_1、第二子栅线120\_2及栅线130\_1…130\_k输出的栅信号(即,扫描脉冲)可以通过薄膜晶体管的栅电极输入到像素110。而且,奇数数据线

140\_1...140\_5及偶数数据线150\_1...150\_5输出的数据信号可以通过所述薄膜晶体管的源电极输入到像素110。示例性的实施例中,像素110可以分别包括薄膜晶体管、液晶电容器(liquid crystal capacitor)、储能电容器(storage capacitor)。此时,所述液晶电容器可以包括用于施加有数据信号的像素电极、用于施加有公共电压的公共电极、及位于它们之间的具有介电各向异性(dielectric anisotropy)的液晶层。

[0069] 在液晶显示面板100中,第一子栅线120\_1及第二子栅线120\_2可以位于栅线130\_1,...,130\_k的外围。例如,第一子栅线120\_1可以与在其下侧与之邻接的第一行像素相连接,第二子栅线120\_2可以与在其上侧与之邻接的第二行像素相连接。栅线130\_1...130\_k位于第一子栅线120\_1和第二子栅线120\_2之间,分别可以与上侧的第二行像素和下侧的第一行像素以之字形(zigzag)连接。其中,行像素是指构成一个行的像素。例如,第一行像素可以与排列在同一行的像素110中奇数列的像素相应,第二行像素可以与排列在同一行的像素110中的偶数列的像素相应。即,第一子栅线120\_1可以与位于上部最外围的像素110中奇数列的像素连接,第二子栅线120\_2可以与位于下部最外围的像素110中偶数列的像素连接。栅线130\_1...130\_k可以分别与上侧行像素中偶数列的像素连接,并且分别可以与下侧的行像素中奇数列的像素连接。

[0070] 而且,液晶显示面板100上与奇数数据线140\_1...140\_5连接的像素110和与偶数数据线150\_1...150\_5连接的像素110可以相互不同。例如,奇数数据线140\_1...140\_5可以与第二列像素连接,偶数列数据线150\_1...150\_5可以与第一列像素连接。示例性的实施例中,第一列像素可以与排列在同一列像素110中的奇数行像素相应,第二列像素可以与排列在同一列像素110中的偶数行像素相应。根据另一实施例,第一列像素可以与排列在同一列像素110中的偶数行像素相应,第二列像素与排列在同一列像素中的奇数行像素相应。但是,图1仅图示了奇数数据线140\_1...140\_5与排列在同一列像素110中的偶数行的像素连接,偶数数据线150\_1...150\_5与排列在同一列像素110中的奇数行的像素相连接的实施例。

[0071] 如上所述,液晶显示面板100的像素110具有如下独特结构:通过薄膜晶体管的栅电极与第一子栅线120\_1、第二子栅线120\_2及栅线130\_1...130\_k连接,通过薄膜晶体管的源电极与奇数数据线140\_1...140\_5及偶数数据线150\_1...150\_5连接,在一帧期间向奇数数据线140\_1...140\_5供给第一极性的数据信号、向偶数数据线150\_1...150\_5供给与所述第一极性相反的第二极性的数据信号时,极性相同的数据信号间隔一水平周期时差施加至排列在同一行的相邻的像素(即,相邻的行像素)上,向排列在同一列的相邻像素(即,相邻的列像素)施加极性相反的数据信号。此时,液晶显示面板100以所述独特结构为基础而工作,实际上可以与列反转方式相似的方式供给数据信号。例如,对于液晶显示面板100,在奇数帧期间可以将第一极性数据信号供给到奇数数据线140\_1...140\_5,可以将第二极性数据信号供给到偶数数据线150\_1...150\_5,相反,在偶数帧期间,可以将第二极性数据信号供给到奇数数据线140\_1...140\_5,可以将第一极性数据信号供给到偶数数据线150\_1...150\_5。

[0072] 而且,液晶显示面板100还可以包括电荷共享控制电路160,使奇数数据线140\_1...140\_5之间相互共享电荷、使偶数数据线150\_1...150\_5之间相互共享电荷(charge)。在示例性的实施例中,电荷共享控制电路160可包括:第一开关OST,可基于电荷共享控制信

号(CSC)使奇数数据线140\_1...140\_5相互连接;以及第二开关EST,可基于电荷共享控制信号(CSC)使偶数数据线150\_1...150\_5相互连接。此时,电荷共享控制信号(CSC)可以为前电荷共享信号(Pre-Charge Sharing,简称为:PCS)。根据示例性的实施例,第一开关OST及第二开关EST,以所述第一子栅线120\_1、所述第二子栅线120\_2、所述栅线130\_1...130\_k为单位分别在充电像素之前导通(turn on),或者充电所述像素110之后导通,从而能够使奇数数据线140\_1...140\_5之间相互共享电荷、能够使偶数数据线150\_1...150\_5之间共享电荷。例如,第一开关OST及第二开关EST为N型金属氧化物(NMOS)晶体管时,如果电荷共享控制信号(CSC)具有逻辑“高”电平,导通第一开关OST及第二开关EST,可以使奇数数据线140\_1...140\_5相互连接,可以使偶数数据线150\_1...150\_5相互连接。相反,第一开关OST及第二开关EST为P型金属氧化物PMOS晶体管时,如果电荷共享控制信号(CSC)具有逻辑“低”电平,导通第一开关OST及第二开关EST,可以使奇数数据线140\_1...140\_5相互连接,可以使偶数数据线150\_1...150\_5相互连接。依此,液晶显示面板100包括电荷共享控制电路160,在大变化的模式中(pattern)中也可以减少功耗,以提高像素110的充电特性来提高整体的性能。如上所述,以液晶显示面板100具有电荷共享控制电路160而进行了说明,根据所需条件电荷共享电路160也可以装备在集成电路(integrated circuit,简称为:IC)内部。

[0073] 如上所述,液晶显示装置为防止像素110内部液晶电容器的劣化,而每隔一定周期反转数据信号的极性,液晶显示面板100以所述独特结构为基础,在一帧期间以每个数据线为单位反转供给极性相同的数据信号,从而可以有效减少功耗。间隔一水平周期的时差,将极性相同的数据信号供给至构成一个行的奇数列像素和偶数列像素,从而能够防止水平串扰。间隔一水平周期的时差,依次施加极性相反的数据信号至构成一个列的像素110,从而能够防止垂直串扰。另外,为在液晶显示面板100上呈现颜色,各个像素110可以固定显示红色(red)、绿色(green)以及蓝色(blue)之中的一种或者显示黄色(yellow)、青色(cyan)、紫红色(magenta)中的一种颜色(即,空间分隔),或者可以按时间轮流显示红色(red)、绿色(green)以及蓝色(blue)或者黄色(yellow)、青色(cyan)以及紫红色(magenta)(即,时间分隔)。此时,液晶显示面板能够以红色(red)、绿色(green)以及蓝色(blue)或者黄色(yellow)、青色(cyan)以及紫红色(magenta)的空间或者时间的集合来显示图像。为此,虽未在图1中显示,液晶显示面板100可以在像素110分别对应的位置上具备红色滤光片、绿色滤光片、及蓝色滤光片或者黄色滤光片、青色滤光片以及紫红色滤光片。

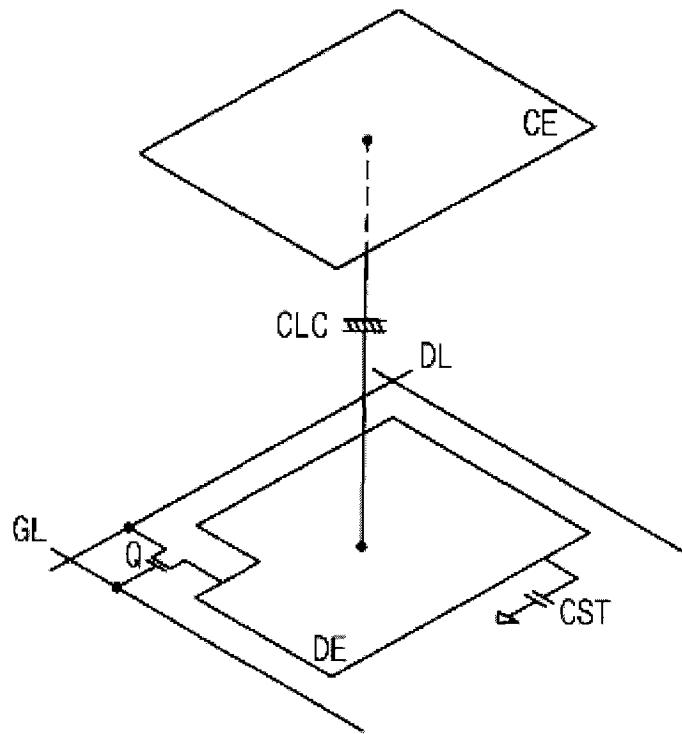

[0074] 图2是显示图1中液晶显示面板上排列的像素结构的示意图。

[0075] 如图2所示,像素110可以分别包括开关器件Q、液晶电容器CLC及储能电容器CST。根据示例性的实施例,开关器件Q可以为由非晶硅(amorphous silicon)形成的薄膜晶体管(TFT)。

[0076] 开关器件Q可形成在下部显示基板上。所述薄膜晶体管(TFT)响应数据GL供给的栅信号,可以将数据线DL供给的数据信号供给到液晶电容器CLC上。为此,开关器件Q可通过栅电极连接到栅线GL上,可通过源电极连接到数据线DL,可通过漏电极连接到液晶电容器CLC。以施加至像素电极DE的数据信号和施加至公共电极CE的公共电压的电位差来充电液晶电容器CLC,以这种充电电压为基础,可以调节液晶层的光透过率。例如,常黑模式(normally black)时,数据信号和公共电压的电位差,即充电电压越大可增加液晶层的光透过率,数据信号和公共电压的电位差,即充电电压越小可减少液晶层的光透过率。为此,

液晶电容器CLC可以包括形成在下部显示基板的像素电极DE和形成在上部显示基板的公共电极CE，在像素电极DE和公共电极CE之间可以包含液晶层。根据示例性的实施例，也可以在下部显示基板形成液晶电容器CLC的公共电极CE。例如，像素电极DE连接于开关器件Q的漏电极，并可以施加有供给自与源电极连接的数据线DL的数据信号，公共电极CE可以通过形成在下部显示基板的信号线(未图示)施加公共电压。示例性的实施例中，施加数据信号和公共电压到液晶显示面板100，施加正极性数据信号时施加低公共电压，施加负极性数据信号时，施加高公共电压。此时，实际上，因相比施加的数据信号更高的电压引导到液晶电容器CLC，从而能够相对减少功耗。储能电容器CST可维持液晶电容器CLC的充电电压。即，储能电容器CST执行液晶电容器CLC的辅助功能，其可通过在下部显示板的信号线(未图示)和像素电极DE之间设置绝缘体而形成。然而，像素110根据所需条件可不包括储能电容器CST。虽未在图2显示，但上部显示基板可设置滤光片，所述上部显示基板和/或所述下部显示基板可附有偏光板。

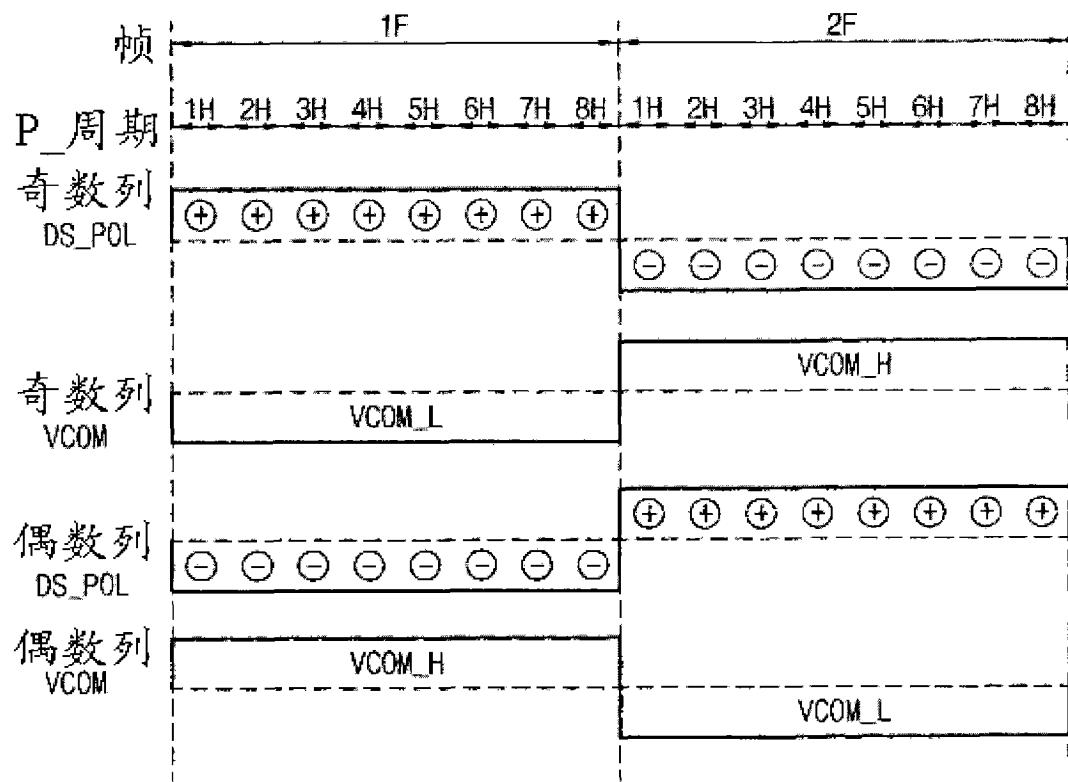

[0077] 图3是根据供给到图1液晶显示面板的数据信号的极性显示公共电压的时序图。

[0078] 如图3所示，第一帧1F和接着所述第一帧1F的第二帧2F可以分别由多个水平周期(1H....8H)形成。此时，第一帧1F可相当于奇数帧，第二帧2F可相当于偶数帧。另外，液晶显示面板100的影像显示是以帧为单位来实现的，第一帧1F和接着所述第一帧1F的第二帧2F可持续反复，直到完成液晶显示面板100的影像显示为止。

[0079] 第一帧1F由多个水平周期1H....8H形成，在每个水平周期1H....8H，栅信号施加至栅线120\_1、130\_1...130\_k、120\_2，输出自奇数数据线140\_1...140\_5或者偶数数据线150\_1...150\_5的数据信号，选择地可施加至所对应的行的奇数列像素或者偶数列像素上。另外，对于液晶显示装置向液晶显示面板100供给数据信号时的公共电压，向液晶显示面板100供给正极性数据信号时，可供给相对低的公共电压(VCOM\_L)；供给负极性数据信号时，可供给相对高的公共电压(VCOM\_H)。例如，第一帧1F期间，具有正极性的数据信号供给到奇数数据线140\_1...140\_5时，连接到奇数数据线140\_1...140\_5的公共电极上可供给相对低的公共电压(VCOM\_L)。而且，第一帧1F期间，偶数数据线150\_1...150\_5供给负极性数据信号时，与偶数数据线150\_1...150\_5的连接像素公共电极可以供给相对高的公共电压(VCOM\_H)。相同地，第二帧2F期间，负极性数据信号供给到奇数数据线140\_1...140\_5时，与奇数数据线140\_1...140\_5连接的像素的公共电极可以供给相对高的公共电压(VCOM\_H)。而且，第二帧2F期间，正极性数据信号供给到偶数数据线150\_1...150\_5时，与偶数数据线150\_1...150\_5连接的像素的公共电极，可供给相对低的公共电压(VCOM\_L)。其结果，引导相比实际施加的数据信号高的充电电压至像素内部的液晶电容器(CLC)。依此，向液晶显示面板100供给公共电压的方式，与以帧为单位交替反转公共电压来提高像素的充电电压的ALS反转方式相似。因此，相比所施加的数据信号更高的充电电压被引导至液晶显示面板100，功耗可以相比以往的反转方式例如点反转方式小。

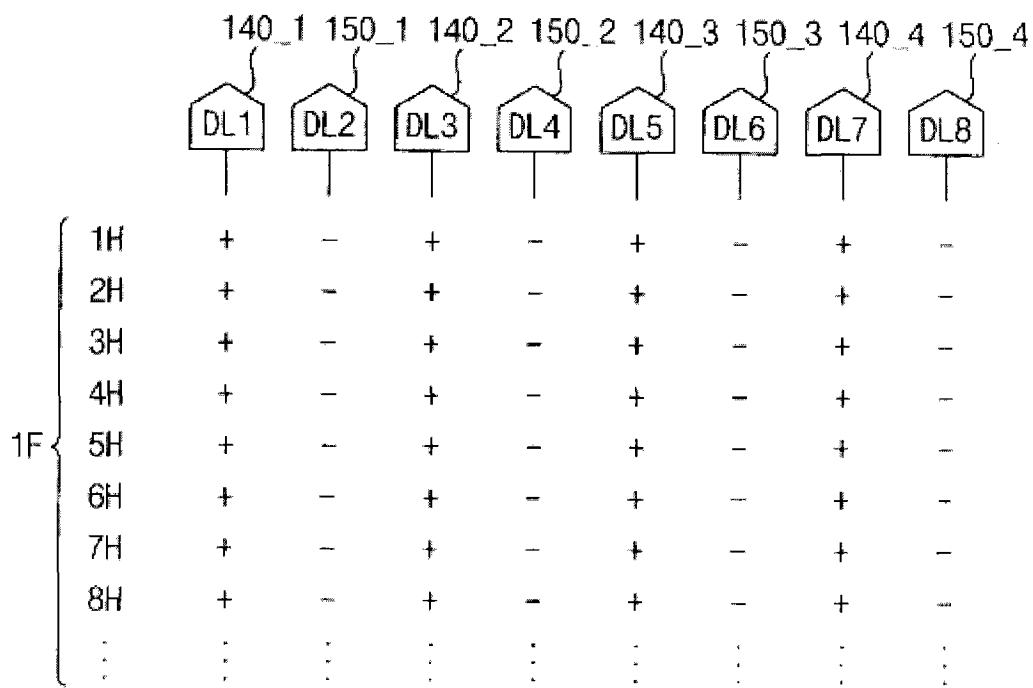

[0080] 图4是奇数帧期间供给到图1液晶显示面板的数据信号极性的示意图。

[0081] 如图4所示，液晶显示装置在奇数帧1F期间向液晶显示面板100的数据线DL1...DL8施加数据信号，液晶显示面板100的数据线DL1...DL8区分奇数数据线140\_1...140\_5和偶数数据线150\_1...150\_5，对此分别供给极性相反的数据信号。例如，液晶显示装置在奇数帧1F期间，向奇数数据线140\_1...140\_5可以依次供给正极性数据信号，向偶

数数据线150\_1...150\_5可以依次供给负极性数据信号。只是如下所述,在奇数帧1F期间供给的数据信号极性与偶数帧2F期间供给的数据信号的极性相反。但是,液晶显示装置100上显示的极性模式可能与施加至数据线DL1...DL8的数据信号的极性模式不同。此时,可以将施加数据信号的极性模式定义为驱动极性模式(driver polarity pattern),可以将液晶显示面板100上显示的数据信号极性模式定义为视极性模式(apparent polarity pattern)。如下所述,液晶显示面板100的驱动极性模式与列反转方式的驱动极性模式相似,视极性模式除间隔一水平周期时差,向排列在同一行的奇数列的像素和偶数列的像素施加数据信号之外,与ALS反转方式的视极性模式或行反转方式的视极性模式相似。对此,参考图5a至图5e说明如下。

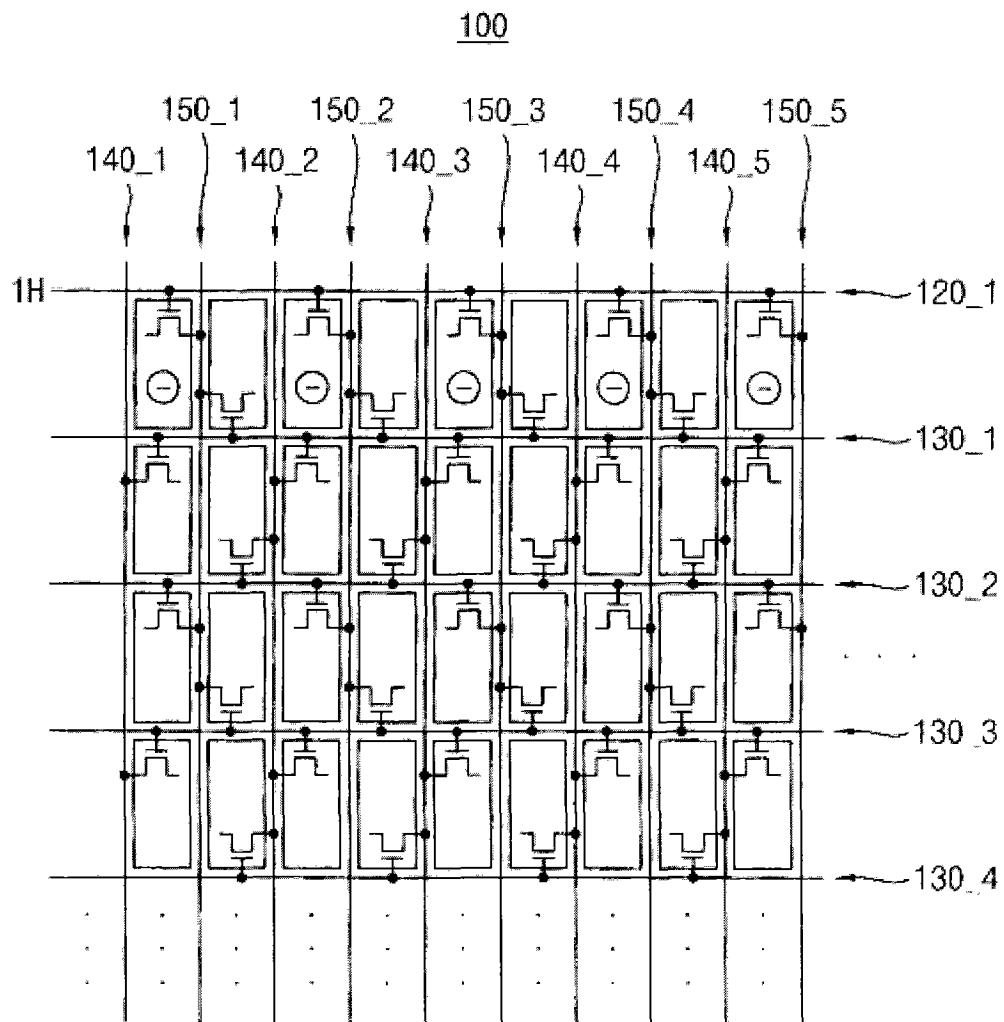

[0082] 图5a至图5e是在奇数帧期间数据信号施加至图1液晶显示面板上的像素的过程的示意图。

[0083] 如图5a所示,在第一水平周期1H,向第一子栅线120\_1可施加用于导通像素内部薄膜晶体管的栅信号。此时,第一子栅线120\_1只与排列在第一行的像素110中奇数列的像素相连接,数据信号只施加到排列在第一行的像素110中奇数列的像素110上。而且,排列在第一行的像素110中的奇数列的像素连接于偶数数据线150\_1...150\_5,奇数帧1F期间向偶数数据线150\_1...150\_5供给的数据信号的极性为负,因此在第一水平周期1H,负极性数据信号仅可以施加至排列在第一行的像素110中奇数列的像素。依此,在第一水平周期1H,不同时向相邻的行像素施加数据信号,因此能够防止水平串扰。

[0084] 如图5b所示,在第二水平周期2H,向第一栅线130\_1可施加用于导通像素内部薄膜晶体管的栅信号。此时,因第一栅线130\_1连接于排列在第一行的像素110中偶数列的像素以及排列在第二行像素110中奇数列的像素,所以数据信号可以仅施加到排列在第一行像素110中的偶数列的像素和排列在第二行像素110中奇数列的像素。而且,排列在第一行像素110中的偶数列的像素连接到偶数数据线150\_1...150\_5,在奇数帧1F期间向偶数数据线150\_1...150\_5供给的数据信号为负极性,因此在第二水平周期2H,负极性数据信号仅可以施加至排列在第一行的像素110中偶数列的像素。相反,排列在第二行的像素110中,奇数列的像素连接于奇数数据线140\_1...140\_5,在奇数帧1F期间供给到奇数数据线140\_1...140\_5的数据信号为正极性,在第二水平周期2H排列在第二行的像素110中奇数列的像素可施加正极性数据信号。依此,在第二水平周期2H,相邻的行像素之间不同时施加数据信号,从而不仅可以防止水平串扰,而且相邻的列像素,即排列在第一行的像素110和排列在第二行的像素110施加极性相反的数据信号,因此还能防止垂直串扰。

[0085] 如图5c所示,在第三水平周期3H,向第二栅线130\_2可施加用于导通像素内部薄膜晶体管的栅信号。此时,因第二栅线130\_2连接于排列在第二行像素110中偶数列的像素以及排列在第三行像素110中奇数列的像素,所以数据信号可仅施加到排列在第二行像素110中的偶数列的像素和排列在第三行像素110中奇数列的像素。而且,排列在第二行的像素110中的偶数列的像素连接到奇数列数据线140\_1...140\_5,在奇数帧1F期间供给到奇数数据线140\_1...140\_5的数据信号为正极性,因此在第三水平周期3H排列在第二行的像素110中偶数列的像素可施加有正极性数据信号。然而,排列在第三行的像素110中奇数列的像素连接于偶数数据线150\_1...150\_5,在奇数帧1F期间供给到偶数数据线150\_1...150\_5的数据信号为负极性,因此第三水平周期3H排列在第三行的像素110中排列在奇数列的像素可

施加有负极性数据信号。依此，在第三水平周期3H，相邻的行像素之间不同时施加数据信号，从而不仅可以防止水平串扰，而且相邻的列像素，即排列在第二行的像素110和排列在第三行的像素110施加极性相反的数据信号，因此还能防止垂直串扰。

[0086] 如图5d所示，在第四水平周期4H，向第三栅线130\_3可施加用于导通像素内部薄膜晶体管的栅信号。此时，因第三栅线1303连接于排列在第三行像素110中偶数列的像素、排列在第四行像素110中奇数列的像素，所以数据信号可仅施加到排列在第三行像素110中的偶数列的像素和排列在第四行像素110中奇数列的像素。而且，排列在第三行的像素110中偶数列的像素连接到偶数数据线150\_1...150\_5，在奇数帧1F期间供给到偶数数据线150\_1...150\_5的数据信号可为负极性，因此在第四水平周期4H排列在第三行的像素110中偶数列的像素可施加有负极性数据信号。相反，排列在第四行的像素110中奇数列的像素连接于奇数数据线140\_1...140\_5，在奇数帧1F期间供给到奇数数据线140\_1...140\_5的数据信号为正极性，因此第四水平周期4H排列在第四行的像素110中排列在奇数列的像素可施加有正极性数据信号。依此，第四水平周期4H，相邻的行像素之间不同时施加数据信号，从而不仅可以防止水平串扰，而且相邻的列像素，即排列在第三行的像素110和排列在第四行的像素110施加极性相反的数据信号，因此还能防止垂直串扰。

[0087] 如图5e所示，第五水平周期5H，向第四栅线130\_4可施加用于导通像素内部薄膜晶体管的数据信号。如上所述，在第五水平周期5H，排列在第四行的像素110中偶数列的像素可施加正极性数据信号。然而，排列在第五行的像素110中奇数列的像素施加负极性数据信号。依此，在第五水平周期5H，相邻的行像素之间不同时施加数据信号，不仅可以防止水平串扰，而且相邻的列像素，即排列在第四行的像素110和排列在第五行的像素110施加极性相反的数据信号，因此还能防止垂直串扰。这种过程反复至栅信号施加到第二子栅线120\_2直到奇数帧1F结束为止，在后续的偶数帧2F中可变更数据信号极性。如图5a至5e所示，在液晶显示面板100中驱动极性模式与列反转方式的驱动极性模式相似，视极性模式除数据信号间隔一水平周期的时差施加到排列在同一行的奇数列的像素和偶数列的像素之外，与ALS反转方式的视极性反转模式、行反转方式的视极性模式相似。

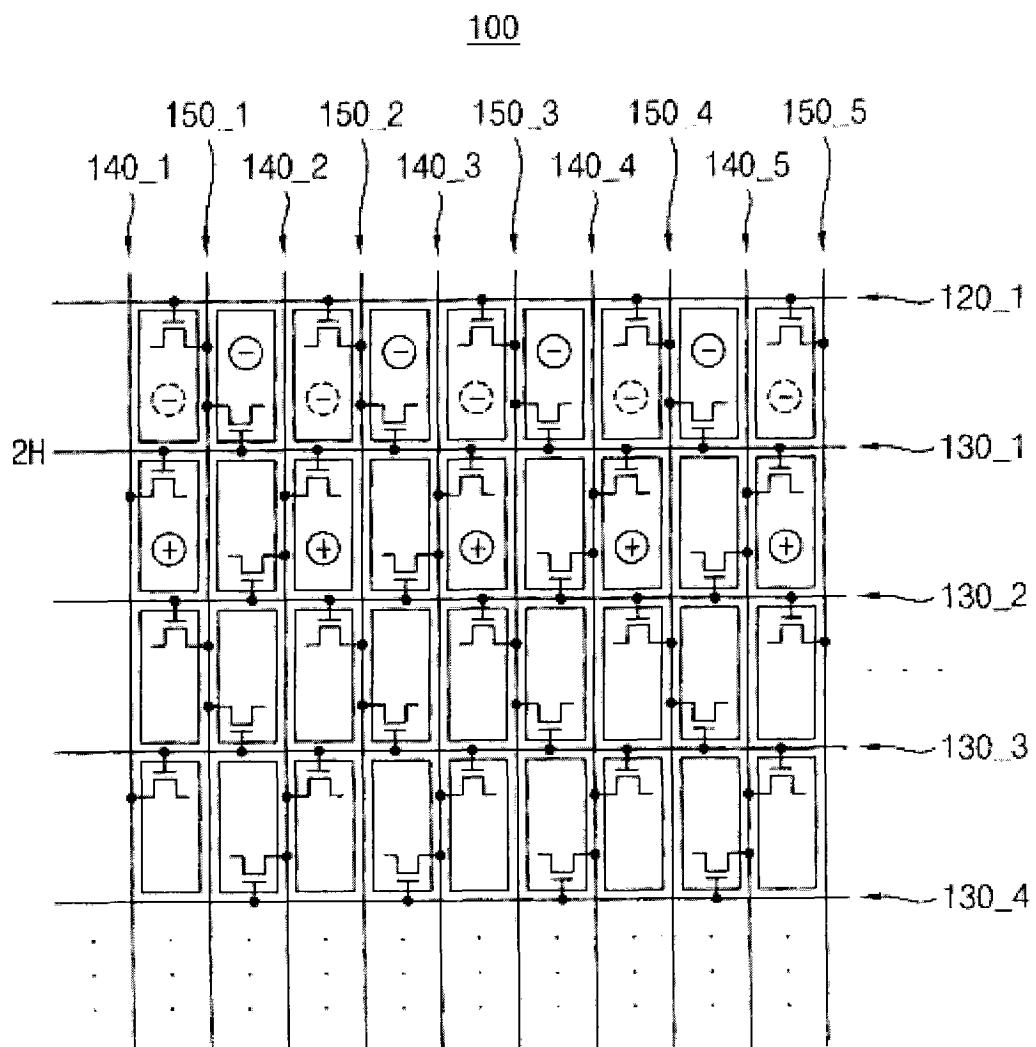

[0088] 图6是在偶数帧期间向图1液晶显示面板供给的数据信号的极性的示意图。

[0089] 如图6所示，液晶显示装置在偶数帧2F期间向液晶显示面板100的数据线DL1...DL8施加数据信号，液晶显示面板100的数据线DL1...DL8区分奇数数据线140\_1...140\_5和偶数数据线150\_1...150\_5，对此分别供给极性相反的数据信号。例如，液晶显示装置在偶数帧2F期间，向奇数数据线140\_1...140\_5可以依次供给负极性数据信号，向偶数数据线150\_1...150\_5可以依次供给正极性数据信号。即，在偶数帧2F期间供给的数据信号极性与奇数帧1F期间供给的数据信号的极性相反。如上所述，液晶显示面板100上显示的极性模式与施加到数据线DL1...DL8的数据信号的极性模式不同。即，液晶显示面板100的驱动极性模式与列反转方式的驱动极性模式相似，视极性模式除数据信号间隔一水平周期时差，向排列在同一行的奇数列的像素和偶数列的像素施加数据信号之外，与ALS反转方式的视极性模式或行反转方式的视极性模式相似。对此，参考图7a至图7e说明如下。

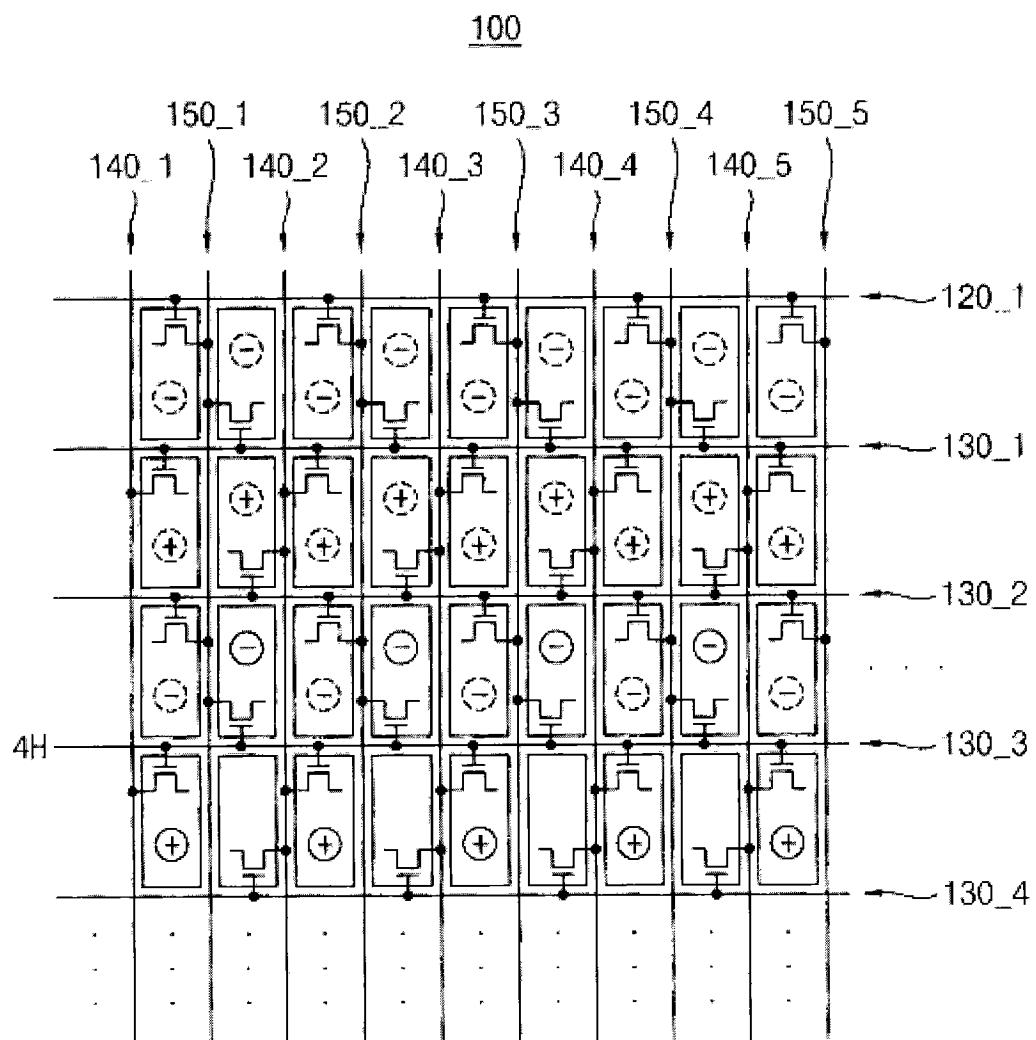

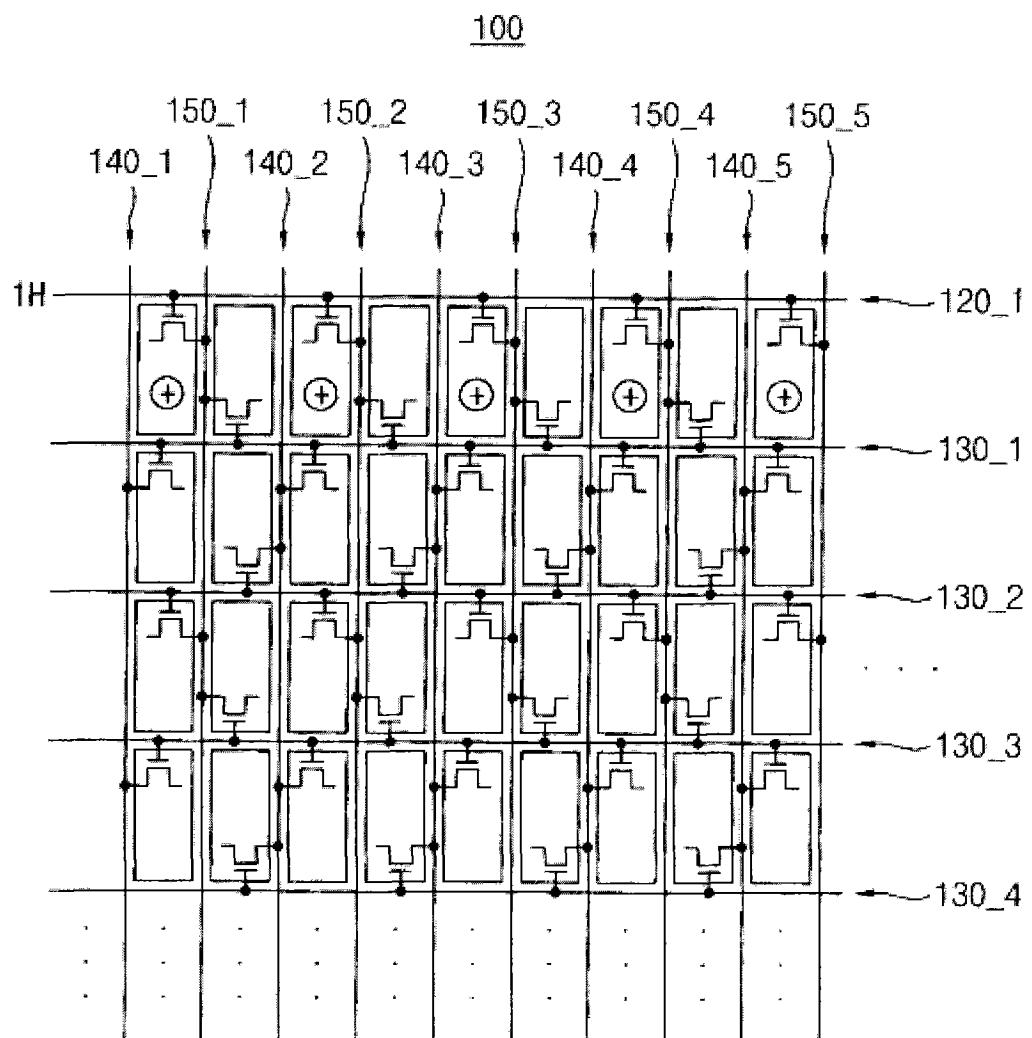

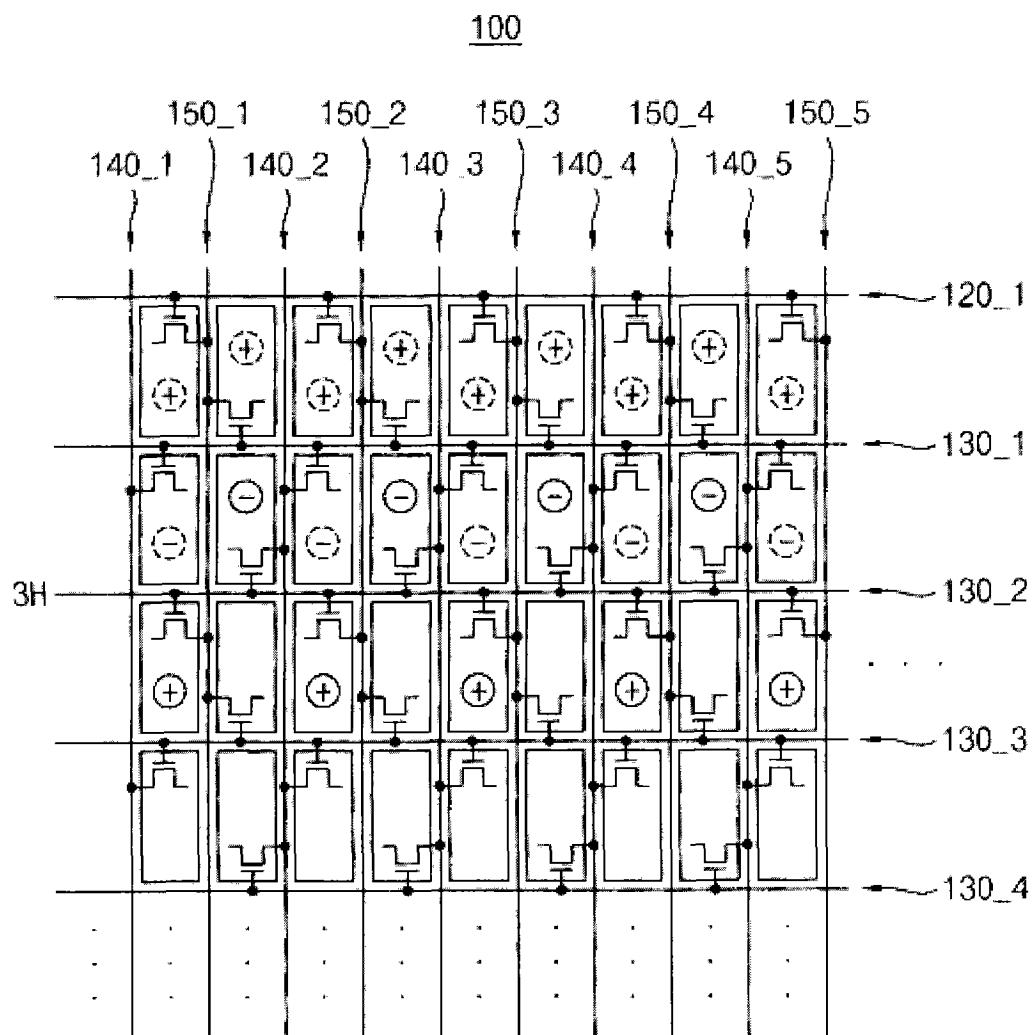

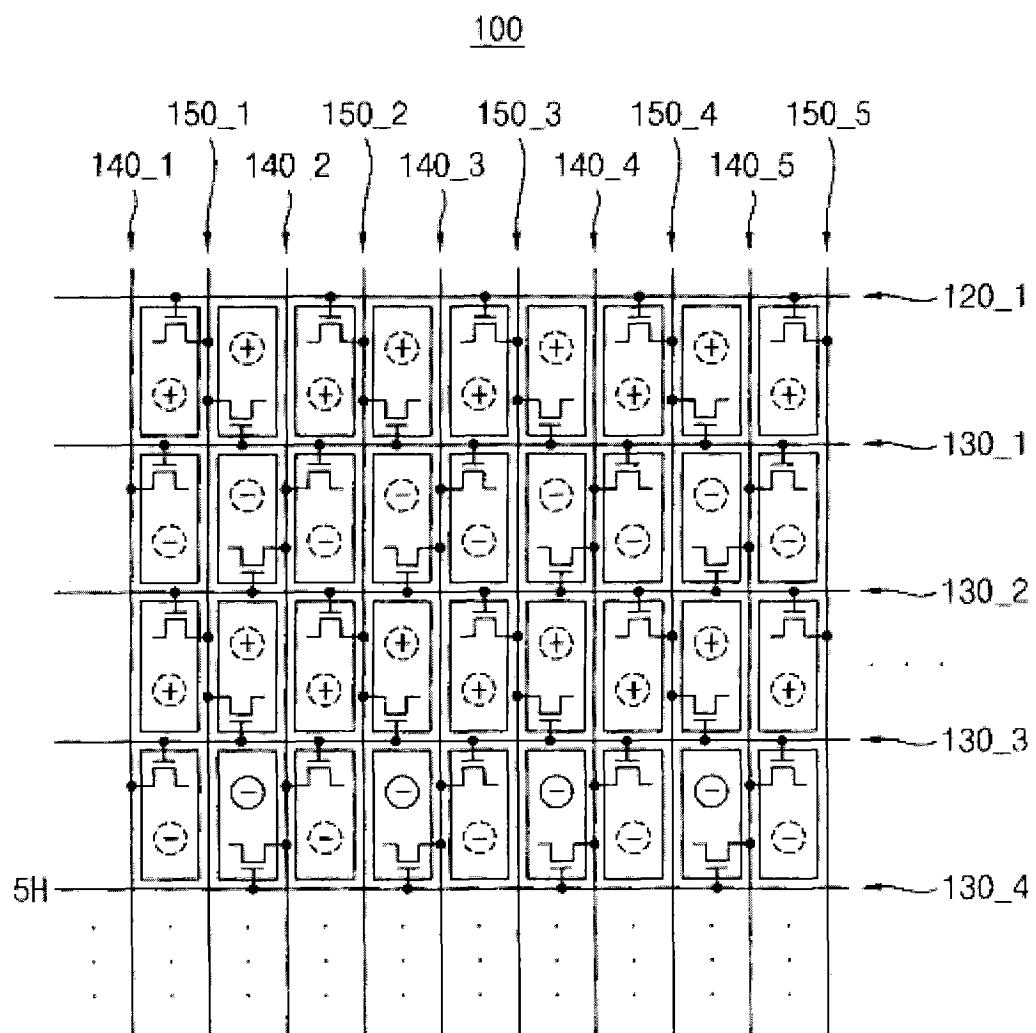

[0090] 图7a至7e是在偶数帧期间数据信号施加至图1液晶显示面板上的像素的过程的示意图。

[0091] 参考图7a，在第一水平周期1H，向第一子栅线120\_1可施加用于导通像素内部薄膜

晶体管的栅信号。此时,第一子栅线120\_1只与排列在第一行的像素110中奇数列的像素相连接,数据信号只施加到排列在第一行的像素110中奇数列的像素110上。而且,排列在第一行的像素110中的奇数列的像素连接于偶数数据线150\_1...150\_5,偶数帧2F期间向偶数数据线150\_1...150\_5供给的数据信号的极性为正,因此在第一水平周期1H,正极性数据信号仅可以施加至排列在第一行的像素110中奇数列的像素。依此,在第一水平周期1H,不同时向相邻的行像素施加数据信号,因此能够防止水平串扰。

[0092] 如图7b所示,在第二水平周期2H,向第一栅线130\_1可施加用于导通像素内部薄膜晶体管的栅信号。此时,因第一栅线130\_1连接于排列在第一行的像素110中偶数列的像素以及排列在第二行的像素110中奇数列的像素,所以数据信号可以仅施加至排列在第一行的像素110中的偶数列的像素和排列在第二行的像素110中奇数列的像素。而且,排列在第一行的像素110中的偶数列的像素连接到偶数数据线150\_1...150\_5,在偶数帧2F期间向偶数数据线150\_1...150\_5供给的数据信号为正极性,因此在第二水平周期2H,正极性数据信号仅可以施加至排列在第一行的像素110中偶数列的像素。相反,排列在第二行的像素110中,奇数列的像素连接于奇数数据线140\_1...140\_5,在偶数帧2F期间,供给到奇数数据线140\_1...140\_5的数据信号为负极性,在第二水平周期2H,排列在第二行的像素110中奇数列的像素可施加负极性数据信号。如此,在第二水平周期2H,相邻的行像素之间不同时施加数据信号,不仅可以防止水平串扰,而且相邻的列像素,即排列在第一行的像素110和排列在第二行的像素110施加极性相反的数据信号,因此还能防止垂直串扰。

[0093] 如图7c所示,在第三水平周期3H,向第二栅线130\_2可施加用于导通像素内部薄膜晶体管的栅信号。此时,因第二栅线130\_2连接于排列在第二行的像素110中偶数列的像素以及排列在第三行的像素110中奇数列的像素,所以数据信号可仅施加到排列在第二行的像素110中的偶数列的像素和排列在第三行的像素110中奇数列的像素。而且,排列在第二行的像素110中的偶数列的像素连接到奇数数据线140\_1...140\_5,在偶数帧2F期间供给到奇数数据线140\_1...140\_5的数据信号为负极性,因此在第三水平周期3H排列在第二行的像素110中偶数列的像素可施加有负极性数据信号。然而,排列在第三行的像素110中奇数列的像素连接于偶数数据线150\_1...150\_5,在偶数帧2F期间供给到偶数数据线150\_1...150\_5的数据信号为正极性,因此第三水平周期3H排列在第三行的像素110中排列在奇数列的像素可施加有正极性数据信号。依此,在第三水平周期3H,相邻的行像素之间不同时施加数据信号,从而不仅可以防止水平串扰,而且相邻的列像素,即排列在第二行的像素110和排列在第三行的像素110施加极性相反的数据信号,因此还能防止垂直串扰。

[0094] 如图7d所示,在第四水平周期4H,向第三栅线130\_3可施加用于导通像素内部薄膜晶体管的栅信号。此时,因第三栅线130\_3连接于排列在第三行的像素110中偶数列的像素、排列在第四行的像素110中奇数列的像素,所以数据信号可仅施加到排列在第三行的像素110中的偶数列的像素和排列在第四行的像素110中奇数列的像素。而且,排列在第三行的像素110中偶数列的像素连接到偶数数据线150\_1...150\_5,在偶数帧2F期间供给到偶数数据线150\_1...150\_5的数据信号可为正极性,因此在第四水平周期4H排列在第三行的像素110中偶数列的像素可施加有正极性数据信号。相反,排列在第四行的像素110中奇数列的像素连接于奇数数据线140\_1...140\_5,在偶数帧2F期间供给到奇数数据线140\_1...140\_5的数据信号为负极性,因此第四水平周期4H排列在第四行的像素110中排列在奇数列的像

素可施加有负极性数据信号。依此,第四水平周期4H,相邻的行像素之间不同时施加数据信号,从而不仅可以防止水平串扰,而且相邻的列像素,即排列在第三行的像素110和排列在第四行的像素110施加极性相反的数据信号,因此还能防止垂直串扰。

[0095] 如图7e所示,在第五水平周期5H,向第四栅线130\_4可施加用于导通像素内部薄膜晶体管的数据信号。如上所述,在第五水平周期5H,排列在第四行的像素110中偶数列的像素可施加负极性数据信号。然而,排列在第五行的像素110中奇数列的像素施加正极性数据信号。依此,在第五水平周期5H,相邻的行像素之间不同时施加数据信号,不仅可以防止水平串扰,而且相邻的列像素,即排列在第四行的像素110和排列在第五行的像素110施加极性相反的数据信号,因此还能防止垂直串扰。这种过程反复至栅信号施加到第二子栅线120\_2直到偶数帧2F结束为止,在后续的偶数帧2F中可变更数据信号极性。如图7a至7e所示,在液晶显示面板100中驱动极性模式与列反转方式的驱动极性模式相似,视极性模式除数据信号间隔一水平周期的时差施加到排列在同一行的奇数列的像素和偶数列的像素之外,与ALS反转方式的视极性反转模式、行反转方式的视极性模式相似。

[0096] 图8是根据本发明的另一实施例的液晶显示面板的示意图。

[0097] 如图8所示,液晶显示面板500,可以包括多个像素510、第一子栅线520\_1、第二子栅线520\_2、栅线530\_1...530\_k、奇数数据线540\_1...540\_5以及偶数数据线550\_1...550\_5。示例性的实施例中,液晶显示面板500还可以包括电荷共享控制电路560。

[0098] 液晶显示面板500的像素510,能够以矩阵形式排列在第一子栅线520\_1、第二子栅线520\_2及栅线530\_1...530\_k和奇数数据线540\_1...540\_5及偶数数据线550\_1...550\_5交叉的位置上。像素510可以通过内部的开关器件(即,薄膜晶体管)的栅电极连接到第一子栅线520\_1、第二子栅线520\_2及栅线530\_1...530\_k,可以通过所述薄膜晶体管的源电极与奇数数据线540\_1...540\_5及偶数数据线550\_1...550\_5连接。例如,第一子栅线520\_1、第二子栅线520\_2及栅线530\_1...530\_k输出的栅信号(即,扫描脉冲)可以通过薄膜晶体管的栅电极输入到像素510。而且,奇数数据线540\_1...540\_5及偶数数据线550\_1...550\_5输出的数据信号,可以通过所述薄膜晶体管的源电极输入到像素510。

[0099] 在液晶显示面板500中,第一子栅线520\_1及第二子栅线520\_2可以位于栅线530\_1...530\_k的外围。例如,第一子栅线520\_1可与在其下侧与之邻接的第一行像素相连,第二子栅线520\_2可以与在其上侧与之邻接的第二行像素相连。栅线530\_1...530\_k位于第一子栅线520\_1和第二子栅线520\_2之间,分别与上侧的第二行像素和下侧的第一行像素以之字形连接。示例性的实施例中,所述第一行像素可以与排列在同一行的像素510中偶数列的像素510相应,第二行像素可以与排列在同一行的像素510中的奇数列的像素510相应。即,第一子栅线520\_1可以与位于上部最外围的像素510中偶数列的像素连接,第二子栅线520\_2可以与位于下部最外围的像素510中奇数列的像素510连接。栅线530\_1...530\_k可以分别与上侧行像素中奇数列的像素连接,栅线530\_1...530\_k可以分别与下侧的行像素中偶数列的像素连接。

[0100] 而且,液晶显示面板500上,与奇数数据线540\_1...540\_5连接的像素510和与偶数数据线550\_1...550\_5连接的像素510可以相互不同。例如,奇数数据线540\_1...540\_5可以与第二列像素连接,偶数列数据线550\_1...550\_5可以与第一列像素连接。示例性的实施例中,第一列像素可以与排列在同一列像素510中的奇数行像素510相应,第二列像素可

以与排列在同一列像素510中的偶数行像素510相应。根据另一实施例,第一-列像素可以与排列在同一列像素510中的偶数行像素510相应,第二-列像素可以与排列在同一列像素510中的奇数行像素510相应。但是,图8仅图示了奇数数据线540\_1...540\_5与排列在同一列像素510中的偶数行的像素510连接,偶数数据线550\_1...550\_5与排列在同一列像素510中的奇数行的像素510相连接的实施例。

[0101] 如上所述,液晶显示面板500具有如下独特结构:像素510通过薄膜晶体管的栅电极与第一子栅线520\_1、第二子栅线520\_2及栅线530\_1...530\_k连接,通过薄膜晶体管的源电极与奇数数据线540\_1...540\_5及偶数数据线550\_1...550\_5连接,在一帧期间向奇数数据线540\_1...540\_5供给第一极性的数据信号、向偶数数据线550\_1...550\_5供给与所述第一极性相反的第二极性的数据信号时,极性相同的数据信号间隔一水平周期的时差施加到排列在同一行的相邻的像素(即,相邻的行像素)上,向排列在同一列的相邻像素(即,相邻的列像素)施加极性相反的数据信号。此时,液晶显示面板500以所述独特结构为基础而工作,实际上可以与列反转方式相似的方式供给数据信号。例如,对于液晶显示面板500,在奇数帧期间可以将第一极性数据信号供给到奇数数据线540\_1...540\_5,可以将第二极性数据信号供给到偶数数据线550\_1...550\_5,相反,在偶数帧期间,可以将第二极性数据信号供给到奇数数据线540\_1...540\_5,可以将第一极性数据信号供给到偶数数据线550\_1...550\_5。

[0102] 而且,液晶显示面板500还可以包括电荷共享控制电路560,用于在奇数数据线540\_1...540\_5之间相互共享电荷、在偶数数据线550\_1...550\_5之间相互共享电荷。在示例性的实施例中,电荷共享控制电路560可包括:第一开关OST,可基于电荷共享控制信号CSC使奇数数据线540\_1...540\_5相互连接;以及第二开关EST,可基于电荷共享控制信号CSC使偶数数据线550\_1...550\_5相互连接。此时,电荷共享控制信号CSC可以为前电荷共享信号。根据示例性的实施例,第一开关OST及第二开关EST,以第一子栅线520\_1、所述第二子栅线520\_2、所述栅线530\_1...530\_k为单位分别充电像素510之前导通,或者充电所述像素510以后导通,使奇数数据线540\_1...540\_5之间可以相互共享电荷、使偶数数据线550\_1...550\_5之间可以共享电荷。如依此,液晶显示面板500包括电荷共享控制电路560,在大变化大的模式中(pattern)也可以减少功耗,以提高像素510的充电特性来提高整体的性能。如上所述,以液晶显示面板500具有电荷共享控制电路560而进行了说明,根据所需条件电荷共享电路560也可以装备在集成电路(integrated circuit,简称为:IC)内部。

[0103] 图9是具有根据本发明实施例的液晶显示面板的液晶显示装置的模块图。

[0104] 如图9所示,液晶显示装置1000包括液晶显示面板100、源驱动器200、栅驱动器300以及时序控制器400。虽未在图9图示,液晶显示装置1000还可以包括连接于源驱动器200以形成灰阶电压的灰阶电压生成器。

[0105] 液晶显示面板100,以源驱动器200输出的数据信号以及栅驱动器300的输出栅信号(即,扫描脉冲)为基础,能够显示影像。液晶显示面板100包括以矩阵形式排列的多个像素。其中排列于同一行的像素区分为奇数列像素和偶数列像素,排列于同一列的像素区分为奇数行像素和偶数行像素。在液晶显示面板100中,在行方向可以间隔一水平周期的时差向同一行的奇数列像素和偶数列像素施加极性相同的数据信号,在列方向可以间隔一水平周期的时差依次将极性相反的数据信号施加至同一列的像素。为此,液晶显示面板100可以

包括：多个像素，以矩阵形态排列；第一子栅线，与所述像素中的、在其下侧与之相邻的第一行像素连接；第二子栅线，与所述像素中的、在其上侧与之相邻的第二行像素连接；多个栅线，位于所述第一子栅线和所述第二子栅线之间，分别与在其上侧与之相邻的第二行像素和在其下侧与之相邻的第一行像素以之字形连接；偶数数据线，与所述像素中与之相邻的第一列像素连接；以及奇数数据线，与所述像素中与之相邻的第二列像素连接。并且，液晶显示面板100还可以包括：在奇数数据线之间共享电荷、在偶数数据线之间共享电荷的电荷共享控制电路。如上所述，所述第一行像素可以与排列在同一行的像素中的奇数列像素相应，所述第二行像素可以与排列在同一行的像素中的偶数列像素相应。或者，所述第一行像素可以与排列在同一行的像素中的偶数列像素相应；所述第二行像素可以与排列在同一行的像素中的奇数列像素相应。此外，所述第一列像素可以与排列在同一列的像素中的奇数行像素相应；所述第二列像素可以与排列在同一列的像素中的偶数行像素相应，或者，所述第一列像素可以与排列在同一列的像素中的偶数行像素相应；所述第二列像素可以与排列在同一列的像素中的奇数行像素相应。由于对此已进行过详细说明，因此省略重复说明。

[0106] 源驱动器200，以时序控制器400输出的数据控制信号(DCS)为基础，可以将与影像相应的数据信号施加至数据线DL1...DLm。此时，以分别选择由灰阶电压生成器生成的灰阶电压的方式，生成数据信号。此时，所述灰阶电压生成器可以生成相对于公共电压的极性极性相反的灰阶电压对；源驱动器200，可以通过在灰阶电压对中选择一个的方式，来确定数据信号的极性。结果，数据信号具有：以公共电压为基准的正极性、或者是以公共电压为基准的负极性。示例性的实施例中，数据控制信号(DCS)可以包括用于将数据信号的极性控制成正极性或负极性的极性控制信号。对此，液晶显示装置1000以极性控制信号为基础，以一定单位反转供给至数据线DL1...DLm的数据信号的极性。例如，在一帧内，液晶显示装置1000将第一极性的数据信号施加到偶数数据线，将与所述第一极性相反的第二极性的数据信号施加至奇数数据线。此时，每次变化帧时，液晶显示装置1000可以对施加至液晶显示面板100的数据信号的极性进行变化。栅驱动器300，基于输出自时序控制器400的栅控制信号(GCS)，可以施加栅信号(即，扫描脉冲)，其中所述栅信号在液晶显示面板100的栅线GL1、.....GLn中依次位移。时序控制器400可生成用于控制驱动时间的栅控制信号(GCS)和数据控制信号(DCS)。示例性的实施例中，外部的图形控制器(graphic controller)(未图示)输入红绿蓝影像信号(分别为R、G、B)、水平同步信号(H)、垂直同步信号(V)、主时钟CLK和数据使能信号DES等信号至时序控制器400，并且，时序控制器400，基于这种信号，可生成栅控制信号(GCS)和数据控制信号(DCS)。例如，栅控制信号(GCS)包括：控制开始输出栅信号的垂直同步起始信号、控制栅信号输出时机的栅时钟信号和控制栅信号持续时间的输出使能信号，数据控制信号(DCS)可以包括：控制开始输入数据信号的水平同步起始信号、将数据信号施加至数据线DL1...DLm的负载信号、以一定单位反转从源驱动器200输出至液晶显示面板100的数据信号极性的极性控制信号等。

[0107] 图10是驱动图9液晶显示装置的方法顺序图。

[0108] 如图10所示，液晶显示装置1000，以由多个水平周期形成的帧为单位来显示影像。为此，液晶显示装置1000的驱动方法可以包括：步骤S120，间隔一水平周期时差，将极性相同的数据信号，向行方向施加至奇数列像素和偶数列像素；步骤S140，间隔一水平周期时

差,将极性相反的数据信号,向列方向依次施加至排列于同一列的像素;步骤S160,每次变化帧时,变更供给至液晶显示面板100的数据信号的极性。

[0109] 示例性的实施例的液晶显示装置1000驱动方法中,为了防止水平串扰和垂直串扰,并且有效地减小功耗,步骤S120,间隔一水平周期时差,将极性相同的数据信号,向行方向施加至奇数列像素和偶数列像素时,步骤S140,间隔一水平周期时差,将极性相反的数据信号,向列方向依次施加至排列在同一列的像素。即,步骤S120,由于间隔一水平周期的时差,将极性相同的数据信号,向行方向施加至奇数列像素和偶数列像素,因此即使极性相同的数据信号施加至排列于同一行的相邻像素,由于在他们之间具有一水平周期的时差,所以不会产生水平串扰。例如,在第一水平周期内,第一极性的数据信号,施加至排列于同一行像素中的奇数列像素,在随后的第二水平周期内,第一极性的数据信号,同时施加至排列于同一行像素中的偶数列像素。依此,步骤S140,由于间隔一水平周期时差,将极性相反的数据信号,向列方向依次施加至排列于同一列的像素,因此,即使极性相反的数据信号施加至排列于同一列的相邻的像素,也不会产生垂直串扰。例如,在第一水平周期内,在排列于同一列的像素中,第一极性的数据信号施加至第一行的像素;在随后的第二水平周期内,第二极性的数据信号施加至第二行的像素;在随后的第三水平周期内,第一极性的数据信号施加至第三行的像素;在随后的第四水平周期内,第二极性的数据信号施加至第四行的像素。

[0110] 液晶显示装置1000的驱动方法中,如上所述,以由多个水平周期构成的帧为单位执行所述步骤S120、S140,每次变化帧的时候可变更供给至液晶显示面板100的数据信号的极性(步骤S160)。例如,在第一帧期间,向奇数数据线施加的数据信号可以具有第一极性、向偶数数据线施加的数据信号可以具有第二极性。在随后的第二帧期间,向奇数数据线施加的数据信号可以具有第二极性、向偶数数据线施加的数据信号可以具有第一极性。在随后的第三帧期间,向奇数数据线施加的数据信号可以再次具有第一极性、向偶数数据线施加的数据信号可以再次具有第二极性。此时,由于极性相同的数据信号以数据线为单位供给至液晶显示面板100,从而可有效减少功耗。与此相同,液晶显示装置1000的驱动方法,与列反转方式的驱动器极性模式相似的方式,供给驱动器极性模式,并且除间隔一水平周期时差将数据信号施加至排列在同一行的奇数列像素和偶数列像素之外,与ALS反转方式的视极性模式或者行反转方式的视极性模式相似的视极性模式显示。

[0111] 图11是包括图9的液晶显示装置的电子装置的框示图。

[0112] 如图11所示,电子装置1100包括:液晶显示装置1000、处理器1010、内存装置1020、存储装置1030、输入输出装置1040和电源1050。电子装置1100可以为用户通过液晶显示装置1000可视影像的电视、手机、智能手机等装置。进一步地,电子装置1100还可以包括:能够与显卡(video card)、声卡(sound card)、内存卡(memory card)、USB等装置通信或者能够与其他电子装置通信的多个端口(port)。

[0113] 处理器1010能够执行特定的计算或者任务(task)。示例性的实施例中,处理器1010可以为微处理器(micro processor)、中央处理单元(Central Processing Unit,简称为:CPU)。处理器1010,通过地址总线(address bus)、控制总线(control bus)和数据总线(data bus),与内存装置1020、存储装置1030和输入输出装置1040连接通信。在示例性的实施例中,处理器1010还可以连接至外围部件互联(Peripheral Component Interconnect,

简称为:PCI)总线等扩展总线。内存装置1020存储有运行电子器械1100所需的数据。例如,内存装置1020可以包括:易失性内存装置,如:动态随机存储器(Dynamic Random Access Memory,简称为:DRAM)、静态随机存储器(Static Random Access Memory,简称为:SRAM)等,以及非易失性内存装置,如:可擦除可编程只读存储器(Erasable Programmable Read-Only Memory,简称为:EPROM)、电可擦可编程只读存储器(Electrically Erasable Programmable Read-Only Memory,简称为:EEPROM)和闪存装置(flash memory device)等。存储装置1030可以包括:固态驱动器(Solid State Drive,简称为:SSD)、硬盘驱动器(Hard Disk Drive,简称为:HDD)和只读光盘(Compact Disc Read-Only Memory,简称为:CD-ROM)。输入输出装置1040可以包括:输入装置,如:键盘(keyboard)、袖珍键盘(keypad)、鼠标(mouse)等,以及输出装置,如:打印机等。在示例性的实施例中,输入输出装置1040可以包括液晶显示装置1000。电源1050供给运行电子器械1100所需的电压。

[0114] 液晶显示装置1000,通过所述总线或者其它通信链路,与处理器1010连接,并进行通信。如上所述,液晶显示装置1000可以包括:液晶显示面板100、源驱动器200、栅驱动器300和时序控制器400。此时,以源驱动器200输出的数据信号和栅驱动器300输出的栅信号为基础显示影像的液晶显示面板100中,间隔一水平周期的时差,可以将极性相同的数据信号,向行方向同时施加至奇数列像素和偶数列像素;间隔一水平周期时差,也可以将极性相反的数据信号,依次施加至同一列的像素。为此,液晶显示面板100可以包括:像素、第一子栅线、第二子栅线、栅线、奇数数据线、偶数数据线和电荷共享控制电路。只是,由于已对此进行过详细说明,在此省略重复说明。在示例性的实施例中,液晶显示装置1000可以应用于扭曲向列型(Twisted Nematic,简称为:TN)模式和垂直取向型(Vertical Alignment,简称为:VA)模式、共平面切换性(IPS:In Plane Switching,)模式以及边缘场切换型(Fringe Field Switching,简称为:FFS)模式等。

[0115] 工业应用性

[0116] 本发明可以应用于液晶显示装置及包括所述液晶显示装置的电子装置。例如,本发明可以应用于电脑显示器、数字电视、便携式计算机、数码相机、摄像机(video camcorder)、手机、智能手机、个人数字助理(PDA:personal digital assistants)、便携式媒体播放器(PMP:portable multimedia player)、MP3播放器、车辆导航装置、视频电话等。

[0117] 以上参照本发明示例性的实施例进行了说明,但本发明并不限于上述的实施方式。在不偏离本发明的思想和范围的情况下,本领域普通技术人员可进行各种变化和修改,前述的变化及修改对本领域的技术人员是显而易见的。

图1

110

图2

图3

图4

图5a

图5b

图5c

图5d

图5e

|    | 140_1 | 150_1 | 140_2 | 150_2 | 140_3 | 150_3 | 140_4 | 150_4 |

|----|-------|-------|-------|-------|-------|-------|-------|-------|

|    | DL1   | DL2   | DL3   | DL4   | DL5   | DL6   | DL7   | DL8   |

| 2F | 1H    | -     | +     | -     | +     | -     | +     | -     |

|    | 2H    | -     | +     | -     | +     | -     | +     | -     |

|    | 3H    | -     | +     | -     | +     | -     | +     | -     |

|    | 4H    | -     | +     | -     | +     | -     | +     | -     |

|    | 5H    | -     | +     | -     | +     | -     | +     | -     |

|    | 6H    | -     | +     | -     | +     | -     | +     | -     |

|    | 7H    | -     | +     | -     | +     | -     | +     | -     |

|    | 8H    | -     | +     | -     | +     | -     | +     | -     |

|    | :     | :     | :     | :     | :     | :     | :     | :     |

图6

图7a

图7b

图7c

图7d

图7e

500

图8

1000

图9

图10

1100

图11

|                |                                                                                                                     |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示面板、液晶显示装置及液晶显示装置的驱动方法                                                                                           |         |            |

| 公开(公告)号        | <a href="#">CN102456334B</a>                                                                                        | 公开(公告)日 | 2016-08-03 |

| 申请号            | CN201110329203.1                                                                                                    | 申请日     | 2011-10-24 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                            |         |            |

| 申请(专利权)人(译)    | 三星移动显示器株式会社                                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 三星显示有限公司                                                                                                            |         |            |

| [标]发明人         | 李丞珪<br>李东勳<br>金喆镐<br>朴晋佑                                                                                            |         |            |

| 发明人            | 李丞珪<br>李东勳<br>金喆镐<br>朴晋佑                                                                                            |         |            |

| IPC分类号         | G09G3/36 G02F1/133                                                                                                  |         |            |

| CPC分类号         | G09G3/3614 G09G3/3648 G09G2300/0426 G09G2310/0248 G09G2320/0209 G09G2320/0247<br>G09G2330/023 G09G3/3659 G09G3/3688 |         |            |

| 代理人(译)         | 王艳春                                                                                                                 |         |            |

| 优先权            | 1020100105654 2010-10-28 KR                                                                                         |         |            |

| 其他公开文献         | <a href="#">CN102456334A</a>                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                      |         |            |

**摘要(译)**

本发明涉及液晶显示面板，包括：像素，以矩阵形式排列；第一子栅线，与所述像素中下侧相邻的第一?行像素连接；第二子栅线，与上侧相邻的第二?行像素连接；栅线，位于所述第一子栅线和所述第二子栅线之间，分别与相邻上侧的第二?行像素和下侧的第一?行像素以之字形连接；偶数数据线，与相邻的第一?列像素连接；奇数数据线，与相邻的第二?列像素连接。所述液晶显示面板可防止水平及垂直串扰，同时可有效减少功耗。