## (12) 发明专利

(10) 授权公告号 CN 102135691 B

(45) 授权公告日 2012.05.23

(21) 申请号 201110020250.8

CN 101515097 A, 2009.08.26,

(22) 申请日 2011.01.18

CN 1448770 A, 2003.10.15,

## (66) 本国优先权数据

CN 1226663 C, 2005.11.09,

201010286926.3 2010.09.17 CN

CN 1448770 A, 2003.10.15,

(73) 专利权人 京东方科技股份有限公司

CN 1614742 A, 2005.05.11,

地址 100015 北京市朝阳区酒仙桥路 10 号

CN 100476529 C, 2009.04.08,

专利权人 成都京东方光电科技有限公司

CN 1885140 A, 2006.12.27,

(72) 发明人 黄炜赞 高永益 玄明花

CN 101308299 A, 2008.11.19,

(74) 专利代理机构 北京同达信恒知识产权代理

CN 101308294 A, 2008.11.19,

有限公司 11291

审查员 李晴晴

代理人 黄志华

## (51) Int. Cl.

G02F 1/1362(2006.01)

H01L 27/12(2006.01)

H01L 21/77(2006.01)

## (56) 对比文件

CN 101515097 A, 2009.08.26,

权利要求书 2 页 说明书 11 页 附图 21 页

## (54) 发明名称

阵列基板及其制造方法和液晶显示器

## (57) 摘要

本发明公开了一种阵列基板及其制造方法和液晶显示器。阵列基板，包括衬底基板，所述衬底基板的像素区域中形成有横纵交叉围设形成多个像素单元的数据线和栅线，每个像素单元中包括开关元件、像素电极和公共电极，所述公共电极为具有狭缝且布设在像素区域中的整块图案，其中：所述像素区域中还形成有公共电极线，所述公共电极线与所述公共电极连通。本发明在液晶显示器的阵列基板的像素区域形成公共电极线，并且公共电极线与公共电极连通，公共电极线与公共电极可以形成并联电路，减小了公共电极的电阻，从而减小公共电极的 RC 信号延迟，提高公共电压信号的负荷能力，因此，可以减弱串扰现象，提高液晶显示器的画面质量。

B

102135691

CN

1. 一种阵列基板，包括衬底基板，所述衬底基板的像素区域中形成有横纵交叉围设形成多个像素单元的数据线和栅线，每个像素单元中包括开关元件、像素电极和公共电极，所述公共电极为具有狭缝且布设在像素区域中的整块图案，其特征在于：

所述像素区域中还形成有公共电极线，所述公共电极线与所述公共电极连通；

其中，多行或多列像素单元共用一条公共电极线。

2. 根据权利要求 1 所述的阵列基板，其特征在于：

所述公共电极线与所述数据线同层设置且相互平行，所述公共电极线通过接触过孔与所述公共电极连通。

3. 根据权利要求 1 所述的阵列基板，其特征在于：

所述公共电极线与所述栅线同层设置且相互平行，所述公共电极线通过接触过孔与所述公共电极连通。

4. 根据权利要求 1 所述的阵列基板，其特征在于：

所述公共电极线包括第一公共电极线和第二公共电极线，所述第一公共电极线与所述数据线同层设置且相互平行，所述第二公共电极线与所述栅线同层设置且相互平行，所述第一公共电极线和第二公共电极线分别通过接触过孔与所述公共电极连通。

5. 根据权利要求 1 ~ 4 任一所述的阵列基板，其特征在于：所述公共电极线的材料为金属或金属氧化物。

6. 根据权利要求 1 ~ 4 任一所述的阵列基板，其特征在于：

所述像素电极的行数或列数为所述公共电极线数量的整数倍，所述公共电极线均匀且间隔地分布于所述像素区域中。

7. 一种阵列基板的制造方法，包括在衬底基板的像素区域中形成栅线、开关元件、数据线、像素电极和公共电极的流程，所述公共电极为具有狭缝且布设在像素区域中的整块图案，其特征在于，还包括：

在所述像素区域中，与所述栅线同层形成公共电极线的图案，所述公共电极线与所述栅线相互平行；和 / 或，在所述像素区域中，与所述数据线同层形成公共电极线的图案，且所述公共电极线与所述数据线相互平行；

连通所述公共电极和所述公共电极线；

其中，多行或多列像素单元共用一条公共电极线。

8. 根据权利要求 7 所述的阵列基板的制造方法，其特征在于，在衬底基板的像素区域中形成栅线、开关元件、数据线、像素电极、公共电极和公共电极线的流程包括：

在衬底基板上通过构图工艺形成包括栅线和栅电极的图案；

在形成上述图案的衬底基板上形成栅极绝缘层；

在形成上述图案的衬底基板上通过构图工艺形成包括数据线、公共电极线、源电极、漏电极和有源层的图案；

在形成上述图案的衬底基板上通过构图工艺形成包括像素电极的图案，所述像素电极与所述漏电极搭接连通；

在形成上述图案的衬底基板上形成钝化层，通过构图工艺形成包括接触过孔的图案；

在形成上述图案的衬底基板上通过构图工艺形成包括所述公共电极的图案，所述公共电极线与所述公共电极通过所述接触过孔连通。

9. 根据权利要求 7 所述的阵列基板的制造方法,其特征在于,在衬底基板的像素区域中形成栅线、开关元件、数据线、像素电极、公共电极和公共电极线的流程包括:

在衬底基板上通过构图工艺形成包括栅线、栅电极和公共电极线的图案;

在形成上述图案的衬底基板上形成栅极绝缘层;

在形成上述图案的衬底基板上通过构图工艺形成包括数据线、源电极、漏电极和有源层的图案;

在形成上述图案的衬底基板上通过构图工艺形成包括像素电极的图案,所述像素电极与所述漏电极搭接连通;

在形成上述图案的衬底基板上形成钝化层,通过构图工艺形成包括接触过孔的图案;

在形成上述图案的衬底基板上通过构图工艺形成包括所述公共电极的图案,所述公共电极线与所述公共电极通过所述接触过孔连通。

10. 根据权利要求 7 所述的阵列基板的制造方法,其特征在于,所述公共电极线包括第一公共电极线和第二公共电极线;在衬底基板的像素区域中形成栅线、开关元件、数据线、像素电极、公共电极和公共电极线的流程包括:

在衬底基板上通过构图工艺形成包括栅线、栅电极和第二公共电极线的图案;

在形成上述图案的衬底基板上形成栅极绝缘层;

在形成上述图案的衬底基板上通过构图工艺形成包括数据线、第一公共电极线、源电极、漏电极和有源层的图案;

在形成上述图案的衬底基板上通过构图工艺形成包括像素电极的图案,所述像素电极与所述漏电极搭接连通;

在形成上述图案的衬底基板上形成钝化层,通过构图工艺形成包括接触过孔的图案;

在形成上述图案的衬底基板上通过构图工艺形成包括所述公共电极的图案,所述第二公共电极线与所述第一公共电极线分别通过接触过孔与所述公共电极连通。

11. 根据权利要求 8 或 10 所述的阵列基板的制造方法,其特征在于,所述在形成上述图案的衬底基板上通过构图工艺形成包括数据线、源电极、漏电极和有源层的图案,包括:

在形成上述图案的衬底基板上通过一次构图工艺形成包括数据线、源电极、漏电极和有源层的图案;或

在形成上述图案的衬底基板上通过两次构图工艺形成包括数据线、源电极、漏电极和有源层的图案。

12. 一种液晶显示器,包括液晶面板,其特征在于:所述液晶面板包括对盒设置的彩膜基板和权利要求 1-6 任一所述的阵列基板,所述彩膜基板和阵列基板中夹设有液晶层。

## 阵列基板及其制造方法和液晶显示器

### 技术领域

[0001] 本发明涉及液晶显示技术，尤其涉及一种阵列基板及其制造方法和液晶显示器。

### 背景技术

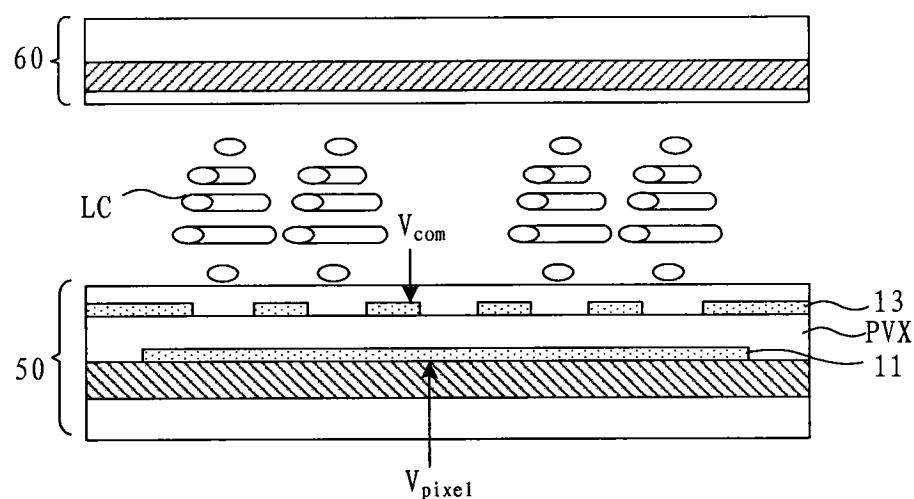

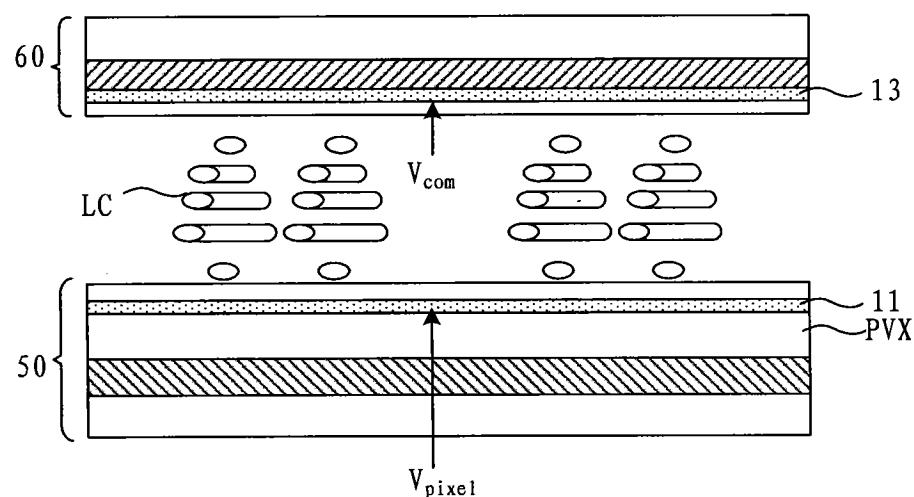

[0002] 液晶显示器是目前常用的平板显示器，其中薄膜晶体管液晶显示器 (Thin Film Transistor Liquid Crystal Display, 简称 TFT-LCD) 是液晶显示器中的主流产品。TFT-LCD 由于其低成本、高良率以及良好的显示效果，使得其在中小尺寸领域，占据着绝大部分的市场份额。尽管 TFT-LCD 的工艺已经日渐成熟，但画面品质仍需要不断提高，以满足消费者的挑剔需求。比如现有的宽视角技术包括边缘场切换开关技术和 (Fringe Field Switching, 简称 FFS) 和高级超维场开关技术 (Advanced-Super Dimensional Switching；简称 :AD-SDS)。AD-SDS 通过同一平面内像素电极边缘所产生的平行电场以及像素电极层与公共电极层间产生的纵向电场形成多维空间复合电场，使液晶盒内像素电极间、电极正上方以及液晶盒上方所有取向液晶分子都能够产生旋转转换，从而提高了平面取向系液晶工作效率并增大了透光效率，可以提高 TFT-LCD 画面品质，具有宽视角、高开口率、低响应时间、无挤压水波纹 (push Mura) 波纹等优点。但由于 FFS 或 AD-SDS 型阵列基板制备过程、电场形成和液晶偏转模式等原因，造成公共电压 ( $V_{com}$ ) 的信号延迟比较严重，产生串扰 (Crosstalk) 的现象明显。串扰是画面质量的重要参数，可以表征一个区域灰阶画面，对其相邻像素区域的画面影响程度。行业标准一般要求串扰  $\leq 2\%$ 。

[0003] 公共电极与像素电极之间形成的电容是公共电极产生信号延迟的重要因素，该电容的大小可以参见计算公式： $C = \epsilon_r \epsilon_0 * S/d$ 。其中 C 为电容； $\epsilon_r$  为 相对介电常数，与材料特性有关； $\epsilon_0$  为绝对介电常数；S 为电极的面积；d 为电极之间的距离。图 1 为 FFS 或 AD-SDS 模式下公共电极与像素电极之间形成的电容的示意图，图 2 为 TN 模式下公共电极与像素电极之间形成的电容的示意图，如图 1 和图 2 所示，公共电极 13 通公共电压 ( $V_{com}$ ) 信号，像素电极 11 通公共电压 ( $V_{pixel}$ ) 信号，并且公共电极与像素电极之间形成的电容。其中，如图 1 所示，公共电极 13 与像素电极 11 处于阵列基板 50 上，公共电极 13 与像素电极 11 之间的电容介质是钝化层 (PVX)，其  $\epsilon_r$  约为 5，d 约为 0.5um。如图 2 所示，在 TN 模式中，公共电极 13 处于彩膜基板上，像素电极 11 处于阵列基板 60 上，公共电极 13 与像素电极 11 之间的电容介质是液晶 (LC)，其  $\epsilon_r$  约在 4 ~ 12 之间，d 约为 5um。参见上述公式可估算得到， $C_{com}$  约为 TN 模式下的  $C_{com}$  10 倍，公共电极与像素电极形成的电容要比 TN 模式下高出近一个数量级，因此，相比于 TN 模式，FFS 或 AD-SDS 模式的公共电压 ( $V_{com}$ ) 负荷 (Loading) 能力很低，产生的串扰现象明显。

[0004] 高开口率边缘场切换开关技术 (High aperture ratio Fringe FieldSwitching，简称 HFFS) 和高开口率高级超维场开关技术 (High apertureratioAD-SDS；简称 :HAD-SDS)，主要应用于中小尺寸的 TFT-LCD。HFFS 或 HAD-SDS 型阵列基板的典型结构是包括衬底基板，衬底基板上形成有横纵交叉围设形成多个像素单元的数据线和栅线，每个像素单元中包括开关元件、像素电极和具有狭缝的公共电极，各像素单元构成像素区域，像素

区域外围是接口区域,矩阵状排列的像素电极与整块的公共电极相对设置,且公共电极具有狭缝。

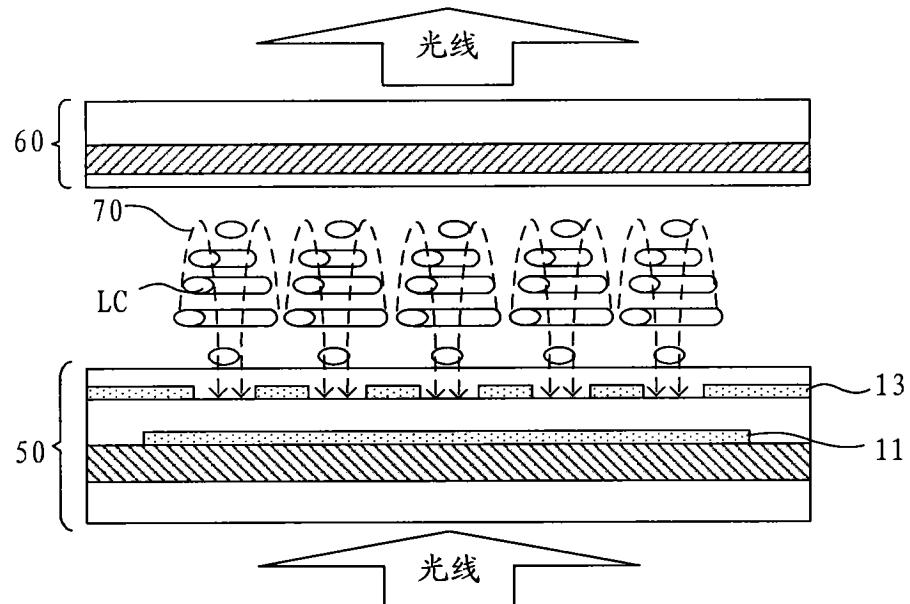

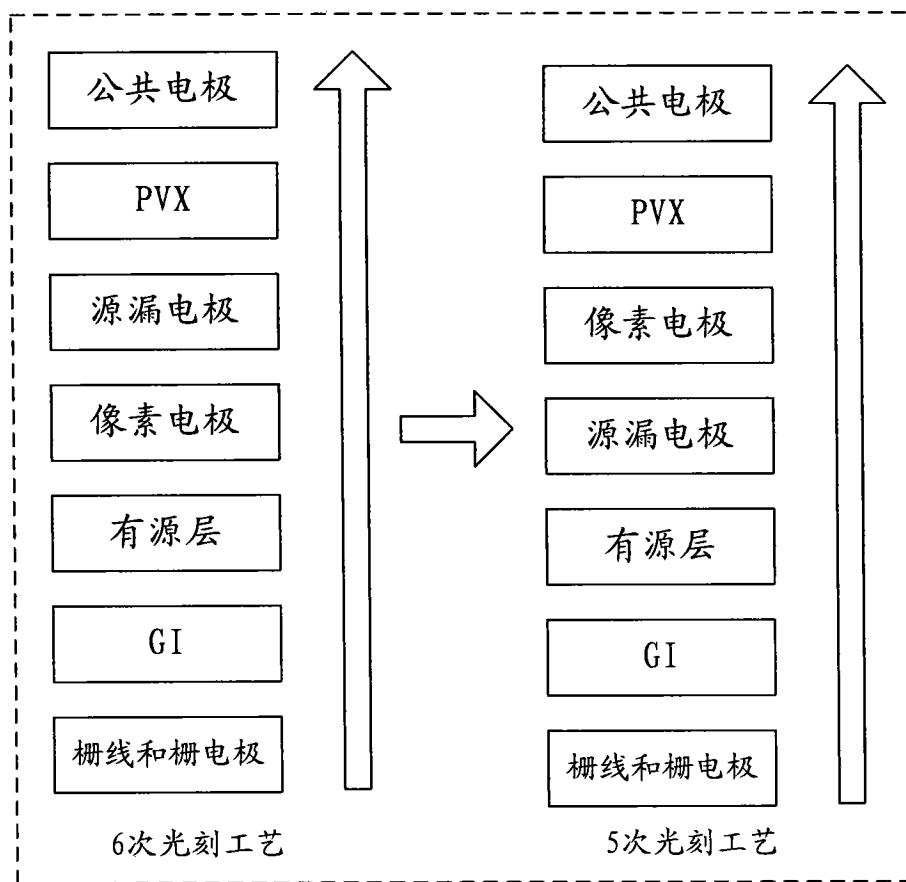

[0005] 图 3 为现有 HFFS 或 HAD-SDS 电场形成及液晶旋转的示意图。如图 3 所示,公共电极和像素电极均位于阵列基板上,且可以均由纳米铟锡氧化物 (Indium Tin Oxides ;简称 : ITO) 形成。具有狭缝的公共电极 13 与像素电极 11 形成水平电场 70,可以使阵列基板 50 与彩膜基板 60 之间水平排布的液晶 (LC) 分子旋转,起到一个光阀的作用。图 4 为 HFFS 或 HAD-SDS 层次 结构的示意图,如图 4 所示,采用 6 次光刻工艺制成的 HFFS 或 HAD-SDS 沉积刻蚀的先后顺序可以为 :栅线和栅电极 (Gate)、栅绝缘层 (GI)、有源层 (Active)、像素电极 (第一层 ITO)、源漏电极 (SD)、钝化层 (PVX)、公共电极 (第二层 ITO) ;采用 5 次光刻工艺制成 HFFS 或 HAD-SDS 沉积刻蚀的先后顺序可以为 :栅线和栅电极、栅绝缘层、有源层、源漏电极、像素电极、钝化层、公共电极。

[0006] HFFS 或 HAD-SDS 的公共电极具有狭缝,比平铺的整块公共电极电阻更大,公共电极的 RC 信号延迟更大,使得公共电压信号的负荷 (Loading) 能力下降,进而串扰现象更加明显,影响画面品质。

## 发明内容

[0007] 本发明提供一种阵列基板及其制造方法和液晶显示器,以减弱液晶显示器的串扰现象,提高液晶显示器的画面质量。

[0008] 本发明提供一种阵列基板,包括衬底基板,所述衬底基板的像素区域中形成有横纵交叉围设形成多个像素单元的数据线和栅线,每个像素单元中包括开关元件、像素电极和公共电极,所述公共电极为具有狭缝且布设在像素区域中的整块图案,其特征在于 :

[0009] 所述像素区域中还形成有公共电极线,所述公共电极线与所述公共电极连通;

[0010] 其中,多行或多列像素单元共用一条公共电极线。

[0011] 本发明又提供一种阵列基板的制造方法,包括在衬底基板的像素区域中形成栅线、开关元件、数据线、像素电极和公共电极的流程,所述公共电极为具有狭缝且布设在像素区域中的整块图案,其中,还包括 :

[0012] 在所述像素区域中,与所述栅线同层形成公共电极线的图案,所述公共电极线与所述栅线相互平行;和 / 或,在所述像素区域中,与所述数据线同层形成公共电极线的图案,且所述公共电极线与所述数据线相互平行;

[0013] 连通所述公共电极和所述公共电极线;

[0014] 其中,多行或多列像素单元共用一条公共电极线。

[0015] 本发明还提供一种液晶显示器,包括液晶面板,其特征在于 :所述液晶面板包括对盒设置的彩膜基板和本发明提供的阵列基板,所述彩膜基板和阵 列基板中夹设有液晶层。

[0016] 本发明在液晶显示器的阵列基板的像素区域形成公共电极线,并且公共电极线与公共电极连通,公共电极线与公共电极可以形成并联电路,减小了公共电极的电阻,从而减小公共电极的 RC 信号延迟,提高公共电压信号的负荷能力,因此,可以减弱串扰现象,提高液晶显示器的画面质量。

## 附图说明

- [0017] 图 1 为 FFS 或 AD-SDS 模式下公共电极与像素电极之间形成的电容的示意图；

[0018] 图 2 为 TN 模式下公共电极与像素电极形成之间形成的电容的示意图；

[0019] 图 3 为现有 HFFS 或 HAD-SDS 电场形成及液晶旋转的示意图；

[0020] 图 4 为 HFFS 或 HAD-SDS 层次结构的示意图；

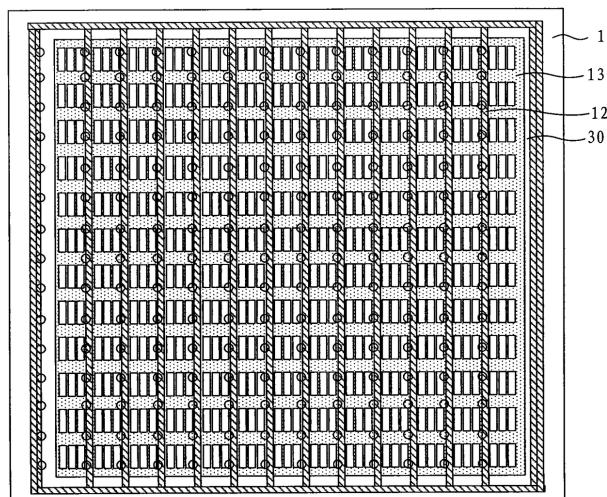

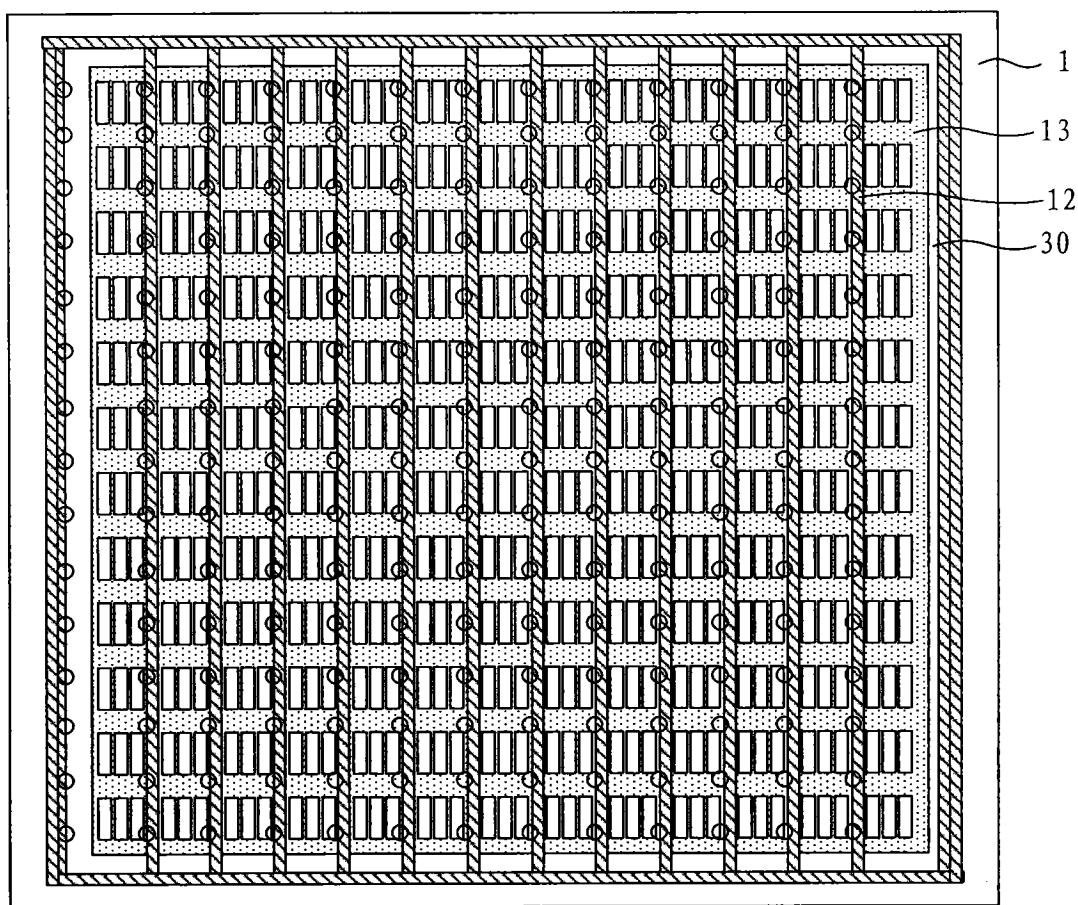

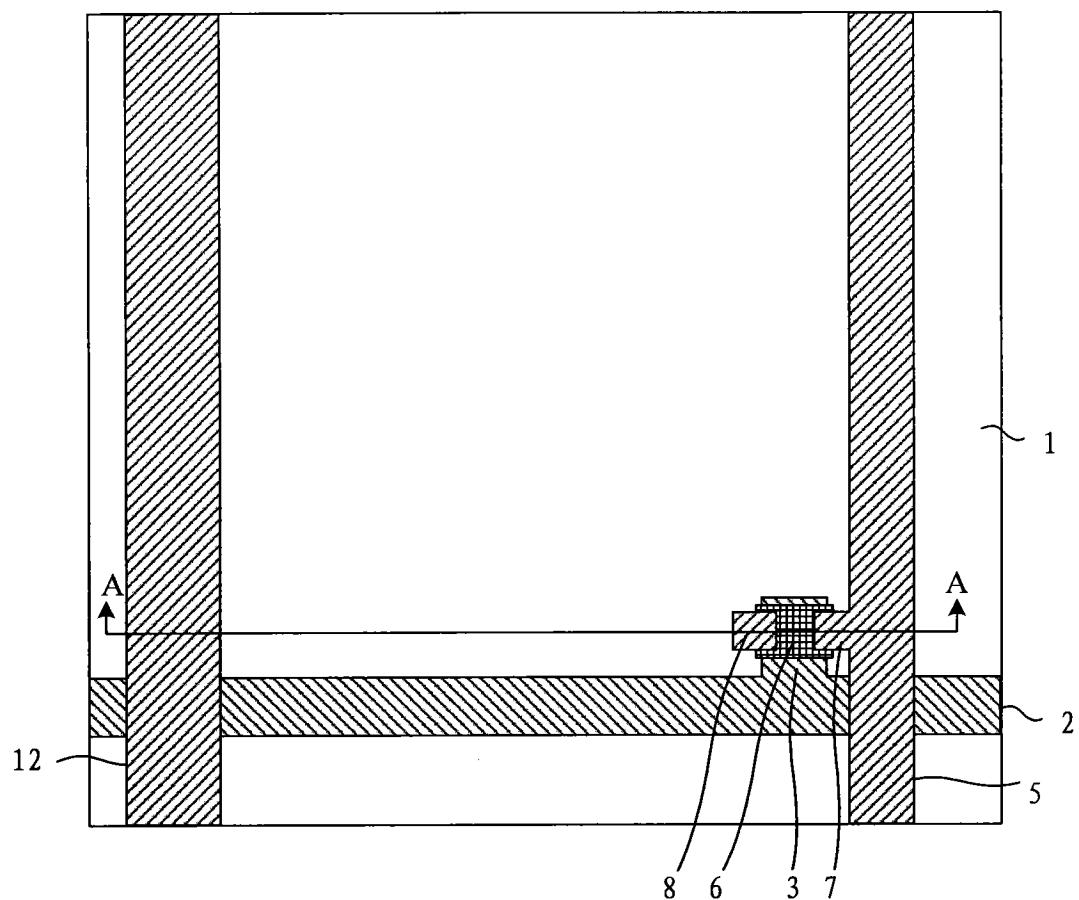

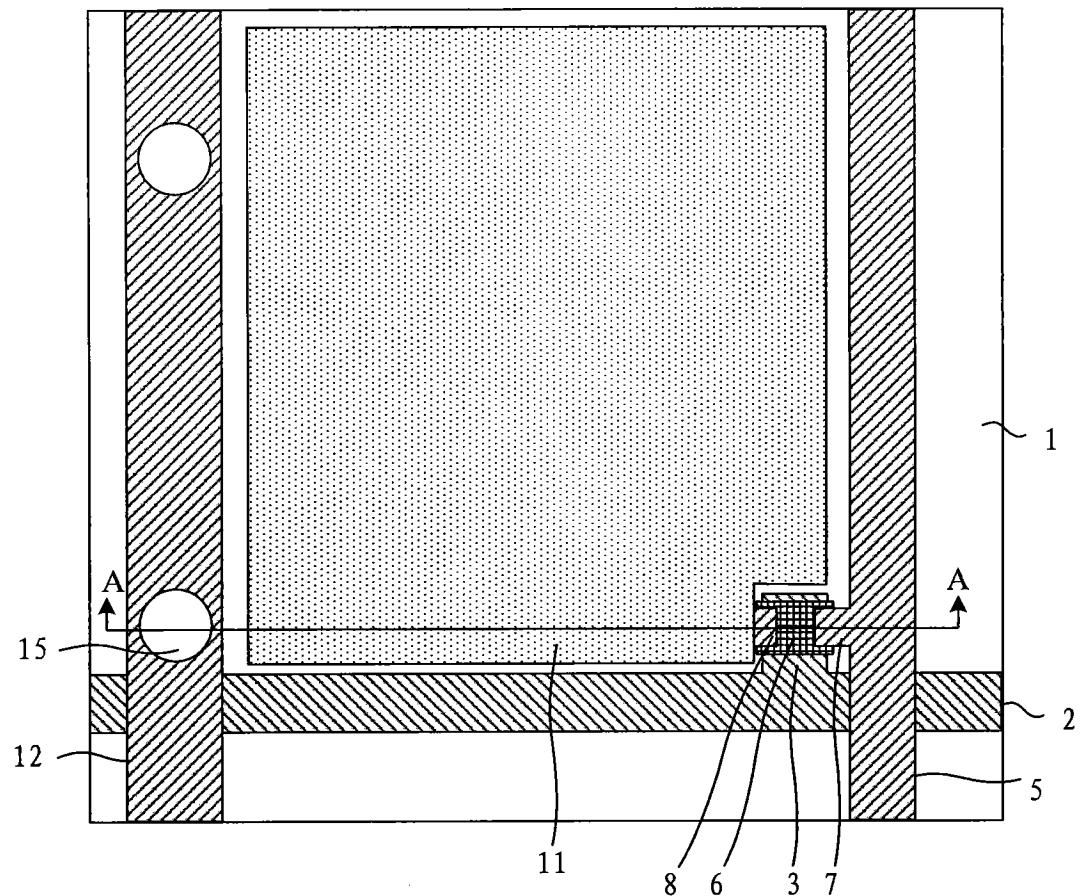

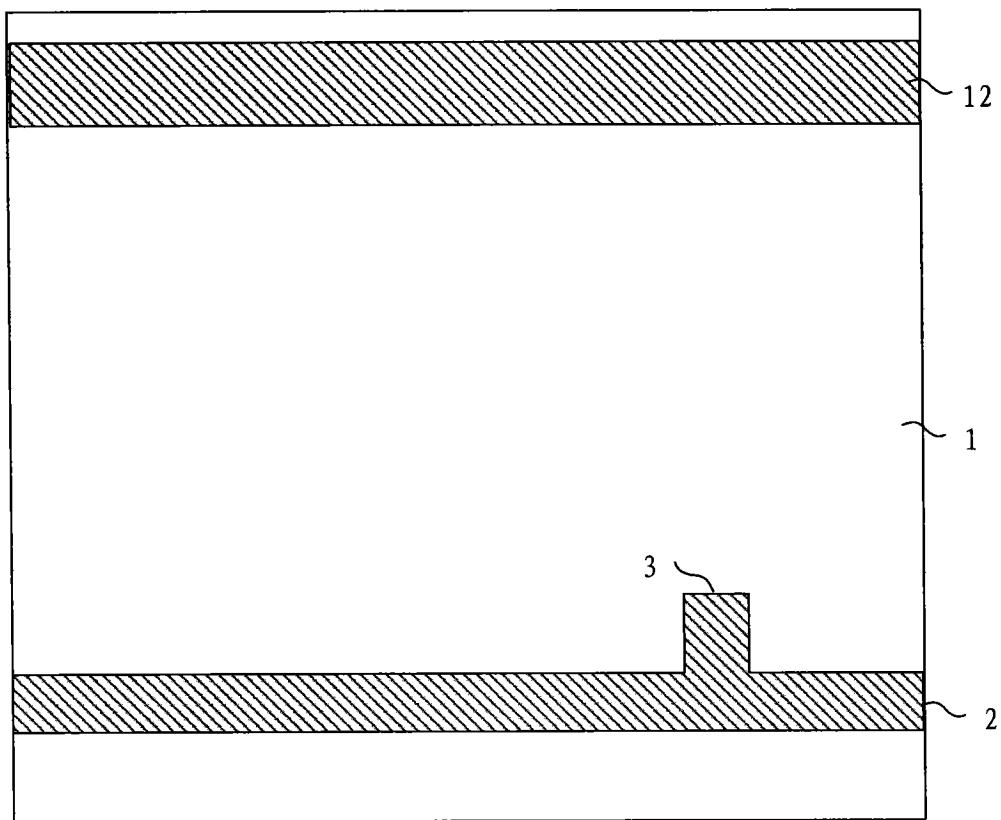

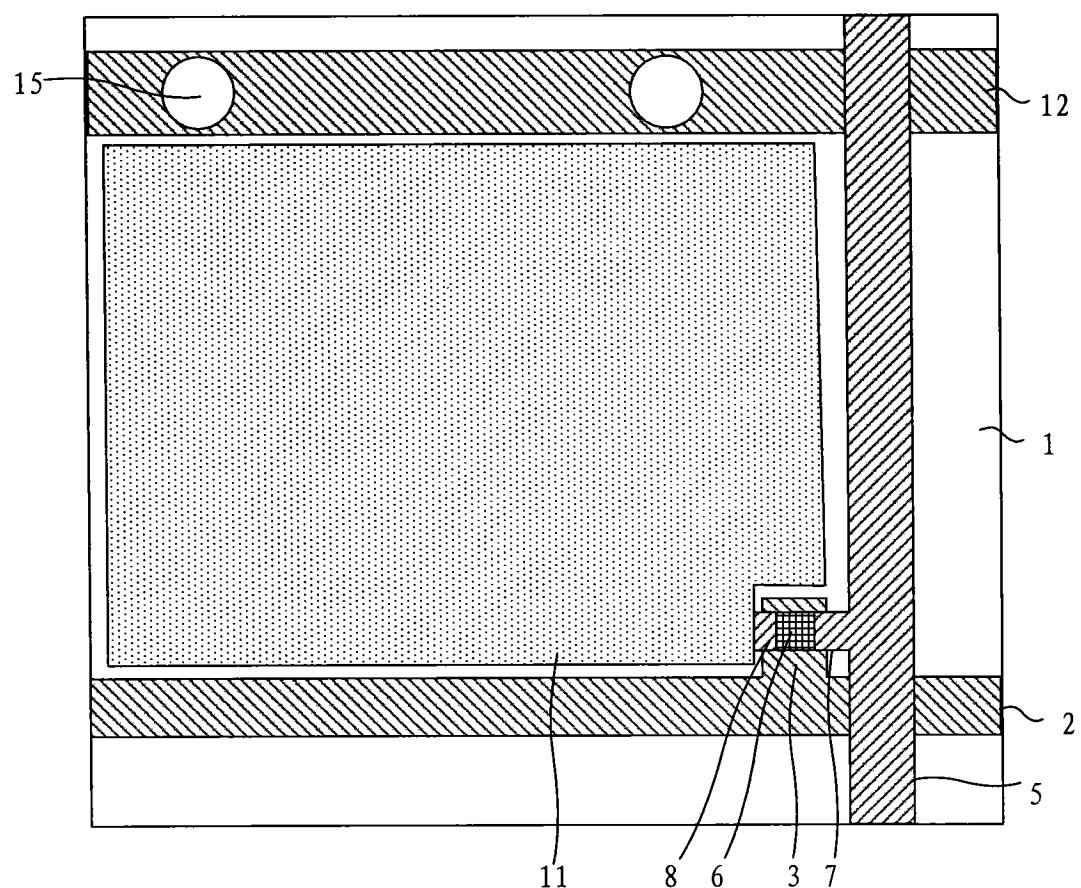

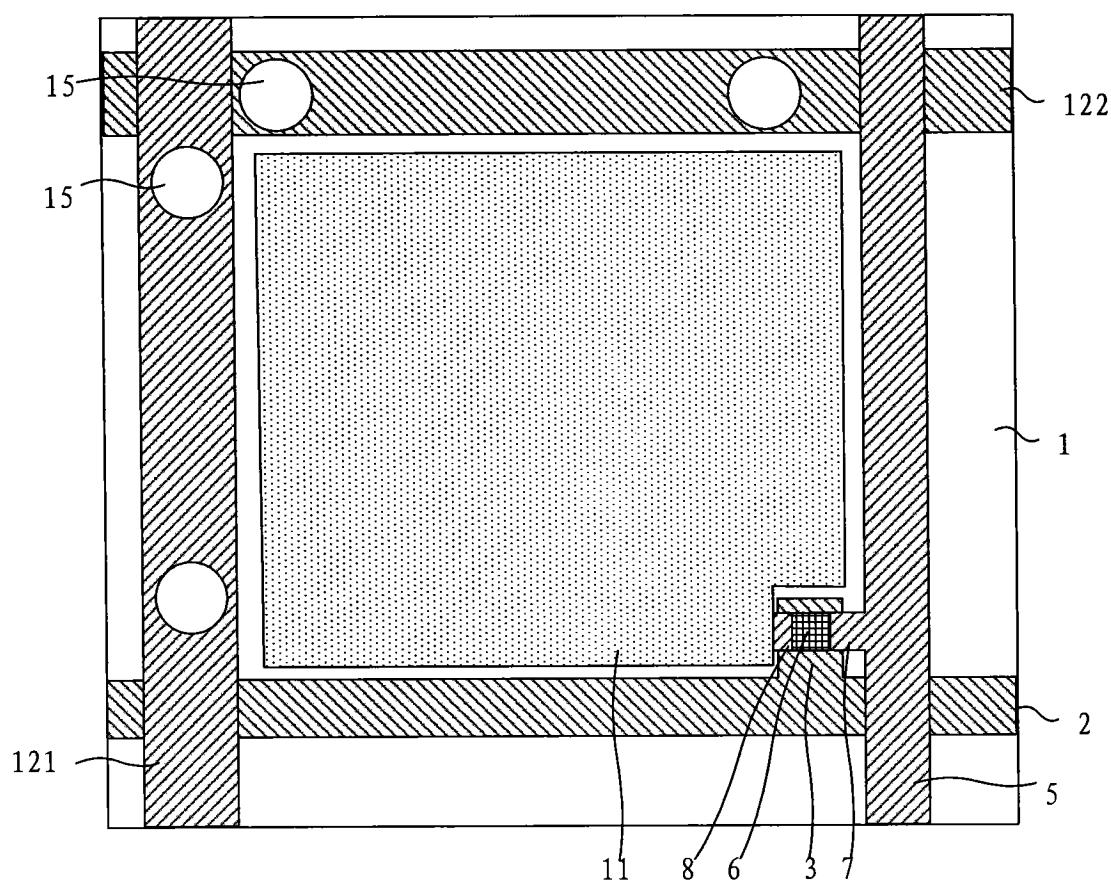

[0021] 图 5 为本发明实施例一提供的阵列基板的结构示意图；

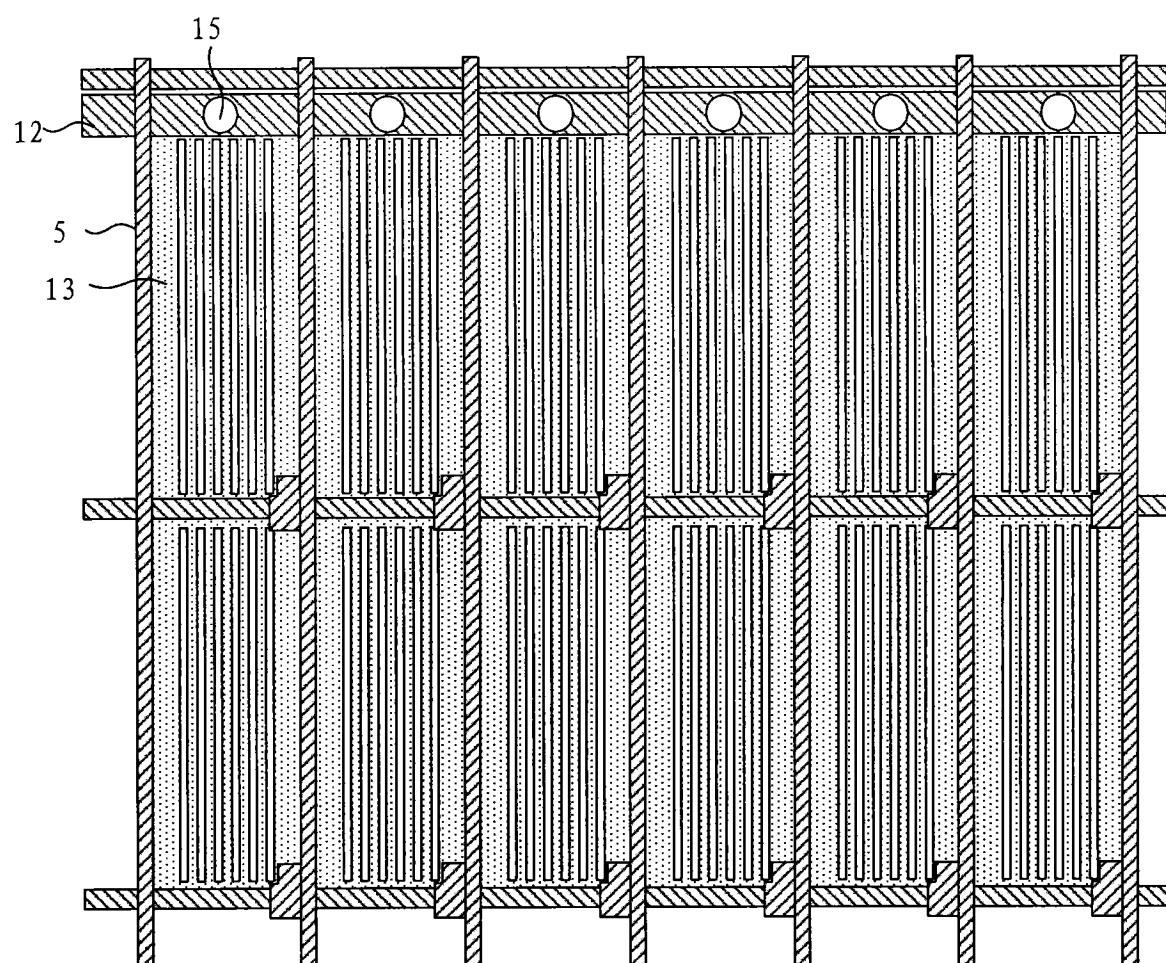

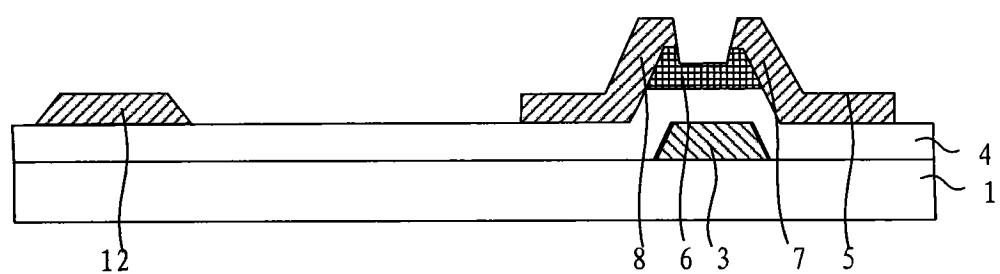

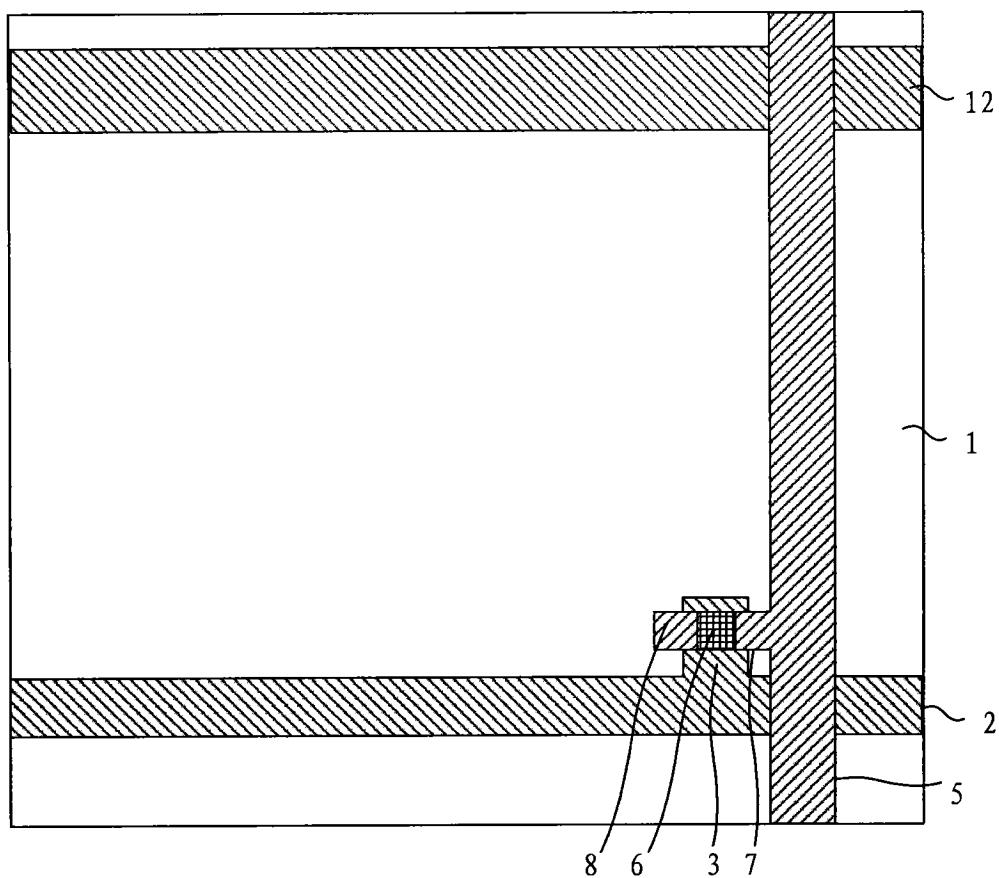

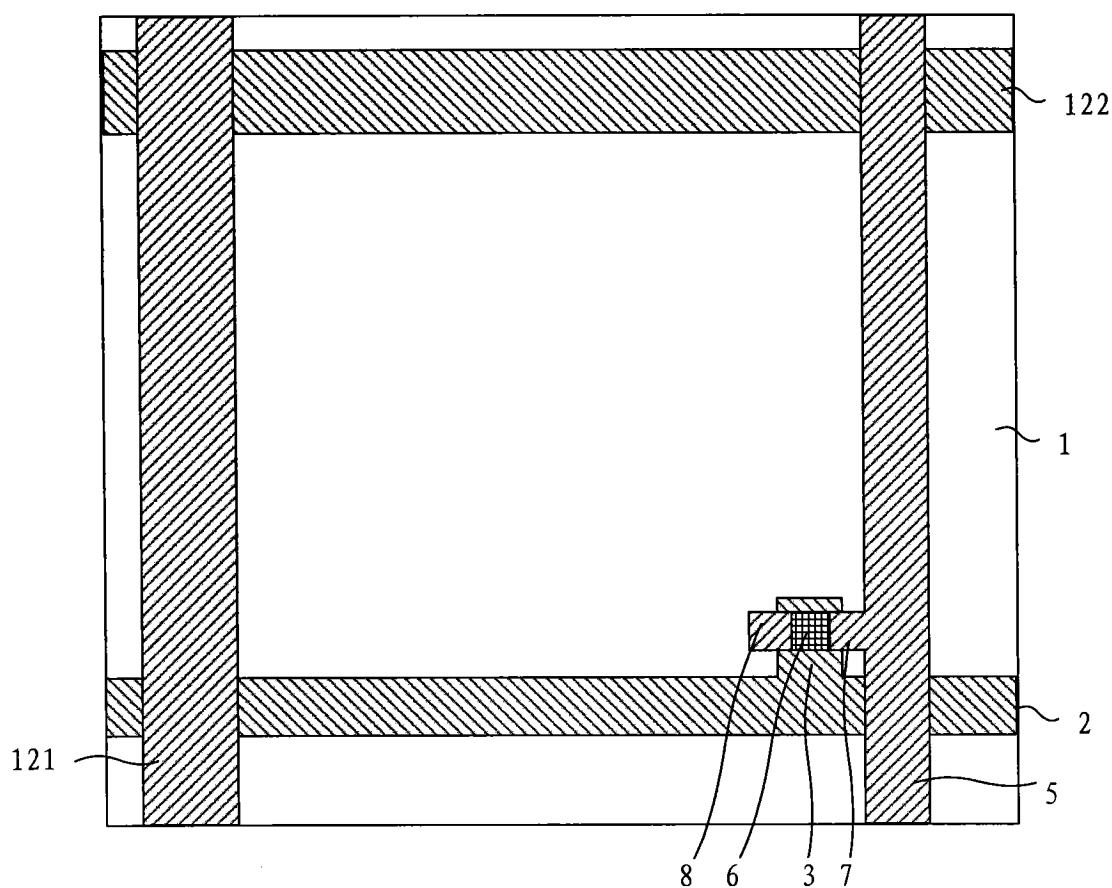

[0022] 图 6A 为本发明实施例二提供的阵列基板的方式一的结构示意图；

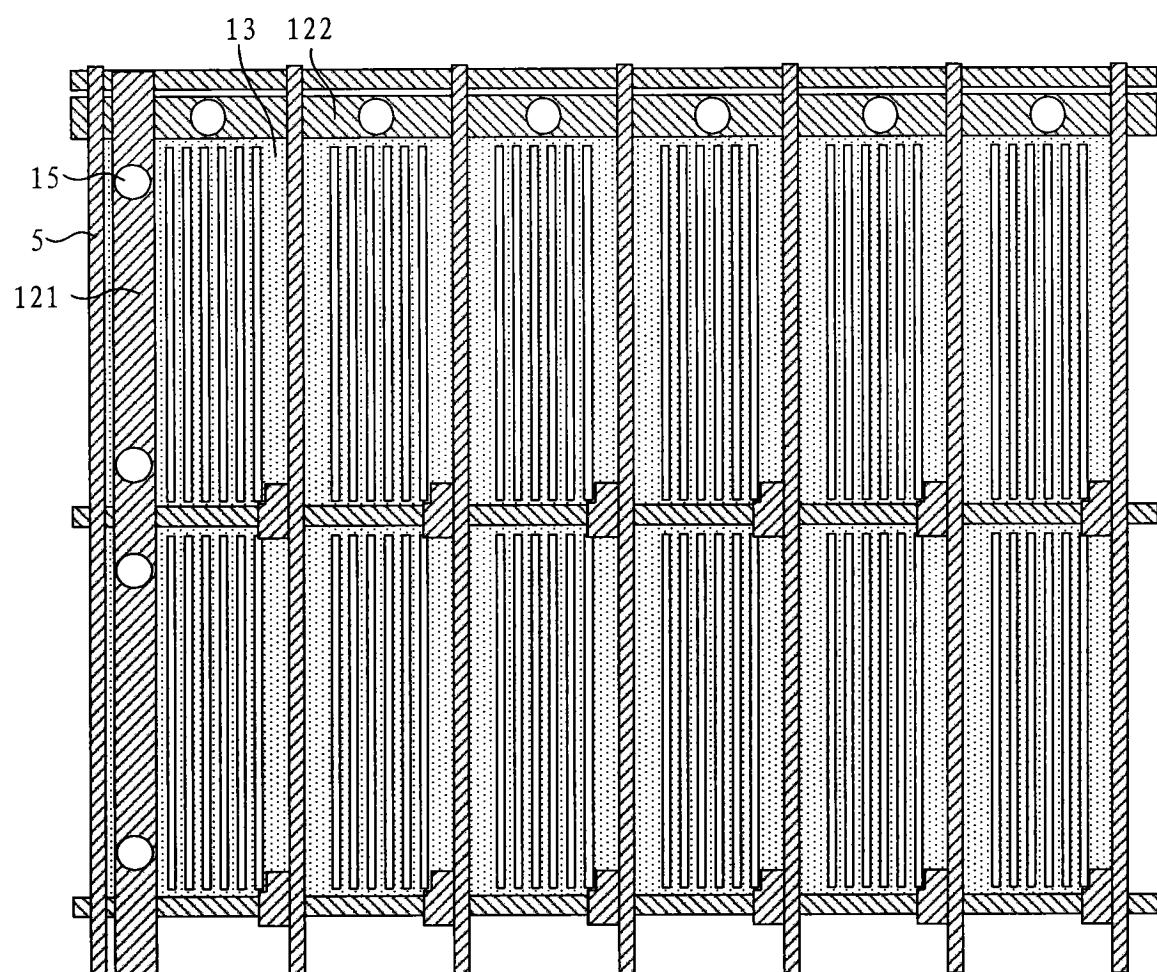

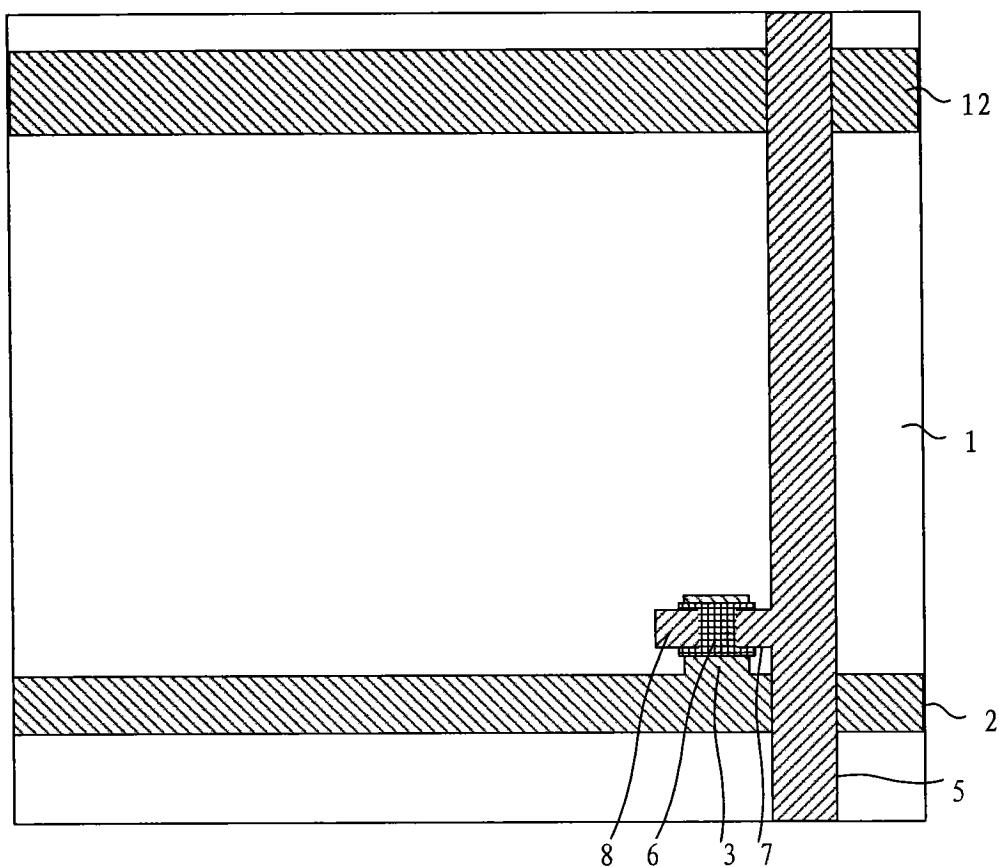

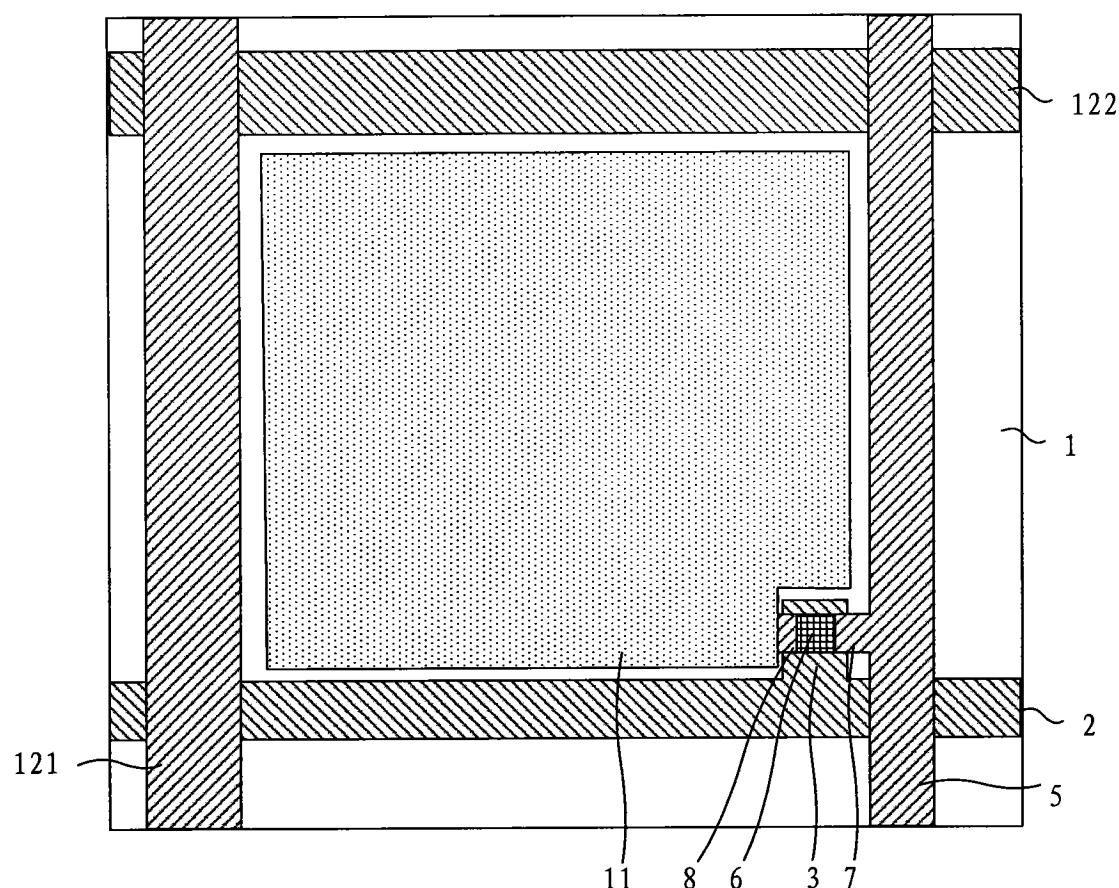

[0023] 图 6B 为本发明实施例二提供的阵列基板的方式二的结构示意图；

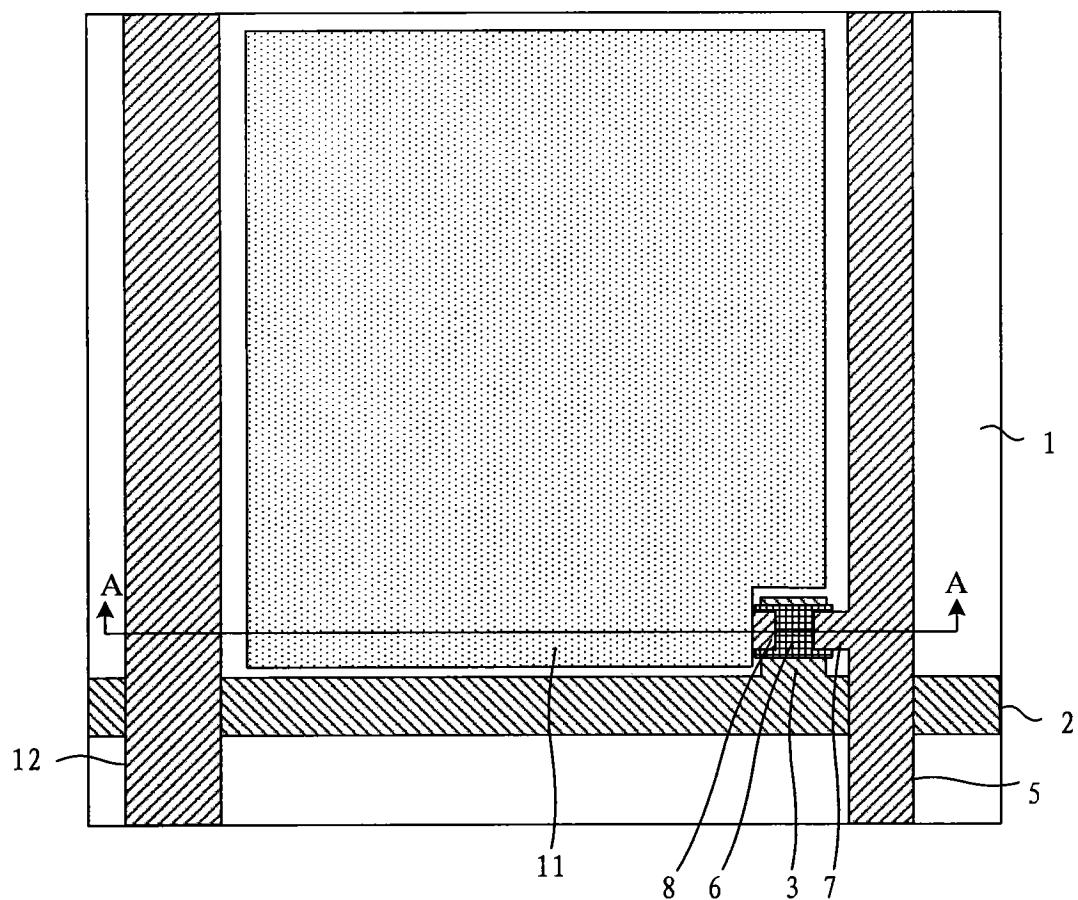

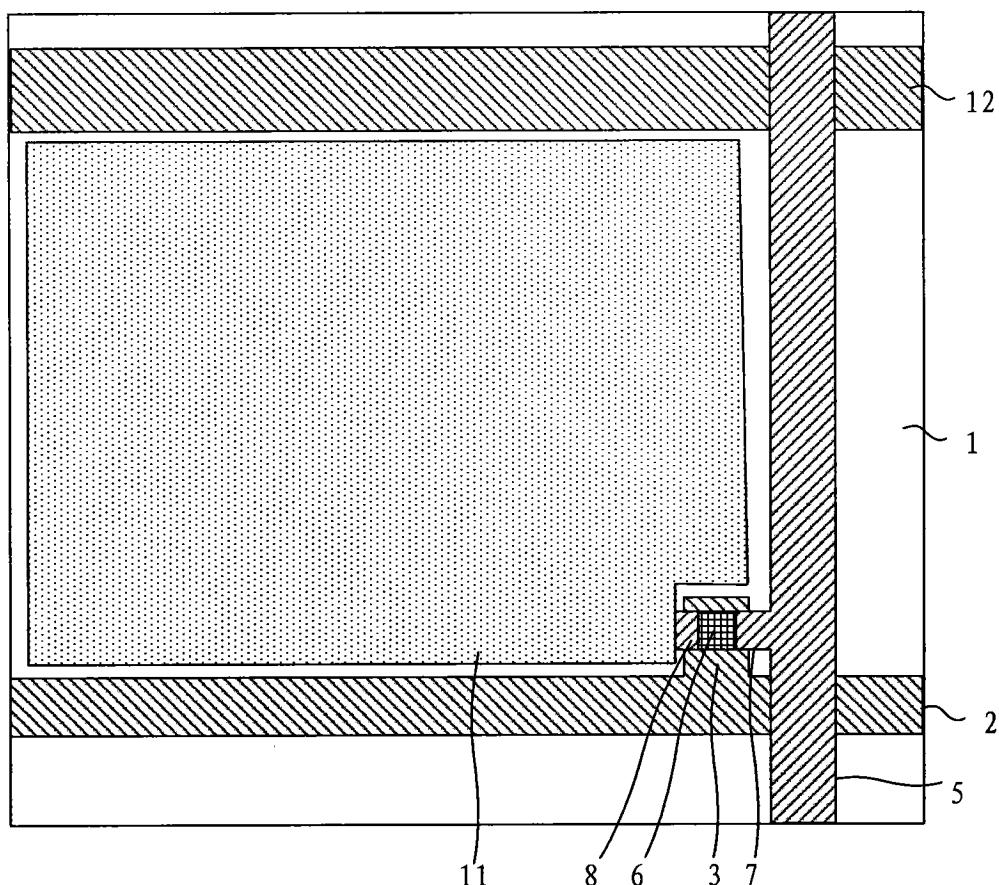

[0024] 图 6C 为本发明实施例二提供的阵列基板的方式三的结构示意图；

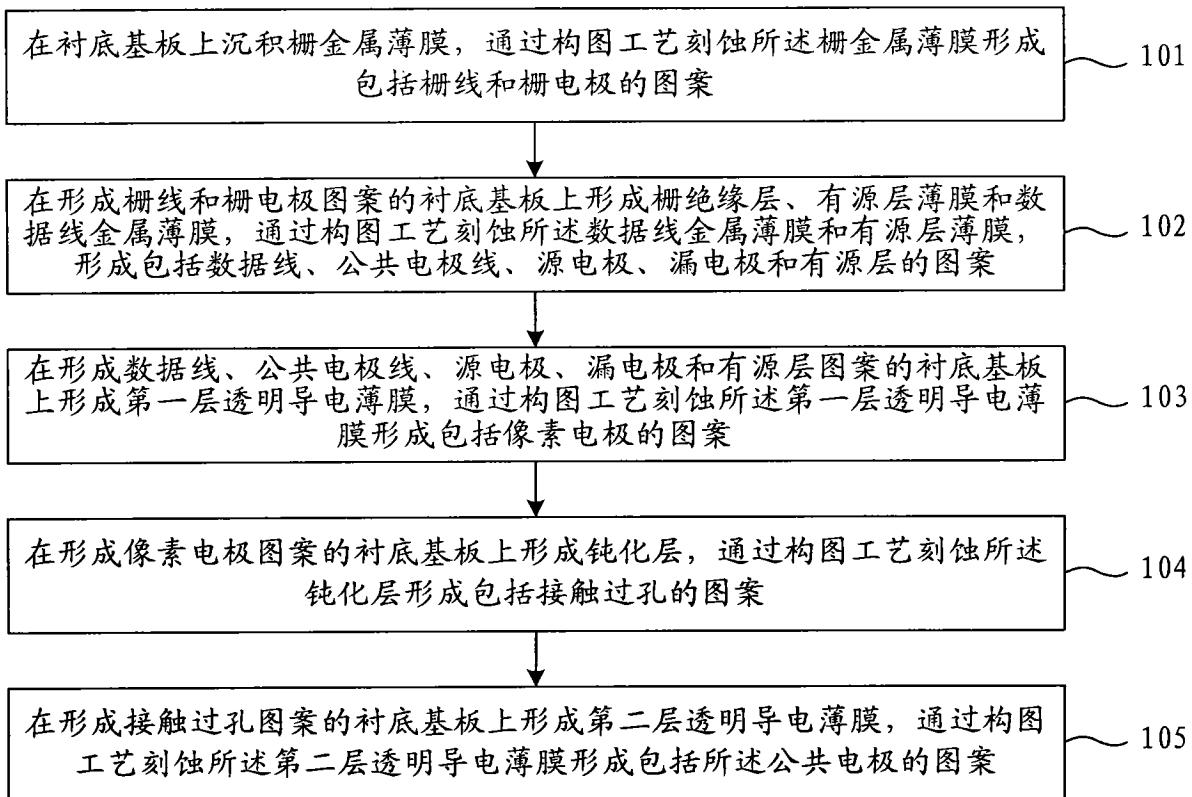

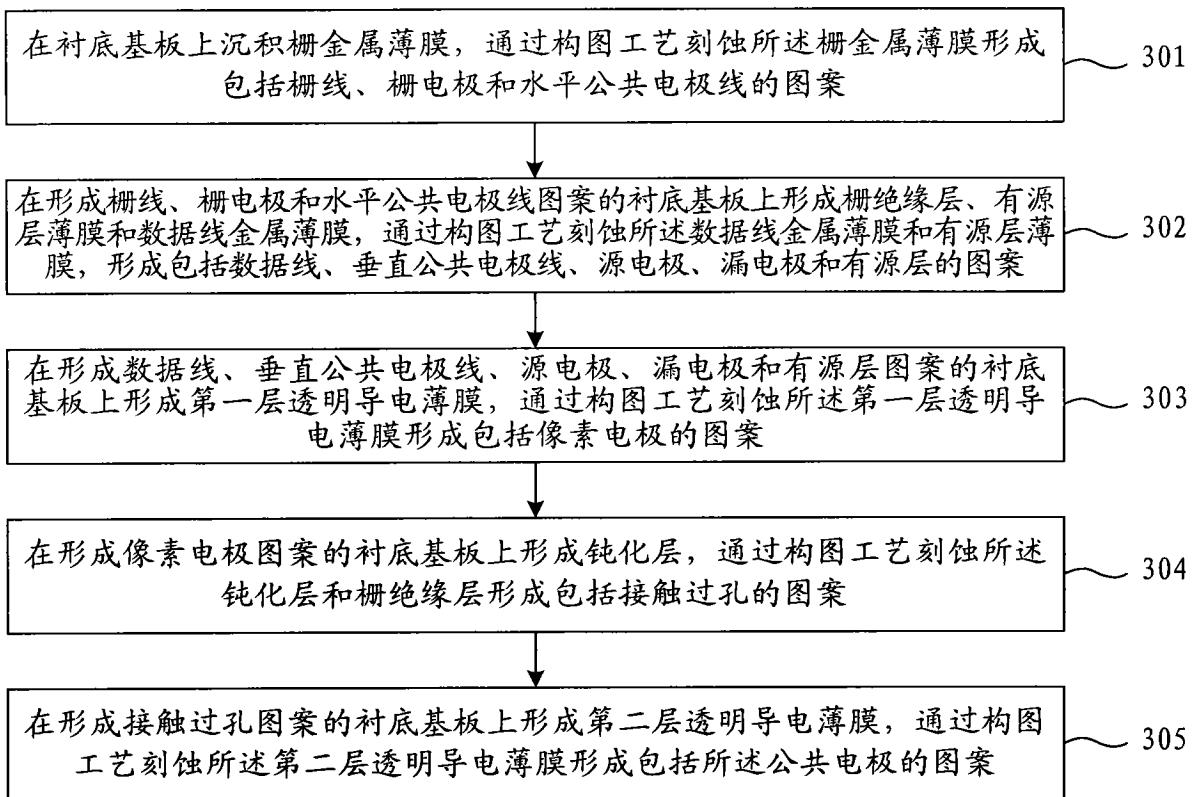

[0025] 图 7A 为本发明实施例三提供的阵列基板的制造方法的流程图；

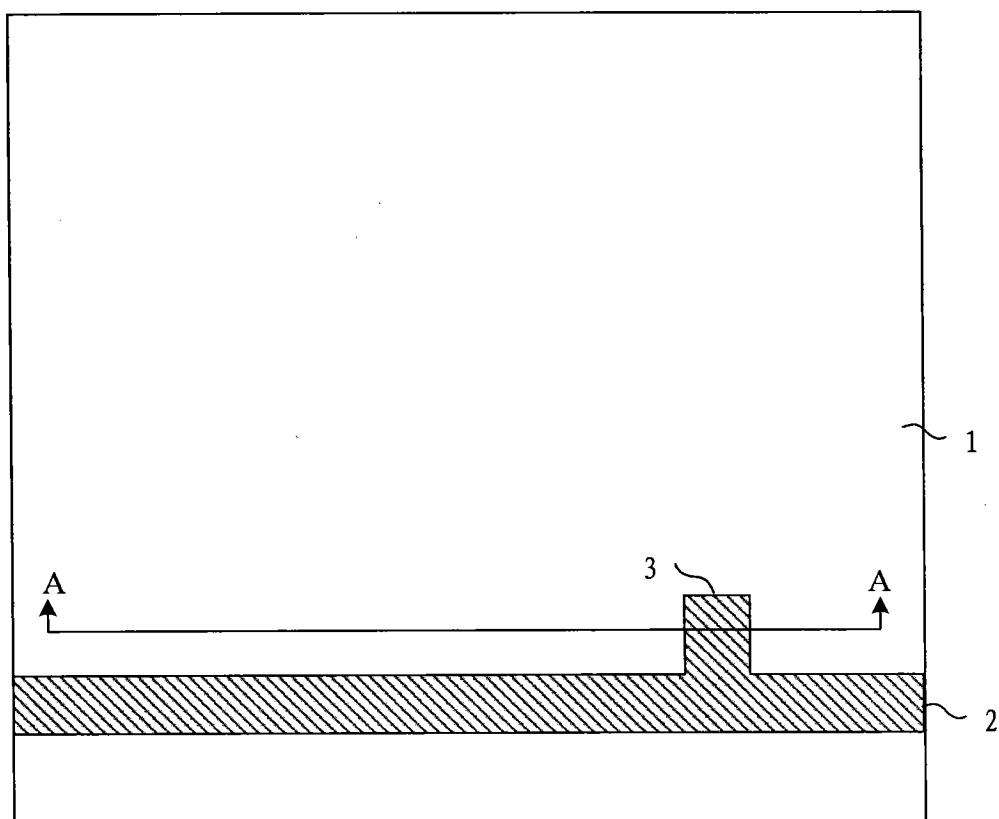

[0026] 图 7B 为本发明实施例三提供的阵列基板的制造方法中形成栅线和栅电极的衬底基板的局部俯视结构示意图；

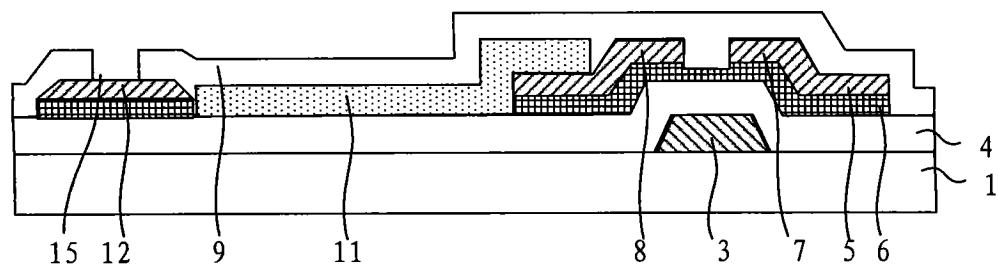

[0027] 图 7C 为图 7B 中沿 A-A 线的侧视剖切结构示意图；

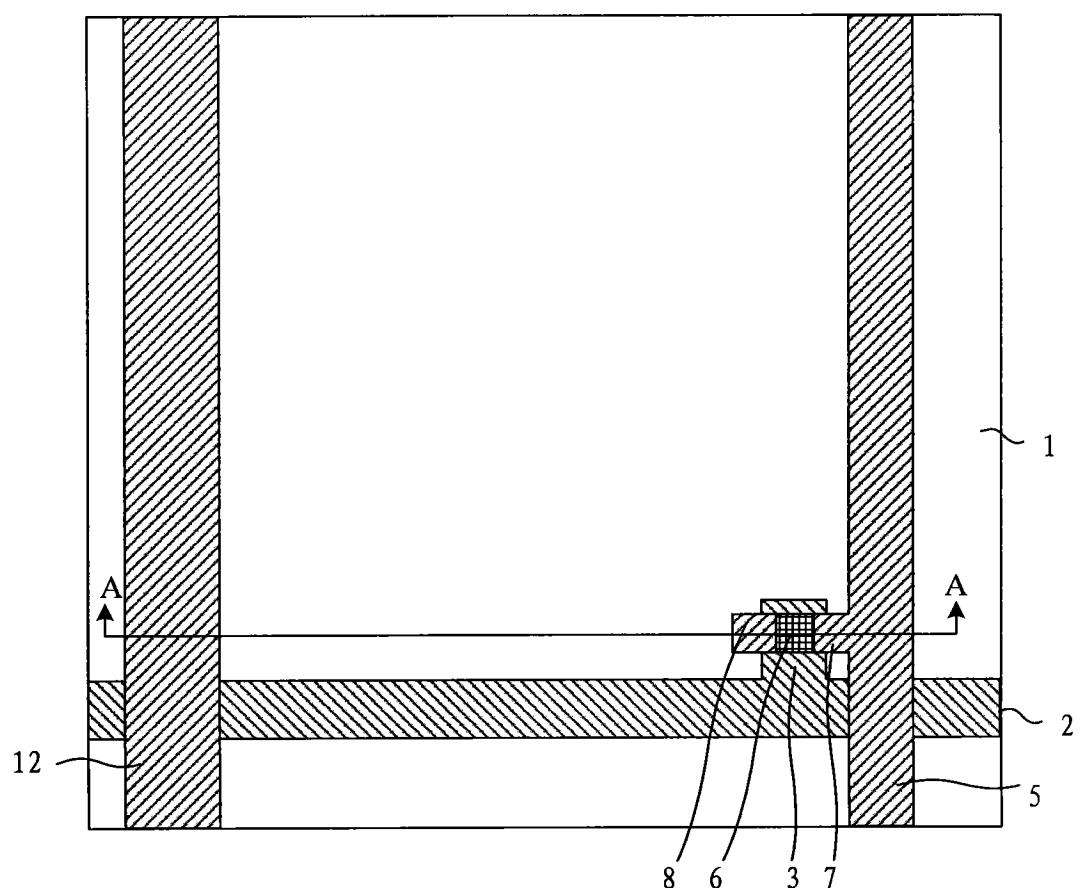

[0028] 图 7D 为本发明实施例三提供的阵列基板的制造方法中形成数据线、公共电极线、源电极、漏电极和有源层的衬底基板的一种局部俯视结构示意图；

[0029] 图 7E 为图 7D 中沿 A-A 线的侧视剖切结构示意图；

[0030] 图 7F 为本发明实施例三提供的阵列基板的制造方法中形成数据线、公共电极线、源电极、漏电极和有源层的衬底基板的另一种局部俯视结构示意图；

[0031] 图 7G 为图 7F 中沿 A-A 线的侧视剖切结构示意图；

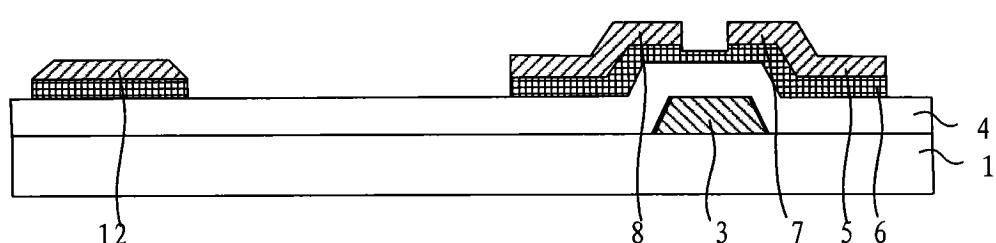

[0032] 图 7H 为本发明实施例三提供的阵列基板的制造方法中形成像素电极的衬底基板的一种局部俯视结构示意图；

[0033] 图 7I 为图 7H 中沿 A-A 线的侧视剖切结构示意图；

[0034] 图 7J 为本发明实施例三提供的阵列基板的制造方法中形成接触过孔的衬底基板的一种局部俯视结构示意图；

[0035] 图 7K 为图 7J 中沿 A-A 线的侧视剖切结构示意图；

[0036] 图 7L 为本发明实施例三提供的阵列基板的制造方法中形成公共电极的衬底基板的一种侧视剖切结构示意图；

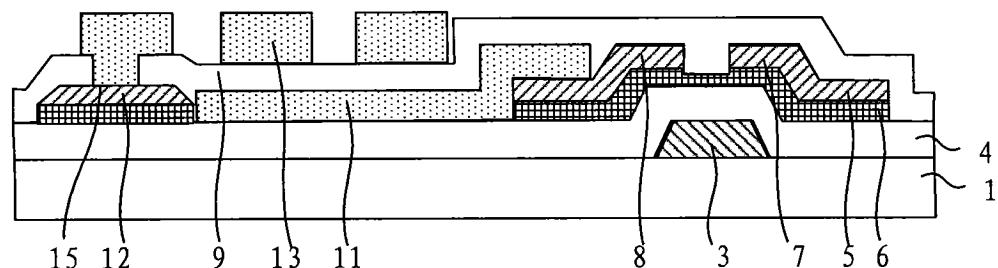

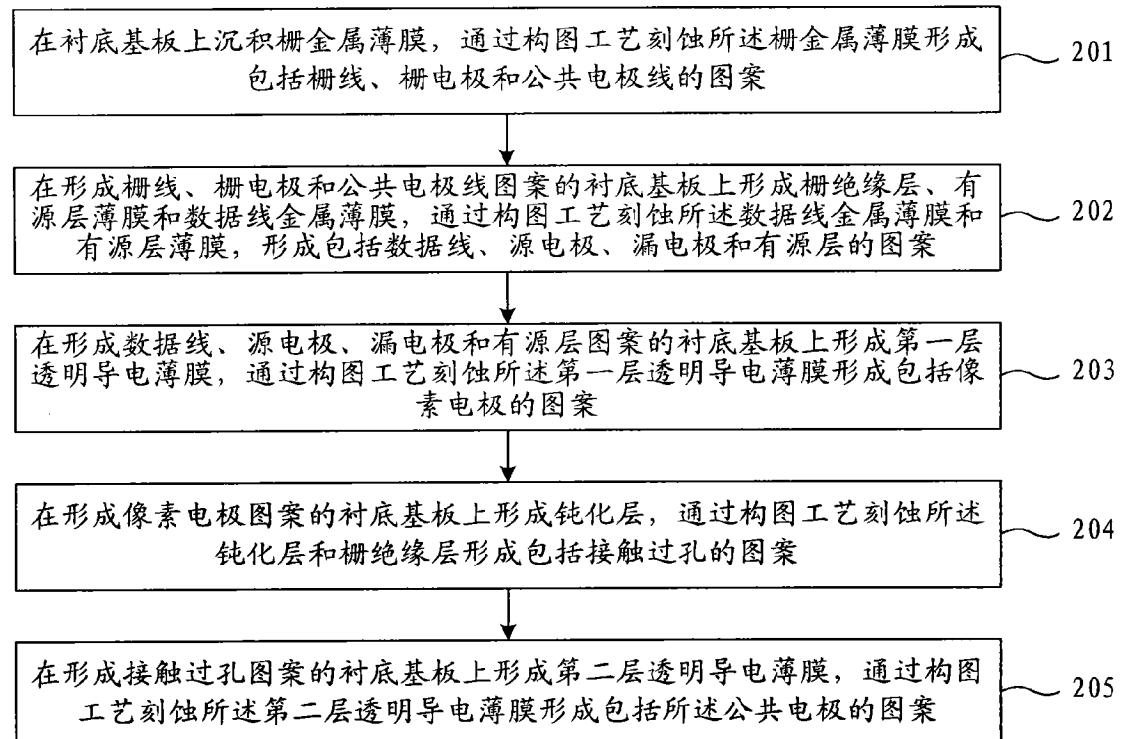

[0037] 图 8A 为本发明实施例四提供的阵列基板的制造方法的流程图；

[0038] 图 8B 为本发明实施例四提供的阵列基板的制造方法中形成栅线、栅电极和公共电极线的衬底基板的局部俯视结构示意图；

[0039] 图 8C 为本发明实施例四提供的阵列基板的制造方法中形成数据线、源电极、漏电极和有源层的衬底基板的一种局部俯视结构示意图；

[0040] 图 8D 为本发明实施例四提供的阵列基板的制造方法中形成数据线、源电极、漏电极和有源层的衬底基板的另一种局部俯视结构示意图；

[0041] 图 8E 为本发明实施例四提供的阵列基板的制造方法中形成像素电极的衬底基板的一种局部俯视结构示意图；

[0042] 图 8F 为本发明实施例四提供的阵列基板的制造方法中形成接触过孔的衬底基板的一种局部俯视结构示意图；

[0043] 图 9A 为本发明实施例五提供的阵列基板的制造方法的流程图。

[0044] 图 9B 为本发明实施例五提供的阵列基板的制造方法中形成数据线、第一公共电

极线、源电极、漏电极和有源层的衬底基板的一种局部俯视结构示意图；

[0045] 图 9C 为本发明实施例五提供的阵列基板的制造方法中形成像素电极 的衬底基板的一种局部俯视结构示意图；

[0046] 图 9D 为本发明实施例五提供的阵列基板的制造方法中形成像素电极的衬底基板的一种局部俯视结构示意图。

[0047] 主要附图标记：

- |        |           |              |           |

|--------|-----------|--------------|-----------|

| [0048] | 1- 衬底基板；  | 2- 棚线；       | 3- 棚电极；   |

| [0049] | 4- 棚绝缘层；  | 5- 数据线；      | 6- 有源层；   |

| [0050] | 61- 半导体层； | 62- 重掺杂半导体层； | 7- 源电极；   |

| [0051] | 8- 漏电极；   | 9- 钝化层；      |           |

| [0052] | 11- 像素电极； | 12- 公共电极线；   | 13- 公共电极； |

| [0053] | 14- 开关元件； | 15- 接触过孔；    | 30- 像素区域； |

| [0054] | 50- 阵列基板； | 60- 彩膜基板；    | 70- 电场。   |

## 具体实施方式

[0055] 为使本发明实施例的目的、技术方案和优点更加清楚，下面将结合本发明实施例中的附图，对本发明实施例中的技术方案进行清楚、完整地描述，显然，所描述的实施例是本发明一部分实施例，而不是全部的实施例。基于本发明中的实施例，本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例，都属于本发明保护的范围。本发明实施例以 HFFS 或 HAD-SDS 模式的液晶显示器举例说明。

[0056] 实施例一

[0057] 图 5 为本发明实施例一提供的阵列基板的结构示意图，如图 5 所示，该阵列基板包括衬底基板 1，衬底基板 1 的像素区域 30 中形成有横纵交叉围设形成多个像素单元的数据线和棚线，每个像素单元中包括开关元件、像素电极和公共电极 13，公共电极 13 为具有狭缝且布设在像素区域中的整块图案，其中：像素区域 30 中还形成有公共电极线 12，公共电极线 12 与公共电极 13 连通。

[0058] 在 HFFS 或 HAD-SDS 模式的液晶显示器的阵列基板中，可以将公共电极线 12 形成在像素区域 30 中，其中，公共电极线 12 和公共电极 13 可以通过接触过孔连通，也可以直接搭接连通。由于公共电极 13 为具有狭缝且布设在像素区域中的整块图案，在公共电极线 12 和公共电极 13 连通后，公共电极线 12 和公共电极 13 的电阻可以形成并联电路，可以减小公共电极的电阻。

[0059] 本实施例在液晶显示器的阵列基板的像素区域形成公共电极线，并将公共电极线与公共电极连通，可以减小公共电极的电阻，从而减小公共电极的 RC 信号延迟，提高公共电压 ( $V_{com}$ ) 信号的负荷能力，因此，可以减弱串扰现象，提高液晶显示器的画面质量。

[0060] 实施例二

[0061] 本发明实施例二提供的阵列基板包括衬底基板 1，衬底基板 1 的像素区域 30 中形成有横纵交叉围设形成多个像素单元的数据线和棚线，每个像素单元中包括开关元件、像素电极和公共电极 13，公共电极 13 为具有狭缝且布设在像素区域 30 中的整块图案，其中：像素区域 30 中还形成有公共电极线 12，公共电极线 12 与公共电极 13 连通，参见图 5。

[0062] 进一步地，在像素区域 30 中形成的公共电极线的位置可以包括以下几种方式：

[0063] 方式一、公共电极线 12 与数据线 5 同层设置且相互平行，公共电极线 12 通过接触过孔 15 与公共电极 13 连通，如图 6A 所示。

[0064] 其中，图 6A 为本发明实施例二提供的阵列基板的方式一的结构示意图。如图 6A 所示，公共电极线 12 与数据线 5 同层设置，二者可以相互平行且相邻，由于数据线 5 的材料一般采用金属薄膜，方块电阻低，而公共电极线 12 与数据线可以同步制成且材料相同，而公共电极一般采用 ITO 等透明金属氧化膜，因此公共电极线 12 的方块电阻也比公共电极 13 低。在公共电极线 12 和公共电极 13 连通后，公共电极线 12 和公共电极 13 的电阻可以形成并联电路，并且公共电极线 12 的电阻低，可以大幅减小公共电极 13 的电阻。并且公共电极线 12 通过接触过孔 15 与公共电极 13 连通，增加了公共电极线 12 与公共电极 13 的接触点，可以提高输入的公共电压 ( $V_{com}$ ) 信号的均匀性。此外，公共电极线 12 与数据线 5、源电极、漏电极可以采用同一道构图工艺刻蚀形成。接触过孔 15 可以与钝化层 (PVX) 采用同一道构图工艺刻蚀形成，可以不增加构图工艺的步骤，与现有工艺的工艺兼容性强。其中，本发明实施例中一次构图工艺的过程包括形成薄膜、涂覆光刻胶、曝光显影、刻蚀和剥离剩余的光刻胶的步骤，一次构图工艺过程中可以有多次刻蚀过程。

[0065] 此外，本实施例中的子像素结构设计与传统的保持一致，尺寸可以根据公共电极线的尺寸进行设计。在像素单元与公共电极线 12 相邻的区域形成的电场类似于横向电场 (In-Plane Shift；简称：IPS) 的平面电场，并不会发生像素漏光的现象。在公共电极线 12 上通过刻蚀接触过孔 15，可以将公共电极线 12 与公共电极 13 的 ITO 连通。

[0066] 方式二、公共电极线 12 与栅线 2 同层设置且相互平行，公共电极线 12 通过接触过孔 15 与公共电极 13 连通，如图 6B 所示。

[0067] 其中，图 6B 为本发明实施例二提供的阵列基板的方式二的结构示意图。如图 6B 所示，公共电极线 12 与栅线 2 同层设置，二者可以相互平行且相邻。由于栅线 2 的材料一般采用金属薄膜，方块电阻低，而公共电极线 12 与栅线 2 可以同步制成且材料相同，而公共电极一般采用 ITO 等透明金属氧化膜，因此公共电极线 12 的方块电阻也比公共电极 13 低。在公共电极线 12 和公共电极 13 连通后，公共电极线 12 和公共电极 13 的电阻可以形成并联电路，并且公共电极线 12 的电阻低，可以大幅减小公共电极 13 的电阻。并且公共电极线 12 通过接触过孔 15 与公共电极 13 连通，增加了公共电极线 12 与公共电极 13 的接触点，可以提高输入的公共电压 ( $V_{com}$ ) 信号的均匀性。此外，公共电极线 12 与栅线 2、栅电极可以采用同一道构图工艺刻蚀形成。接触过孔 15 可以与钝化层 (PVX) 采用同一道构图工艺刻蚀形成，可以不增加构图工艺的步骤，与现有工艺的工艺兼容性强。

[0068] 此外，在公共电极线 12 上通过刻蚀接触过孔 15，可以将公共电极线 12 与公共电极 13 的 ITO 连通。

[0069] 方式三、公共电极线包括第一公共电极线 121 和第二公共电极线 122，其中，第一公共电极线 121 与数据线 5 同层设置且相互平行，第二公共电极线 122 与栅线 2 同层设置且相互平行，第一公共电极线 121 和第二公共电极线 122 分别通过接触过孔 15 与公共电极 13 连通，如图 6C 所示。

[0070] 其中，图 6C 为本发明实施例二提供的阵列基板的方式三的结构示意图。如图 6C 所示，公共电极线包括第一公共电极线 121 和第二公共电极线 122，其中第一公共电极线 121

与数据线 5 同层设置，二者可以相互平行且相邻，第一公共电极线 121 与数据线 5 可以同步制成且材料相同。而第二公共电极线 122 与栅线 2 同层设置，二者可以相互平行且相邻，第二公共电极线 122 与栅线 2 可以同步制成且材料相同。由于数据线 5 和栅线 2 的材料一般采用金属薄膜，方块电阻低，而公共电极一般采用 ITO 等透明金属氧化膜，因此第一公共电极线 121 和第二公共电极线 122 的方块电阻也比公共电极 13 低。

[0071] 此外，在公共电极线上通过刻蚀接触过孔 15，可以将公共电极线 12 与公共电极 13 的 ITO 连通。

[0072] 除了本发明实施例中所举方式之外，公共电极线的位置也可以为其他的方式，例如：在公共电极上层直接形成公共电极线，此时公共电极线与公共电极直接搭接连通，公共电极线与公共电极的接触点增加，也可以形成并联电路，降低公共电极的电阻。

[0073] 其中，公共电极线的材料为金属或金属氧化物。如果公共电极线与数据线或栅线同步制成，则该公共电极线的材料可以为与数据线或栅线的材料相同的金属。如果公共电极线单独制成，也可以为其他材料制成，例如：金属氧化物等。

[0074] 再进一步地，像素电极的行数或列数为公共电极线数量的倍数，公共电极线均匀且间隔地分布于像素区域中，如图 6A、图 6B 和图 6C，可以多行或多列像素单元共用一条公共电极线。

[0075] 多列例如：“2、3、4……”列像素共用一条公共电极线 12，这样可以提高开口率。此外，由于在公共电极线 12 上层的钝化层 (PVX) 穿孔，故公共电极线 12 的宽度可以大于 10um，这是由于接触过孔的大小一般为 7 ~ 8um，为了使 ITO 和 SD 接触良好，需要左右各 2.5um 的偏差，因此公共电极线的宽度最好大于 10um。当然，公共电极线的宽度也可以选择其他尺寸，根据具体的应用场景进行选择，多列像素共用一条公共电极线 12 时，可以节省数据线 5 与公共电极线 12 的间隙，而增加公共电极线 12 的线宽。

[0076] 本实施例在液晶显示器的阵列基板的像素区域形成公共电极线，并且公共电极线与公共电极连通，可以形成并联电路，减小了公共电极的电阻；其中，公共电极线与数据线和 / 或栅线同层设置，可以采用数据线和 / 或栅线的材料制成，此时公共电极线的材料相对于公共电极的材料的方块电阻低，公共电极线与公共电极并联，可以进一步减小公共电极的电阻；从而减小公共电极的 RC 信号延迟，提高公共电压信号的负荷能力，因此，可以减弱串扰现象，提高液晶显示器的画面质量。

[0077] 本发明实施例提供的阵列基板的制造方法包括：在衬底基板的像素区域中形成栅线、开关元件、数据线、像素电极和公共电极的流程，所述公共电极为具有狭缝且布设在像素区域中的整块图案；

[0078] 此外，该阵列基板的制造方法还包括：在所述像素区域中，与所述栅线和 / 或数据线同层形成公共电极线的图案，所述公共电极线与所述栅线和 / 或数据线相互平行；

[0079] 连通所述公共电极和公共电极线。

[0080] 在液晶显示器的阵列基板的像素区域形成公共电极线，并且公共电极线与公共电极连通，可以形成并联电路，减小公共电极的电阻；其中，公共电极线与数据线同层设置，可以采用数据线的材料制成，此时公共电极线的材料相对于公共电极的材料的方块电阻低，公共电极线与公共电极并联，可以进一步减小公共电极的电阻；从而减小公共电极的 RC 信号延迟，提高公共电压信号的负荷能力，因此，可以减弱串扰现象，提高液晶显示器的画面

质量。

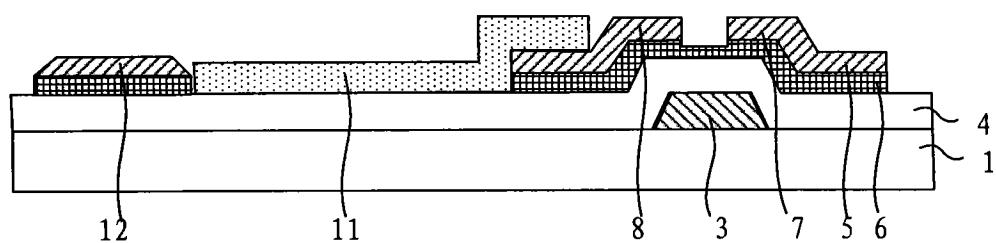

[0081] 实施例三

[0082] 图 7A 为本发明实施例三提供的阵列基板的制造方法的流程图,如图 7A 所示,该阵列基板的制造方法中,在衬底基板的像素区域中形成栅线、开关元件、数据线、像素电极、公共电极和公共电极线的流程包括:

[0083] 步骤 101、在衬底基板上通过构图工艺形成包括栅线和栅电极的图案。

[0084] 图 7B 为本发明实施例三提供的阵列基板的制造方法中形成栅线和栅电极的衬底基板的局部俯视结构示意图,图 7C 为图 7B 中沿 A-A 线的侧视剖切结构示意图,如图 7B 和图 7C 所示,在衬底基板 1 上沉积栅金属薄膜,涂覆光刻胶,采用单色调掩膜板对光刻胶进行曝光显影,刻蚀所述栅金属薄膜形成包括栅线 2 和栅电极 3 的图案后,剥离剩余的光刻胶。

[0085] 步骤 102、在形成上述图案的衬底基板上形成栅极绝缘层;在形成上述

[0086] 图案的衬底基板上通过构图工艺形成包括数据线、公共电极线、源电极、漏电极和有源层的图案;

[0087] 该步骤 102 可以为一次光刻过程:在形成上述图案的衬底基板上通过一次构图工艺形成包括数据线、公共电极线、源电极、漏电极和有源层的图案。如图 7D 所示,为本发明实施例三提供的阵列基板的制造方法中形成数据线、公共电极线、源电极、漏电极和有源层的衬底基板的一种局部俯视结构示意图,如图 7E 所示,为图 7D 中沿 A-A 线的侧视剖切结构示意图,在形成上述图案的衬底基板 1 上形成栅绝缘层 4 后,在形成上述图案的衬底基板 1 上形成有源层薄膜和数据线金属薄膜,涂覆光刻胶,采用双色调掩膜板对光刻胶进行曝光显影,形成包括完全保留区域、半保留区域和完全去除区域的光刻胶图案;刻蚀完全去除区域对应的所述有源层薄膜和数据线金属薄膜,形成包括数据线 5、有源层 6 和公共电极线 12 的图案;再刻蚀半保留区域对应的 所述数据线金属薄膜和有源层,形成包括 TFT 沟道、源电极 7 和漏电极 8 的图案,然后剥离剩余的光刻胶。

[0088] 该步骤 102 也可以为两次光刻过程:在形成上述图案的衬底基板上通过两次构图工艺形成包括数据线、公共电极线、源电极、漏电极和有源层的图案。图 7F 为本发明实施例三提供的阵列基板的制造方法中形成数据线、公共电极线、源电极、漏电极和有源层的衬底基板的另一种局部俯视结构示意图,图 7G 为图 7F 中沿 A-A 线的侧视剖切结构示意图,如图 7F 和图 7G 所示,在形成上述图案的衬底基板上形成栅绝缘层后,在形成上述图案的衬底基板 1 上形成有源层薄膜,涂覆光刻胶,采用单色调掩膜板对光刻胶进行曝光显影,刻蚀所述有源层薄膜形成包括有源层 6 的图案,然后剥离剩余的光刻胶;在形成上述图案的衬底基板 1 上形成数据线金属薄膜,涂覆光刻胶,采用单色调掩膜板对光刻胶进行曝光显影,刻蚀所述数据线金属薄膜,形成包括数据线 5、公共电极线 12、源电极 7 和漏电极 8 的图案,然后剥离剩余的光刻胶。

[0089] 步骤 103、在形成上述图案的衬底基板上通过构图工艺形成包括像素电极的图案,所述像素电极与所述漏电极搭接连通;

[0090] 图 7H 为本发明实施例三提供的阵列基板的制造方法中形成像素电极的衬底基板的一种局部俯视结构示意图,图 7I 为图 7H 中沿 A-A 线的侧视剖切结构示意图,如图 7H 和图 7I 所示,在形成上述图案的衬底基板 1 上形成第一层透明导电薄膜,涂覆光刻胶后,采用单色调掩膜板对光刻胶进行曝光显影,刻蚀所述第一层透明导电薄膜形成包括像素电极 11

的图案，所述像素电极 11 与所述漏电极 8 搭接连通，然后剥离剩余的光刻胶。

[0091] 步骤 104、在形成上述图案的衬底基板上形成钝化层，通过构图工艺形成包括接触过孔的图案；

[0092] 图 7J 为本发明实施例三提供的阵列基板的制造方法中形成接触过孔的衬底基板的一种局部俯视结构示意图，图 7K 为图 7J 中沿 A-A 线的侧视剖切结构示意图，如图 7J 和图 7K 所示，在形成上述图案的衬底基板 1 上形成钝化层 9 后，涂覆光刻胶，采用单色调掩膜板对光刻胶进行曝光显影，刻蚀所述钝化层 9 形成包括接触过孔 15 的图案，然后剥离剩余的光刻胶。

[0093] 步骤 105、在形成上述图案的衬底基板上通过构图工艺形成包括所述公共电极的图案，所述公共电极线与所述公共电极通过所述接触过孔连通；

[0094] 图 7L 为本发明实施例三提供的阵列基板的制造方法中形成公共电极的衬底基板的一种侧视剖切结构示意图，如图 7L 所示，在形成上述图案的衬底基板 1 上形成第二层透明导电薄膜，涂覆光刻胶，采用单色调掩膜板对光刻胶进行曝光显影，刻蚀所述第二层透明导电薄膜形成包括所述公共电极 13 的图案，所述公共电极线 12 与所述公共电极 13 通过所述接触过孔 15 连通，然后剥离剩余的光刻胶。

[0095] 本实施例得到的阵列基板的结构，可以参见上述实施例二中的方式一的相关描述以及图 6A。

[0096] 本实施例在液晶显示器的阵列基板的像素区域形成公共电极线，并且公共电极线与公共电极连通，可以形成并联电路，减小了公共电极的电阻；其中，公共电极线与数据线同层设置，可以采用数据线的材料制成，此时公共电极线的材料相对于公共电极的材料的方块电阻低，公共电极线与公共电极并联，可以进一步减小公共电极的电阻；从而减小公共电极的 RC 信号延迟，提高公共电压信号的负荷能力，因此，可以减弱串扰现象，提高液晶显示器的画面质量。

#### [0097] 实施例四

[0098] 图 8A 为本发明实施例四提供的阵列基板的制造方法的流程图，如图 8A 所示，该阵列基板的制造方法中，在衬底基板的像素区域中形成栅线、开关元件、数据线、像素电极、公共电极和公共电极线的流程包括：

[0099] 步骤 201、在衬底基板上通过构图工艺形成包括栅线、栅电极和公共电极线的图案；

[0100] 图 8B 为本发明实施例四提供的阵列基板的制造方法中形成栅线、栅电极 和公共电极线的衬底基板的局部俯视结构示意图，如图 8B 所示，在衬底基板上沉积栅金属薄膜，涂覆光刻胶，采用单色调掩膜板对光刻胶进行曝光显影，刻蚀所述栅金属薄膜形成包括栅线 2、栅电极 3 和公共电极线 12 的图案；如图 8B 所示，为刻蚀形成的包括栅线、栅电极和公共电极线的图案，然后剥离剩余的光刻胶。

[0101] 步骤 202、在形成上述图案的衬底基板上形成栅极绝缘层；在形成上述图案的衬底基板上通过构图工艺形成包括数据线、源电极、漏电极和有源层的图案；

[0102] 该步骤 202 可以为一次光刻过程：在形成上述图案的衬底基板上通过一次构图工艺形成包括数据线、源电极、漏电极和有源层的图案。如图 8C 所示，为本发明实施例四提供的阵列基板的制造方法中形成数据线、源电极、漏电极和有源层的衬底基板的一种局部俯

视结构示意图，在形成上述图案的衬底基板 1 上形成栅绝缘层后，在形成上述图案的衬底基板 1 上形成有源层薄膜和数据线金属薄膜，涂覆光刻胶，采用双色调掩膜板光刻胶进行曝光显影，形成包括完全保留区域、半保留区域和完全去除区域的光刻胶图案；刻蚀完全去除区域对应的所述有源层薄膜和数据线金属薄膜，形成包括数据线 5 和有源层 6 的图案；再刻蚀半保留区域对应的所述数据线金属薄膜，形成包括 TFT 沟道、源电极 7 和漏电极 8 的图案，然后剥离剩余的光刻胶。

[0103] 该步骤 202 也可以为两次光刻过程：在形成上述图案的衬底基板上通过两次构图工艺形成包括数据线、源电极、漏电极和有源层的图案。如图 8D 所示，为本发明实施例四提供的阵列基板的制造方法中形成数据线、源电极、漏电极和有源层的衬底基板的另一种局部俯视结构示意图，在形成上述图案的衬底基板上 1 形成栅绝缘层后，在形成上述图案的衬底基板上形成有源层薄膜，涂覆光刻胶，采用单色调掩膜板对光刻胶进行曝光显影，刻蚀所述有源层薄膜形成包括有源层 6 的图案，剥离剩余的光刻胶；在形成上述图案的衬底基板 1 上形成数据线金属薄膜，涂覆光刻胶，采用单色调掩膜板对光刻胶进行曝光显影，刻蚀所述数据线金属薄膜，形成包括数据线 5、源电极 7 和漏电极 8 的图案，然后剥离剩余的光刻胶。

[0104] 步骤 203、在形成上述图案的衬底基板上通过构图工艺形成包括像素电极的图案，所述像素电极与所述漏电极搭接连通；

[0105] 图 8E 为本发明实施例四提供的阵列基板的制造方法中形成像素电极的衬底基板的一种局部俯视结构示意图，在形成上述图案的衬底基板 1 上形成第一层透明导电薄膜，涂覆光刻胶，采用单色调掩膜板对光刻胶进行曝光显影，刻蚀所述第一层透明导电薄膜形成包括像素电极 11 的图案，所述像素电极 11 与所述漏电极 8 搭接连通，然后剥离剩余的光刻胶。

[0106] 步骤 204、在形成上述图案的衬底基板上形成钝化层，通过构图工艺形成包括接触过孔的图案；

[0107] 图 8F 为本发明实施例四提供的阵列基板的制造方法中形成接触过孔的衬底基板的一种局部俯视结构示意图，在形成上述图案的衬底基板 1 上形成钝化层后，涂覆光刻胶，采用单色调掩膜板对光刻胶进行曝光显影，通过构图工艺刻蚀所述钝化层和栅绝缘层形成包括接触过孔 15 的图案，然后剥离剩余的光刻胶。

[0108] 步骤 205、在形成上述图案的衬底基板上通过构图工艺形成包括所述公共电极的图案，所述公共电极线与所述公共电极通过所述接触过孔连通。

[0109] 在形成上述图案的衬底基板上形成第二层透明导电薄膜，涂覆光刻胶，采用单色调掩膜板对光刻胶进行曝光显影，刻蚀所述第二层透明导电薄膜形成包括所述公共电极的图案，所述公共电极线与所述公共电极通过所述接触过孔连通，然后剥离剩余的光刻胶。

[0110] 本实施例得到的阵列基板的结构，可以参见上述实施例二中的方式二的相关描述以及图 6B。

[0111] 本实施例在液晶显示器的阵列基板的像素区域形成公共电极线，并将公共电极线与公共电极连通，可以形成并联电路，减小了公共电极的电阻；其中，公共电极线与栅线同层设置，可以采用栅线的材料制成，此时公共电极线的材料相对于公共电极的材料的方块电阻低，与公共电极并联，可以进一步减小公共电极的电阻；从而减小公共电极的 RC 信号

延迟,提高公共电压信号的负荷能力,因此,可以减弱串扰现象,提高液晶显示器的画面质量。

[0112] 实施例五

[0113] 图 9A 为本发明实施例五提供的阵列基板的制造方法的流程图,如图 9A 所示,该阵列基板的制造方法中,在衬底基板的像素区域中形成栅线、开关元件、数据线、像素电极、公共电极和公共电极线的流程包括 :

[0114] 步骤 301、在衬底基板上通过构图工艺形成包括栅线、栅电极和第二公共电极线的图案;

[0115] 在衬底基板上沉积栅金属薄膜,涂覆光刻胶,采用单色调掩膜板对光刻胶进行曝光显影,刻蚀所述栅金属薄膜形成包括栅线 2、栅电极 3 和第二公共电极线的图案,然后剥离剩余的光刻胶;可以参见图 8B,其中的公共电极线 12 为第二公共电极线。

[0116] 步骤 302、在形成上述图案的衬底基板上形成栅极绝缘层;在形成上述图案的衬底基板上通过构图工艺形成包括数据线、第一公共电极线、源电极、漏电极和有源层的图案;

[0117] 该步骤 302 可以为一次光刻过程,也可以为两次光刻过程,具体方法可以参照上述实施例中的步骤 102 的相关描述。如图 9B 所示,为本发明实施例五提供的阵列基板的制造方法中形成数据线、第一公共电极线、源电极、漏电极和有源层的衬底基板的一种局部俯视结构示意图,经过步骤 302 后,衬底基板 1 上形成了两种公共电极线,一种与数据线 5 同层设置且相互平行的第一公共电极线 121,一种是与栅线 3 同层设置且相互平行的第二公共电极线 122。

[0118] 步骤 303、在形成上述图案的衬底基板上通过构图工艺形成包括像素电极的图案,所述像素电极与所述漏电极搭接连通;

[0119] 图 9C 为本发明实施例五提供的阵列基板的制造方法中形成像素电极的衬底基板的一种局部俯视结构示意图,如图 9C 所示,在形成上述图案的衬底基板 1 上形成第一层透明导电薄膜,涂覆光刻胶,采用单色调掩膜板对光刻胶进行曝光显影,刻蚀所述第一层透明导电薄膜形成包括像素电极 11 的图案,所述像素电极 11 与所述漏电极 8 搭接连通,然后剥离剩余的光刻胶。

[0120] 步骤 304、在形成上述图案的衬底基板上形成钝化层,通过构图工艺形成包括接触过孔的图案;

[0121] 图 9D 为本发明实施例五提供的阵列基板的制造方法中形成像素电极的衬底基板的一种局部俯视结构示意图,如图 9D 所示,在形成上述图案的衬底基板 1 上形成钝化层后,涂覆光刻胶,采用单色调掩膜板对光刻胶进行曝光显影,刻蚀钝化层、栅绝缘层形成包括接触过孔 15 的图案,然后剥离剩余的光刻胶。

[0122] 步骤 305、在形成上述图案的衬底基板上通过构图工艺形成包括所述公共电极的图案,所述第二公共电极线与所述第一公共电极线分别通过接触过孔与所述公共电极连通。

[0123] 在形成上述图案的衬底基板上形成第二层透明导电薄膜,涂覆光刻胶,采用单色调掩膜板对光刻胶进行曝光显影,刻蚀所述第二层透明导电薄膜形成包括所述公共电极的图案,所述第二公共电极线与所述第一公共电极线分别通过接触过孔与所述公共电极连

通，然后剥离剩余的光刻胶。

[0124] 本实施例得到的阵列基板的结构，可以参见上述实施例二中的方式三的相关描述以及图 6C。

[0125] 本发明上述实施例的阵列基板结构，数据线是竖直设置的、栅线是水平设置的，实际生产当中，可以根据需要变换二者的方向，例如：数据线是水平设置的，栅线是竖直设置的。而且本发明上述实施例只是列举了几种阵列基板的结构，各膜层之间的顺序可以根据需要进行调换。

[0126] 本实施例在液晶显示器的阵列基板的像素区域形成公共电极线，并将公共电极线与公共电极连通，可以形成并联电路，减小了公共电极的电阻；其中，公共电极线分别与数据线和栅线同层设置，可以采用数据线和栅线的材料制成，此时公共电极线的材料相对于公共电极的材料的方块电阻低，与公共电极并联，可以进一步减小公共电极的电阻；从而减小公共电极的 RC 信号延迟，提高公共电压信号的负荷能力，因此，可以减弱串扰现象，提高液晶显示器的画面质量。

[0127] 此外，现有技术为了降低 HFFS 或 HAD-SDS 的串扰现象，采用的处理方法与本发明的比较举例如下。

[0128] 例如：增加公共电压信号输入线的宽度和输入信号的路径；这种方法需要充裕的 Sealant（封框胶）区域，增加液晶面板尺寸，降低玻璃的利用率。相比较而言，本发明不需要增加液晶面板尺寸，阵列基板的玻璃的利用率高。

[0129] 又如：增加公共电极材料 ITO 的厚度，减小公共电极的电阻；这种方法随着 ITO 厚度的增加，液晶面板的透过率下降；如图 10 所示，为在不同厚度的 ITO 的透过率随入射光线波长变化的曲线图，ITO 的厚度从  $400\text{\AA}$  提高到  $800\text{\AA}$  时，透过率约降低 5%。相比较而言，本发明不影响液晶面板的透过率。

[0130] 再如：在钝化层上涂覆一层低介电常数的树脂（Resin），以降低公共电极与像素电极之间的电容；并且，为了防止 IC 绑定（bonding）不良，在一般只在像素区域增加树脂层，需要将钝化层上其他区域的树脂层刻掉，因此，这种方法需要在原来的基础上多一张光刻（Mask），工艺制程复杂，成本提高，并且由于树脂层的作用，液晶的驱动电压要随之增加，液晶面板的能耗增加。

[0131] 本实施例的阵列基板的制造方法可以用于制备本发明实施例所提供的阵列基板，该阵列基板的制造方法具备形成相应结构的步骤。

[0132] 最后应说明的是：以上实施例仅用以说明本发明的技术方案，而非对其限制；尽管参照前述实施例对本发明进行了详细的说明，本领域的普通技术人员应当理解：其依然可以对前述各实施例所记载的技术方案进行修改，或者对其中部分技术特征进行等同替换；而这些修改或者替换，并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

图 1

图 2

图 3

图 4

图 5

图 6A

图 6B

图 6C

图 7A

图 7B

图 7C

图 7D

图 7E

图 7F

图 7G

图 7H

图 7I

图 7J

图 7K

图 7L

图 8A

图 8B

图 8C

图 8D

图 8E

图 8F

图 9A

图 9B

图 9C

图 9D

|                |                                                      |         |            |

|----------------|------------------------------------------------------|---------|------------|

| 专利名称(译)        | 阵列基板及其制造方法和液晶显示器                                     |         |            |

| 公开(公告)号        | <a href="#">CN102135691B</a>                         | 公开(公告)日 | 2012-05-23 |

| 申请号            | CN201110020250.8                                     | 申请日     | 2011-01-18 |

| [标]申请(专利权)人(译) | 京东方科技集团股份有限公司<br>成都京东方光电科技有限公司                       |         |            |

| 申请(专利权)人(译)    | 京东方科技集团股份有限公司<br>成都京东方光电科技有限公司                       |         |            |

| 当前申请(专利权)人(译)  | 京东方科技集团股份有限公司<br>成都京东方光电科技有限公司                       |         |            |

| [标]发明人         | 黄炜赟<br>高永益<br>玄明花                                    |         |            |

| 发明人            | 黄炜赟<br>高永益<br>玄明花                                    |         |            |

| IPC分类号         | G02F1/1362 H01L27/12 H01L21/77                       |         |            |

| CPC分类号         | G02F2001/134372 G02F1/136286 G02F1/136227 H01L27/124 |         |            |

| 代理人(译)         | 黄志华                                                  |         |            |

| 审查员(译)         | 李晴晴                                                  |         |            |

| 优先权            | 201010286926.3 2010-09-17 CN                         |         |            |

| 其他公开文献         | <a href="#">CN102135691A</a>                         |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>       |         |            |

### 摘要(译)

本发明公开了一种阵列基板及其制造方法和液晶显示器。阵列基板，包括衬底基板，所述衬底基板的像素区域中形成有横纵交叉围设形成多个像素单元的数据线和栅线，每个像素单元中包括开关元件、像素电极和公共电极，所述公共电极为具有狭缝且布设在像素区域中的整块图案，其中：所述像素区域中还形成有公共电极线，所述公共电极线与所述公共电极连通。本发明在液晶显示器的阵列基板的像素区域形成公共电极线，并且公共电极线与公共电极连通，公共电极线与公共电极可以形成并联电路，减小了公共电极的电阻，从而减小公共电极的RC信号延迟，提高公共电压信号的负荷能力，因此，可以减弱串扰现象，提高液晶显示器的画面质量。