## [12] 发明专利申请公开说明书

[21] 申请号 200310121289.4

[43] 公开日 2004 年 6 月 30 日

[11] 公开号 CN 1508612A

[22] 申请日 2003.12.17

[74] 专利代理机构 北京康信知识产权代理有限公司

代理人 余 刚

[21] 申请号 200310121289.4

[30] 优先权

[32] 2002.12.17 [33] KR [31] 2002 - 0080812

[71] 申请人 三星电子株式会社

地址 韩国京畿道

[72] 发明人 金东奎

权利要求书 2 页 说明书 27 页 附图 49 页

[54] 发明名称 薄膜晶体管阵列面板及包括该面板的液晶显示器

## [57] 摘要

本发明提供一种 TFT 阵列面板，在其绝缘基板上形成包括栅极线和栅极的栅极布线，在覆盖栅极布线的栅极绝缘层上形成由非晶硅组成的半导体层。在覆盖栅极布线的半导体层或栅极绝缘层上形成包括数据线、源极、及漏极的数据布线。半导体层的一部分延伸至数据线的下部，在栅极布线同一层上形成与位于数据线下部半导体层部分重叠的遮光层。该遮光层用于防止来自背光源入射基板的光射入非晶硅层；从而可防止液晶显示器显示图像时出现的具有不同亮度的条和这类条上下移动的水波纹现象，而液晶显示器是使用背光源由反相器输出的开/关信号的矩形波驱动。

1. 一种薄膜晶体管阵列面板，包括：

绝缘基板；

形成于所述绝缘基板上并且包括栅极线、与所述栅极线连接的栅极的栅极布线；

覆盖所述栅极布线的栅极绝缘层；

包括与所述栅极线交叉的数据线、与所述数据线连接的源极、和相对于所述栅极面对所述源极的漏极的数据布线；

形成于所述栅极绝缘层上并有一部分延伸至所述数据线下部的半导体层；

与所述数据线下部的所述半导体层重叠并与所述栅极布线形成于同层的遮光层；以及

与所述漏极电连接的像素电极。

2. 根据权利要求 1 所述的薄膜晶体管阵列面板，其特征在于，与所述半导体层重叠的所述遮光层的宽度与所述半导体层的宽度相比，等于或大于所述半导体层厚度的 60%。

3. 根据权利要求 1 所述的薄膜晶体管阵列面板，其特征在于，所述数据线下部的所述半导体层形成与所述数据线的宽度相同或比所述数据线的宽度更大的宽度。

4. 根据权利要求 2 所述的薄膜晶体管阵列面板，其特征在于，除所述源极和所述漏极之间的通道部分之外，所述半导体层具有与所述数据布线相同的图案。

5. 根据权利要求 4 所述的薄膜晶体管阵列面板，其特征在于，所述半导体层的一部分露在所述数据布线的边缘。

6. 根据权利要求 2 所述的薄膜晶体管阵列面板，其特征在于，所述数据布线包括下层和形成在所述下层并具有与所述下层不同图案的上层。

7. 一种液晶显示器，包括：

权利要求 1 所述的薄膜晶体管阵列面板；

面对所述薄膜晶体管阵列面板的反向面板；

相对于所述薄膜晶体管阵列面板，用于从所述反向面板的对面发射光入射所述薄膜晶体管阵列面板的背光源，其特点在于，

所述背光源通过输出开/关的矩形波信号的反相器驱动。

# 薄膜晶体管阵列面板及包括该面板的液晶显示器

## 技术领域

本发明涉及一种薄膜晶体管（TFT）阵列面板及包括该面板的液晶显示器。

## 背景技术

液晶显示器是目前使用最广泛的平板显示器之一，其包括具备产生场的电极的两张面板和充填在其间的液晶层，并且通过给电极施加电压使液晶层的液晶分子重新排列来调整所透过光的透射比。

在这些液晶显示器中最流行的是在各自面板上具有电极并具有多个用于切换施加到电极上电压的薄膜晶体管（“TFTs”）的液晶显示器。通常，TFT 在两个面板之一上面形成。

在液晶显示器的一个面板上形成包括用于传递栅极信号的栅极线和用于传递图像信号的数据线的信号布线、传递通过数据线施加图像信号的像素电极、及用于控制通过栅极信号传递到各像素电极上图像信号的 TFT 等，而在另一个液晶显示器面板上形成用于显示彩色图像的滤色器及用于阻挡像素之间的泄漏光并用于防止对比度降低的黑阵。

就 TFT 半导体层而言，通常使用氢化非晶硅。有时非晶硅层被残留在布线的下面以防止布线断线，或在制造过程中无法除掉其下部非晶硅层，因而非晶硅层被残留下以简化该制造过程。

然而，来自作为液晶显示器光源的背光源的光射入半导体层，以在非晶硅层产生空穴或电子，其可引起光泄漏电流，而这种光泄漏电流可导致液晶显示器性能的降低。尤其是，该光泄漏电流可改变图像信号，其结果是改变传递到像素电极的像素电压。因此，当显示图像时，出现具有不同亮度并且上下移动的条。

## 发明内容

本发明涉及一种可以提高液晶显示器显示性能的 TFT 阵列面板及包括该面板的液晶显示器。

根据本发明的 TFT 阵列面板及包括 TFT 阵列面板的液晶显示器，具有位于数据线下部非晶硅层的下部的遮光层。

根据本发明具体实施例，在液晶显示器的 TFT 阵列面板的基板上形成包括栅极线和栅极的栅极布线。在覆盖栅极布线的栅极绝缘层上形成包括与栅极线交叉的数据线、连接在数据线上的源极、以及相对于栅极面对源极的漏极的数据布线。在栅极绝缘层上形成半导体层，而半导体层的一部分延伸至数据线的下部。在面板上形成与栅极布线同层且与数据线下部半导体层重叠的遮光层，在面板上形成与漏极电连接的像素电极。

优选与半导体层重叠的遮光层的宽度与半导体层的宽度相比，等于或大于半导体层的宽度的 60%。而形成的在数据线下部的半导体层具有与数据线相同或比其更大的宽度。

除了源极与漏极之间的通道部分以外，半导体层可以与数据布线具有同样的图案，并且半导体层的一部分可以暴露在数据布线的边缘。

数据布线可以包括下层和形成于下层且具有与下层不同图案的上层。

用于这种根据本发明的包括 TFT 阵列面板的液晶显示器光源的背光源是由输出开 (On)/关 (Off) 的矩形波信号的反相器驱动。

### 附图说明

本发明的上述和其它优点将通过参考附图详细地描述其优选具体实施例而变得更加明显，其中：

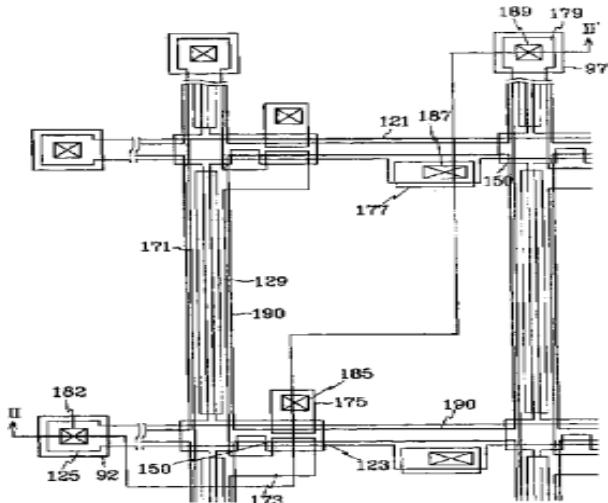

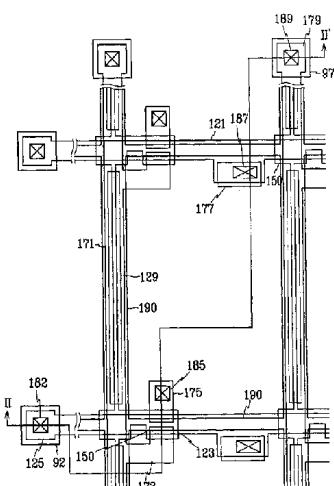

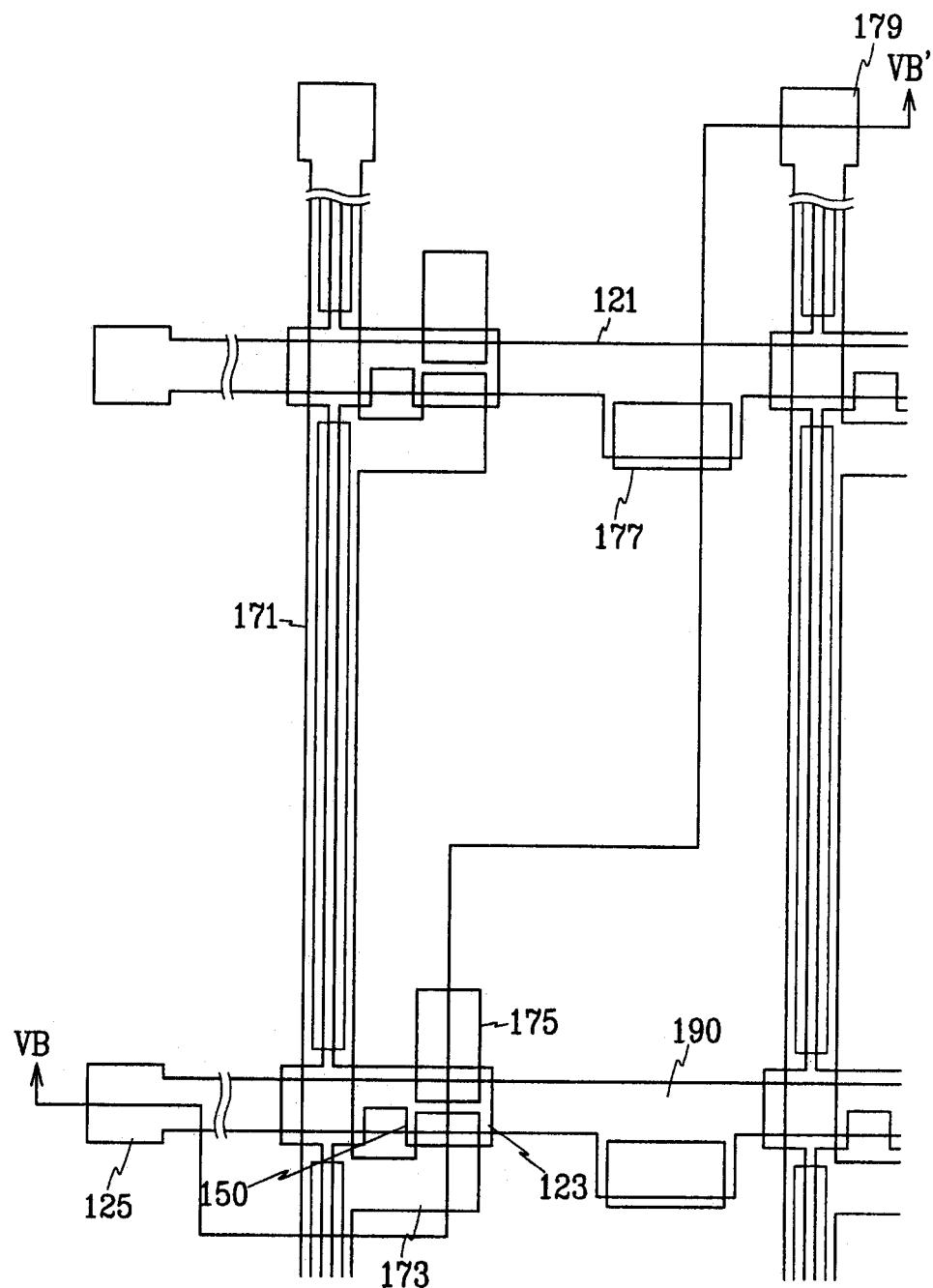

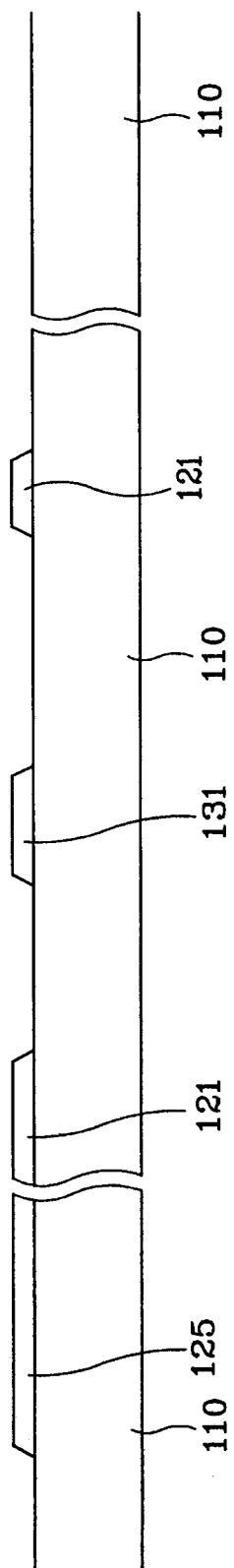

图 1 是根据本发明第一具体实施例的用于液晶显示器的 TFT 阵列面板的配置图；

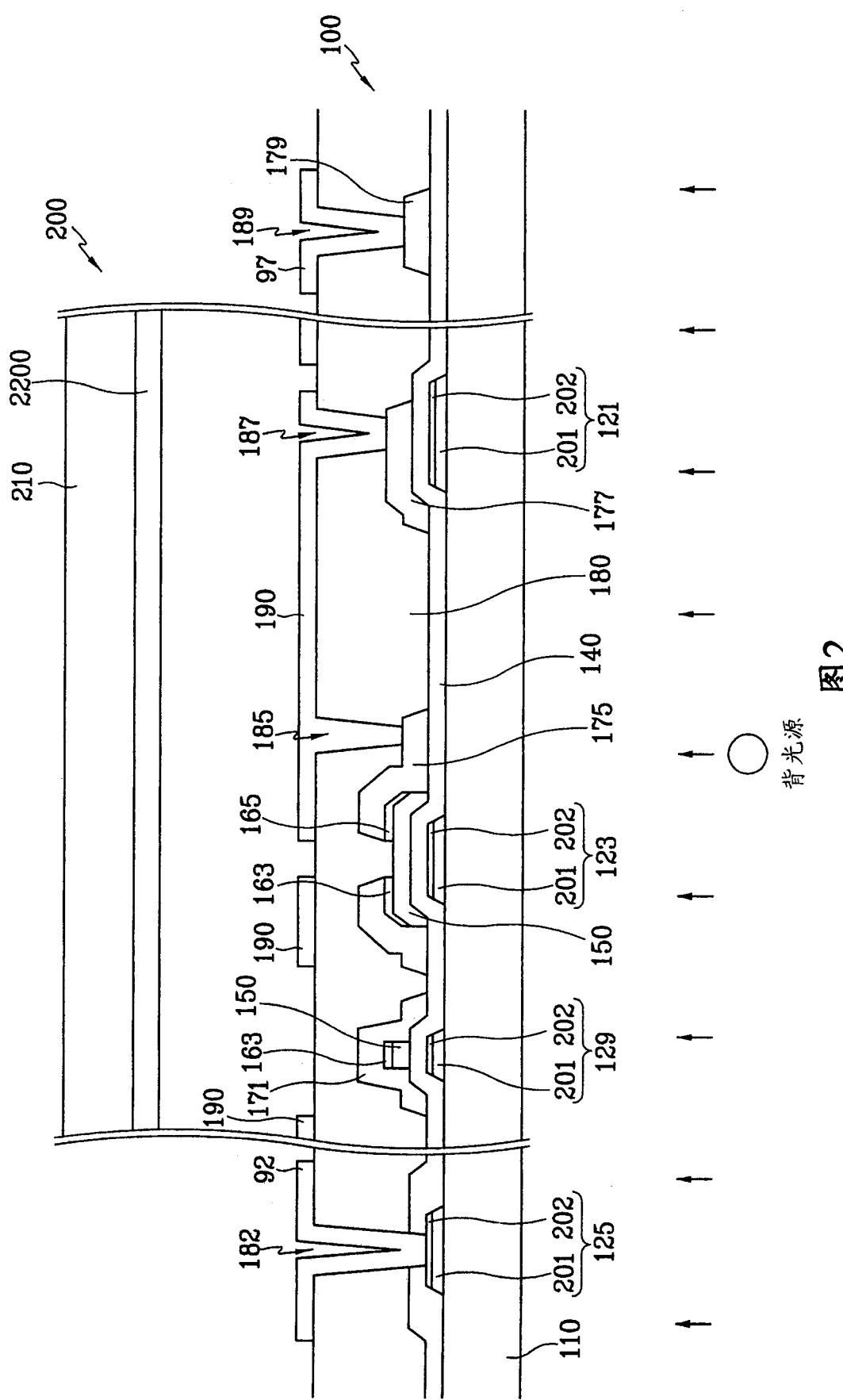

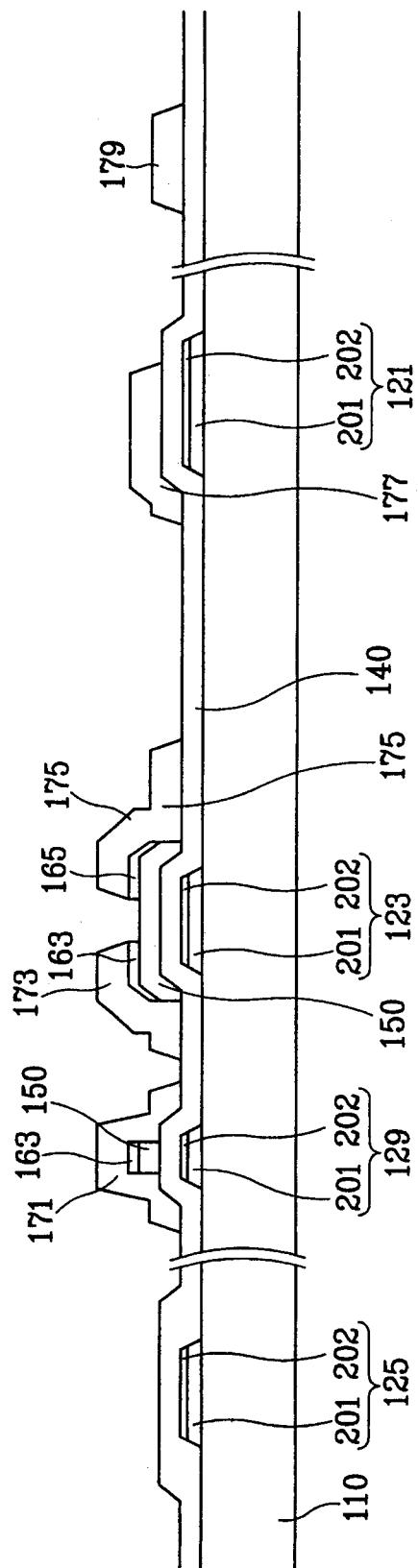

图 2 是图 1 所示的沿着 II-II' 线包括 TFT 阵列面板的液晶显示器的截面图；

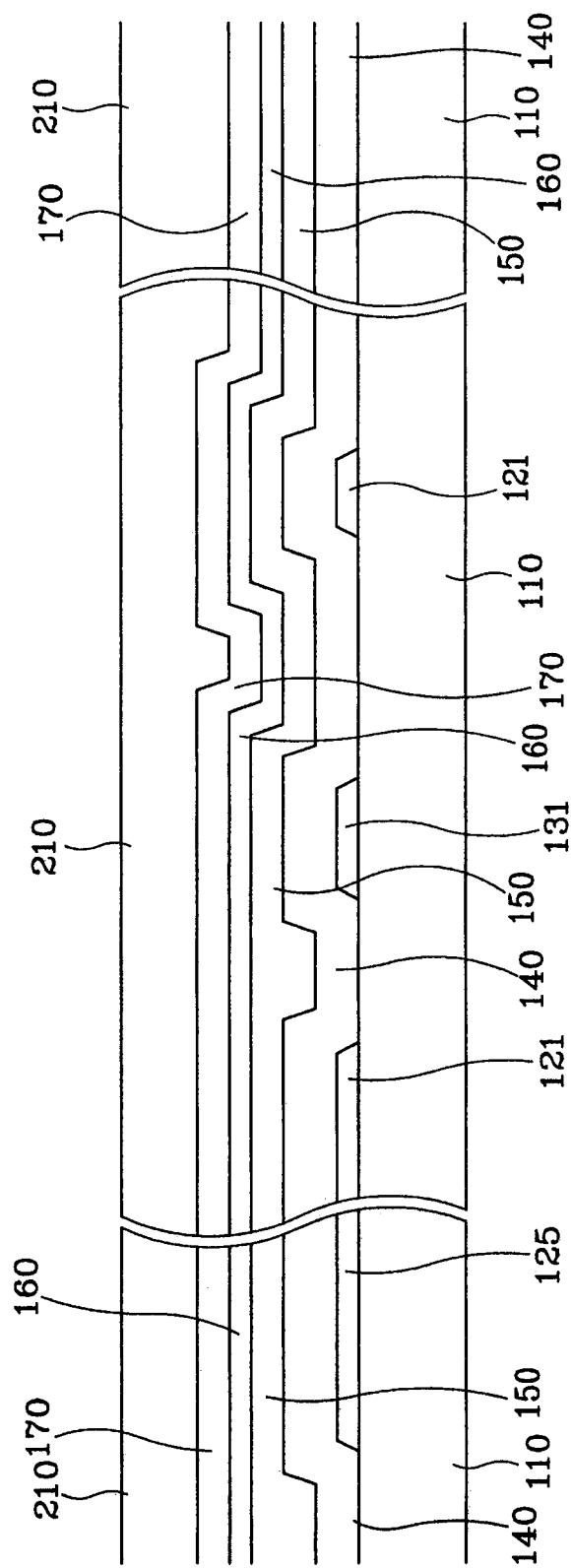

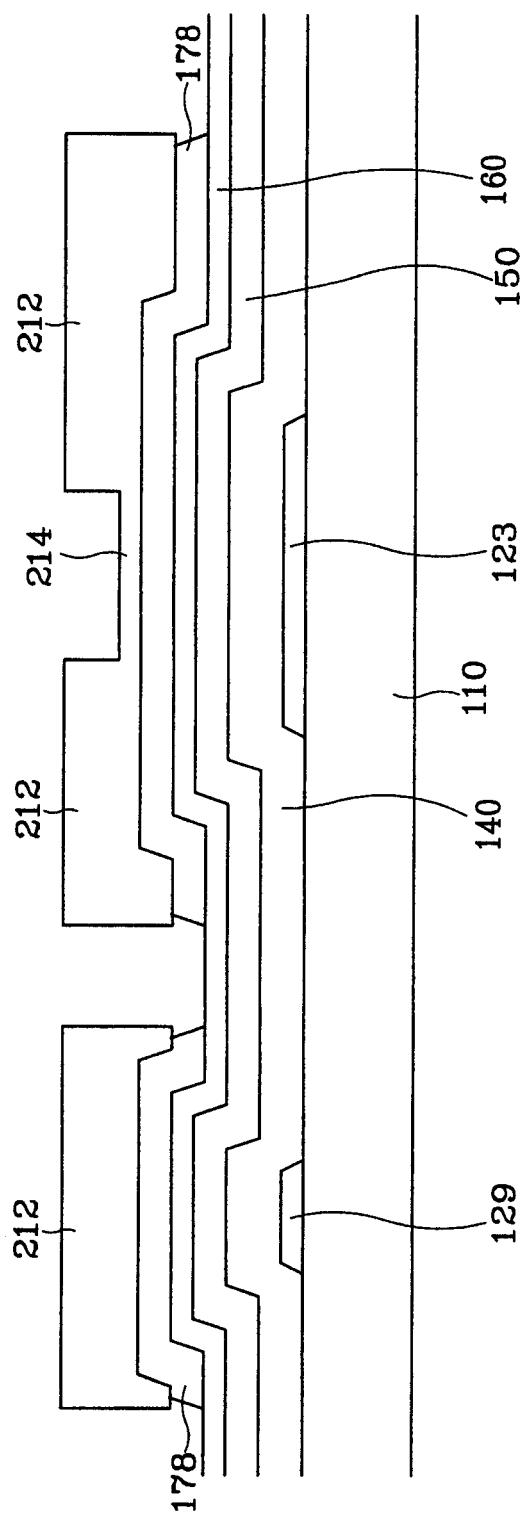

图 3A、4A、5A 及 6A 是在制造方法的步骤中根据本发明具体实施例的用于液晶显示器的 TFT 阵列面板的配置图；

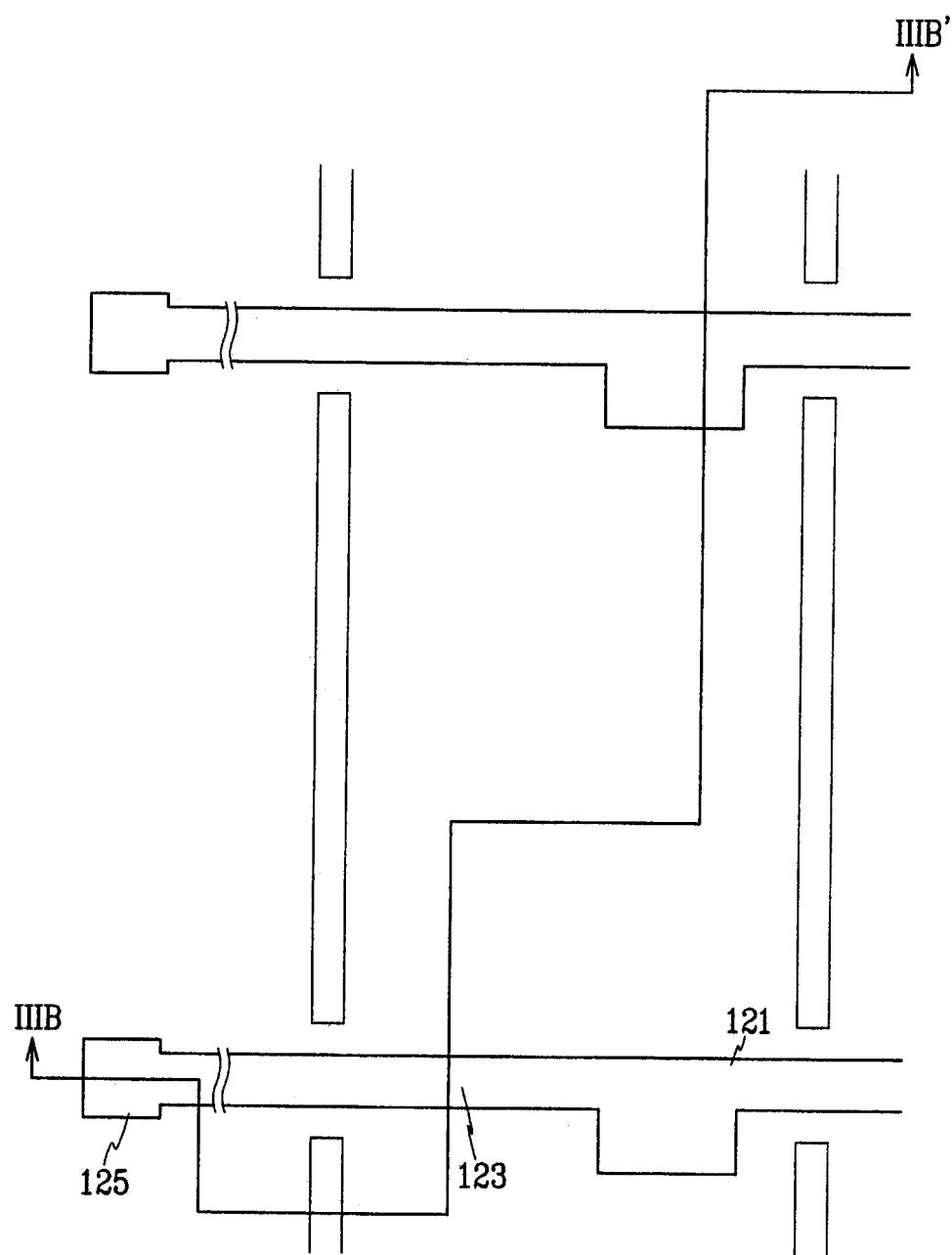

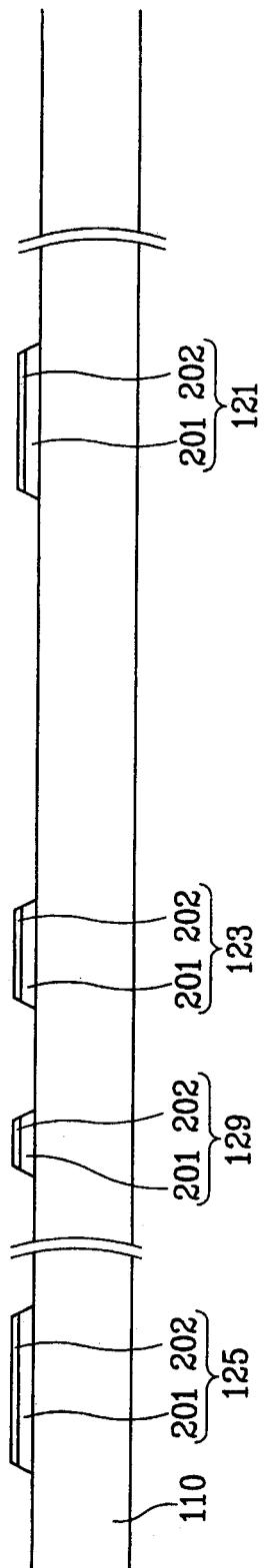

图 3B 是图 3A 所示的沿着 IIIB-IIIB' 线 TFT 阵列面板的截面图；

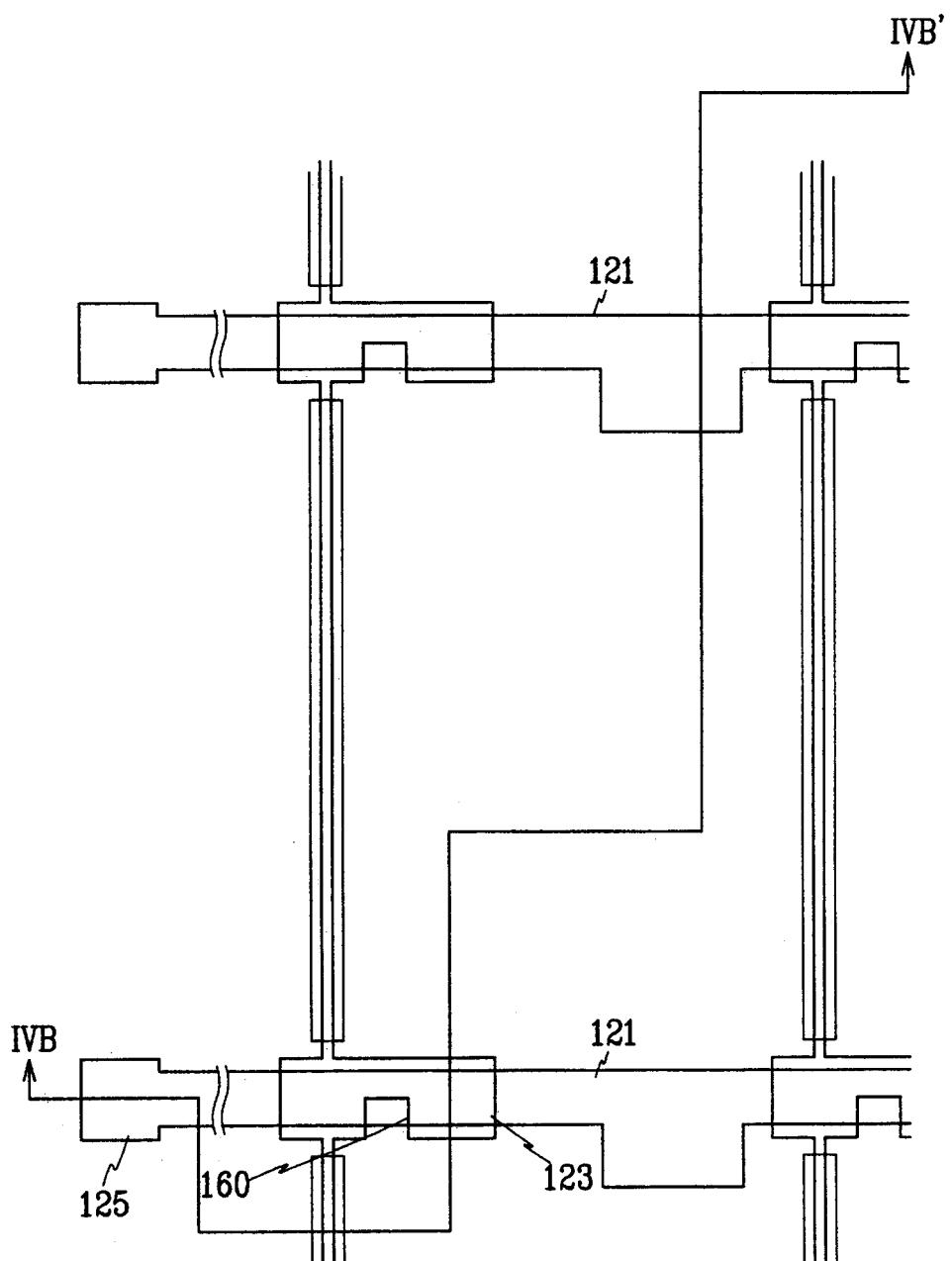

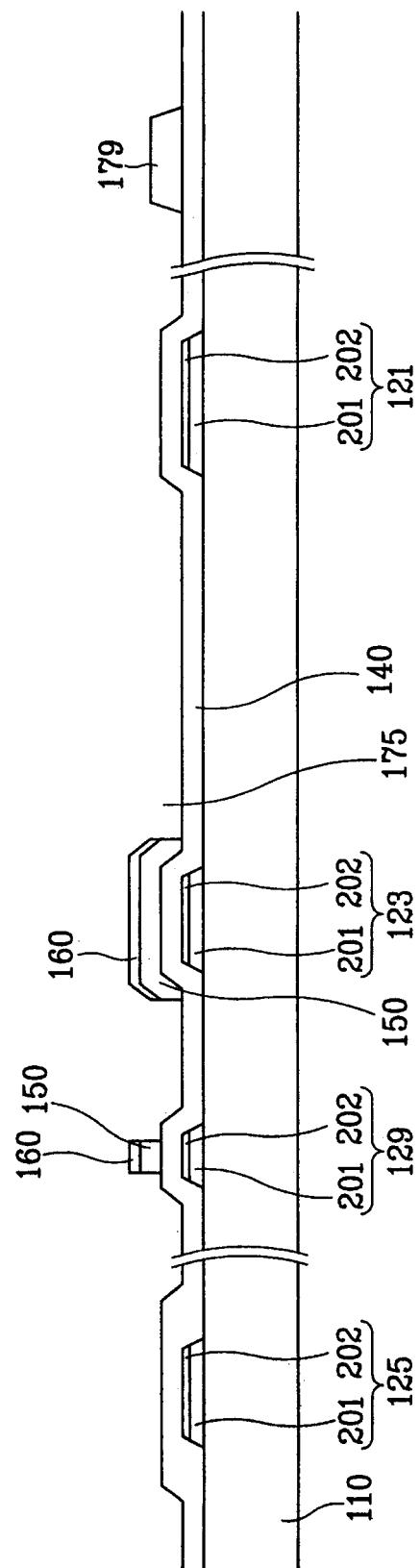

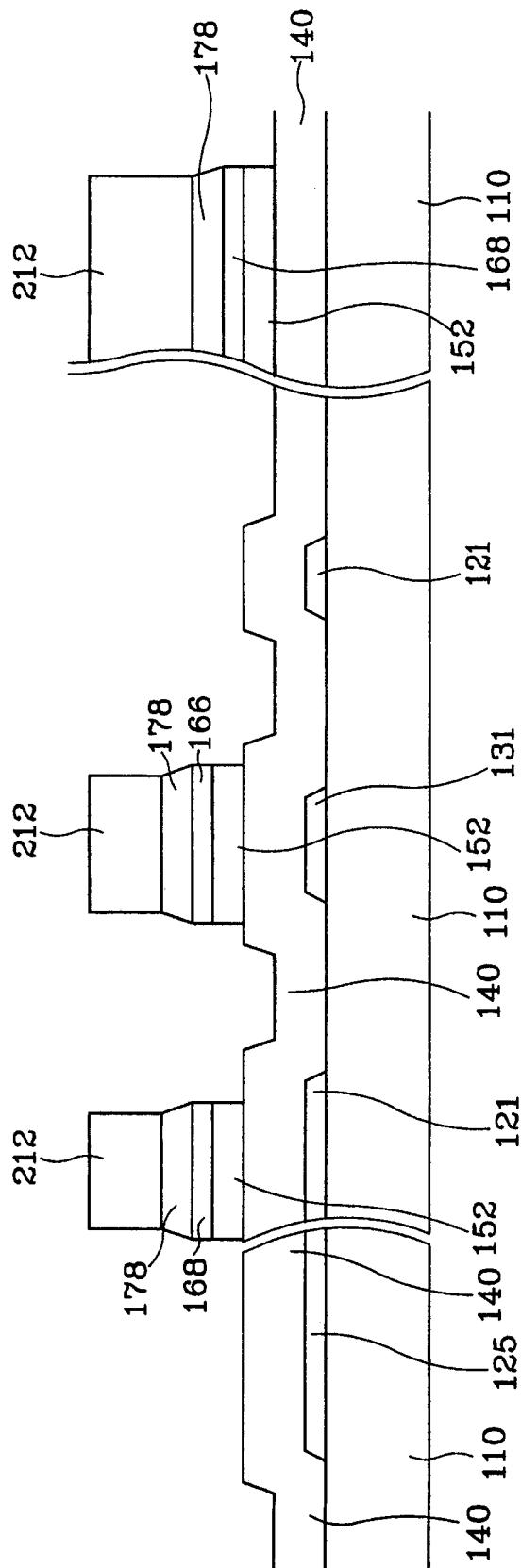

图 4B 是图 4A 所示的沿着 IVB-IVB' 线 TFT 阵列面板的截面图，其是图 3B 的下一个步骤的截面图；

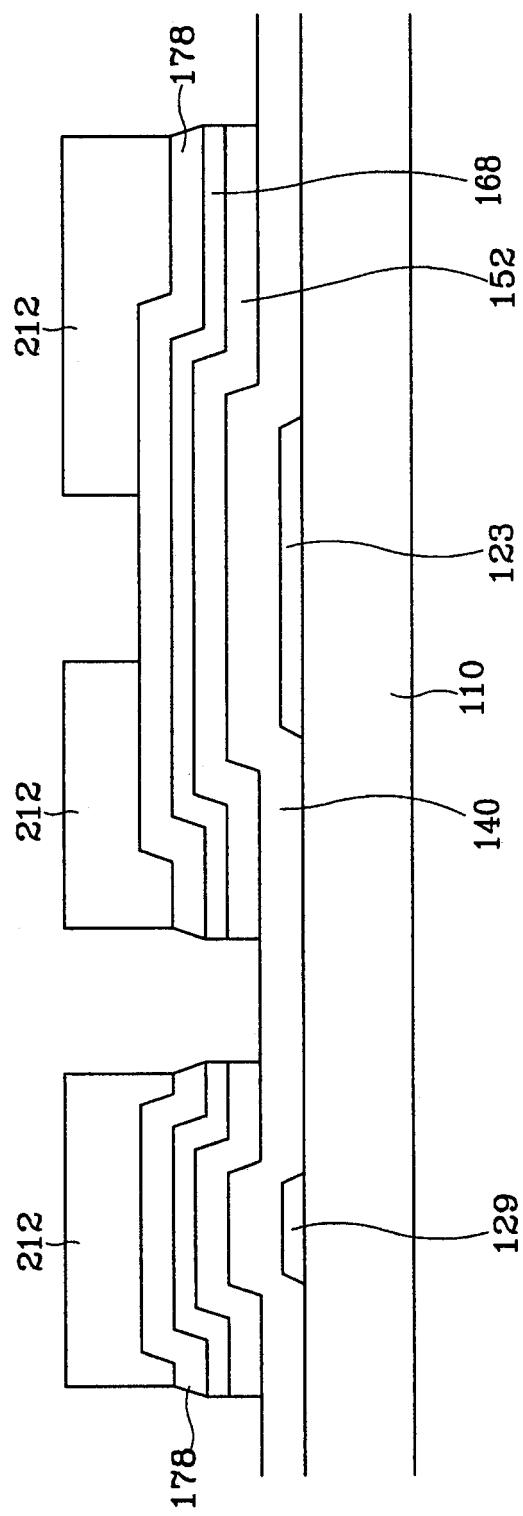

图 5B 是图 5A 所示的沿着 VB-VB' 线 TFT 阵列面板的截面图，其是图 4B 的下一个步骤的截面图；

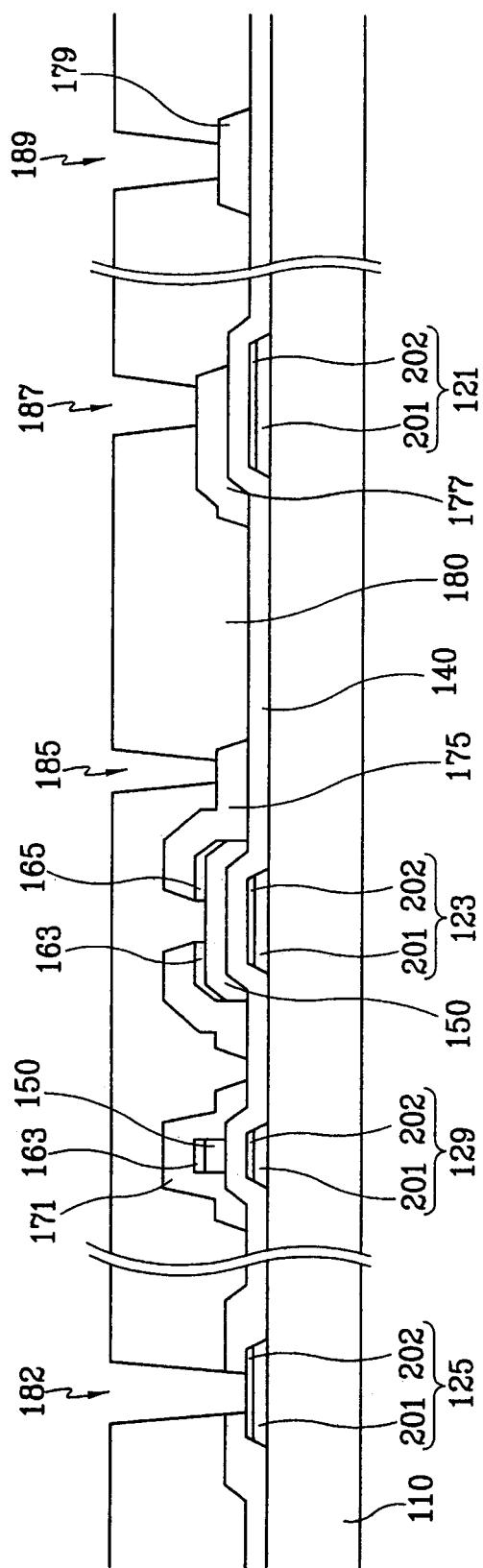

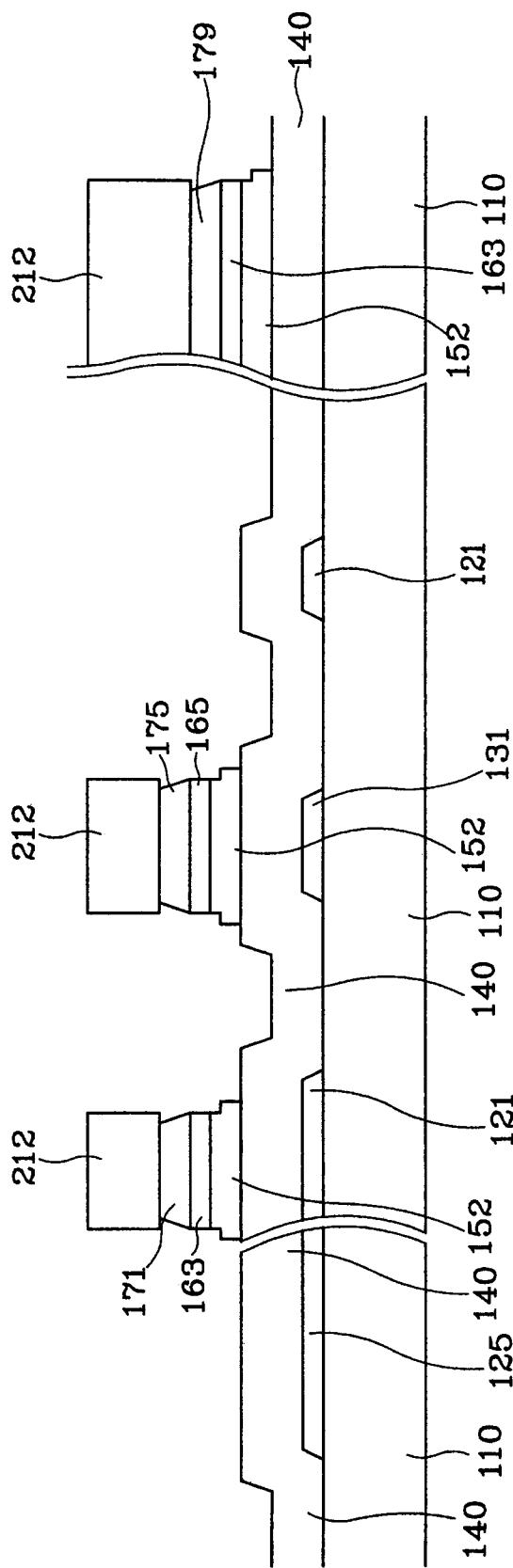

图 6B 是图 6A 所示的沿着 VIB-VIB' 线 TFT 阵列面板的截面图，其是图 5B 的下一个步骤的截面图；

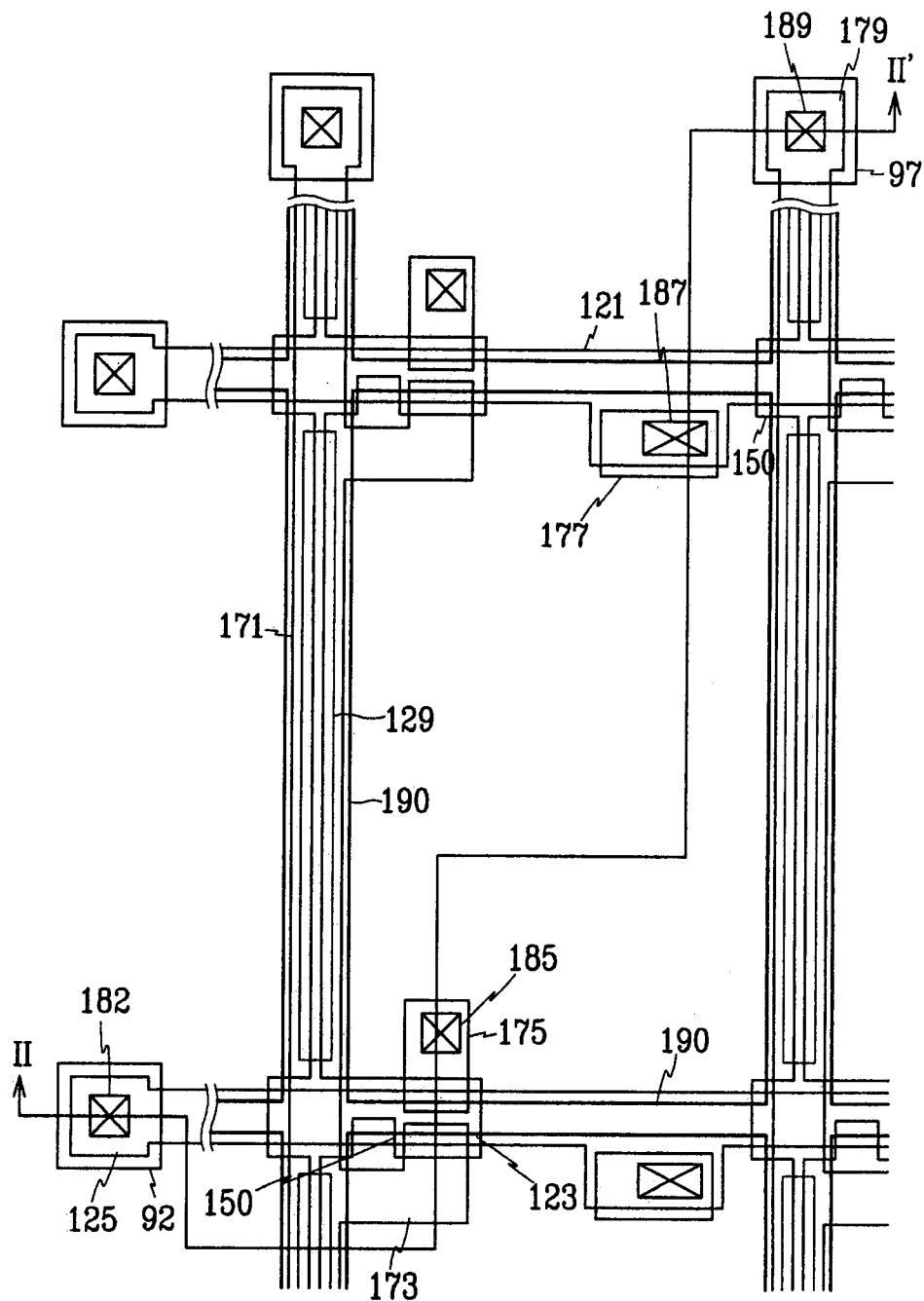

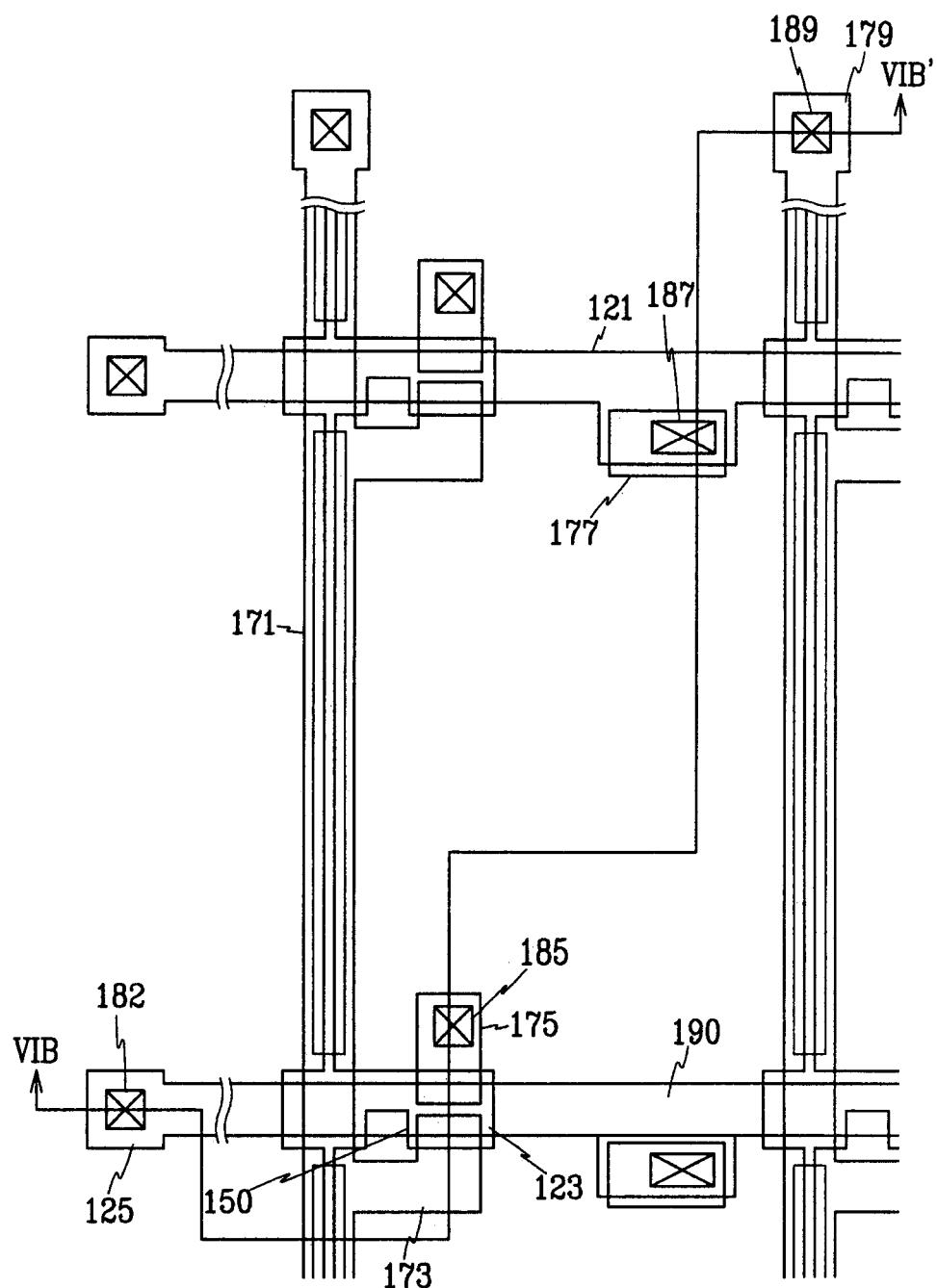

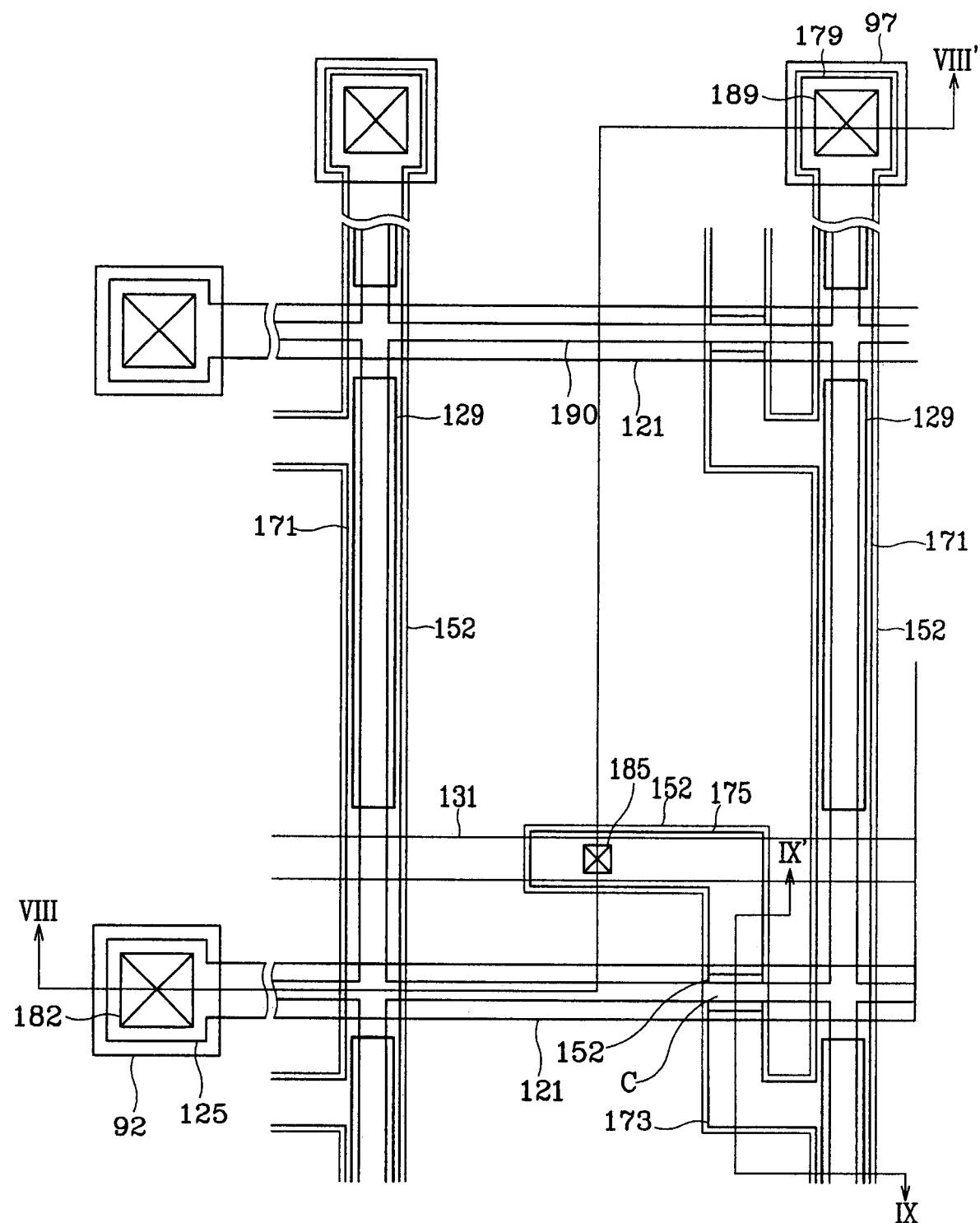

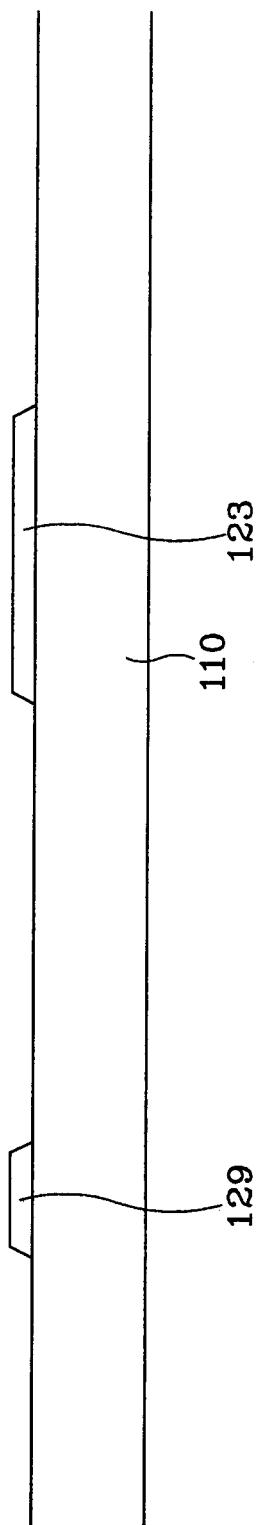

图 7 是根据本发明第二具体实施例的用于液晶显示器的 TFT 阵列面板的配置图；

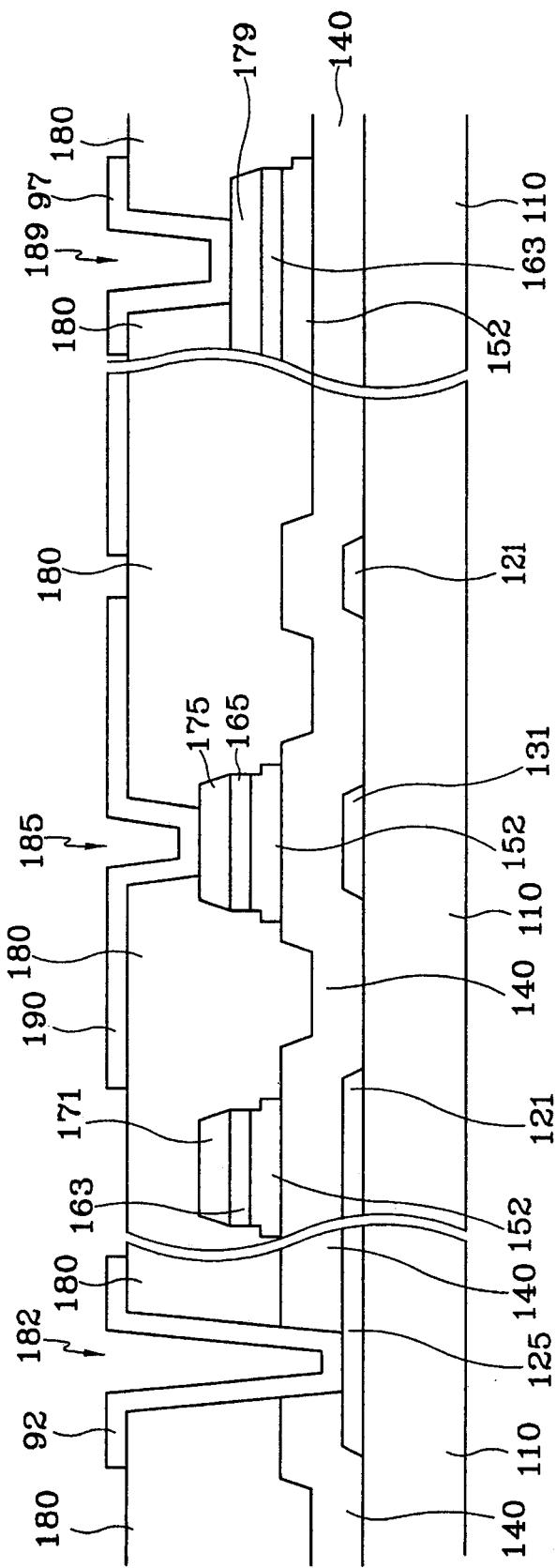

图 8 及图 9 分别是图 7 所示的沿着 VIII-VIII' 线及 IX-IX' 线 TFT 阵列面板的截面图；

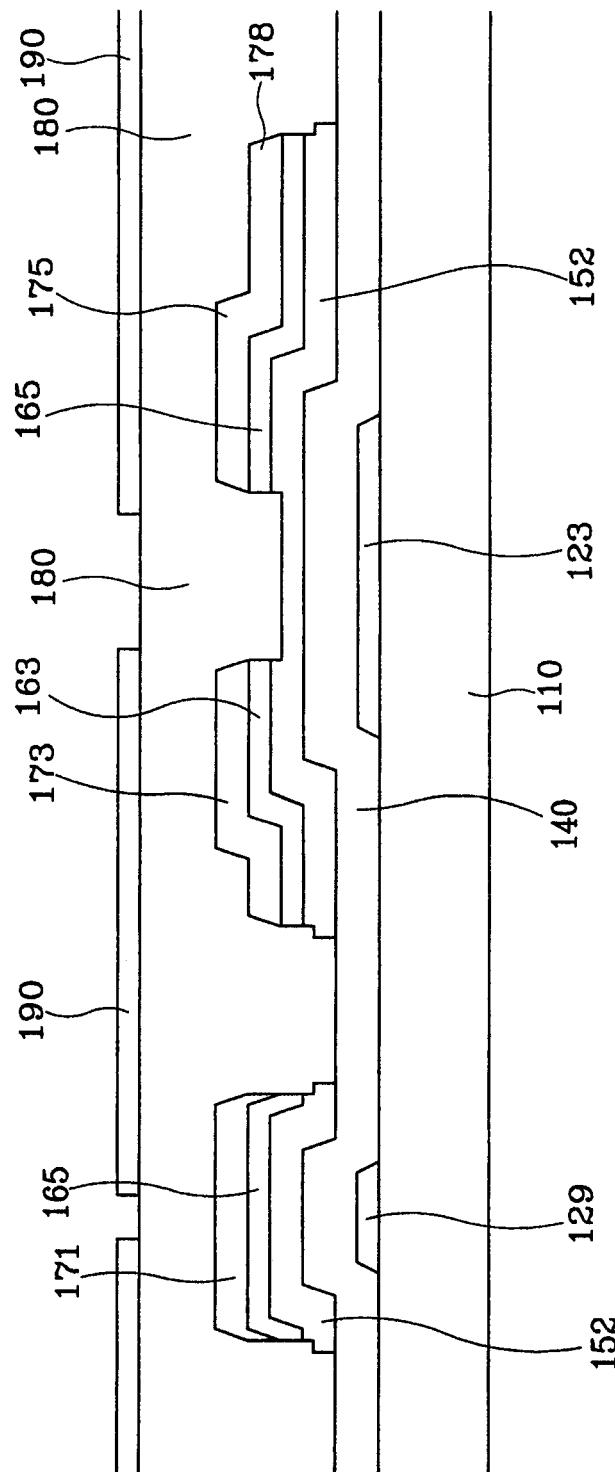

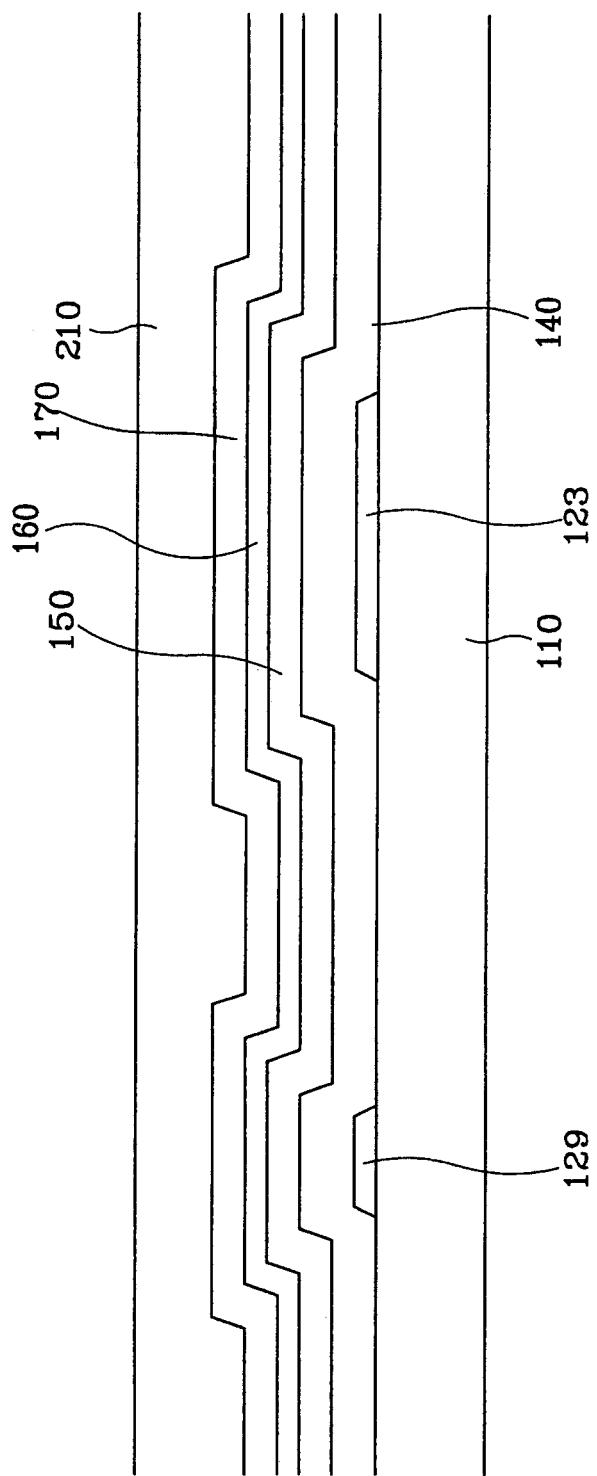

图 10A 是根据本发明第二具体实施例的制造方法的第一步骤中的用于液晶显示器的 TFT 阵列面板的配置图；

图 10B 及图 10C 是图 10A 所示的分别沿着 XB-XB' 线及 XC-XC' 线 TFT 阵列面板的截面图；

图 11A 及图 11B 是图 10A 所示的分别沿着 XB-XB' 线及 XC-XC' 线 TFT 阵列面板的截面图，其是图 10B 及图 10C 的下一个步骤的截面图；

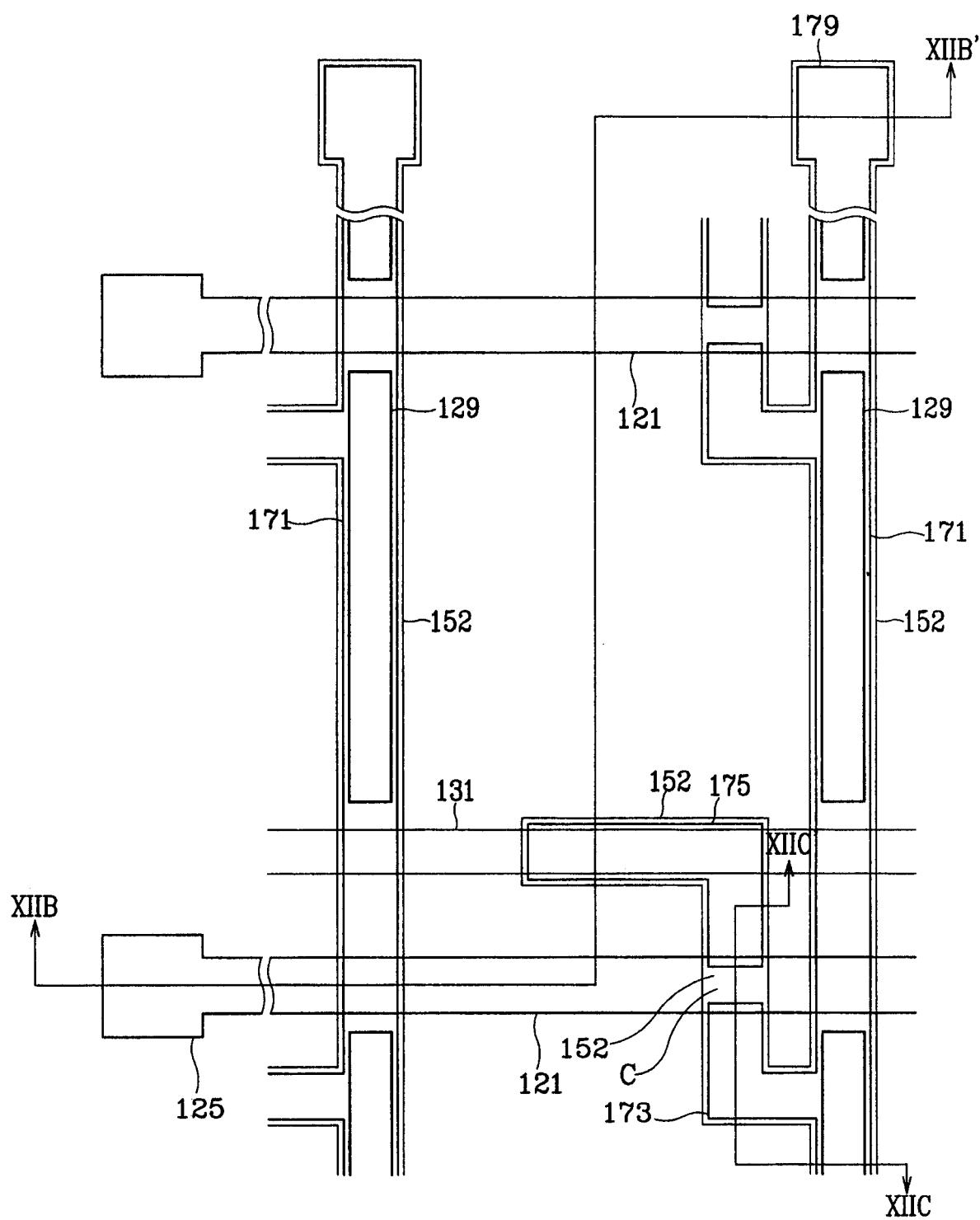

图 12A 是图 11A 及图 11B 的下一个步骤的用于液晶显示器的 TFT 阵列面板的配置图；

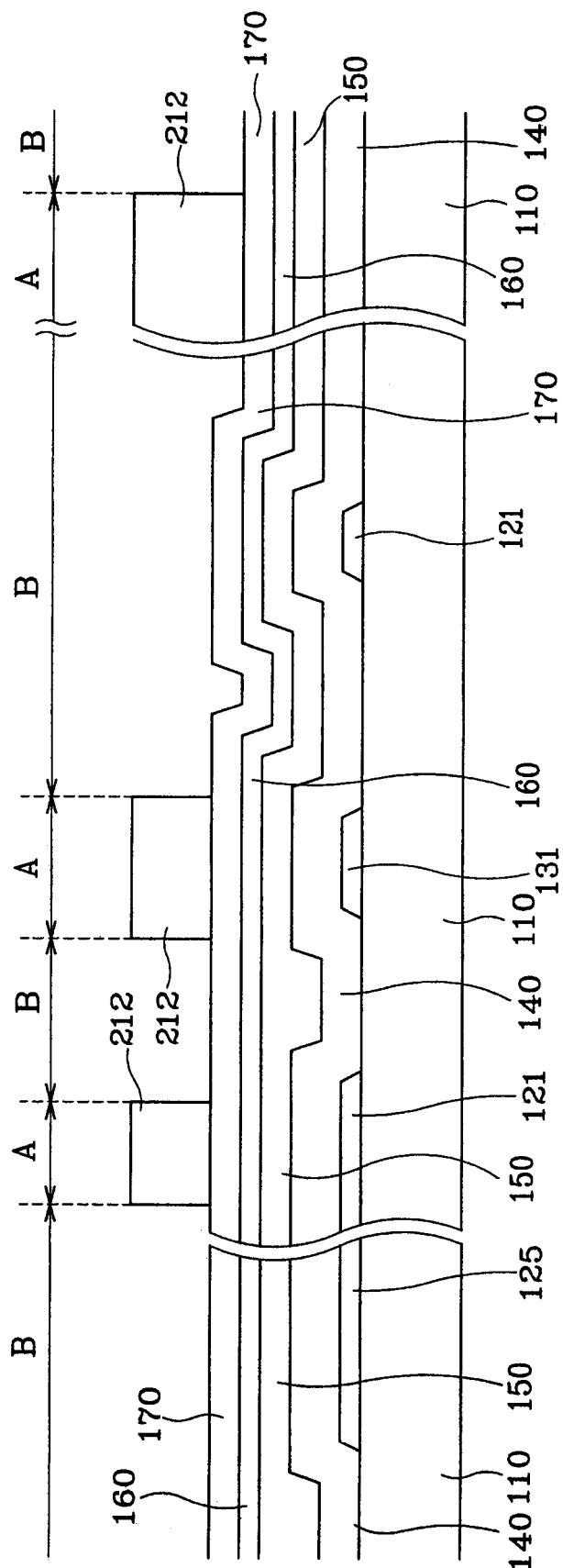

图 12B 及图 12C 是图 12A 所示的分别沿着 XIIB-XIIB' 线及 XIIC-XIIC' 线 TFT 阵列面板的截面图；

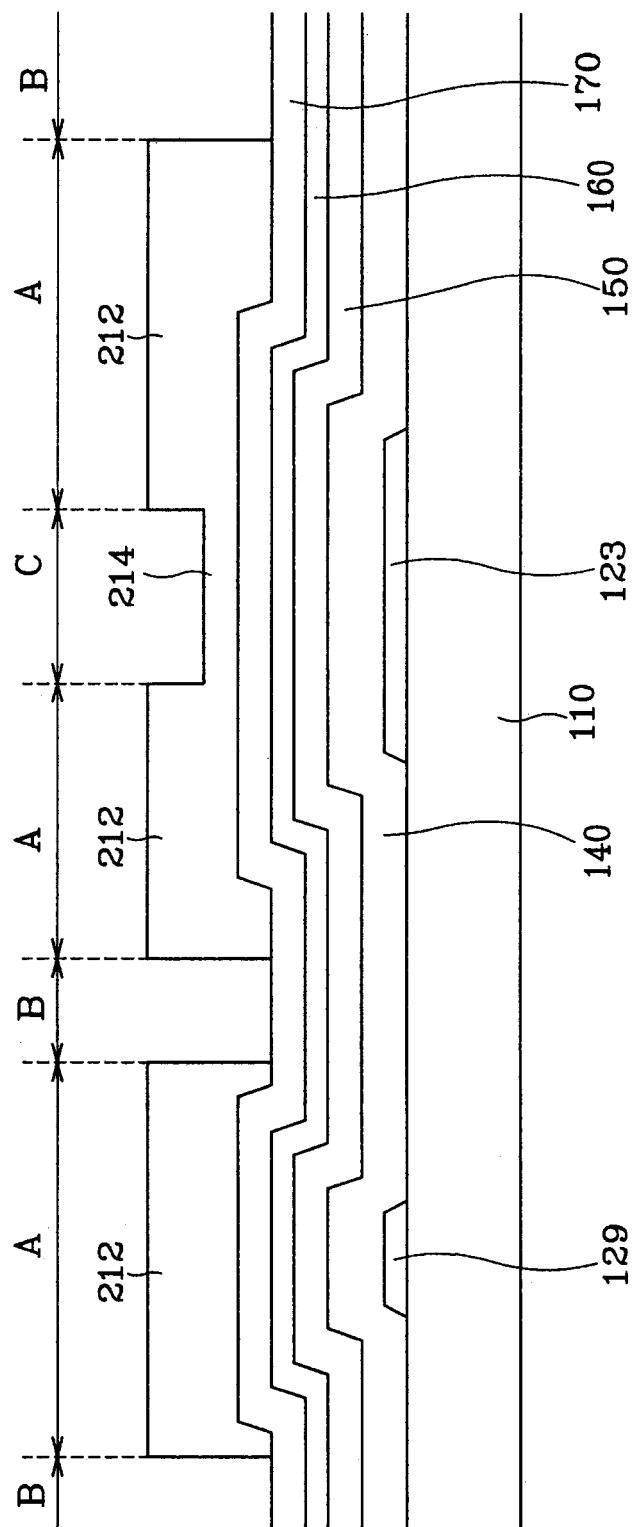

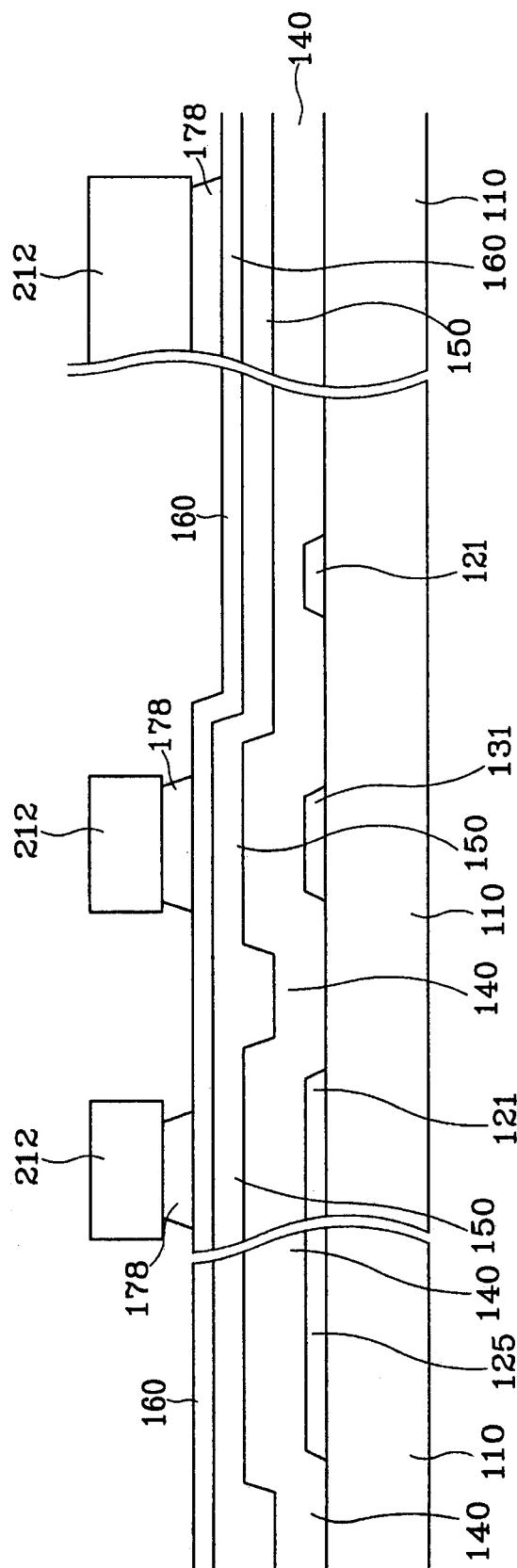

图 13A、14A、15A 和图 13B、14B、15B 是图 12A 所示的分别沿着 XIIB-XIIB' 线及 XIIC-XIIC' 线 TFT 阵列面板的截面图，其是根据制造方法的顺序图 12B 及图 12C 的下一个步骤的截面图；

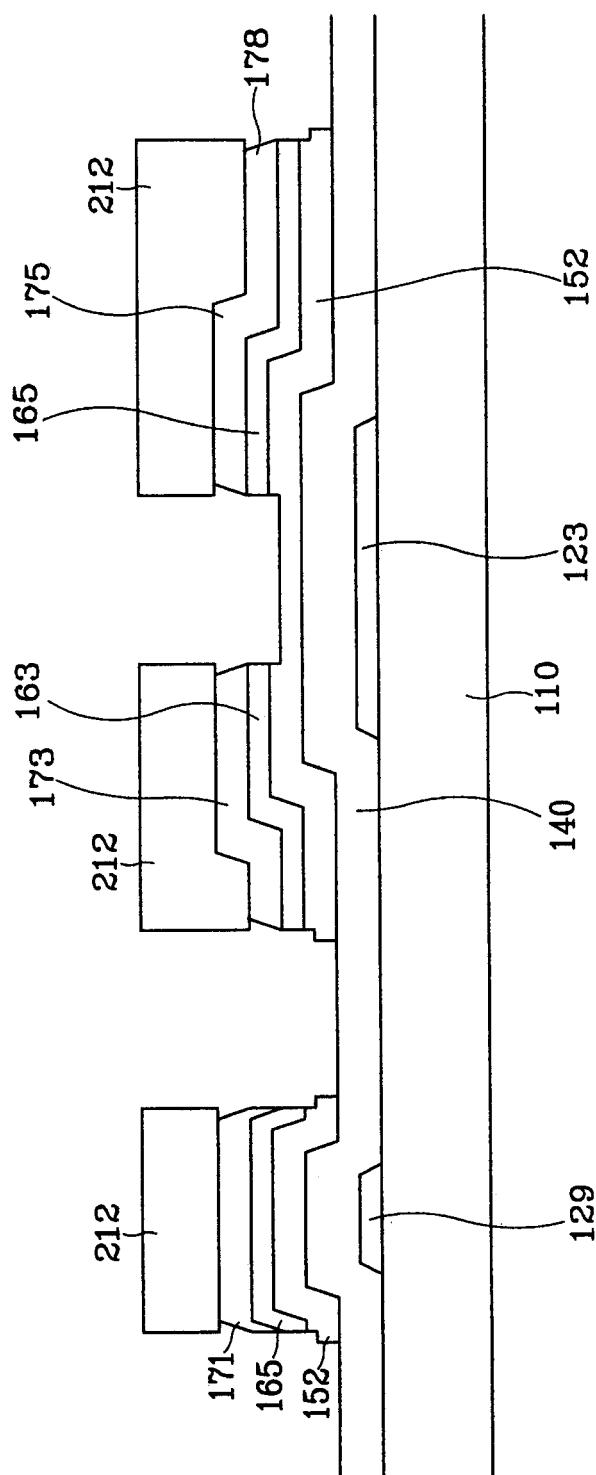

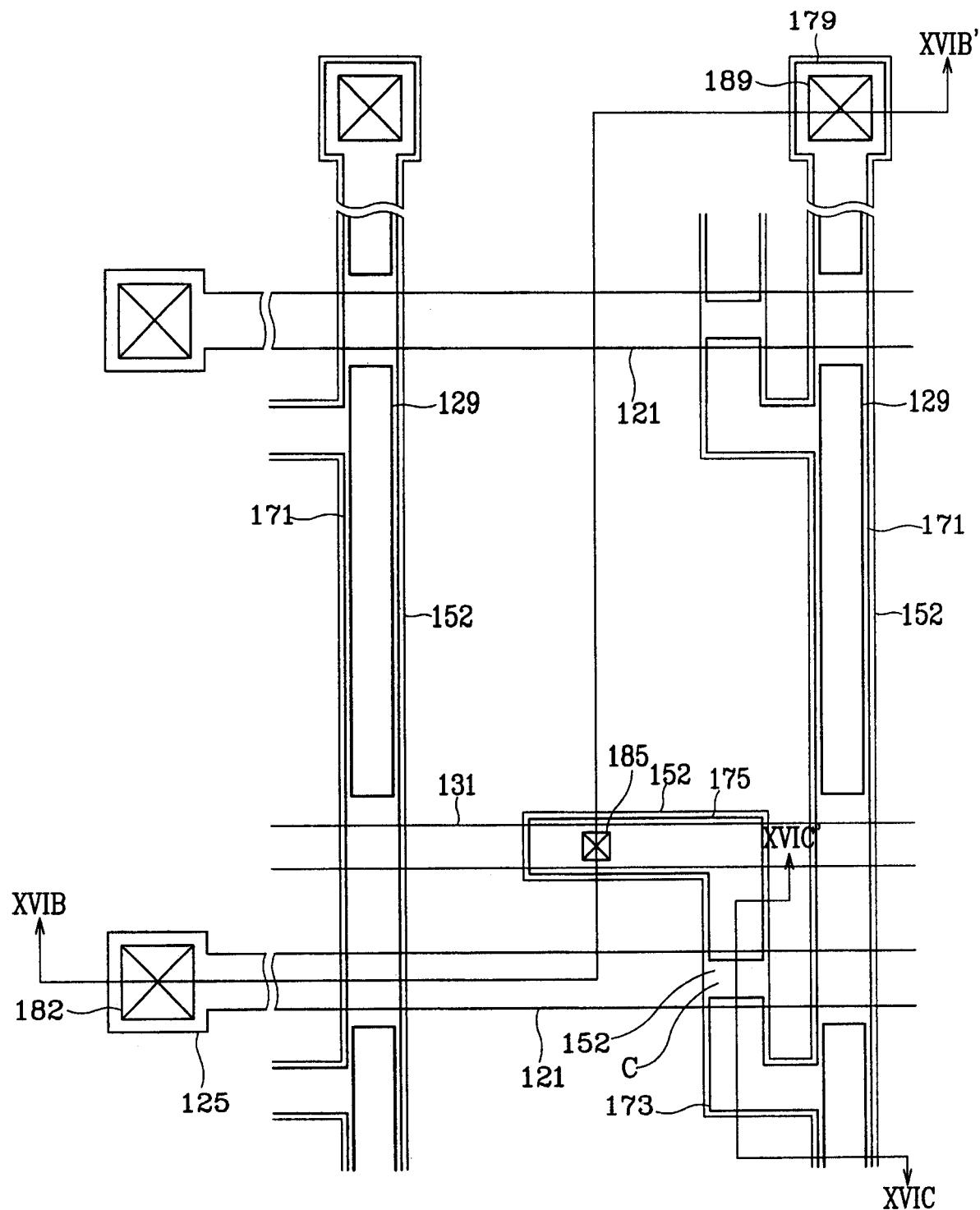

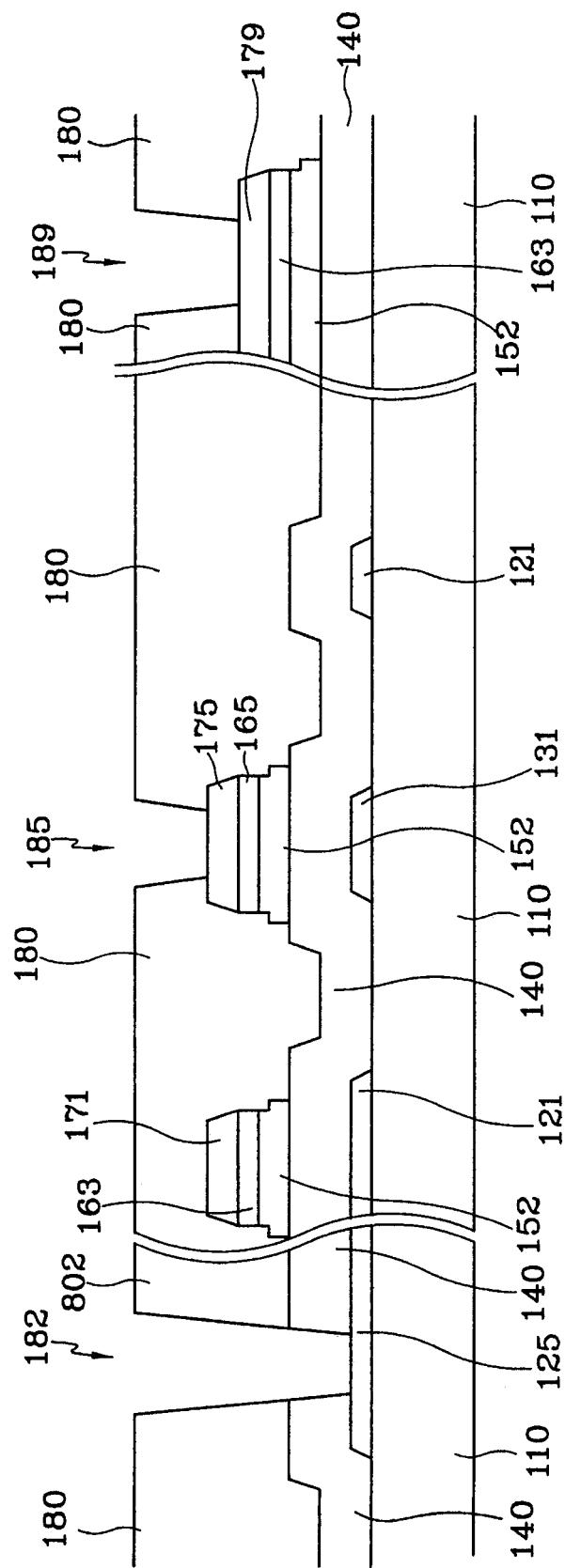

图 16A 是图 15A 及图 15B 的下一个步骤的用于液晶显示器的 TFT 阵列面板的配置图；

图 16B 及图 16C 是图 16A 所示的分别沿着 XVIB-XVIB' 线及 XVIC-XVIC' 线 TFT 阵列面板的截面图；

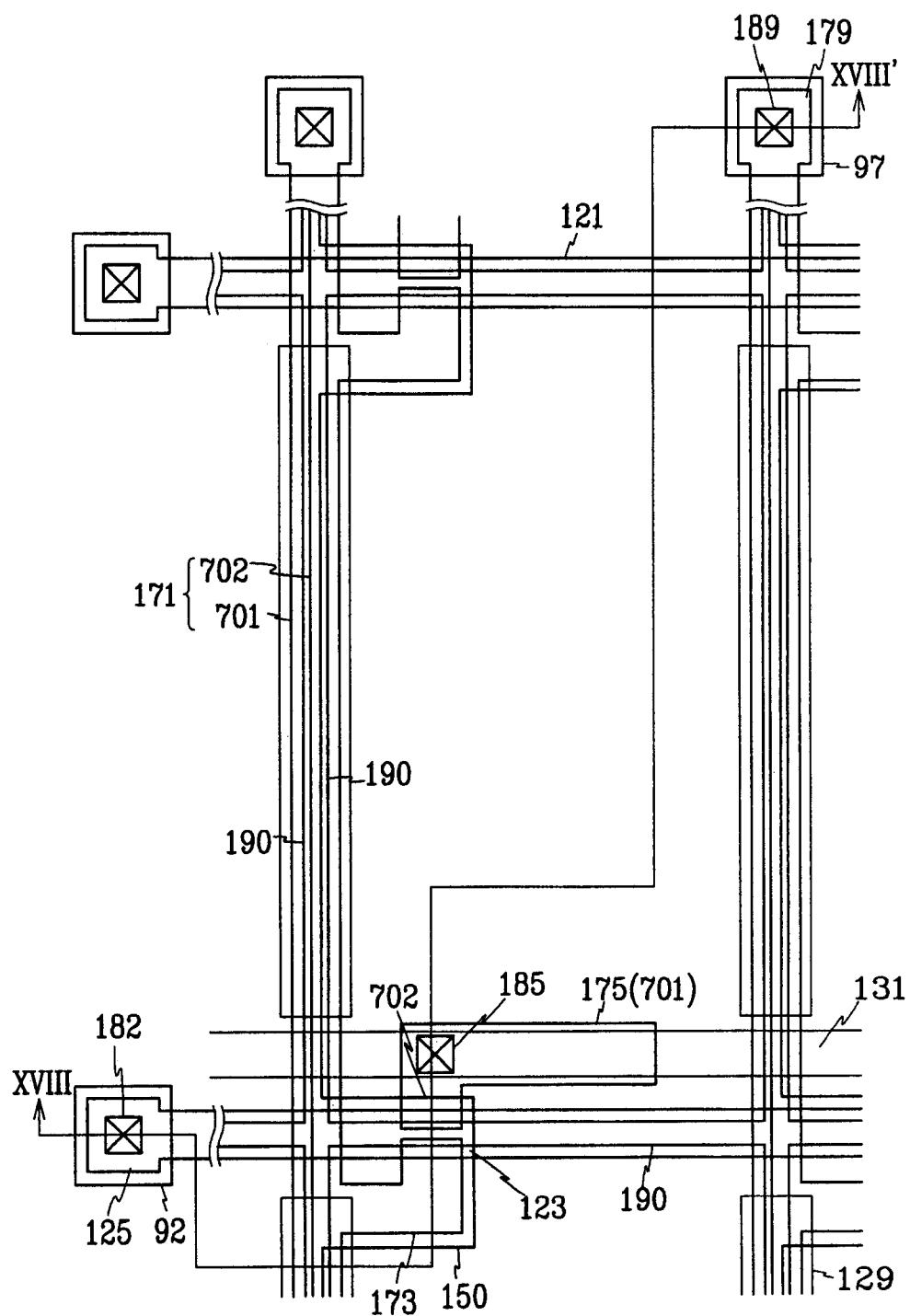

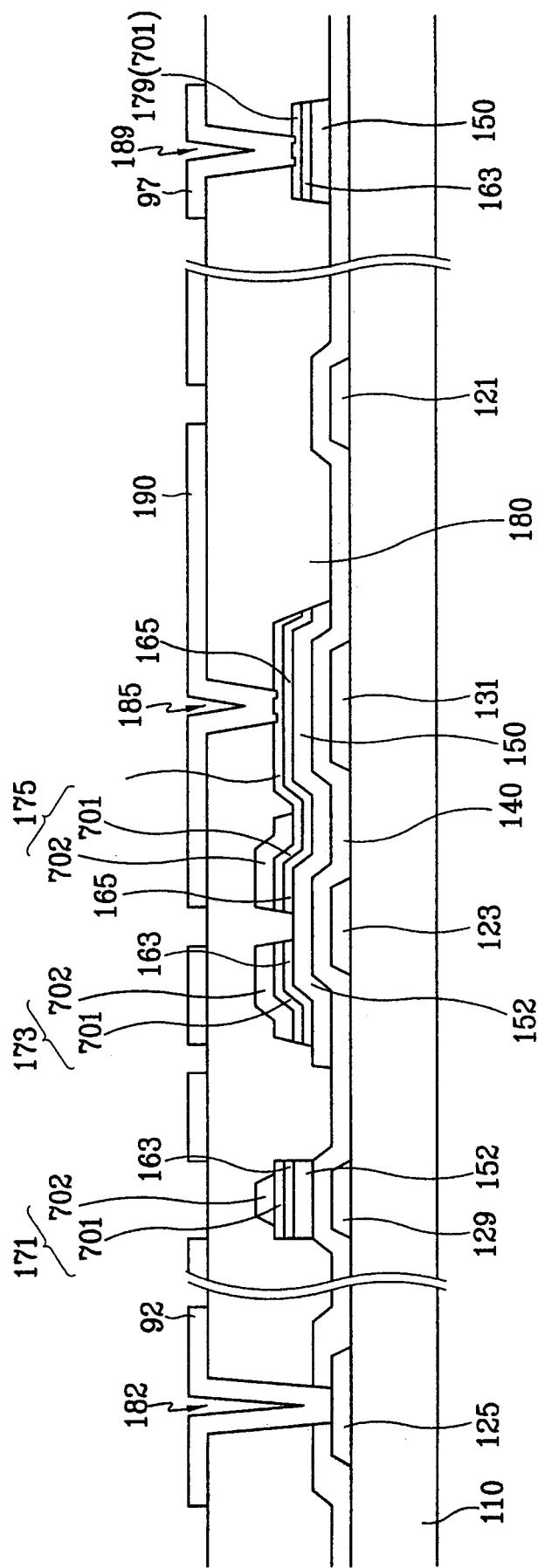

图 17 是根据本发明第三具体实施例的用于液晶显示器的 TFT 阵列面板的配置图；

图 18 是图 17 所示的沿着 XVIII-XVIII' 线 TFT 阵列面板的截面图；

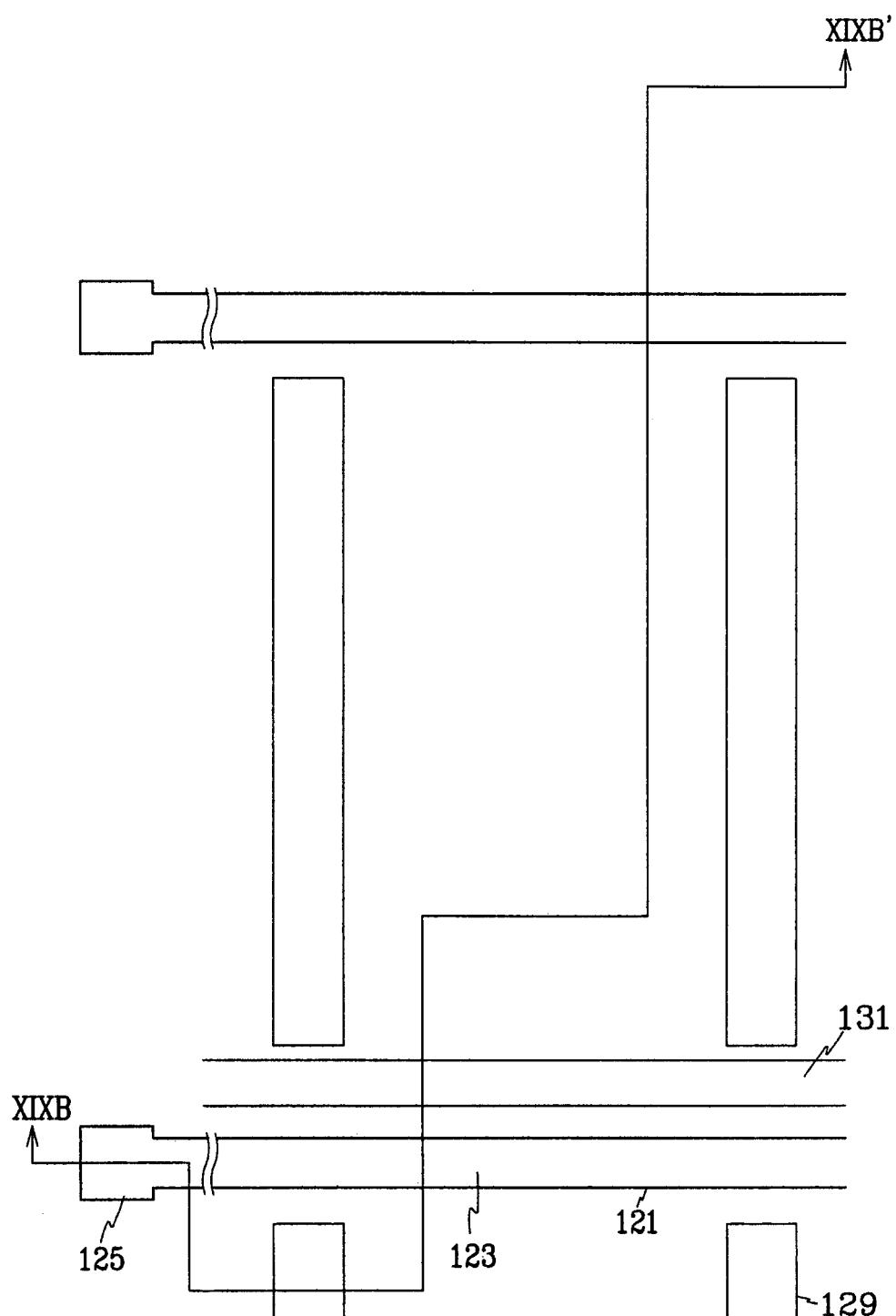

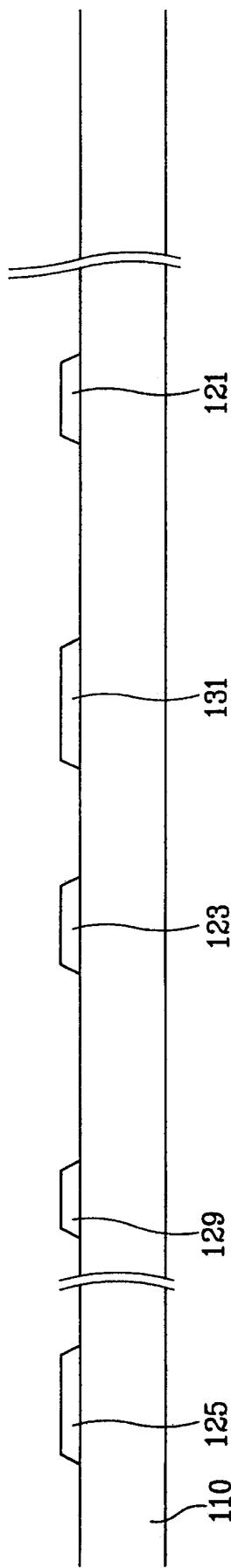

图 19A、20A、21A 及 23A 是在制造方法的步骤中根据本发明第三具体实施例的 TFT 阵列面板的配置图；

图 19B 是图 19A 所示的沿着 XIXB-XIXB' 线 TFT 阵列面板的截面图；

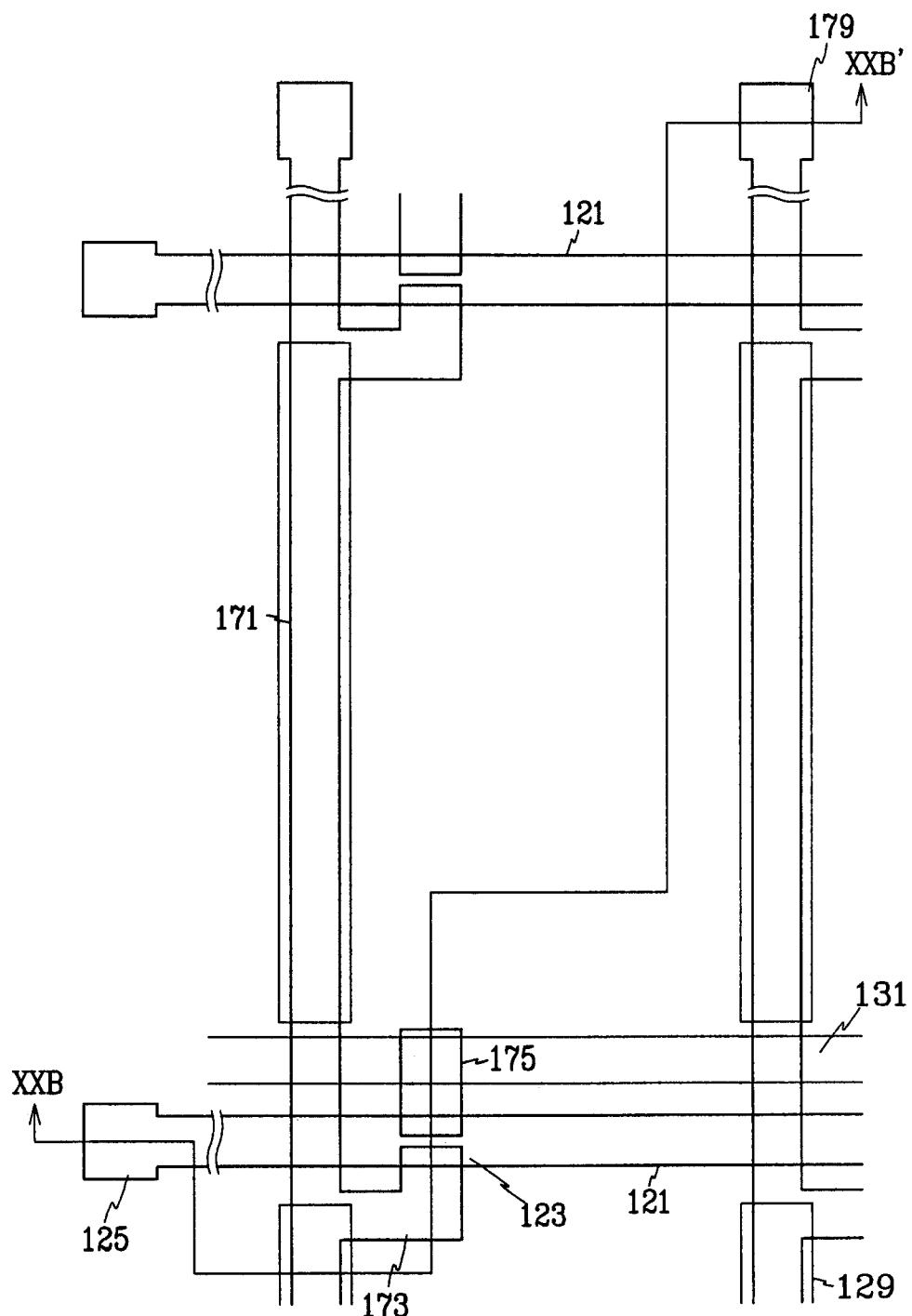

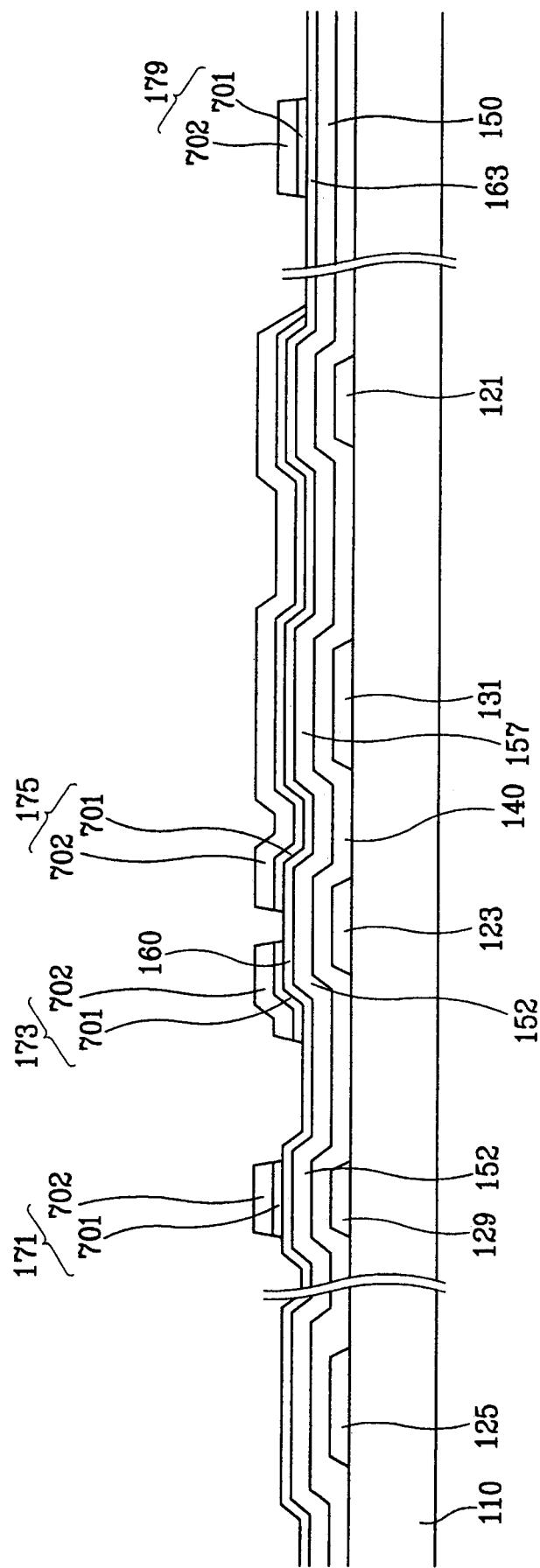

图 20B 是图 20A 所示的沿着 XXB-XXB' 线 TFT 阵列面板的截面图，其是图 19B 的下一个步骤的截面图；

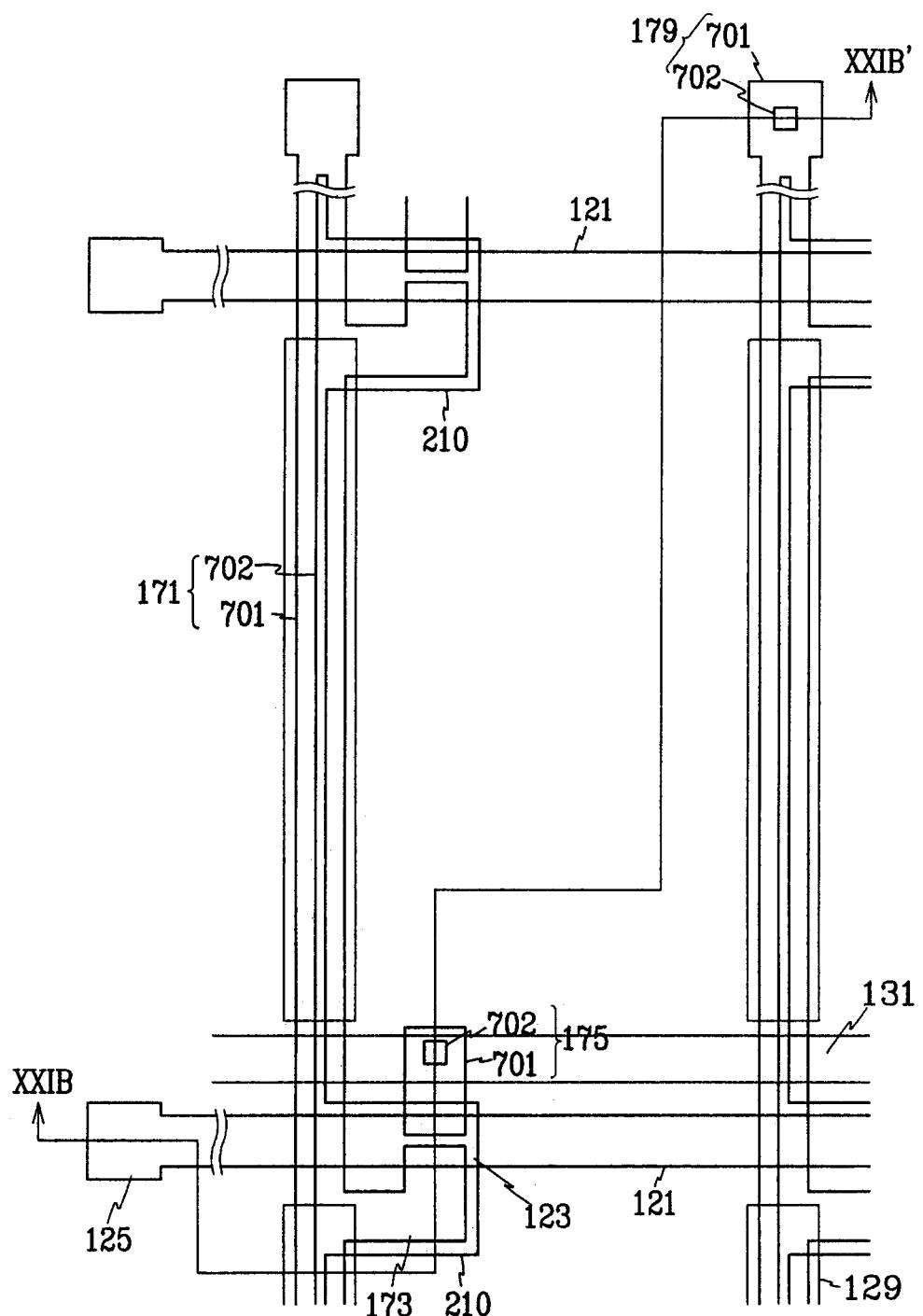

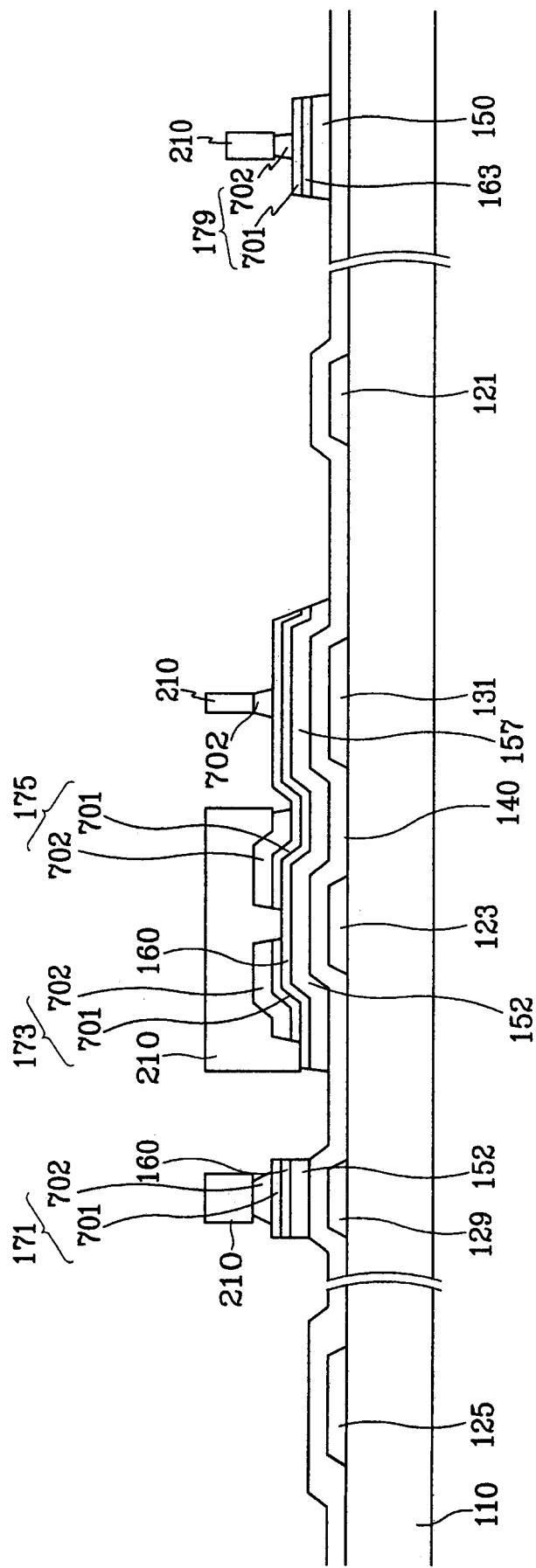

图 21B 是图 21A 所示的沿着 XXIB-XXIB' 线 TFT 阵列面板的截面图，其是图 20B 的下一个步骤的截面图；

图 22 是图 21A 所示的沿着 XXIB-XXIB' 线 TFT 阵列面板的截面图，其是图 21B 的下一个步骤的截面图；

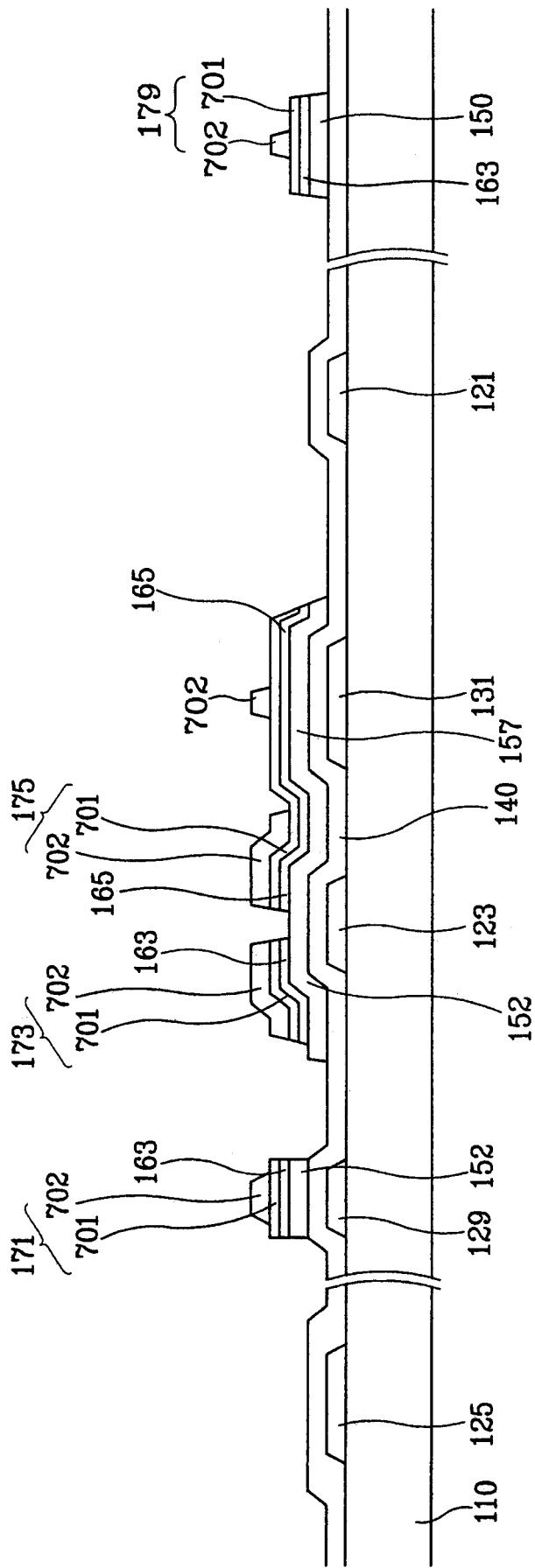

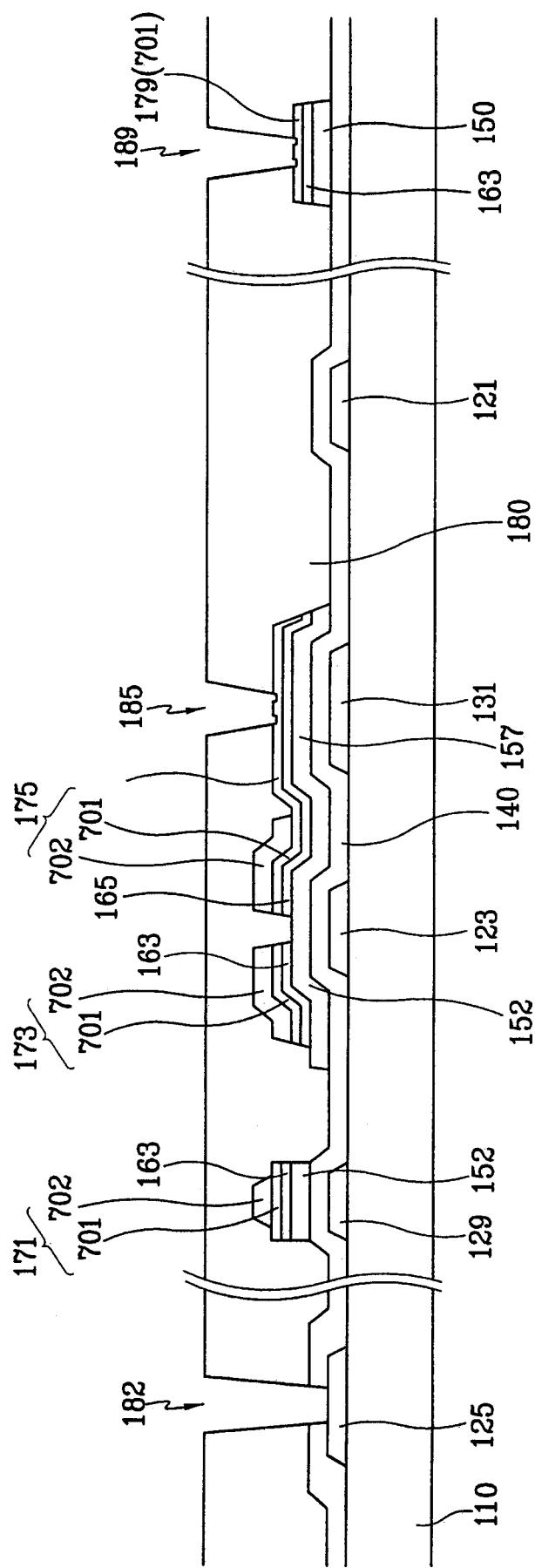

图 23B 是图 23A 所示的沿着 XXIIIB-XXIIIB' 线 TFT 阵列面板的截面图，其是图 22 的下一个步骤的截面图；

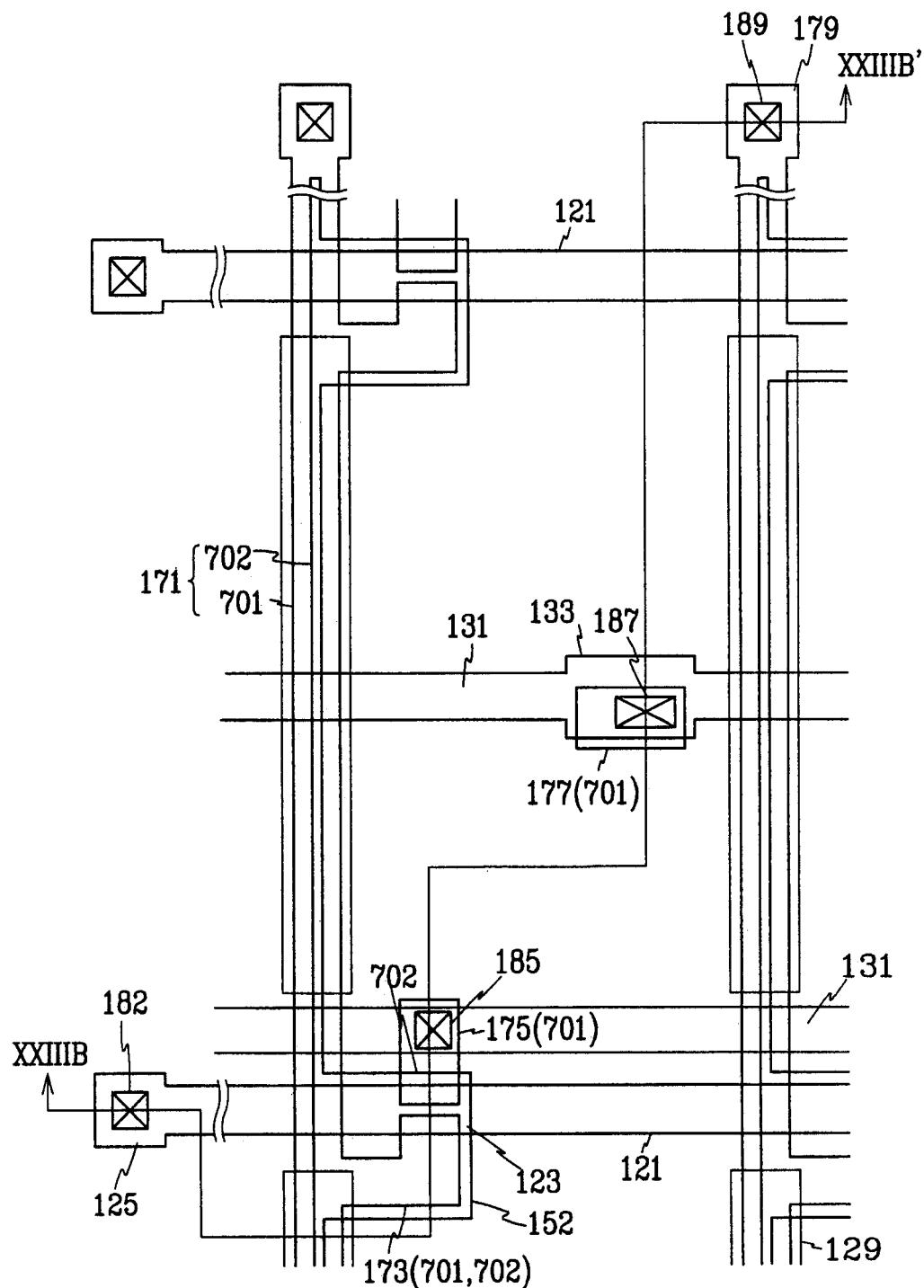

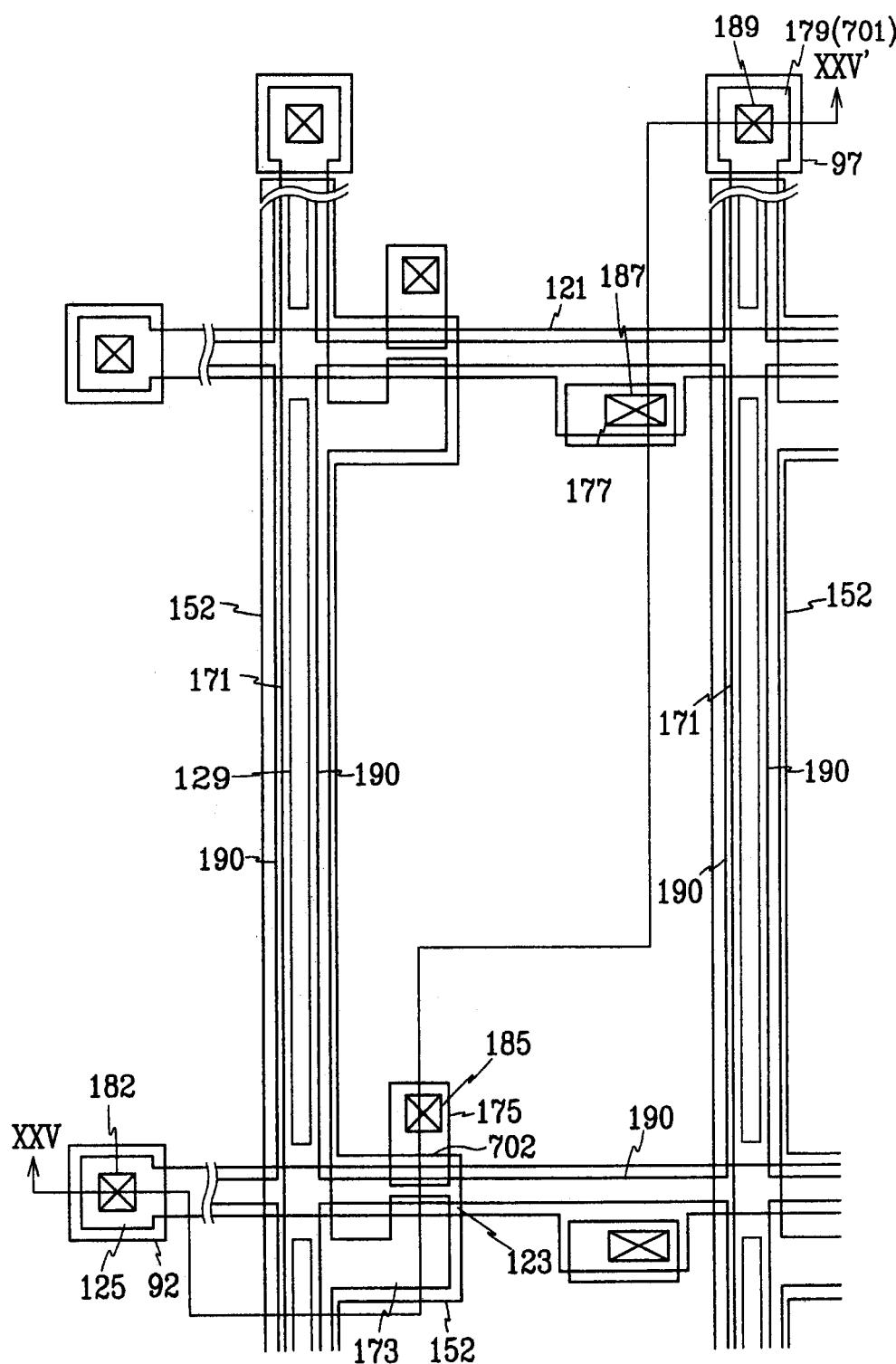

图 24 是根据本发明第四具体实施例的用于液晶显示器的 TFT 阵列面板的配置图；

图 25 是图 24 所示的沿着 XXV-XXV' 线 TFT 阵列面板的截面图；

图 26 是根据本发明第五具体实施例的用于液晶显示器的 TFT 阵列面板的配置图；

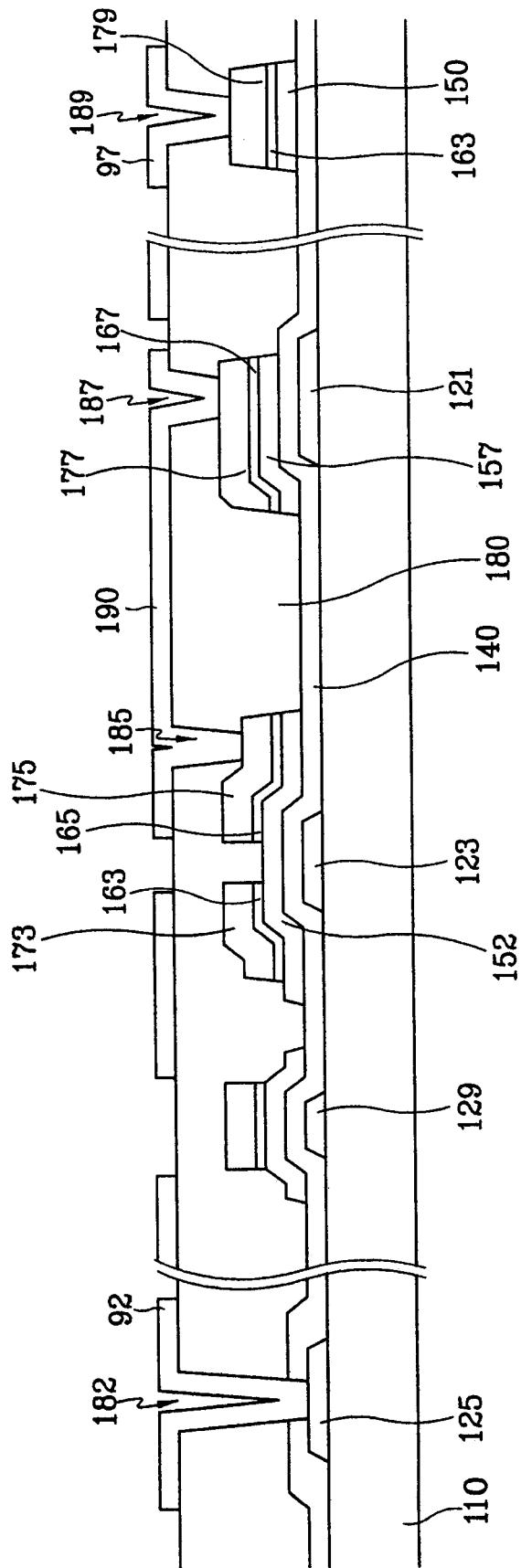

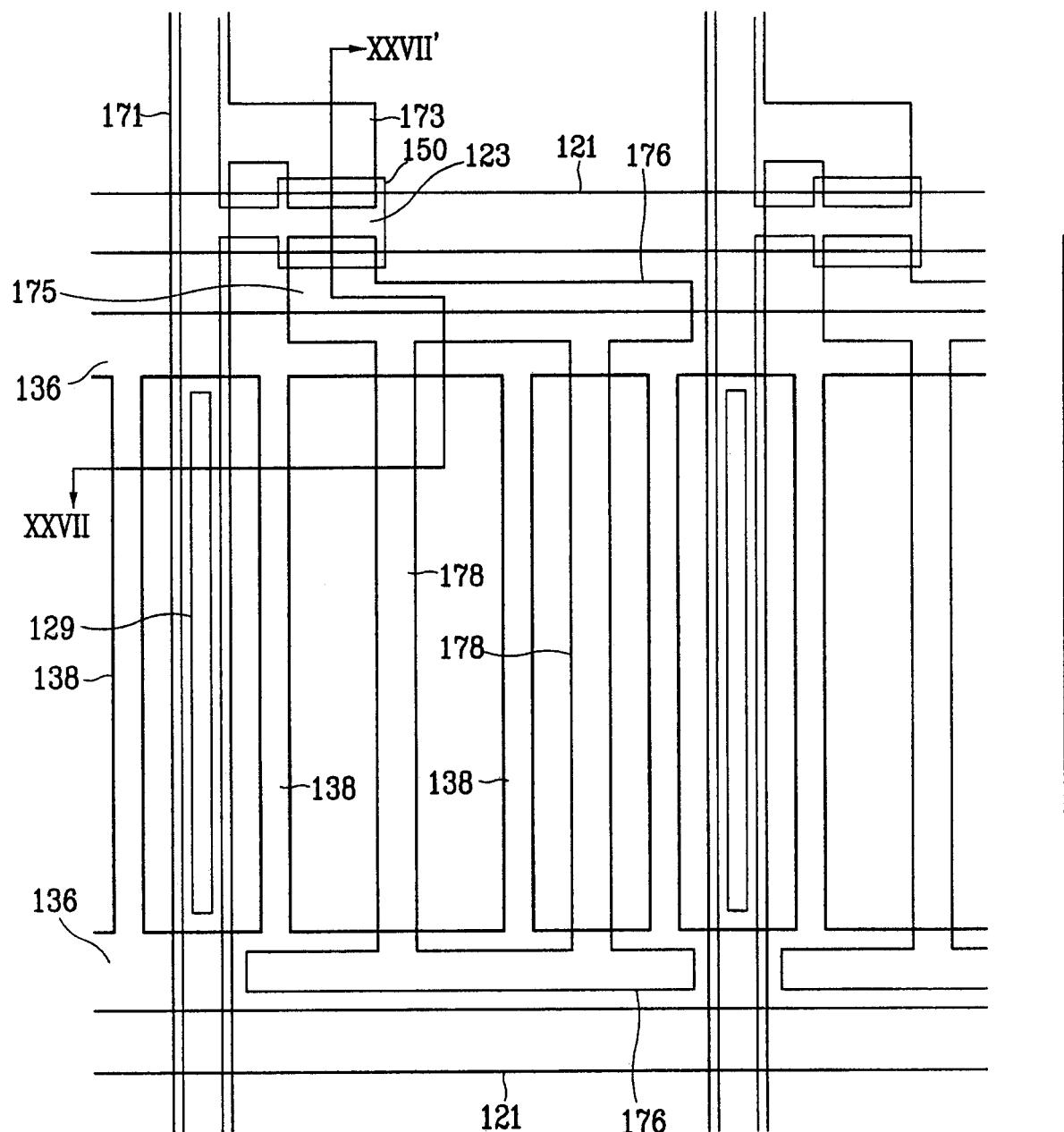

图 27 是图 26 所示的沿着 XXVII-XXVII' 线 TFT 阵列面板的截面图；

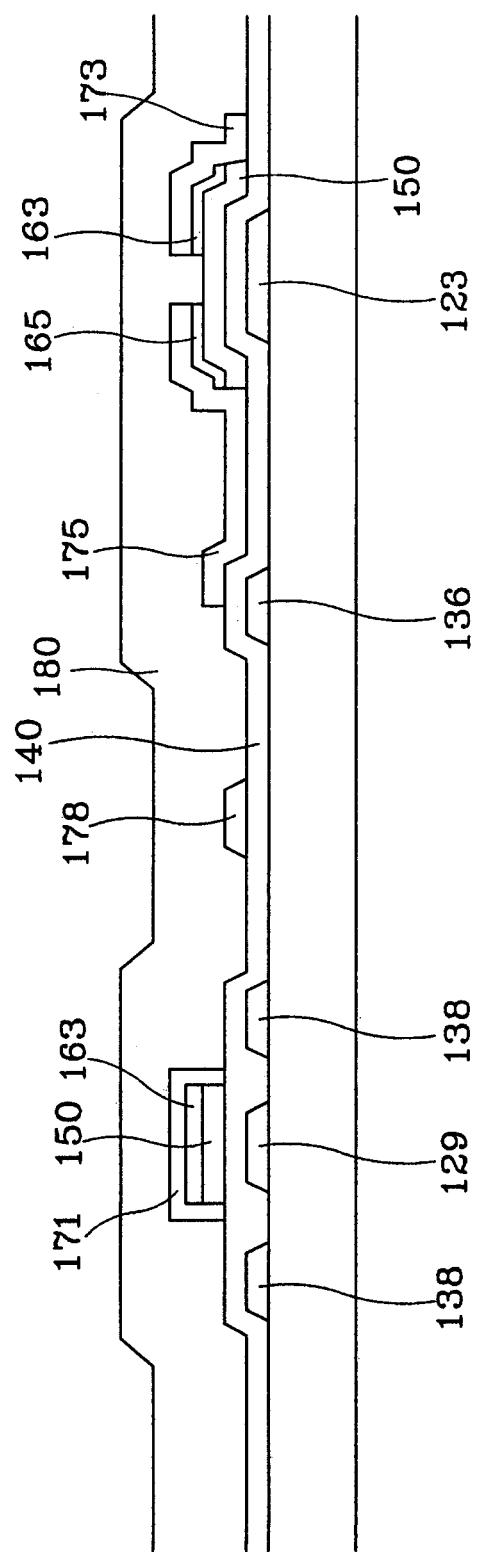

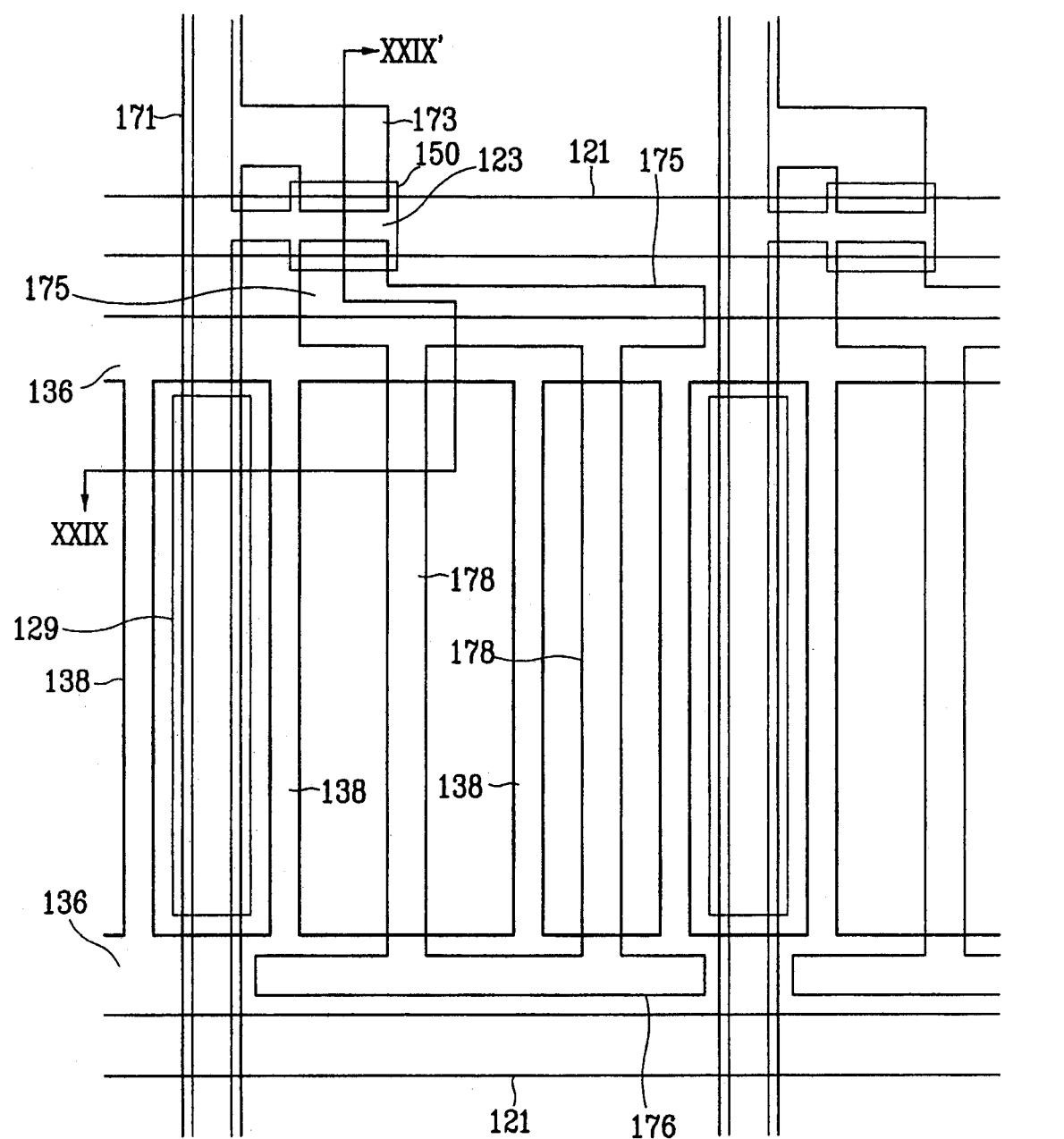

图 28 是根据本发明的第六具体实施例的用于液晶显示器的 TFT 阵列面板的配置图；

图 29 是图 28 所示的沿着 XXIX-XXIX' 线 TFT 阵列面板的截面图；

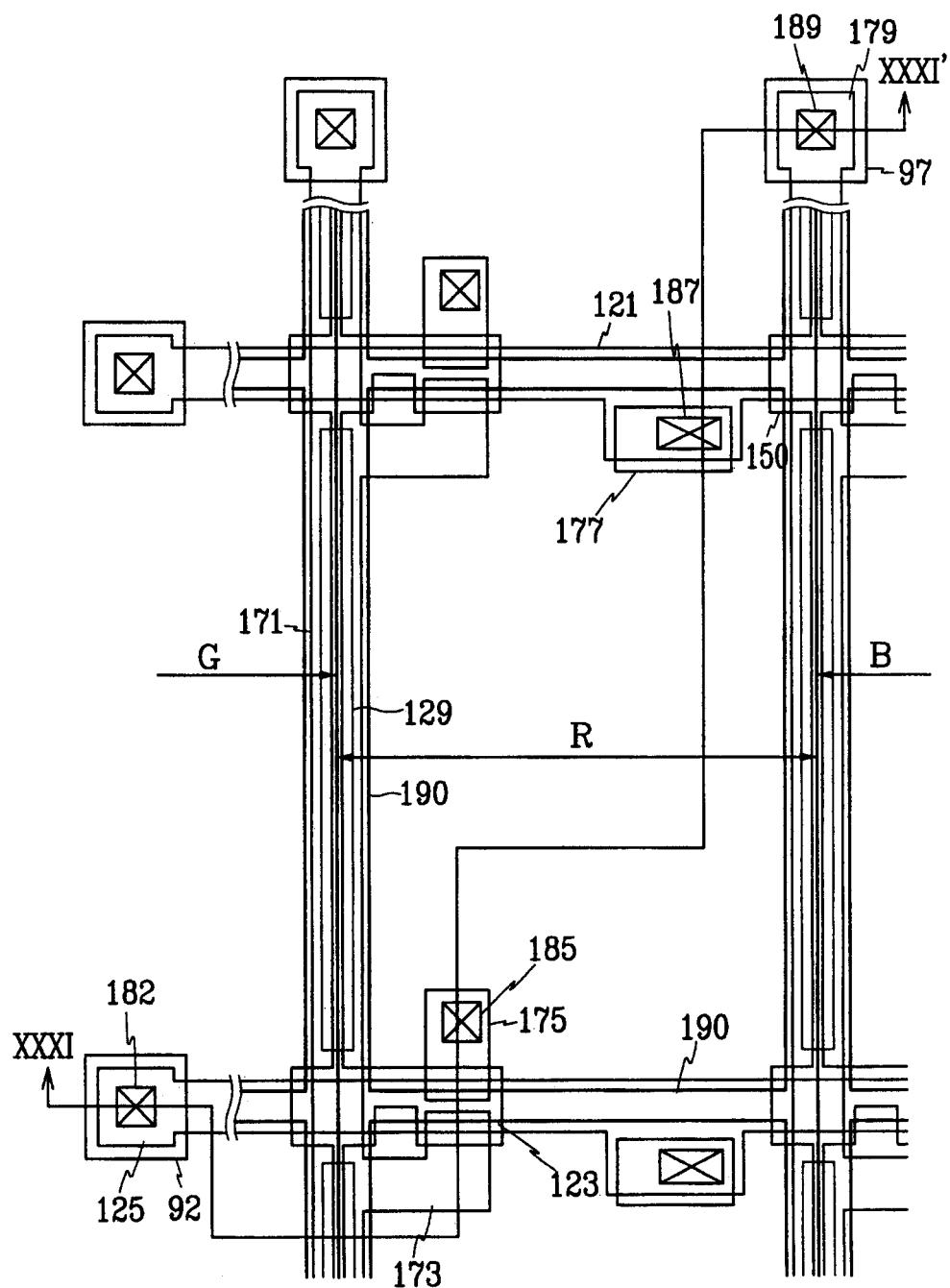

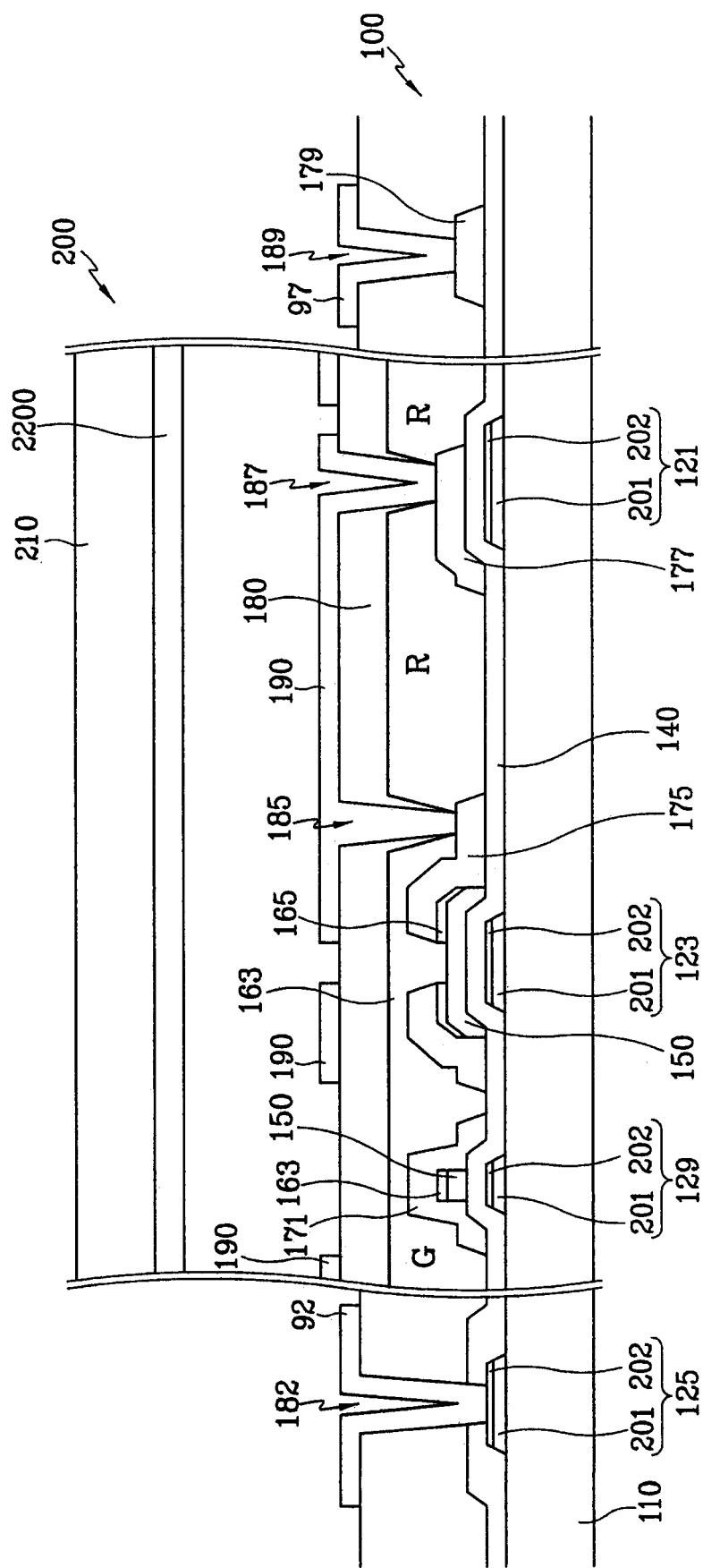

图 30 是根据本发明第七具体实施例的用于液晶显示器的 TFT 阵列面板配置图；

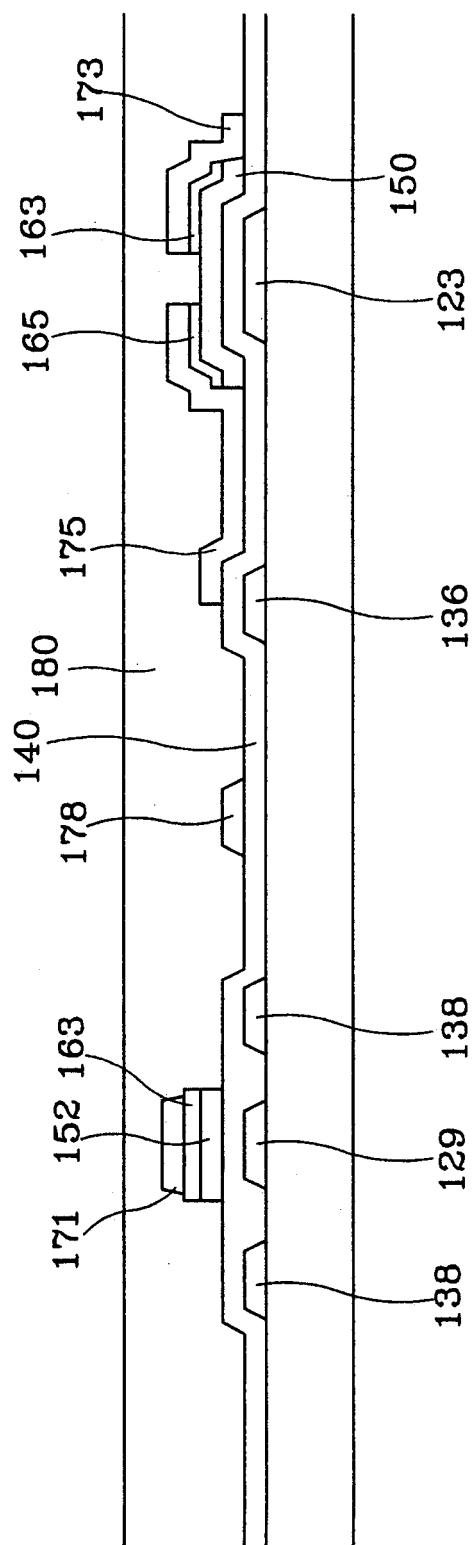

图 31 是图 30 所示的沿着 XXXI-XXXI' 线 TFT 阵列面板的截面图。

## 具体实施方式

本发明现在将参照附图在下文中被说明得更全面，其在本发明的优选实施例中示出。但是本发明可表现为不同形式，它不局限于在此说明的具体实施例。

在附图中，为了清楚起见夸大了各层的厚度及区域。在全篇说明书中对相同元件附上相同的符号，应当理解的是当提到层、区域、或基板等元件在别的部分“之上”时，指其直接位于别的元件之上，或者也可能有别的元件介于其间。相反，当某个元件被提到“直接”位于别的部分之上时，指并无别的元件介于其间。

现在参照附图详细说明根据本发明具体实施例的 TFT 阵列面板及包括各自 TFT 阵列面板的液晶显示器。

首先，参照图 1 及图 2 对根据本发明第一具体实施例的用于液晶显示器的 TFT 阵列面板进行详细说明。

图 1 为根据本发明具体实施例的用于液晶显示器的 TFT 阵列面板的配置图，图 2 是图 1 所示的沿着 II-II' 线 TFT 阵列面板以及与其面对的反向面板的截面图。

TFT 阵列面板 100 包括下绝缘基板 110。在下绝缘基板 110 上形成基本上以横向延伸的多条栅极线 121 以获得锥形结构。各栅极线 121 具有包括由铝组成的下层 201 和由具有良好接触性的材料以及诸如钼或铬之类的其它材料组成的上层 202 的多层结构。接近各栅极线 121 一端的末端部分 125 从外部装置传送栅极信号给栅极线 121，而且各栅极线 121 的末端部分 123 用做各 TFT 的栅极。栅极线 121 还可用做储能电容器的一个电极，用于通过与之后形成的与像素电极 190 连接的储能电容器图案 (storage capacitor pattern) 177 重叠提高像素的电荷存储容量。当电荷存储容量仍然不足时，可以形成与栅极布线分开的附加存储布线。在绝缘基板 110 上形成基本上以纵向延伸并且浮动的遮光层 129。遮光层 129 与之后形成的位于数据线 171 下部的非晶硅层 150、163 重叠，以防止来自背光源的入射基板 110 的光射入非晶硅层 150 和 163。

优选地，由氮化硅 ( $\text{SiN}_x$ ) 或类似物组成的栅极绝缘层 140 覆盖栅极线 121 与遮光层 129。

优选地，在栅极 125 对面的栅极绝缘层 140 上形成由诸如非晶硅等半导体材料组成的半导体层 150，并且优选地，在各自半导体层 150 上形成由硅化物或重掺杂有 n 型杂质的  $n^+$  氢化非晶硅组成的多对欧姆接触层 163、165。对于相应的栅极 125 之一，每对欧姆接触层 163 和 165 的一个欧姆接触层 163 与另一个欧姆接触层 165 是分开的。非晶硅层 150 和 163 为防止之后形成的数据线 171 断线，基本上沿着数据线 171 纵向延伸，并与遮光层 129 重叠。遮光层 129 具有比非晶硅层 150 和 163 更宽的宽度；但是，也可以具有比非晶硅层 150 和 163 窄的宽度。优选地，该重叠的宽度等于或大于非晶

硅层 150 和 163 的宽度的 60%。遮光层 129 位于之后形成的相邻像素区域的像素电极 190 之间，优选不与像素电极 190 重叠。

在欧姆接触层 163 和 165 以及栅极绝缘层 140 上，形成由钼或钼合金组成的多条数据线 171 及多个漏极 175。数据线 171 基本上以纵向延伸与栅极线 121 交叉，用于对以矩阵排列的像素区域进行限定。数据线 171 与遮光层 129 及基本上以纵向延伸的非晶硅层 150 和 163 重叠。数据线 171 的多个分支 173 延伸至欧姆接触层 163 和 165 的相对应的一个欧姆接触层 163 的上表面以形成多个 TFT 的源极 173。接进数据线 171 一端的末端部分 179 是从外源传送数据信号至数据线 171。多个储能电容器图案 177 与相关的栅极线 121 重叠并与相关的像素电极 190 电连接，其将在随后形成，利用与数据线 171 的同层形成以提高存储电容。

优选地，各数据线 171 及漏极 175 与栅极线 121 同为包括由银、银合金、铝、或铝合金组成的导电层。而且，各数据线 171 及漏极 175 可以具有包括由铬、钼、或钼合金组成的导电层的多层结构组成。可供选择地，各数据线 171 及漏极 175 具有包括由钼或钼合金组成的导电层、或由铝组成的导电层、以及由钼或钼合金组成的另一导电层的三层结构。

在数据线 171、漏极 175、以及未覆盖的半导体层 150 上形成优选由诸如氮化硅或 a-Si:C:O:H 等低电容率绝缘材料组成的钝化层 180。该钝化层 180 还可以包括由平坦性良好且具有感光性的有机材料组成的有机绝缘层，而该有机绝缘层优选不要直接覆盖暴露在源极 173 和漏极 175 之间的半导体层 150。优选完全除去分别位于栅极线 121 及数据线 171 的末端部分 125 和 179 的衬垫部分上的有机绝缘材料。因而，其对于 COG (chip on glass) 型 LCD 尤为有益，其中栅极驱动集成电路 (ICs) 及数据驱动集成电路 (ICs) 分别被

直接安装在 TFT 阵列面板上, 以传送扫描信号及图像信号给栅极线 121 及数据线 171 的衬垫部分。

通过钝化层 180 形成分别露出漏极 175、储能电容器图案 177、以及数据线的末端部分 179 的多个接触孔 185、187、和 189, 并且在钝化层 180 和栅极绝缘层 140 上提供露出栅极线的末端部分 125 的另外的接触孔 182。

在钝化层 180 上形成通过接触孔 185 与漏极 175 电连接的多个透明电极 190。像素电极 190 优选由诸如氧化铟锡( ITO ) ( indium tin oxide ) 或氧化铟锌 ( IZO ) ( indium zinc oxide ) 这样的透明导电材料组成。像素电极 190 优选与数据线 171 或栅极线 121 重叠以提高纵横比。但是, 考虑到钝化层 180 的电容率, 将通过数据线 171 及栅极线 121 传递的信号的干扰降低到最小, 像素电极 190 也可以不与数据线 171 及栅极线 121 重叠。此外, 钝化层 180 上还形成通过接触孔 182、189 分别与栅极线 121 及数据线 171 的末端部分 125、179 相连接的辅助栅极附件 92 及辅助数据附件 97。辅助栅极附件 92 及辅助数据附件 97 只是为了保护栅极线 121 及数据线 171 相应的末端部分 125、179, 而并非必需。

在面对 TFT 阵列面板 100 的反向面板 200 的上绝缘基板 210 上, 形成对应于像素区域 P 的具有开口部分的黑阵 (未示出), 并且在各像素区域 P 里形成红色、绿色、蓝色滤色器 (未示出)。可施加共同电压的共同电极 210 覆盖滤色器和黑阵的整个表面, 以通过与像素电极 190 的配合来驱动液晶分子。

这种根据本发明第一具体实施例的包括 TFT 阵列面板 100 的液晶显示器 (LCD), 其包括与 TFT 阵列面板 100 面对的反向面板 200 及相对于 TFT 阵列面板 100 从反向面板 200 的对面发射光入射 TFT 阵列面板 100 的背光源 500。该背光源通过反相器输出的开/关 (On/Off) 信号的矩形波驱动。

如果在本发明第一具体实施例中的液晶显示器没有遮光层 129，当背光源被打开 (On) 时，从背光源发出的光射入非晶硅层 150、163 中。于是，通过来自背光源的光在非晶硅层 150、163 产生电子 (electron) 与空穴 (hole)，它们在施加图像信号时与通过数据线 171 传递的电荷再次结合。另外，当背光源被关闭 (Off) 时，不产生电子与空穴；从而，通过数据线 171 被传递的图像信号只会发生延迟 (delay)。由于根据背光源的开与关状态通过数据线 171 传递的图像信号发生变化，因此还可改变传递到像素电极 190 上的像素电压。从而，当显示图像时，出现具有不同亮度的条。如果用于驱动背光源的反相器频率，即背光源的开 (On) / 关 (Off) 频率和帧频 (frame)，即对所有栅极线 121 依次施加栅极信号的频率不同步时，具有不同亮度的条上下移动的条，发生水波纹现象。

根据本发明第一具体实施例的包括 TFT 阵列面板的液晶显示器具备在沿着数据线 171 形成的非晶硅层 150、163 的下部的遮光层 129，当背光源被打开 (On) 时，射入非晶硅层 150、163 的光可被关闭。从而，遮光层 129 通过背光源可抑制电子或空穴的产生，以便除去不同亮度的条和这些条上下移动的水波纹现象，从而提高液晶显示器的显示性能。

另外，这种根据本发明第一具体实施例的用于液晶显示器的 TFT 阵列面板，栅极布线 121 或数据线 171 包括具有低电阻率的铝层，其可适用于大型液晶显示器并能提高显示性能。

那么，参照图 3A 至图 6B 及图 1 及图 2，对根据本发明具体实施例的 TFT 阵列面板的制造方法进行具体说明。

首先，如图 3A 及 3B 所示，在玻璃基板 110 上将包括铝的下层 201 和包括铬、钼或钼合金的上层 202，分别以  $2000\text{\AA}-4000\text{\AA}$  及  $500\text{\AA}-2000\text{\AA}$  厚度依次进行沉积，利用光掩膜通过光学蚀刻工序对下层 201 和上层 202 一起进行制作布线图案，以形成多条栅极线 121

与多个遮光层 129。栅极线 121 与遮光层 129 通过湿蚀刻形成具有 20-80° 范围倾角的锥形结构。当上层 202 由钼或钼合金组成时，该两层可以利用相同蚀刻液以相同的蚀刻条件进行制作布线图案。

下面，将优选由氮化硅 ( $\text{SiN}_x$ ) 组成的栅极绝缘层 140、优选由非晶硅 (a-Si:H) 组成的半导体层 150、以及掺杂的非晶硅层 ( $n^+a\text{-Si:H}$ ) 160 的三层进行连续沉积。如图 4A 及图 4B 所示，利用光掩膜制作布线图案工序对半导体层 150 和掺杂的非晶质硅层 160 的上部两层顺次进行制作布线图案，在与栅极 125 面对的栅极绝缘层 140 上形成多个半导体层 150 和多个掺杂的非晶质硅层 160。两个非晶硅层 150、160 用干蚀刻一次性进行制作布线图案，为防止随后形成的数据线 171 因非晶硅层 150、160 的断开被断线，沿着数据线 171 纵向形成。但是，若利用反相器驱动的来自背光源的光射入非晶硅层 150、160 时，液晶显示器的显示性能会变差。根据本发明的具体实施例，为了防止背光源的光射入非晶硅层 150、160，在位于数据线 171 下部的非晶硅层 150 和 160 的下部形成遮光层 129。

随后，如图 5A 和图 5B 所示，将铝或铝合金的导电层、或铬或钼或钼合金的导电层进行沉积以获得  $2000\text{\AA}$  的厚度，利用光掩膜通过光学蚀刻工序使其制作布线图案，以形成多个与栅极线 121 交叉的数据线 171、多个漏极 175、以及多个储能电容器图案 177 以获得锥形结构。

数据布线 171 可以包括由铝组成导电层，而且，若是如此，由铝组成的导电层优选位于中心层，并且在铝层上面及下部形成由钼或钼合金组成的两导电层。

随后，未被数据布线 171 及漏极 175 覆盖的掺杂的非晶硅层 160 的部分，将其除去以便在栅极 123 之上的掺杂的非晶硅层 160 的各部分相对于栅极 123 被分成两个欧姆接触层 163 和 165，露出掺杂

的非晶硅层 160 的被除去部分下部的半导体层 150 的部分。优选进行氧等离子处理以稳定半导体层 150 暴露部分的表面。

随后，通过沉积氮化物或用等离子体增强化学沉积（PECVD）（plasma enhanced chemical vapor deposition）方法沉积 a-Si:C:O 层或 a-Si:O:F 层等低电容率化学气相沉积（CVD）层形成钝化层 180。随后，如图 6A 及 6B 所示，用光学蚀刻工序将钝化层 180 和栅极绝缘层 140 制作布线图案，以形成露出栅极线 121 的末端部分 125、漏极 175、数据线 171 的末端部分 179、以及露出储能电容器图案 177 的多个接触孔 182、185、189、187。若通过接触孔 182、185、189、187 暴露的由铝组成的导电层时，考虑到与以后形成的由 ITO 或 IZO 组成的像素电极 190 的接触特性，优选除去铝导电层。

下面，如图 1 及图 2 所示，将具有 900Å 厚度的 ITO 层或 IZO 层进行沉积，利用光掩膜制作布线图案，以分别通过接触孔 185、187 连接相关的漏极 175 及相关的储能电容器图案 177 形成多个像素电极 190，并且分别通过接触孔 182、189 连接栅极线 121 及数据线 171 的末端部分 125、179 形成多个辅助栅极附件 92 及多个辅助数据附件 97。

尽管本发明的该具体实施例利用不同的掩膜采用不同的光学刻蚀工艺形成半导体层和数据线，但是另外的具体实施例则利用可将制造成本降到最低的掩膜形成半导体层和数据线。对此将参照附图更为详细地进行说明。

参照图 7 至图 9，详细说明根据本发明具体第二实施例的用于液晶显示器的 TFT 阵列面板的单位像素结构。

图 7 是根据本发明第二具体实施例的用于液晶显示器的 TFT 阵列面板的配置图，图 8 及图 9 分别是图 7 所示的沿着 VIII-VIII' 线及

IX-IX'线 TFT 阵列面板的截面图。在图 8 及图 9 中，省略了反向面板。

TFT 阵列面板 100 包括绝缘基板 110。多条栅极线 121，每个均包括由铝组成的导电层，其在绝缘基板 110 上形成以获得锥形结构。在与栅极线 121 相同的层上形成与栅极线 121 并联、并给反向面板 200（参照图 2）的共同电极 220（参照图 2）提供共同电极电压或给相邻的像素行 TFT 传送栅极信号的前端栅极线 121 电连接，接收被输入到前端栅极电压之类电压的存储电极线 131。存储电极线 131 与后述的与像素电极 190 相连接的漏极 175 重叠，形成提高像素电荷存储容量的储能电容器，当后述的因像素电极 190 和栅极线 121 彼此重叠而发生的存储电容比较充分时，也可以不形成。并且，在与栅极线 121 相同的层上，与位于随后形成的数据线 171 下部的非晶硅层 152、163 重叠，形成为了遮挡从基板 110 的下部射入非晶硅层 152、163 的光的遮光层 129。在该具体实施例中，遮光层 129 具有比非晶硅层 152、163 窄的宽度。如同在第一具体实施例中，优选遮光层 129 和非晶硅层 152、163 重叠的宽度等于或大于非晶硅层 152、163 宽度的 60%。

优选由氮化硅 ( $\text{SiN}_x$ ) 或其类似物组成的栅极绝缘层 140 覆盖栅极线 121、存储电极线 131、以及遮光层 129。

优选地，在栅极绝缘层 140 之上形成由诸如多晶硅或非晶硅等组成的多个半导体图案 152，而在半导体图案 152 之上形成诸如磷 (P) 等的 N 型或 P 型重掺杂的非晶硅组成的多个欧姆接触层 (ohmic contact layer) 图案或中间层图案 163、165。

在欧姆接触层图案 163、165 上形成由铬、钼或钼合金组成的多条数据线 171 及多个漏极 175 以获得锥形结构。数据线 171 基本上以纵向延伸与栅极线 121 交叉，其每个均具有从外部接收图像信

号的数据线的末端部分 179 和 TFT 的源极 173。该源极 173 相对于 TFT 的通道部分 C 位于与存储电极线 131 重叠的漏极 175 的对面。

欧姆接触层图案 163、165 起降低其下部半导体图案 152 和其上部数据线 171 之间、以及其下部半导体图案 152 和其上部漏极 175 之间的接触电阻的作用。与数据线 171 及漏极 175 具有完全相同的图案。即，数据线部分的中间层图案 163 与数据线 171 相同，而漏极的中间层图案 163 与漏极 175 相同。

另一方面，半导体图案 152 除 TFT 的通道部分 C 之外，与数据线 171 及漏极 175 和其下部的欧姆接触层图案 163、165 具有相同图案。具体来说，在 TFT 通道部分 C，数据线部分 171，特别是源极 173 和漏极 175 处于彼此分离，数据线部分的中间层 163 和用于漏极部分的中间层 165 也处于彼此分离，但用于 TFT 的半导体图案 152 在这里不间断连接并形成 TFT 的通道。半导体图案 152 露出数据线 171 的边缘，位于数据线 171 下部的半导体图案 152 则具有比遮光层 129 更宽的宽度。

在数据线 171 及漏极 175 以及未被其遮盖的半导体图案 152 上部，形成优选由具有低电容率有机材料组成的有机绝缘层或包括和第一具体实施例相同的低电容率 PECVD 层的钝化层 180。在半导体图案 152 分别露出数据线的末端部分 179 及漏极 175 的多个接触孔 189、185，并且在钝化层 180 和栅极绝缘层 140 上提供露出栅极线的末端部分 125 的另外的接触孔 182。

钝化层 180 之上形成从 TFT 接收图像信号并与上面板的电极一起产生电场的多个像素电极 190。像素电极 190 优选由诸如 ITO 或 IZO 类透明的导电材料或由诸如铝或银等的具有反射率的导电材料组成，通过接触孔 185 与漏极 175 形成物理电连接以接收图像信号。因为钝化层 180 包括具有低电容率的有机绝缘层，即使像素电极 190 与数据线 171 及栅极线 121 重叠以提高纵横比，但几乎不会因其重

叠发生信号的干扰。并且，遮光层 129 还可以通过与相邻像素区域的像素电极 190 重叠，遮挡相邻像素区域间的泄漏光。另外，在钝化层 180 上形成分别通过接触孔 182 与栅极线 121 的末端部分 125 相连以及通过接触孔 189 与数据线 171 的末端部分 179 相连的多个辅助栅极附件 92 及辅助数据附件 97。辅助栅极附件 92 及辅助数据附件 97 用于保护相应的栅极线 121 和数据线 171 的末端部分 125、179，并且用于补充与外部电路装置的接触性能，但这些不是必需的，使用与否自行选择。

这种根据本发明的第二具体实施例的 TFT 阵列面板也和第一具体实施例相同，当背光源被打开 (On) 时，因具备了用于遮挡射入数据线 171 下部的非晶硅层 163 的光的遮光层 129，所以可除去不同亮度的条和发生条上下移动的水波纹现象，以此来提高液晶显示器的显示性能。

那么，对具有图 7 至图 9 所示的用于 TFT 阵列面板的制造方法，将参照图 7 至图 9 和图 10A 至 16C 更为详细地进行说明。

首先，如图 10A 至 10C 所示，将由铝或含铝的材料组成的导电层、或者由铬或钼或钼合金组成的导电层进行沉积，并且利用光掩膜通过光学蚀刻工序制作布线图案，以形成多条栅极线 121、多条存储电极线 131、及多个遮光层 129 以获得锥形结构。

下面，如图 11A 及 11B 所示，利用化学气相沉积 (CVD) 对优选由氮化硅组成的栅极绝缘层 140、未掺杂的非晶硅半导体层 150、掺杂的非晶硅中间层 160 分别以  $1500\text{\AA}-5000\text{\AA}$ 、 $500\text{\AA}-2000\text{\AA}$ 、以及  $1400\text{\AA}-600\text{\AA}$  的厚度进行连续沉积。随后，如图 11A 及 11B 所示，用溅射等方法将由钼或钼合金组成的导电材料、或只由铝组成的导电材料组成的导电体层 170 进行沉积以获得  $1500\text{\AA}-3000\text{\AA}$  的厚度，并涂覆感光层 210 以获得  $1\mu\text{m}-2\mu\text{m}$  的厚度。

随后，通过掩膜向感光层 210 照射光，并显像形成图 12B 及图 12C 所示的感光层图案 212、214。在感光层图案 212、214 中使 TFT 通道部分 C，即位于源极 173 和漏极 175 之间第一部分 214 厚度比位于数据布线 A，即位于数据线 171 形成部分的第二部分 212 厚度小，其余部分 B 的感光层都要除去。通道部分 C 剩余感光层部分 214 厚度和数据布线 A 剩余感光层部分 212 厚度之比应取决于后述蚀刻的操作条件而变化，优选第一部分 214 厚度小于第二部分 212 厚度的 1/2，例如等于或小于 4000Å。

根据位置可以采用不同方法制造不同厚度的感光层。例如，为了调整 A 部分的光透过量，可使用具有狭缝（slit）图案或晶格图案的半透明部分的掩膜。

当使用狭缝（slit）图案时，优选狭缝的宽度或狭缝之间的距离小于用于该步骤的曝光机的分辨率。可供选择地，通过利用具有不同透射率或厚度的多个层形成掩膜而获得具有半透明部分的掩膜。

当通过上述的掩膜给感光层照射光时，直接暴露在光下部分的聚合物被完全分解，在狭缝（slit）图案或形成半透明层的部分，因光的照射量少，聚合物处于未完全分解的状态，而被遮光层遮住的部分聚合物几乎未分解。当感光层显像时，只剩下聚合物未分解部分，感光照射量少的中间部分剩下比未被光照射部分更薄的感光层。这时若曝光时间过长，所有聚合物会被分解，所以应防止其发生。

这种薄的感光层 214 可为利用可以回流的材料组成的感光层。用光完全透过部分和光完全不能透过部分组成的常规掩膜曝光后，显像并回流，用未残留感光层的部分使感光层一部分流下来。于是，可形成一薄层的感光层。

随后，对感光层图案 214 及其下部的层，即，将导电体层 170、中间层 160、及半导体层 150 进行蚀刻。就数据线部分 A 而言，剩下数据线及其下部的层。就通道部分 C 而言，只能剩下半导体层及其下部的层。在余下部分 B 应全部除去上述 3 个层 170、160、150，并应该露出栅极绝缘层 140。

首先，如图 13A 及 13B 所示，除去其它部分 B 露出的导电体层 170，露出其下部的中间层 160。这个过程中可以使用干蚀刻或湿蚀刻方法，优选在导电体层 170 被蚀刻而感光层图案 212、214 基本不被蚀刻的条件下进行。但是，干蚀刻很难满足只蚀刻导电体层 170 而不蚀刻感光层图案 212、214 的条件，所以只能在感光层图案 212、214 一同被蚀刻的条件下进行。这时不采用湿蚀刻，而是增加第一部分 214 厚度来防止发生在此过程中第一部分 214 被除去而露出下部导电层 170 的情况。

这样，如图 13A 及图 13B 所示，只剩下通道部分 C 及数据布线部分 A 的导电体层，即用于源/漏的导电体图案 178，部分 B 的导电体层 170 被全部除去，露出其下部中间层 160。除源极及漏极 173、175 未分离相连接的地方之外，剩余导电体图案 178 与数据线 171 和漏极 175 形态相同。若将导电体层 170 进行干蚀刻，一部分的感光层图案 212、214 也要进行蚀刻。

接着，如图 14A 及 14B 所示，将部分 B 露出的中间层 160 及其下部半导体 150 与感光层的第一部分 214 一起用干蚀刻方式同时除去。这种蚀刻，同时蚀刻感光层图案 212、214 和中间层 160 及半导体层 150（半导体层和中间层几乎没有蚀刻选择性），但必须在栅极绝缘层 140 不被蚀刻的条件下进行。优选地，对感光层图案 212、214 和半导体层 150 的蚀刻比基本相同的条件下蚀刻。例如，用 SF<sub>6</sub> 和 HCL 混合气体或 SF<sub>6</sub> 和 O<sub>2</sub> 混合气体，可以将两个层蚀刻成几乎同样的厚度。对感光层图案 212、214 和半导体层 150 的蚀刻比相

同时，第一部分厚度应与半导体层 150 和中间层 160 厚度之和相同或应比其小。

这样，如图 14A 及 14B 所示，通道部分 C 的第一部分 214 被除去，露出用于源/漏导电体图案 178，部分 B 的中间层 160 及半导体层 150 被除去，露出其下部栅极绝缘层 140。另外，数据布线部 A 的第二部分 212 也被蚀刻，其厚度变薄。在该步骤中，最终形成半导体图案 152。图中标号 168 是指用于源/漏导电体图案 178 下部的中间层图案。

接着，通过抛光，除去残留在通道部分 C 用于源/漏导电体图案 178 表面的感光层残渣。这样做的话，感光层图案 212 的厚度及宽度的一部分也被除去，使源/漏导电体图案 178 和其下部的中间层图案 168 及半导体层图案 152 的边缘部分露在感光层图案 212 外面。

然后，如图 15A 及图 15B 所示，蚀刻并除去通道部分 C 的用于源/漏导电体图案 178 及其下部用于源/漏中间层图案 168。可以对用于源/漏导电体图案 178 和中间层图案 168 均只进行干蚀刻，也可能对用于源/漏导电体图案 178 进行利用蚀刻液的湿蚀刻，对中间层图案 168 也可以进行干蚀刻。就前者而言，优选在用于源/漏导电体图案 178 和中间层图案 168 的蚀刻选择性大的条件下进行蚀刻，这是因为蚀刻选择性不大时，很难找到蚀刻终点，因而很难调整残留在通道部分 C 的半导体图案 152 厚度。作为蚀刻中间层图案 168 及半导体图案 152 时使用的蚀刻气体的例子，有所述的 CF<sub>4</sub> 和 HCl 混合气体或 CF<sub>4</sub> 和 O<sub>2</sub> 混合气体，若使用 CF<sub>4</sub> 和 O<sub>2</sub>，可以使残留的半导体图案 152 的厚度很均匀。这时如图 15B 所示，半导体图案 152 一部分被除去，其厚度也可能变小，对感光层图案的第二部分 212 厚度也有一定的蚀刻。这时要保证不蚀刻栅极绝缘层 140。优选感光层图案要厚，以防止第二部分 212 被蚀刻露出其下部的数据线 171 及漏极 175。

这样，如图 12A 所示，将漏极 175 从数据线 171 处分离，从而完成其下部的欧姆接触层图案 163、165。

最后，除去残留在数据布线部分 A 的感光层的第二部分 212。可供选择地，第二部分 212 的去除也可以在除去通道部分 C 的用于源/漏导电体图案 178 以后，除去中间层图案 168 之前完成。

如上所述，可以交替地使用湿蚀刻和干蚀刻或也可以单独使用干蚀刻。就后者而言，只使用一种蚀刻，其工序比较简单，但寻找合适的蚀刻条件较难。反之，前者较容易寻找蚀刻条件，但比起后者工序有繁琐的一面。

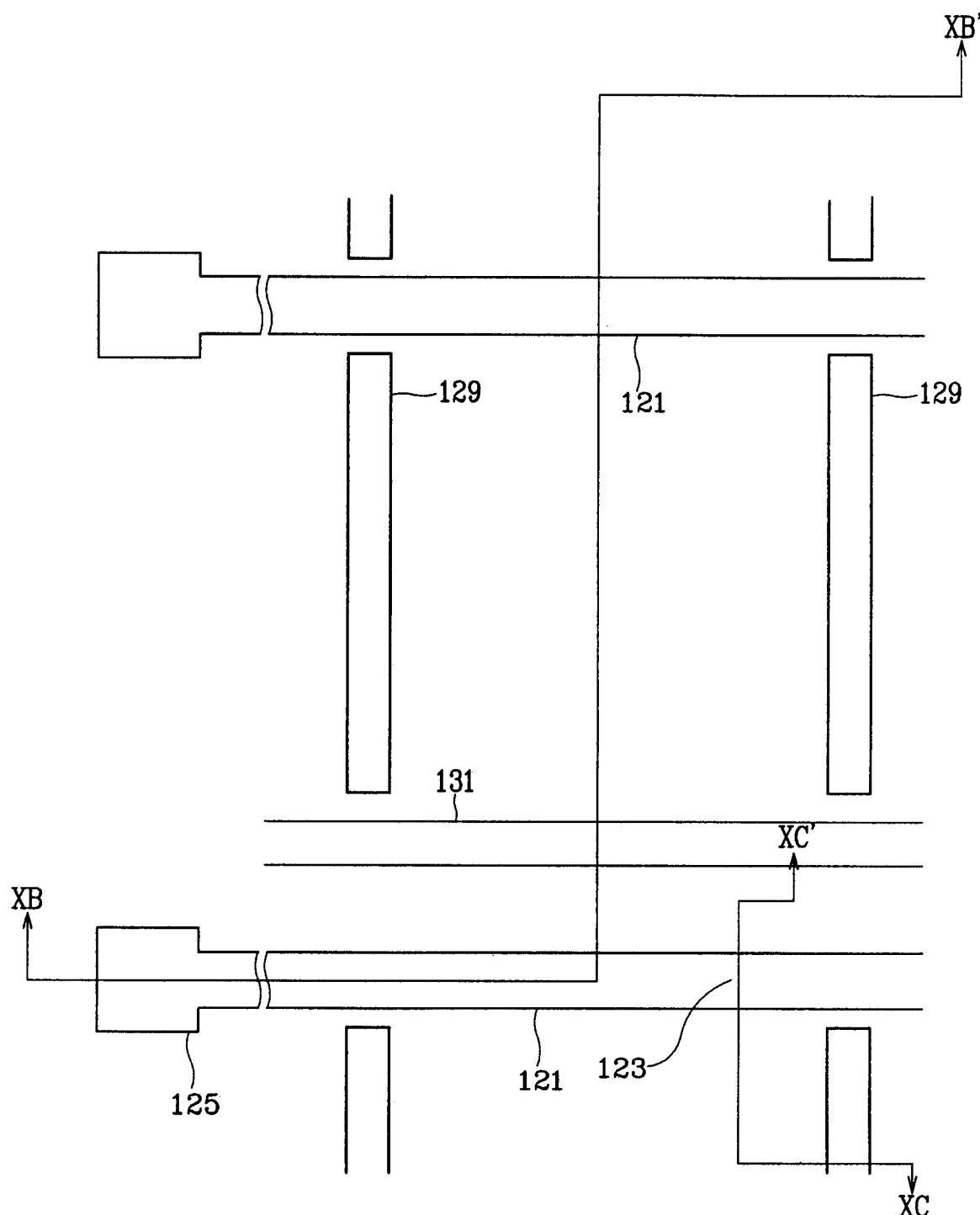

如前所述，在形成数据线 171 及漏极 175 后，通过有机绝缘材料的沉积形成钝化层 180。如图 16A 至 16C 所示，利用掩膜通过蚀刻钝化层 180 和栅极绝缘层 140，形成分别露出栅极线 121 的末端部分 125、数据线 171 的末端部分 179、和漏极 175 的多个接触孔 182、189、185。

接着，如图 7 至图 9 所示，沉积 500Å-1000Å 厚度的 ITO 层或 IZO 层，利用掩膜进行湿蚀刻形成与漏极 175 连接的像素电极 190，与栅极线及数据线各自的末端部分 125、179 连接的辅助栅极附件 92 及辅助数据附件 97。

在这种根据本发明的第二具体实施例，利用一个掩膜形成数据线 171 和其下部欧姆接触层图案 163、165 及半导体图案 152、157，且在这过程中可以分离源极 173 和漏极 175 来简化制造工序。

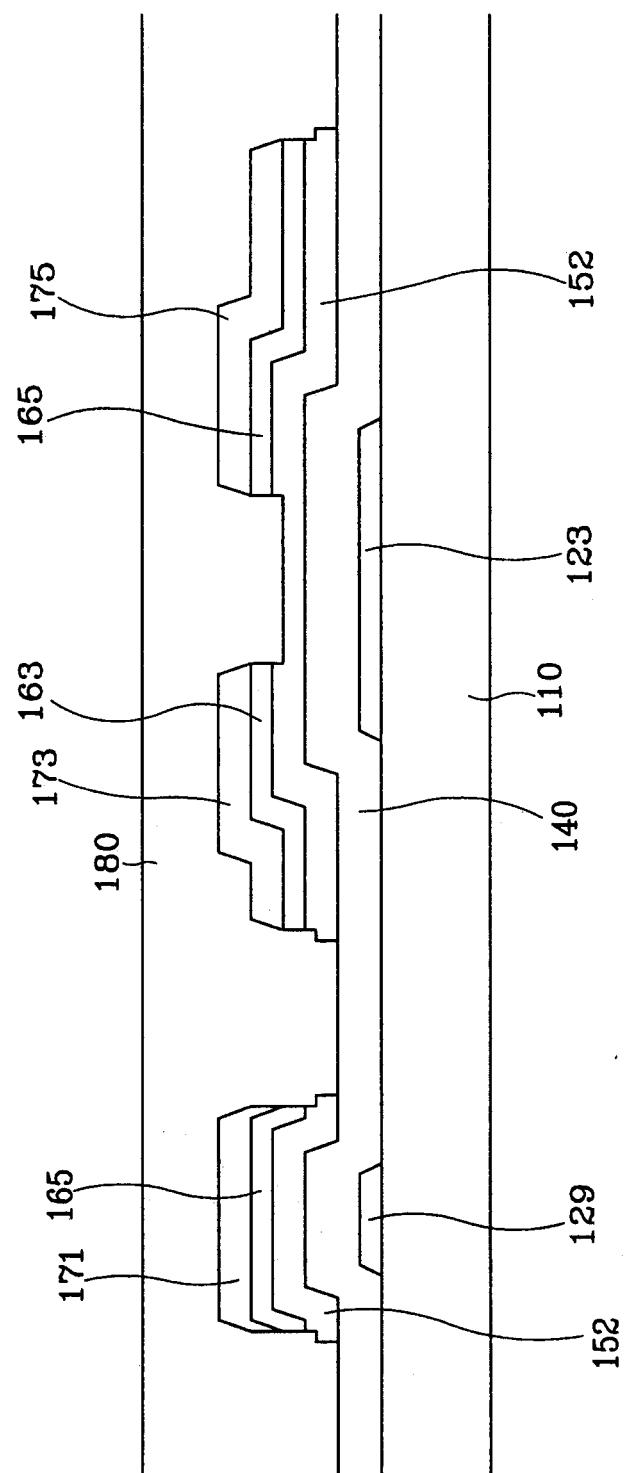

尽管在本发明的第一及第二具体实施例当中说明了非晶硅层 150、152 具有比数据线 171 更宽或更窄宽度的情况，但非晶硅层可以具有与数据线相同的宽度，对此将参照附图进行具体说明。

图 17 是根据本发明第三具体实施例的用于液晶显示器的 TFT 阵列面板，图 18 是图 17 所示的沿着 XVIII-XVIII' 线 TFT 阵列面板的截面图。

在绝缘基板 110 上具有低电阻的包括银或银合金或铝或铝合金的由金属材料组成的导电层的多条栅极线 121，以及给上面板的共同电极提供共同电极电压或从外部接收给相邻的像素行 TFT 传送的栅极电压类的电压的多条存储电极线 131，形成具有 20-70° 范围倾角的锥形结构。另外，在基板 110 上如同第一及第二具体实施例，以基本上纵向形成遮光层 129。

优选地，在栅极 125 对面的栅极绝缘层 140 上部形成由诸如非晶硅等半导体材料组成的半导体层图案 152 及多对欧姆接触层 163、165 以得到具有 20-80° 范围倾角的锥形结构。

在欧姆接触层 163、165 上形成包括由诸如钼 (Mo) 或钼-钨 (Mo-W) 合金、铬 (Cr)、钽 (Ta)、或钛 (Ti) 等屏蔽金属 (barrier metal) 组成的下层 701 和由诸如低电阻的银、银合金、铝 (Al)、或铝合金 (Al alloy) 组成的上层 702 的多条数据线 171 及多个漏极 175。

数据线 171 中由铝 (Al) 或铝合金 (Al alloy) 组成的上层 702，在其接触部分，即漏极 175 及数据线的末端部分 179 的部分被除去，而上层 702 被除掉的接触部分露出与别的材料接触性能良好、并为防止铝或铝合金扩散到硅层 150、163、165 的由屏蔽金属组成的下层 701，而上层 702 的边界线位于下层 701 的上部，数据线 171 包括具有互不相同图案的下层 701 与上层 702。

栅极电极 123、漏极 175、及源极 173 位于 TFT 部分，而半导体层图案 152 除去 TFT 部分，数据线 171 及漏极 175 与欧姆接触层 163、165 具有同样的图案。特别是，数据线 171 下部的半导体图案

**152** 与数据线 **171** 具有同样的宽度, 这是在制造工序上将数据线 **171** 或为数据线 **171** 制作布线图案的感光层图案当作蚀刻掩膜使用, 对半导体图案 **152** 进行制作布线图案。

优选地, 通过由具有良好平坦性和感光性的有机材料、诸如 a-Si:C:O 或 a-Si:O:F 等具有低电容率的绝缘材料、或氮化硅组成的钝化层 **180** 形成分别露出接触部分 (即, 漏极 **171** 和数据线的末端部分 **179**) 的下层 **701** 的多个接触孔 **187**、**189**, 并钝化层 **180** 和栅极绝缘层 **140** 上提供露出栅极线的末端部分 **125** 的多个另外的接触孔 **182**。通过接触孔 **185**、**187**、**189** 暴露的下层 **701** 的表面组成具有高度差的不规则表面。没有侧凹的形状 (undercut shape), 钝化层 **180** 在接触孔 **185**、**189** 的周围与下层 **701** 接触, 覆盖通过接触孔 **185**、**189** 露出的下层 **701**。

如同第一或第二具体实施例, 在钝化层 **180** 上形成像素电极 **190**、辅助栅极附件 **92** 及辅助数据附件 **97**, 而像素电极 **190** 及辅助数据附件 **97** 通过接触孔与相应的漏极 **175** 的不规则表面和数据线 **171** 的末端部分 **179** 连接。

这样的根据本发明的第三具体实施例的用于液晶显示器的 TFT 阵列面板上也形成遮光层 **129**, 由此可得到如同第一及第二具体实施例的效果, ITO 层或 IZO 层 **190**、**92**、**97** 在接触部分, 在漏极 **175** 及数据线的末端部分 **179** 的下层 **701** 的上部只与下层 **701** 接触, 能确保接触部分的接触电阻低下, 并通过这些可提高显示器的显示性能。

尽管在上述具体实施例中像素电极 **190** 是由透明的 ITO 或 IZO 组成, 但该像素电极可以用透明的导电性聚合物 (polymer) 等形成。可供选择地, 不透明的导电性材料可用于反射型液晶显示器。

那么，对这样的根据本发明第三具体实施例用于液晶显示器的 TFT 阵列面板的制造方法，参照图 17 及图 18 和图 19A 至图 23B 详细说明。

首先，如图 19A 及图 19B 所示，在玻璃基板 110 上部以锥角结构形成包括栅极线 121 及存储电极线 131 的栅极布线。

接着，如图 20A 及图 20B 所示，栅极绝缘层 140、优选由非晶硅组成的半导体层 150、以及掺杂的非晶硅层 160 的三层顺次沉积。优选地，栅极绝缘层 140 在 250~400℃ 温度范围内，通过具有 2000~5000Å 厚度的氮化硅沉积来形成。接着，由屏蔽金属组成的下层 701 能够用于防止其它材料扩散到半导体层 150 或掺杂的非晶硅层 160 上的同时，如 ITO 或 IZO 等与其它材料接触性能良好的屏蔽金属中由钼或钼合金或铬等组成的下层 701 用 500Å 左右的厚度，利用具有低电阻的铝或铝合金中包括 2at% 的 Nd 的 Al-Nd 合金靶材，将上层 702 在 150℃ 左右，以 2500Å 厚度依次沉积。然后，使用用于数据布线的光掩膜通过光学蚀刻对上层 702 与下层 701 进行制作布线图案，以形成多条数据线 171 及多个漏极 175。上层 702 及下层 701 都可以用湿蚀刻，上层 702 用湿蚀刻，下层 701 则用干蚀刻。如果下层 701 是由钼或钼合金组成时，下层 701 与上层 702 可使用同一个蚀刻条件制作布线图案。

接着，如图 21A 及图 21B 所示，利用用于半导体图案的光掩膜通过光学蚀刻进行曝光及显影，形成用于半导体图案的感光层图案 210。感光层图案 210 要形成为，至少不覆盖数据布线中被用来接触部分的数据线的末端部分 179 及漏极 175。接着，首先利用感光层图案 210 作为蚀刻掩膜，蚀刻含铝的上层 702，在接触部分露出数据线的末端部分 179 及漏极 175 的下层 701。优选地，感光层图案 210 至少在用作接触部分的数据线的末端部分 179 及漏极 175 的上部也留下一部分，并在通过随后形成的接触孔 185、187、189

露出的接触部分上留下上层 702。这是在随后的制作工序中进行干蚀刻工序时,为防止有可能发生的在接触部分下层 701 全面露出时,下层 701 的表面被损伤。优选地,在数据线的末端部分 179 及漏极 175 的接触部分留下的上层 702 比随后形成的钝化层 180 的接触孔 185、189 要小一些,且具有岛形。接着,将数据布线 171、漏极 175、和感光层图案 210 当作蚀刻掩膜,蚀刻露出的掺杂的非晶硅层 160 和半导体层 150 来完成半导体层图案 152,并在其上部留下掺杂的非晶硅层 160。半导体层图案 152 只留在没有被数据线 171 及漏极 175 的下部和感光层图案 210 遮挡的部分,因此至少具有比数据线 171 及漏极 175 大的面积。另外,因为要在接触部分利用感光层图案 210 作为刻蚀掩膜,除掉含铝的上层 702,所以感光层图案 210 至少不遮挡数据布线中的一部分即数据线的末端部分 179 及部分漏极 175,但是在源极 173 和漏极 175 之间的通道部分,为了防止半导体层被蚀刻,至少要覆盖该通道部分。

虽然数据线 171 及漏极 175 形成双重结构,但是也可以形成单层。此外,感光层图案 210 也可形成以完全覆盖数据线 171。

接着,除掉感光层图案 210,如图 22 所示,一面蚀刻未被数据线 171 及漏极 175 遮挡住的掺杂的非晶硅层图案 160,以栅极线为中心分离到两边,另一面则露出两边掺杂的非晶硅层 163、165 之间的半导体层图案 152。在蚀刻掺杂的非晶硅层图案 160 的方法上适用干蚀刻,而干蚀刻时,在数据线的末端部分 179 及漏极 175 的接触部分,下层 701 完全暴露时有可能受到全面损伤,因此如前所述,在数据线的末端部分 179 及漏极 175 的接触部分留下上层 702 后进行干蚀刻。

下面,如图 23A 及图 23B 所示,形成钝化层 180,和栅极绝缘层 140 一起进行干蚀刻制作布线图案,形成分别露出栅极线的末端部分 125 及漏极 175 及数据线的末端部分 179 的下层 701 的接触孔

**182、185、187、189。**而接触孔 **185、189** 是干蚀刻钝化层 **180** 制作布线图案形成的。干蚀刻时，在通过接触孔 **185、189** 露出的数据线的末端部分 **179** 及漏极 **175** 的接触部分，没有被上层 **702** 覆盖住而露出的下层 **701** 部分被蚀刻，而被上层 **702** 覆盖住的地方则没有被蚀刻，因此在接触部分，下层 **701** 存在具有高度差的不规则表面（断开的凹凸结构）。

随后，通过蚀刻除掉通过接触孔 **185** 和 **189** 露出的铝或铝合金组成的上层 **702**。最后，如图 17 及图 18 所示，分别形成通过接触孔 **185** 与漏极 **175** 的下层 **701** 连接的多个像素电极 **190** 和通过接触孔 **182、189** 分别与栅极线及数据线的末端部分 **125、179** 的下层 **701** 连接的多个辅助栅极附件 **92** 及辅助数据附件 **97**。在根据本发明的具体实施例中，作为形成 IZO 层 **190、92、** 和 **97** 的靶材 (target)，使用了 Idemitsu 公司的 IDIXO (indium x-metal oxide) 产品。该靶材包括  $In_2O_3$  及  $ZnO$ ，而  $In+Zn$  中  $Zn$  的含量优选在 15-20at% 之内。并且，为了接触电阻的最小化，IZO 层优选在 250°C 以下的范围内进行沉积。

另一方面，根据本发明的第三具体实施例的 TFT 阵列面板的制造方法中，用于半导体图案的感光层图案 **210** 可以用比数据线 **171** 更大的宽度来显影形成，对于通过这样的制造工序完成的结构，可参照附图进行具体说明。

图 24 是根据本发明第四具体实施例的用于液晶显示器的 TFT 阵列面板的配置图，图 25 是图 24 所示的沿着 XXV-XXV' 线 TFT 阵列面板的截面图。

如图 24 及图 25 所示，该结构与根据本发明的第三具体实施例非常相似。

然而，半导体图案 152 具有比数据线 171 更宽的宽度，并且含有铝的上层 702 在数据线 171 上全面形成。遮光层 129 形成比数据线 171 的宽度窄。

另一方面，可将本发明的第一至第四具体实施例的遮光层应用于用于面内切换 (IPS) (in-plane switching) 型 LCD 的 TFT 阵列面板，其中与面板并联排列的液晶分子通过成直线地排列在同一面板上的像素电极和共同电极进行调整。

图 26 是图示根据本发明第五具体实施例的用于液晶显示器的 TFT 阵列面板结构的配置图；图 27 是图 26 所示的沿着 XXVII-XXVII' 线 TFT 阵列面板的截面图，图 28 是根据本发明第六具体实施例的用于液晶显示器的 TFT 阵列面板的配置图；图 29 是图 28 所示的沿着 XXIX-XXIX' 线 TFT 阵列面板的截面图。

如图 26 及图 27 所示，在绝缘基板 110 上形成栅极线 121 及共同布线。共同布线包括和栅极线 121 并联，并且横向延伸的共同信号线 136 及通过与共同信号线 136 连接的共同信号线 136 施加共同信号的共同电极 138。在此，共同布线 136、138 与随后形成的像素布线 176、178 重叠，可得到形成存储电容的存储电极的功能。并且，在绝缘基板 110 的上部有与位于随后形成的数据线 171 下部的半导体层 150 重叠并且纵向延伸的遮光层 129。

覆盖栅极线 121 及共同布线 136、138 的栅极绝缘层 140 的上部可形成具有沿着随后形成的数据线 171 纵向延伸并与遮光层 129 重叠部分的多个半导体层 150，其上部还形成了欧姆接触层 165、163。

在欧姆接触层 163、165 或栅极绝缘层 140 的上部形成了数据线 171 及漏极 175。并且，在和数据线相同的层上形成；包括与漏极 175 连接并且横向延伸、与共同信号线 136 面对或重叠、形成储

能电容器的像素信号线 176 及；与像素信号线 176 相连接且纵向延伸并和共同电极并联面对的像素电极的像素布线。

在基板 110 的上部形成钝化层 180。钝化层 180 如同第一或第四具体实施例，可具有分别露出栅极线及数据线末端部分的接触孔，而在钝化层的上部还可形成与数据布线 171 相连接的辅助数据线，也可形成栅极线及数据线相应的末端部分电连接的辅助附件。

根据本发明的第六具体实施例的 TFT 阵列面板结构大部分与根据第五具体实施例的结构相同。

但是，除了通道部分以外的半导体图案 152 与数据线 171 及漏极 175 具有同样的图案。

在根据本发明的第五及第六具体实施例中，像素布线 176、178 虽然位于与数据线 171 及漏极 175 相同的层上，但是可以在与栅极线 121 相同的层或钝化层 180 的上部形成。共同布线 136、138 可以在与栅极线 121 不同的层上形成，也可以在与像素布线 176、178 相同的层上形成。

然而，红色、绿色、蓝色滤色器通常安置在反向面板上，有可能安置在 TFT 阵列面板上。对此将参照附图进行具体说明。

图 30 是根据本发明第七具体实施例中 TFT 阵列面板的配置图；图 31 是图 30 所示的沿着 XXXI-XXXI' 线 TFT 阵列面板的截面图。

如图 30 及图 31 所示，根据本发明的第七具体实施例的 TFT 阵列面板结构大部分与图 1 及图 2 相同。

然而，根据本发明的第七具体实施例的 TFT 阵列面板，其像素电极 190 的上部及保护层 180 的下部形成红色 (R)、绿色 (G)、蓝色 (B) 滤色器。

红色 (R)、绿色 (G)、蓝色 (B) 滤色器具有的接触孔虽然比钝化层 180 具有的接触孔 185、187 大，但也可以比它小，因此接触孔 185、187 的侧壁有可能成阶梯形，由此限定接触孔的侧壁优选具有锥形结构。

红色 (R)、绿色 (G)、蓝色 (B) 滤色器可安置在栅极线 121 和基板 110 之间，而其可能在与数据线 171 重叠的边缘处彼此重叠。

如上所述，因为根据本发明的包括 TFT 阵列面板的液晶显示器具有可用于遮挡射入位于数据线下部非晶硅层的来自背光源光的遮光层，其可提高液晶显示器的显示性性能。尤其是，就利用反相器驱动的背光源的液晶显示器而言，可防止显示图像时形成的具有不同亮度的条，并能除掉该条上下移动的水波纹现象。

虽然本发明参照优选具体实施例进行了详细描述，应当理解本发明不局限于公开的实施例，而是相反地，其意味着覆盖了包括在所附权利要求的精神和范围内的各种变形和等同方案。

图 1

2

图3A

图3B

图4A

图4B

图 5A

图5B

图 6A

图 6B

图7

8

图9

图 10A

图10B

图 10C

四 11A

图 11B

图 12A

图12B

图12C

图13A

图13B

图 14A

图14B

图 15A

图 15B

图16A

16B

图 16C

图17

图 18

图19A

图19B

图20A

图 20B

图21A

图21B

图 22

图23A

图23B

图24

图25

图26

图27

图28

图29

图30

三一

|                |                                                                                                                              |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 薄膜晶体管阵列面板及包括该面板的液晶显示器                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">CN1508612A</a>                                                                                                   | 公开(公告)日 | 2004-06-30 |

| 申请号            | CN200310121289.4                                                                                                             | 申请日     | 2003-12-17 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                     |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                                                                                                     |         |            |

| [标]发明人         | 金东奎                                                                                                                          |         |            |

| 发明人            | 金东奎                                                                                                                          |         |            |

| IPC分类号         | G02F1/1368 G02F1/136 G02F1/1362 G09F9/30 G09F9/35 H01L21/28 H01L21/3213 H01L29/417 H01L29/423 H01L29/49 H01L29/786 H01L21/02 |         |            |

| CPC分类号         | G02F1/136286 H01L27/1214 G02F2001/136236 H01L27/1288 H01L29/78633 G02F1/136209 H01L27 /124                                   |         |            |

| 代理人(译)         | 余刚                                                                                                                           |         |            |

| 优先权            | 1020020080812 2002-12-17 KR                                                                                                  |         |            |

| 其他公开文献         | CN100444004C                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                               |         |            |

#### 摘要(译)

本发明提供一种TFT阵列面板，在其绝缘基板上形成包括栅极线和栅极的栅极布线，在覆盖栅极布线的栅极绝缘层上形成由非晶硅组成的半导体层。在覆盖栅极布线的半导体层或栅极绝缘层上形成包括数据线、源极、及漏极的数据布线。半导体层的一部分延伸至数据线的下部，在栅极布线同一层上形成与位于数据线下部半导体层部分重叠的遮光层。该遮光层用于防止来自背光源入射基板的光射入非晶硅层；从而可防止液晶显示器显示图像时出现的具有不同亮度的条和这类条上下移动的水波纹现象，而液晶显示器是使用背光源由反相器输出的开/关信号的矩形波驱动。