## [12] 发明专利申请公开说明书

[21] 申请号 200410083701.2

G02F 1/136

G02F 1/133

H01L 29/786

H01L 21/00

G02B 5/20

[43] 公开日 2005 年 4 月 20 日

[11] 公开号 CN 1607432A

[22] 申请日 2004.10.14

[74] 专利代理机构 北京律诚同业知识产权代理有限公司

[21] 申请号 200410083701.2

代理人 徐金国 梁 挥

[30] 优先权

[32] 2003.10.14 [33] KR [31] 10-2003-0071403

[32] 2003.11.4 [33] KR [31] 10-2003-0077660

[71] 申请人 LG. 菲利浦 LCD 株式会社

地址 韩国汉城

[72] 发明人 南承熙 柳洵城 张允琼 赵兴烈

权利要求书 10 页 说明书 32 页 附图 64 页

[54] 发明名称 薄膜晶体管阵列基板和液晶显示面板及它们的制造方法

## [57] 摘要

本发明公开了一种基板，该基板具有交叉的、中间是栅极绝缘膜的栅极和数据线，设置在栅极和数据线交叉点上的薄膜晶体管，连接到晶体管的像素电极，通过接触孔连接到信号线并且包含有透明导电膜的焊盘，以及与滤色片阵列基板重叠并暴露出该膜的保护膜。所述接触孔暴露出焊盘和/或信号线的端部及其相邻区域。栅极、源极和漏极以及接触电极分别由第一、第二和第三导电层形成。接触孔暴露出一个晶体管的第一导电层和另一晶体管的第二导电层的相邻部分。接触电极连接暴露的第一和第二导电层。制造这种基板仅仅需要三轮掩模工序。

1、一种液晶显示面板，包括：

滤色片阵列基板，具有在上基板上形成的滤色片阵列；以及

薄膜晶体管阵列基板，具有：

5 在下基板上彼此交叉、且中间设有栅极绝缘膜的栅极线和数据线，

设置在栅极线和数据线之间交叉点上的薄膜晶体管，

连接到薄膜晶体管的像素电极，

通过接触孔连接到信号线的焊盘，所述信号线是栅极线或数据线，

所述焊盘含有透明导电膜，以及

10 设置在与滤色片阵列基板重叠的区域的保护膜，暴露出焊盘的透明

导电膜，

其特征在于，所述薄膜晶体管阵列基板与相对的滤色片阵列基板粘接，

并且

所述接触孔暴露出至少一个焊盘和信号线的端部以及与其相邻的区域。

15 2、按照权利要求 1 所述的液晶显示面板，其特征在于，所述焊盘包括：

连接到栅极线的栅极焊盘；以及

连接到数据线的数据焊盘。

3、按照权利要求 2 所述的液晶显示面板，其特征在于，所述至少一栅极

焊盘和数据焊盘包括：

20 透明导电膜；以及

形成在透明导电膜上、暴露出至少一部分透明导电膜的栅极金属膜。

4、按照权利要求 3 所述的液晶显示面板，其特征在于，所述栅极金属膜

包含至少一种钼 (Mo)、铜 (Cu)、钛 (Ti) 和钽 (Ta)。

25 5、按照权利要求 1 所述的液晶显示面板，其特征在于，还包括一存储电

容，其包括栅极线和与栅极线重叠并且绝缘的存储电极，所述存储电极连接到

像素电极。

6、按照权利要求 5 所述的液晶显示面板，其特征在于，还包括设在数据

线、存储电极以及薄膜晶体管的源极和漏极下面的半导体图案。

30 7、按照权利要求 6 所述的液晶显示面板，其特征在于，所述焊盘包括连

接到数据线的数据焊盘，该数据焊盘包括透明导电膜和栅极金属膜，所述接触

孔贯穿半导体图案、栅极绝缘膜和栅极金属膜，暴露出数据焊盘的透明导电膜和下基板的一部分。

8、按照权利要求 1 所述的液晶显示面板，其特征在于，还包括公共电极，在公共电极与像素电极之间施加电位差时与像素电极产生一电场；

5 向公共电极提供参考电压的公共焊盘；

由不同于形成公共焊盘的导电层形成的公共电压源线；以及

用于连接公共焊盘和公共电压源线并且暴露出至少一公共焊盘和公共电压源线的端部及其相邻区域的公共接触孔。

9、按照权利要求 1 所述的液晶显示面板，其特征在于，还包括：

10 多个第一短路图案，其中的每个第一短路图案连接到信号线；

连接到第一短路图案的第二短路图案；以及

暴露出第一短路图案之一和第二短路图案的端部及其相邻区域的短路接触孔以电连接第一短路图案之一和第二短路图案。

10、按照权利要求 1 所述的液晶显示面板，其特征在于，还包括在保护膜上以与保护膜相同的图案形成的定向膜。

11、一种薄膜晶体管阵列基板，包括：

防静电装置，包括在非显示区上各自连接到信号线的多个薄膜晶体管，

其特征在于，每一薄膜晶体管包括：

由第一导电层形成的栅极；

20 由第二导电层形成的源极和漏极；

在源极和漏极之间限定沟道的半导体层；

暴露出第一薄膜晶体管的第一导电层和第二薄膜晶体管的第二导电层的相邻部分的第一接触孔；以及

25 在第一接触孔内由第三导电层形成的第一接触电极，连接暴露的第一导电层和暴露的第二导电层。

12、按照权利要求 11 所述的薄膜晶体管阵列基板，其特征在于，各个薄膜晶体管还包括：

第二接触孔，暴露出相应薄膜晶体管的第一导电层和第二导电层的相邻部位；以及

30 在第二接触孔内由第三导电层形成的第二接触电极，连接暴露的第一导

电层和暴露的第二导电层。

13、按照权利要求 11 所述的薄膜晶体管阵列基板，其特征在于，还包括：

用于测试非显示区上的信号线的第一和第二短路棒，

其中，第一和第二短路棒各自包括：

5 形成于连接到信号线的至少一个第一和第二导电层的多个第一和第二短路图案；

形成于与第一短路图案相同的导电层的第一公共短路图案；

形成于不同于第二短路图案的导电层、与第一短路图案交叉的第二公共短路图案；

10 暴露出第二短路图案之一和第二公共短路图案的相邻部分的第三接触孔；以及

形成于第三接触孔内的第三导电层的第三接触电极，连接暴露的第二短路图案和暴露的公共短路图案。

14、按照权利要求 11 所述的薄膜晶体管阵列基板，其特征在于，各接触孔贯穿第一导电层上的栅极绝缘膜和第二导电层上的保护膜，并且各接触电极接触到相应接触孔内的保护膜。

15、按照权利要求 12 所述的薄膜晶体管阵列基板，其特征在于，各接触孔贯穿第一导电层上的栅极绝缘膜和第二导电层上的保护膜，并且各接触电极接触到相应接触孔内的保护膜。

20 16、按照权利要求 13 所述的薄膜晶体管阵列基板，其特征在于，各接触孔贯穿第一导电层上的栅极绝缘膜和第二导电层上的保护膜，并且各接触电极接触到相应接触孔内的保护膜。

17、按照权利要求 11 所述的薄膜晶体管阵列基板，其特征在于，所述半导体层沿第二导电层延伸。

25 18、按照权利要求 12 所述的薄膜晶体管阵列基板，其特征在于，所述半导体层沿第二导电层延伸。

19、按照权利要求 13 所述的薄膜晶体管阵列基板，其特征在于，所述半导体层沿第二导电层延伸。

20、按照权利要求 17 所述的薄膜晶体管阵列基板，其特征在于，各接触孔还暴露出第二导电层下的部分半导体。

21、按照权利要求 18 所述的薄膜晶体管阵列基板，其特征在于，各接触孔还暴露出第二导电层下的部分半导体。

22、按照权利要求 19 所述的薄膜晶体管阵列基板，其特征在于，各接触孔还暴露出第二导电层下的部分半导体。

5 23、按照权利要求 11 所述的薄膜晶体管阵列基板，其特征在于，所述信号线包括至少一条栅极线和数据线。

24、按照权利要求 12 所述的薄膜晶体管阵列基板，其特征在于，所述信号线包括至少一条栅极线和数据线。

10 25、按照权利要求 13 所述的薄膜晶体管阵列基板，其特征在于，所述信号线包括至少一条栅极线和数据线。

26、一种薄膜晶体管阵列基板，包括：

在基板上形成的第一导电层；

在第一导电层上形成的第一绝缘层；

贯穿第一绝缘层暴露出第一导电层和第一导电层的相邻区域的接触孔；

15 以及

通过所述接触孔连接到第一导电层的第二导电层。

27、按照权利要求 26 所述的薄膜晶体管阵列基板，其特征在于，所述第一导电层包括至少一条栅极线和数据线的信号线，而第二导电层包括连接到信号线的焊盘。

20 28、按照权利要求 26 所述的薄膜晶体管阵列基板，其特征在于，还包括：

形成在第一绝缘层上并通过所述接触孔连接到第二导电层的第三导电层；以及

形成在第三导电层上并通过所述接触孔连同第三导电层的相邻部分暴露出来的第二绝缘层。

25 29、按照权利要求 28 所述的薄膜晶体管阵列基板，其特征在于，所述第二导电层形成在由第一和第二绝缘层限定的接触孔内。

30、一种液晶显示面板的制造方法，包括：

提供一滤色片阵列基板；并且

提供一面对滤色片阵列基板的薄膜晶体管阵列基板，并且具有：

30 在下基板上中间为栅极绝缘膜的彼此交叉的栅极线和数据线，

- 5           设置在栅极线和数据线之间交叉点上的薄膜晶体管，

连接到薄膜晶体管的像素电极，

通过接触孔连接到信号线的焊盘，所述信号线包括栅极线或数据线，

所述焊盘形成于透明导电膜，以及

5           设置在与滤色片阵列基板重叠的区域上以暴露出透明导电膜的保护膜；

用密封剂将薄膜晶体管阵列基板与滤色片阵列基板粘接，暴露出包括栅

极焊盘和数据焊盘的焊盘区；并且

用滤色片阵列基板作为掩模去除保护膜以暴露出焊盘区的透明导电膜，

其中的接触孔暴露出至少一个焊盘和信号线的端部及其相邻的区域。

10          31、按照权利要求 30 所述的方法，其特征在于，还包括：

提供一公共电极，在向该公共电极与像素电极之间施加电压时产生一电

场；

提供一向公共电极施加驱动电压的公共电压焊盘；

提供一由不同于形成公共焊盘的导电层形成的公共电压源线；并且

15          提供一公共接触孔用于将公共电压焊盘连接到公共电压源线，并且暴露

出至少一公共电压焊盘和公共电压源线的端部及其相邻区域。

32、按照权利要求 30 所述的方法，其特征在于，还包括：

提供多个第一短路图案，其中第一短路图案之一连接到信号线；

提供一连接到多个第一短路图案的第二短路图案；并且

20          提供一暴露出第一短路图案之一和第二短路图案的端部及其相邻区域的

短路接触孔，以电连接第一短路图案之一和第二短路图案。

33、按照权利要求 30 所述的方法，其特征在于，提供薄膜晶体管阵列基

板包括：

在基板上形成包括栅极线、栅极、栅极焊盘和数据焊盘的栅极图案，以

25          及一像素电极，所述栅极图案包括有透明导电膜；

形成一半导体图案，其具有的接触孔暴露出数据焊盘的端部及其相邻区

域，并在设有栅极图案和像素电极的基板上形成栅极绝缘图案，并且暴露出数

据焊盘、栅极焊盘和像素电极的透明导电膜；

形成一包括数据线、源极、以及通过接触孔连接到设有半导体图案和栅

30          极绝缘图案的基板上的数据焊盘的漏极的数据图案；并且

在设有数据图案的基板上形成保护膜。

34、按照权利要求 33 所述的方法，其特征在于，所述至少一栅极焊盘和数据焊盘包括：

透明导电膜；以及

5 形成在透明导电膜上暴露出至少一部分透明导电膜的栅极金属膜。

35、按照权利要求 34 所述的方法，其特征在于，所述栅极金属膜含有至少一种钼 (Mo)，铜 (Cu)，钛 (Ti) 和钽 (Ta)。

36、一种制造薄膜晶体管阵列基板的方法，包括：

在基板上提供栅极图案和像素电极，所述栅极图案包括栅极线、栅极、10 栅极焊盘和数据焊盘，该栅极图案包括透明导电膜；

在设有栅极图案和像素电极的基板上提供一半导体图案和一栅极绝缘图案，并且暴露出数据焊盘、栅极焊盘和像素电极的至少一部分透明导电膜；

提供一数据图案，其包括数据线、源极以及通过接触孔连接到设有半导体图案和栅极绝缘图案的基板上的数据焊盘的漏极；

15 在整个基板上提供一保护膜用于保护栅极图案、半导体图案、栅极绝缘图案和数据图案构成的薄膜晶体管；

在保护膜上包括栅极焊盘和数据焊盘的焊盘区以外的区域上提供定向膜；并且

20 用定向膜作为掩模去除覆盖焊盘区的保护膜，暴露出焊盘区的透明导电膜，

其中，接触孔暴露出至少一数据焊盘和数据线的端部及其相邻区域。

37、按照权利要求 36 所述的方法，其特征在于，还包括：

提供一在公共电极和像素电极之间施加电位差时和像素电极共同形成电场的公共电极；

25 提供向公共电极施加驱动电压的公共电压焊盘；

用不同于公共焊盘的导电层提供一条公共电压源线；并且

提供一公共接触孔用于将公共电压焊盘连接到公共电压源线，并且暴露出至少一公共电压焊盘和公共电压源线的端部及其相邻区域。

38、按照权利要求 36 所述的方法，其特征在于，还包括：

30 提供多个第一短路图案，其中第一短路图案之一连接到栅极线和数据线

之一；

提供一连接到第一短路图案的第二短路图案；并且

提供一暴露出第一短路图案之一和第二短路图案的端部及其相邻区域的短路接触孔，以电连接第一短路图案之一和第二短路图案。

5 39、按照权利要求 36 所述的方法，其特征在于，所述至少一栅极焊盘和数据焊盘包括

透明导电膜；以及

形成在透明导电膜上暴露出至少一部分透明导电膜的栅极金属膜。

40、按照权利要求 39 所述的方法，其特征在于，所述栅极金属膜含有至少一种钼 (Mo)，铜 (Cu)，钛 (Ti) 和钽 (Ta)。

41、一种薄膜晶体管阵列基板的制造方法，所述基板包括一防静电装置，该防静电装置包括在非显示区上各自连接到信号线的多个薄膜晶体管，该方法包括：

15 在一基板上提供中间有栅极绝缘膜的第一和第二导电层，以及包括连同信号线的半导体层的薄膜晶体管；

提供覆盖多个薄膜晶体管的保护膜；

提供第一接触孔，贯穿保护膜和栅极绝缘膜暴露出第一薄膜晶体管的第一导电层和第二薄膜晶体管的第二导电层的相邻部分；并且

20 在第一接触孔内提供第三导电层的第一接触电极，将暴露的第一导电层连接到暴露的第二导电层。

42、按照权利要求 41 所述的方法，其特征在于，还包括：

提供第二接触孔，暴露出相应薄膜晶体管的第一导电层和第二导电层的相邻部分；并且

25 在第二接触孔内提供第三导电层的第二接触电极，将暴露的第一导电层连接到暴露的第二导电层。

43、按照权利要求 42 所述的方法，其特征在于，还包括：

用要在非显示区上连接到信号线的至少一个第一和第二导电层形成第一和第二短路棒的第一和第二短路图案；

30 用形成第一短路图案的同一个导电层形成第一短路棒的公共短路图案，共同连接到第一短路图案；

用不同于形成第二短路图案的导电层的导电层形成与第一短路图案交叉的第二短路棒的公共短路图案；

形成贯穿保护膜和栅极绝缘膜的第三接触孔，暴露出第二短路棒的第二短路图案和公共短路图案的相邻部分；并且

5 在第三接触孔内形成第三导电层的第三接触电极，用于将暴露的第二短路图案连接到第二短路棒暴露的公共短路图案。

44、按照权利要求 41 所述的方法，其特征在于，所述形成第一接触孔和第一接触电极包括：

在保护膜上形成光刻胶图案；

10 蚀刻保护膜和通过光刻胶图案暴露出的栅极绝缘膜；

在设有光刻胶图案的基板上形成第三导电层；并且

去除光刻胶图案连同上面的第三导电层。

45、按照权利要求 42 所述的方法，其特征在于，所述所述形成各个接触孔和接触电极包括：

15 在保护膜上形成光刻胶图案；

蚀刻保护膜和通过光刻胶图案暴露出的栅极绝缘膜；

在设有光刻胶图案的基板上形成第三导电层；并且

去除光刻胶图案连同上面的第三导电层。

46、按照权利要求 43 所述的方法，其特征在于，所述形成各个接触孔和接触电极包括：

在保护膜上形成光刻胶图案；

蚀刻保护膜和通过光刻胶图案暴露出的栅极绝缘膜；

在设有光刻胶图案的基板上形成第三导电层；并且

去除光刻胶图案连同上面的第三导电层。

25 47、按照权利要求 41 所述的方法，其特征在于，所述提供各个薄膜晶体管包括：

用第一导电层形成薄膜晶体管的栅极；

形成栅极绝缘膜；

形成半导体层；并且

30 用第二导电层形成薄膜晶体管的源极和漏极。

48、按照权利要求 42 所述的方法，其特征在于，所述提供各个薄膜晶体管包括：

用第一导电层形成薄膜晶体管的栅极；

形成栅极绝缘膜；

5 形成半导体层；并且

用第二导电层形成薄膜晶体管的源极和漏极。

49、按照权利要求 43 所述的方法，其特征在于，所述提供各个薄膜晶体管包括：

用第一导电层形成薄膜晶体管的栅极；

10 形成栅极绝缘膜；

形成半导体层；并且

用第二导电层形成薄膜晶体管的源极和漏极。

50、按照权利要求 47 所述的方法，其特征在于，所述半导体层及源极和漏极用同一掩模形成，并且该半导体层沿着第二导电层延伸。

15 51、按照权利要求 48 所述的方法，其特征在于，所述半导体层及源极和漏极用同一掩模形成，并且该半导体层沿着第二导电层延伸。

52、按照权利要求 49 所述的方法，其特征在于，所述半导体层及源极和漏极用同一掩模形成，并且该半导体层沿着第二导电层延伸。

53、按照权利要求 50 所述的方法，其特征在于，所述第一接触孔还暴露出第二导电层下面的部分半导体。

20 54、按照权利要求 51 所述的方法，其特征在于，所述各接触孔还暴露出第二导电层下面的部分半导体。

55、按照权利要求 52 所述的方法，其特征在于，所述各接触孔还暴露出第二导电层下面的部分半导体。

25 56、按照权利要求 47 所述的方法，其特征在于，所述形成各信号线包括：连同栅极形成第一导电层的栅极线；并且

连同源极和漏极形成第二导电层的数据线。

57、按照权利要求 48 所述的方法，其特征在于，所述形成各信号线包括：连同栅极形成第一导电层的栅极线；并且

30 连同源极和漏极形成第二导电层的数据线。

58、按照权利要求 49 所述的方法，其特征在于，形成各信号线包括：

连同栅极形成第一导电层的栅极线；并且

连同源极和漏极形成第二导电层的数据线。

5 59、一种薄膜晶体管阵列基板的制造方法，包括：

在一基板上提供第一导电层；

在第一导电层上提供第一绝缘层；

提供一贯穿第一绝缘层的接触孔，暴露出第一导电层和第一导电层的相邻部分；并且

提供通过接触孔连接到第一导电层的第二导电层。

10 60、按照权利要求 59 所述的方法，其特征在于，所述在基板上提供第一导电层包括在基板上形成至少一条信号线，该信号线是至少一条栅极线和数据线，而提供连接到第一导电层的第二导电层包括形成连接到信号线的焊盘。

61、按照权利要求 59 所述的方法，其特征在于，还包括：

提供形成在第一绝缘膜上的第三导电层，并且通过接触孔连接到第二导15 电层；以及

提供形成在第三导电层上的第二绝缘层，并且连同第三导电层的相邻部分通过接触孔暴露出来。

62、按照权利要求 61 所述的方法，其特征在于，所述第二导电层形成在第一和第二绝缘层所限定的接触孔内。

20 63、一种薄膜晶体管阵列基板的形成方法，该方法包括用最多三个导电层形成多个薄膜晶体管和向薄膜晶体管提供信号的信号线，在各个导电层的至少一部分上按最多三轮掩模工序用绝缘层将导电层隔开。

64、按照权利要求 63 所述的方法，其特征在于，还包括用第一导电层形成第一短路部分，所述第一短路部分将第一组信号线短接到一起，所述第一组25 信号线沿特定方向延伸。

65、按照权利要求 64 所述的方法，其特征在于，还包括用第二导电层形成第二短路部分，所述第二短路部分将第二组信号线短接到一起，该第二组信号线沿特定方向延伸。

66、按照权利要求 65 所述的方法，其特征在于，所述第一和第二导电层30 不同。

## 薄膜晶体管阵列基板和液晶显示面板及它们的制造方法

5 本申请要求享有 2003 年 10 月 14 日和 2003 年 11 月 4 日在韩国递交的韩国专利申请 P2003-71403 和 P2003-77660 号的权益，以上申请可供参考。

### 技术领域

10 本发明涉及到液晶显示器，具体涉及到适合简化工序并且保证可靠性的一种薄膜晶体管阵列基板及其制造方法。本发明还涉及到具有这种基板的液晶显示面板及其制造方法。

### 背景技术

15 液晶显示器 (LCD) 一般是用电场控制液晶的光透射比来显示图像。为此，LCD 包括一具有按矩阵形式设置的液晶单元的液晶显示面板，以及用于驱动液晶显示面板的驱动电路。

液晶显示面板包括彼此面对的薄膜晶体管阵列基板和滤色片基板，注入两个基板之间的液晶，以及用于在两个基板之间保持盒间隙的衬垫料。

20 薄膜晶体管阵列基板由栅极线，数据线，形成在栅极线和数据线的各个交叉点上作为开关器件的薄膜晶体管，按各个液晶单元形成并且连接到薄膜晶体管的像素电极，以及涂覆在上面的定向膜组成。栅极线和数据线通过各个焊盘部分从驱动电路接收信号。薄膜晶体管响应提供到栅极线的扫描信号将提供到数据线的像素信号提供给像素电极。

25 滤色片阵列基板由为各液晶单元形成的滤色片，用于分隔滤色片并且反射外部光的黑矩阵，对液晶单元施加公共参考电压的公共电极，以及涂覆在上面的定向膜组成。

分别制备膜阵列基板和滤色片阵列基板，将它们接合到一起，在二者之间注入液晶，并且将其密封就制成了液晶显示面板。

30 在这种液晶显示器中，薄膜晶体管因其复杂的制造工序而成为增加液晶显示面板制造成本的主要因素。其制造工序包括半导体工序并且需要多轮掩模

工序。为了降低制造成本，希望在制造薄膜晶体管时减少掩模工序的数量。每个掩模工序包括许多独立步骤，诸如膜淀积、清洗、光刻、蚀刻、光刻胶剥离和检测步骤等等。迄今为止，标准的制造工序包括五轮掩模工序。然而已经开发出了包括四轮掩模工序的制造工序。

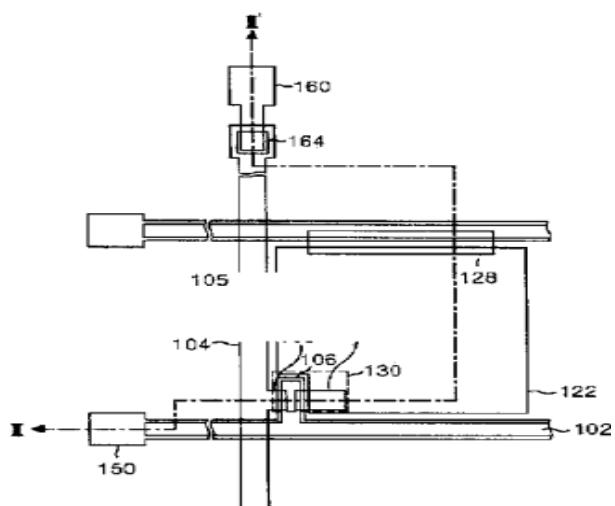

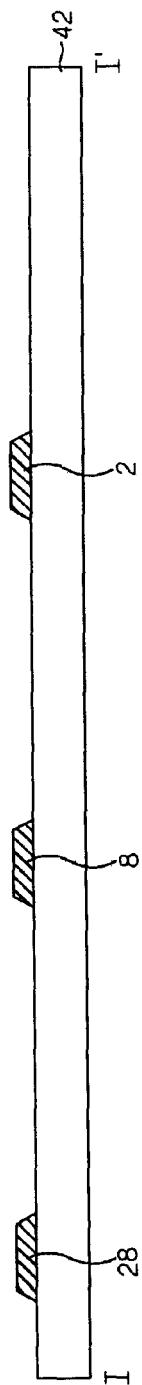

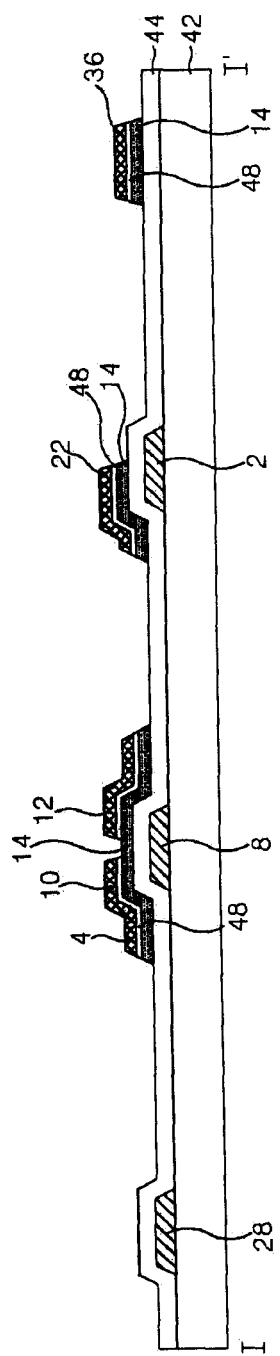

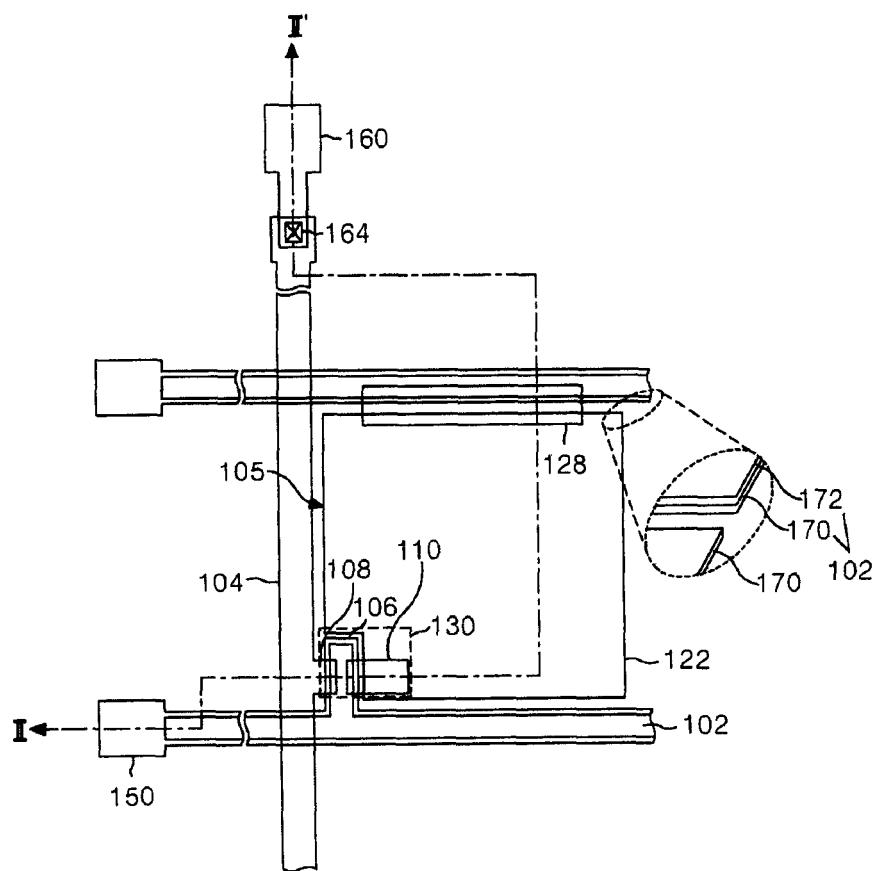

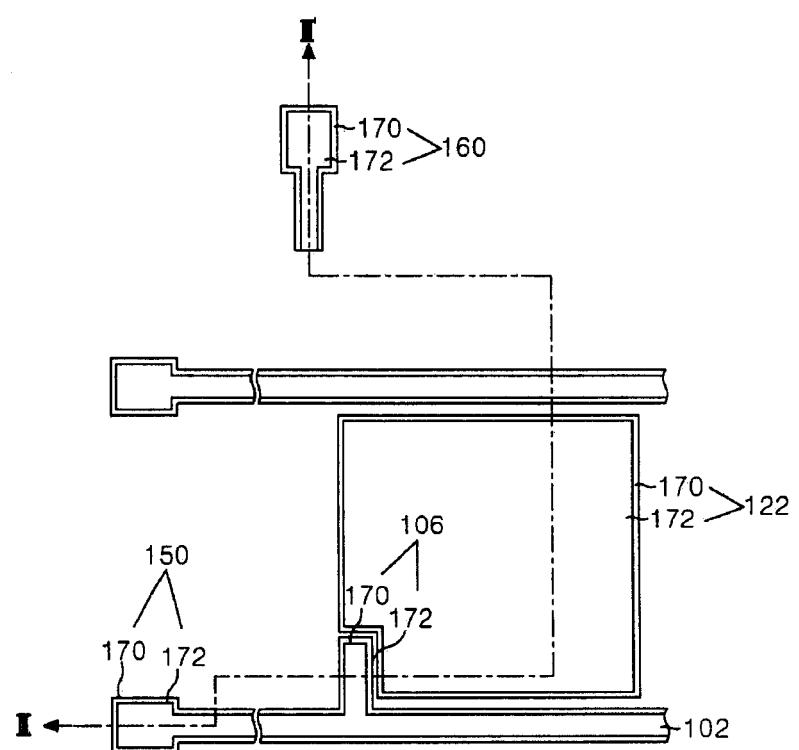

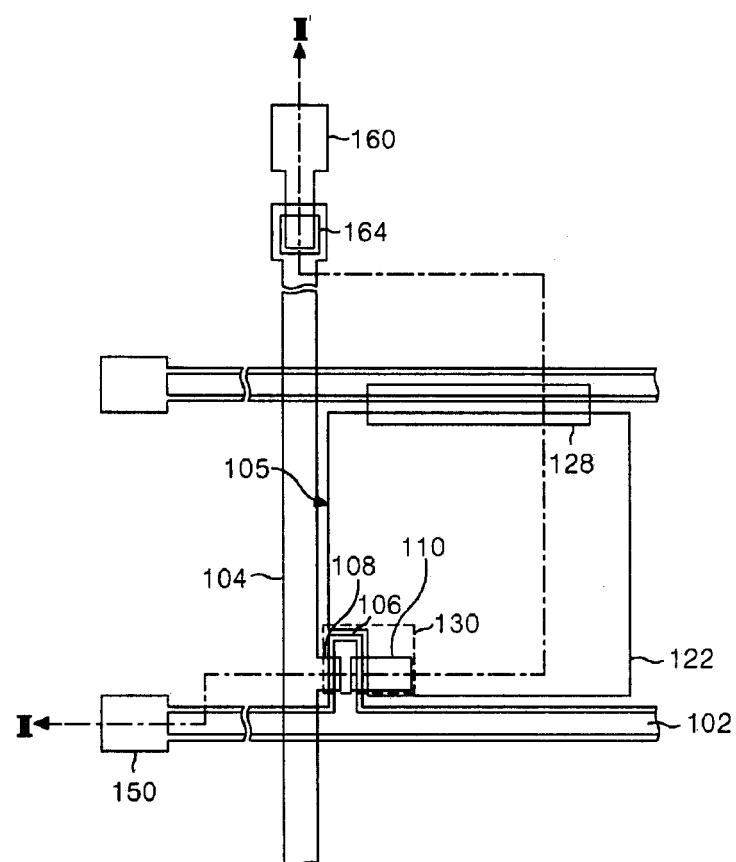

5 图 1 的平面图表示采用四轮掩模工序的薄膜晶体管阵列基板，而图 2 是沿图 1 中 I-I'线提取的薄膜晶体管阵列基板的截面图。

参见图 1 和图 2，薄膜晶体管阵列基板包括设置在下基板 42 上彼此交叉将栅极绝缘膜 44 夹在中间的栅极线 2 和数据线 4，设置在各交叉点上的薄膜晶体管 6，以及设置在具有交叉结构的单元区上的像素电极 18。薄膜晶体管阵 10 阵列基板还包括设置在像素电极 18 与前级栅极线 2 之间的重叠部位上的存储电容 20，连接到栅极线 2 的栅极焊盘部分 26，以及连接到数据线 4 的数据焊盘部分 34。

15 薄膜晶体管 6 响应施加在栅极线 2 上的扫描信号将施加在数据线 4 上的像素信号充入像素电极 18 并且保持。为此，薄膜晶体管 6 包括连接到栅极线 2 的栅极 8，连接到数据线 4 的源极 10，连接到像素电极 18 的漏极 12，以及与栅极 8 重叠并在源极 10 和漏极 12 之间限定一沟道的有源层 14。

20 与源极 10 和漏极 12 重叠并在源极 10 和漏极 12 之间有一沟道部分的有源层 14 还与数据线 4、下数据焊盘电极 36 和存储电极 22 重叠。在有源层 14 上还设有数据线 4、源极 10、漏极 12、下数据焊盘电极 36、存储电极 22 和欧姆接触层 48。

25 像素电极 18 通过贯穿保护膜 50 的第一接触孔 16 连接到薄膜晶体管 6 的漏极 12。充入的像素电压使像素电极 18 相对于设在上基板（未示出）上的公共电极产生一个电位差。这一电位差利用液晶的介电各向异性旋转位于薄膜晶体管阵列基板和上基板之间的液晶，并且向上基板发射从一光源（未示出）通过像素电极 18 输入的光。

30 存储电容 20 由前级栅极线 2、与栅极线 2 重叠的存储电极 22 以及二者之间的栅极绝缘膜 44、有源层 14 和欧姆接触层 48 组成，同时，像素电极 18 与存储电极 22 重叠，二者之间有保护膜 50 并且通过保护膜 50 中限定的第二接触孔 24 连接。存储电容 20 能使充入像素电极 18 的像素信号一直保持到充入下一像素电压。

栅极线 2 通过栅极焊盘部分 26 连接到栅极驱动器（未示出）。栅极焊盘部分 26 由栅极线 2 延伸出的下栅极焊盘电极 28，以及通过贯穿栅极绝缘膜 44 和保护膜 50 的第三接触孔 30 连接到下栅极焊盘电极 28 的上栅极焊盘电极 32 组成。

5 数据线 4 通过数据焊盘部分 34 连接到数据驱动器（未示出）。数据焊盘部分 34 由数据线 4 延伸出的下数据焊盘电极 36，以及通过贯穿保护膜 50 的第四接触孔 38 连接到下数据焊盘电极 36 的上数据焊盘电极 40 组成。

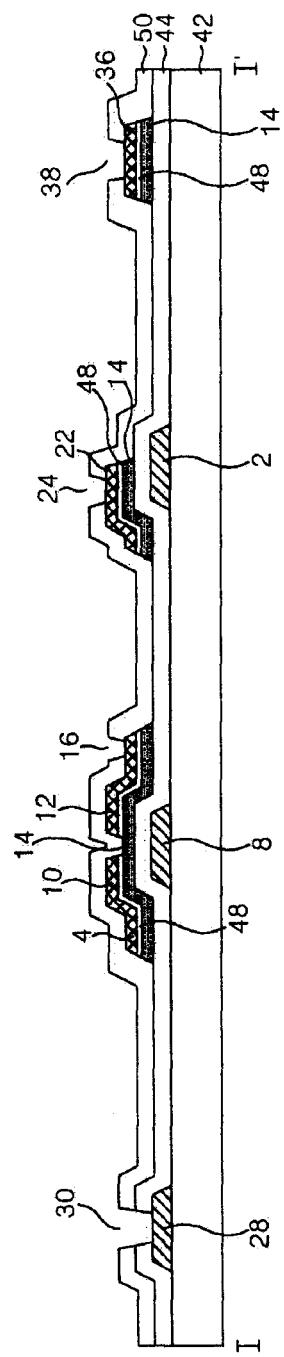

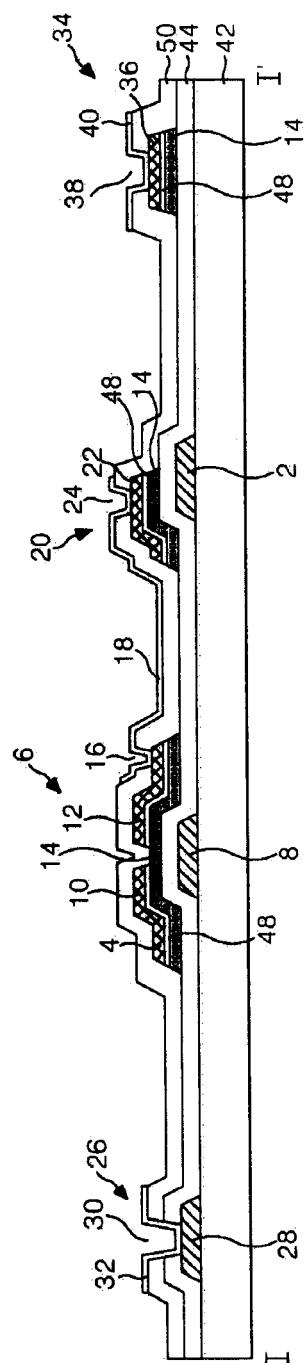

以下要具体参照图 3A 到图 3D 详细描述适合四步掩模工序的具有上述结构的薄膜晶体管基板的一种制造方法。

10 参见图 3A，在下基板 42 上用第一掩模工序形成包括栅极线 2，栅极 8 和下栅极焊盘电极 28 的栅极金属图案。

具体地说，在下基板 42 上用溅射等淀积技术形成一栅极金属层。然后用光刻术对栅极金属层构图并且用第一掩模蚀刻，形成包括栅极线 2、栅极 8 和下栅极焊盘电极 28 的栅极金属图案。栅极金属层具有铬 (Cr)、钼 (Mo) 或 15 一种铝族金属的单层或双层结构。

参见图 3B，栅极绝缘膜 44 被涂覆在设有栅极金属图案的下基板 42 上。进而用第二掩模工序在栅极绝缘膜 44 上设置包括有源层 14 和欧姆接触层 48 的半导体图案，包括数据线 4、源极 10 和漏极 12 的源极/漏极金属图案，以及下数据焊盘电极 36 和上存储电极 22。

20 具体地说，利用诸如等离子体增强化学汽相淀积 (PECVD) 和溅射等淀积技术在设有栅极金属图案的下基板 42 上依次形成栅极绝缘膜 44、非晶硅层、n+ 非晶硅层和源极/漏极金属层。此处的栅极绝缘膜 44 用诸如氮化硅 (SiNx) 或氧化硅 (SiO<sub>x</sub>) 等无机绝缘材料形成。源极/漏极金属选自钼 (Mo)、钛 (Ti)、钽 (Ta) 或钼合金。

25 然后采用第二掩模按光刻术在源极/漏极金属层上形成光刻胶图案。在这种情况下，用一种在薄膜晶体管的沟道部分具有衍射曝光部分的衍射曝光掩模作为第二掩模，使得沟道部分的光刻胶图案具有比源极/漏极图案部分的光刻胶图案较高的高度。

接着用光刻胶图案按湿蚀刻法对源极/漏极金属层构图，形成的源极/漏极 30 金属图案包括数据线 4、源极 10、与源极 10 构成一体的漏极 12 以及存储电极

22。

同时用同一光刻胶图案按干蚀刻法对 n+非晶硅层和非晶硅层构图，形成欧姆接触层 48 和有源层 14。

5 采用灰化法从沟道部分上去除高度比较低的光刻胶图案，然后用干蚀刻法蚀刻源极/漏极金属图案和沟道部分的欧姆接触层 48。这样就暴露出沟道部分的有源层 14，将源极 10 与漏极 12 断开。

然后通过剥离去除留在源极/漏极金属图案组上的光刻胶图案。

参见图 3C，在具有源极/漏极金属图案的栅极绝缘膜 44 上形成包括第一到第四接触孔 16、24、30 和 38 的保护膜 50。

10 具体地说，在具有源极/漏极金属图案的整个栅极绝缘膜 44 上用诸如 PECVD 等淀积技术形成保护膜 50。然后用光刻术对保护膜 50 构图，并且用第三掩模蚀刻得到第一到第四接触孔 16、24、30 和 38。第一接触孔 16 贯穿保护膜 50 暴露出漏极 12，而第二接触孔 24 贯穿保护膜 50 暴露出存储电极 22。第三接触孔 30 贯穿保护膜 50 和栅极绝缘膜 44 暴露出下栅极焊盘电极 28。第 15 四接触孔 38 贯穿保护膜 50 暴露出下数据焊盘电极 36。

保护膜 50 用和栅极绝缘膜相同的无机绝缘材料构成，或是一种有机绝缘材料，例如具有小介电常数的丙烯酸有机化合物，BCB（苯并环丁烯），或是 PFCB（全氟环丁烷）等等。

20 参见图 3D，在保护膜 50 上用第四掩模工序形成包括像素电极 18、上栅极焊盘电极 32 和上数据焊盘电极 40 的透明导电膜图案。

在整个保护膜 50 上用溅射等淀积技术淀积一透明导电膜。然后用光刻术对透明导电膜构图，并且用第四掩模蚀刻形成包括像素电极 18、上栅极焊盘电极 32 和上数据焊盘电极 40 的透明导电膜图案。像素电极 18 通过第一接触孔 16 电连接到漏极 12，同时通过第二接触孔 24 电连接到与前级栅极线 2 重叠的存储电极 22。上栅极焊盘电极 32 通过第三接触孔 30 电连接到下栅极焊盘电极 28。上数据焊盘电极 40 通过第四接触孔 38 的电路连接到下数据焊盘电极 36。此处的透明导电膜用铟锡氧化物 (ITO)、氧化锡 (TO) 或是铟锌氧化物 (IZO) 形成。

30 如上所述，上述的常规薄膜晶体管阵列基板及其制造方法采用四轮掩模工序，从而减少了制造工序的数量，且因此比采用五轮掩模工序的制造技术降

低了制造成本。然而，由于四轮掩模工序仍然存在限制降低成本的复杂制造工序，总希望简化制造工序以进一步降低制造成本。

## 发明内容

5 按照本发明一方面的液晶显示面板包括滤色片阵列基板，其具有在一上基板上形成的滤色片阵列；一薄膜晶体管阵列基板，其具有在一下基板上彼此交叉、且中间有栅极绝缘膜的栅极线和数据线，设置在栅极线和数据线之间交叉点上的薄膜晶体管，连接到薄膜晶体管的像素电极，通过接触孔连接到包括栅极线和/或数据线的信号线上并且由透明导电膜制成的焊盘，以及设置在与10 滤色片阵列基板重叠的区域的保护膜，暴露出焊盘所包括的透明导电膜，并且与对面的滤色片阵列基板粘接，形成的接触孔暴露出焊盘和/或信号线的端部以及与其相邻的区域。

在液晶显示面板中，所述焊盘包括连接到栅极线的栅极焊盘和连接倒数据线的数据焊盘。

15 所述栅极焊盘和/或数据焊盘包括透明导电膜和形成在透明导电膜上的栅极金属膜，暴露出至少一部分透明导电膜。

所述栅极金属膜含有钼 (Mo)，铜 (Cu)，钛 (Ti) 和/或钽 (Ta)。

所述液晶显示面板还包括一存储电容，其包括栅极线和按照与栅极线绝缘并且连接到像素电极的方式与栅极线重叠的存储电极。

20 所述液晶显示面板还包括设在数据线、存储电极以及薄膜晶体管的源极和漏极下面的半导体图案。

所述接触孔贯穿半导体图案、栅极绝缘膜和栅极金属膜，暴露出数据焊盘的透明导电膜和下基板的一部分。

25 所述液晶显示面板还包括连同像素电极产生一电场的公共电极；向公共电极提供参考电压的公共焊盘；用不同于公共焊盘的金属制成的公共电压源线；以及用于连接公共电压焊盘和公共电压源线并且暴露出公共电压焊盘和/或公共电压源线的端部及其相邻区域的公共接触孔。

30 所述液晶显示面板还包括连接到各条信号线的第一短路图案；连接到第一短路图案的第二短路图案；以及暴露出第一和/或第二短路图案的端部及其相邻区域的短路接触孔，以电连接第一短路图案和第二短路图案。

所述液晶显示面板还包括在保护膜上按与保护膜相同的图案形成的定向膜。

按照本发明另一方面的薄膜晶体管阵列基板，包括一防静电装置，其包括在非显示区上各自连接到信号线的多个薄膜晶体管，该多个薄膜晶体管各自包括用第一导电层形成的栅极；用第二导电层形成的源极和漏极；在源极和漏极之间限定一沟道的半导体层；同时暴露出相应薄膜晶体管的第一导电层和另一薄膜晶体管的第二导电层的相邻部分的接触孔；以及在接触孔内形成的第三导电层的接触电极，用于将暴露的第一导电层连接到暴露的第二导电层。

所述多个薄膜晶体管各自还包括另一接触孔，用于同时暴露出第一导电层的相邻部分和相应薄膜晶体管的第二导电层；以及在另一接触孔内形成的第三导电层的另一接触电极，用于将暴露的第一导电层连接到暴露的第二导电层。

所述薄膜晶体管阵列基板的非显示区上还包括用于测试信号线的第一和第二短路棒，该第一和第二短路棒各自包括由连接到信号线的第一和/或第二导电层形成的多个第一和第二短路图案；由要共同连接的多个第一短路图案的同一导电层形成的第一公共短路图案；由不同于多个第二短路图案的导电层形成的与第一短路图案交叉的第二公共短路图案；同时暴露出第二短路图案和第二公共短路图案的相邻部分的另一接触孔；以及在另一接触孔内形成的第三导电层的另一接触电极，用于将暴露的第二短路图案连接到暴露的公共短路图案。

此处的各接触孔贯穿第一导电层上的栅极绝缘膜和第二导电层上的保护膜，并且各接触电极在相应的接触孔内接触到保护膜。

所述半导体层沿第二导电层延伸。

各接触孔还暴露出第二导电层下面的部分半导体。

所述信号线包括栅极线和/或数据线。

按照本发明另一方面的薄膜晶体管阵列基板，包括在一基板上形成的第一导电层；在第一导电层上形成的第一绝缘层；贯穿第一绝缘层同时暴露出第一导电层和第一导电层的相邻区域的接触孔；以及通过该接触孔连接到第一导电层的第二导电层。

此处的第一导电层是栅极线和/或数据线的信号线，而第二导电层是连接

到信号线的焊盘。

所述薄膜晶体管阵列基板还包括形成在第一绝缘层上并通过接触孔连接到第二导电层的第三导电层；以及形成在第三导电层上并通过接触孔连同第三导电层的相邻部分暴露出来的第二绝缘层。

5 所述第二导电层形成在由第一和第二绝缘层限定的接触孔内。

按照本发明的另一方面，一种液晶显示面板的制造方法，包括提供一滤色片阵列基板；并且提供一面对滤色片阵列基板的薄膜晶体管阵列基板，在其下基板上具有中间是栅极绝缘膜的彼此交叉的栅极线和数据线，设置在栅极线和数据线之间交叉点上的薄膜晶体管，连接到薄膜晶体管的像素电极，通过接触孔连接到信号线的焊盘，所述信号线包括用透明导电膜形成的栅极线和/或数据线，以及设置在与滤色片阵列基板重叠的区域上、暴露出透明导电膜的保护膜；用密封剂将薄膜晶体管阵列基板与滤色片阵列基板粘接，暴露出包括栅极焊盘和数据焊盘的焊盘区；并且用滤色片阵列基板作为掩模去除保护膜暴露出的焊盘区的透明导电膜，其中，形成该接触孔暴露出焊盘和/或信号线的端部及其相邻区域。

该方法还包括提供一和像素电极共同形成电场的公共电极；提供一向公共电极施加驱动电压的公共电压焊盘；由不同于公共焊盘的金属提供一公共电压源线；并且提供一公共接触孔用于将公共电压焊盘连接到公共电压源线，并且暴露出所有公共电压焊盘和公共电压源线的端部及其相邻区域。

20 该方法还包括提供一连接到信号线的第一短路图案；提供一同连接到多个短路图案的第二短路图案；并且提供一暴露出第一和/或第二短路图案的端部及其相邻区域的短路接触孔，以电连接第一短路图案和第二短路图案。

所述提供薄膜晶体管阵列基板包括在基板上形成栅极图案，该栅极图案包括栅极线、栅极、各自包括透明导电膜的栅极焊盘和数据焊盘，以及一像素电极；形成一半导体图案，其具有的接触孔暴露出数据焊盘的端部及其相邻区域，以及设有栅极图案和像素电极的基板上的栅极绝缘图案，并且暴露出数据焊盘、栅极焊盘和像素电极所包括的透明导电膜；形成一数据图案，其包括数据线、源极以及通过接触孔连接到设有半导体图案和栅极绝缘图案的基板上的数据焊盘的漏极；并且在设有数据图案的基板上形成保护膜。

30 所述栅极焊盘和/或数据焊盘包括透明导电膜；以及形成在透明导电膜上

暴露出至少一部分透明导电膜的栅极金属膜。

所述栅极金属膜含有钼 (Mo)，铜 (Cu)，钛 (Ti) 和/或钽 (Ta)。

按照本发明的另一方面，一种薄膜晶体管阵列基板的制造方法包括在基板上提供栅极图案和像素电极，所述栅极图案包括栅极线、栅极、栅极焊盘和

5 数据焊盘，其中各自包括透明导电膜；在设有栅极图案和像素电极的基板上提供一半导体图案和一栅极绝缘图案，并且暴露出数据焊盘、栅极焊盘和像素电极所包括的至少一部分透明导电膜；提供一数据图案，其包括数据线、源极以及通过接触孔连接到设有半导体图案和栅极绝缘图案的基板上的数据焊盘的漏极；在整个基板上提供一保护膜用于保护薄膜晶体管；在保护膜上包括栅极

10 焊盘和数据焊盘的焊盘区以外的剩余区域上提供一定向膜；并且用定向膜作为掩模去掉覆盖焊盘区形成的保护膜，暴露出包括在焊盘区内的透明导电膜，所形成的接触孔暴露出数据焊盘和/或数据线的端部及其相邻区域。

该方法还包括提供一和像素电极共同形成一电场的公共电极；提供一向公共电极施加驱动电压的公共电压焊盘；用不同于公共焊盘的金属提供一公共电压源线；并且提供一公共接触孔用于将公共电压焊盘连接到公共电压源线，15 并且暴露出所有公共电压焊盘和公共电压源线的端部及其相邻区域。

该方法还包括提供一连接到信号线的第一短路图案；提供一同连接到多个短路图案的第二短路图案；并且提供一暴露出第一和/或第二短路图案的端部及其相邻区域的短路接触孔，以电连接第一短路图案和第二短路图案。

20 所述栅极焊盘和/或数据焊盘包括透明导电膜；以及形成在透明导电膜上暴露出至少一部分透明导电膜的栅极金属膜。

所述栅极金属膜含有钼 (Mo)，铜 (Cu)，钛 (Ti) 和/或钽 (Ta)。

一种薄膜晶体管阵列基板的制造方法，所述基板包括一防静电装置，它包括在非显示区上各自连接到信号线的多个薄膜晶体管，按照本发明的另一方25 面包括，在一基板上提供中间有栅极绝缘膜的第一和第二导电层，以及包括连同信号线的半导体层的薄膜晶体管；提供一覆盖多个薄膜晶体管的保护膜；提供一接触孔，其贯穿保护膜和栅极绝缘膜同时暴露出相应薄膜晶体管的第一导电层和另一薄膜晶体管的第二导电层的相邻部分；并且在接触孔内提供一第三导电层的接触电极，将暴露的第一导电层连接到暴露的第二导电层。

30 该方法还包括提供另一个接触孔，同时暴露出相应薄膜晶体管的第一导

电层和第二导电层的相邻部分；并且在另一接触孔内提供第三导电层的另一接触电极，将暴露的第一导电层连接到暴露的第二导电层。

该方法还包括由要在非显示区上连接到信号线的第一和/或第二导电层形成第一和第二短路棒的第一和第二短路图案；由要共同连接的多个第一短路图案的同一个导电层形成第一短路棒的公共短路图案；由不同于多个第二短路图案的导电层形成与第一短路图案交叉的第二公共短路图案；形成贯穿保护膜和栅极绝缘膜的另一接触孔，同时暴露出第二短路图案和第二短路棒的公共短路图案的相邻部分；并且在另一接触孔内形成第三导电层的另一接触电极，用于将暴露的第二短路图案连接到第二短路棒暴露的公共短路图案。

在此处，形成相应的接触孔和相应的接触电极包括在保护膜上形成光刻胶图案；蚀刻保护膜和通过光刻胶图案暴露出的栅极绝缘膜；在设有光刻胶图案的基板上形成第三导电层；并且去除光刻胶图案连同上面的第三导电层。

提供多个薄膜晶体管包括用第一导电层形成薄膜晶体管的栅极；形成栅极绝缘膜；形成半导体层；并且用第二导电层形成薄膜晶体管的源极和漏极。

所述半导体层及源极和漏极由同一掩模形成，并且该半导体层沿着第二导电层延伸。

各接触孔还暴露出第二导电层下面的部分半导体。

形成信号线包括连同栅极形成第一导电层的栅极线；并且连同源极和漏极形成第二导电层的数据线。

按照本发明再一方面的一种薄膜晶体管阵列基板的制造方法包括在一基板上提供第一导电层；在第一导电层上提供第一绝缘层；提供一贯穿第一绝缘层的接触孔，同时暴露出第一导电层和第一导电层的相邻部分；并且提供通过接触孔连接到第一导电层的第二导电层。

在基板上提供第一导电层包括在基板上形成栅极线和数据线的至少一条信号线，而提供连接到第一导电层的第二导电层包括连接到信号线的焊盘。

该方法还包括提供形成在第一绝缘膜上的第三导电层，并且通过接触孔连接到第二导电层；以及提供形成在第三导电层上的第二绝缘层，并且连同第三导电层的相邻部分通过接触孔暴露出来。

所述第二导电层形成在第一和第二绝缘层所限定的接触孔内。

## 附图说明

以下要参照附图详细描述本发明的实施例，在附图中：

图 1 的平面图表示常规薄膜晶体管阵列基板的一部分；

图 2 是沿图 1 中的 I-I'线提取的薄膜晶体管阵列基板的截面图；

5 图 3A 到图 3D 的截面图表示图 2 中的薄膜晶体管阵列基板的一种制造方法；

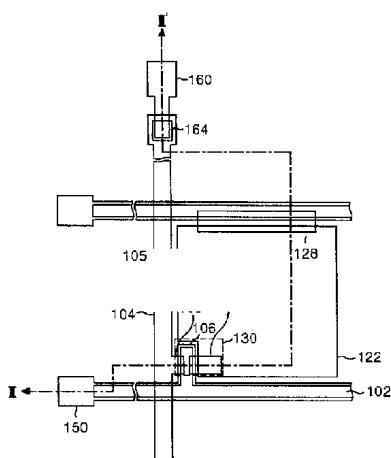

图 4 的平面图表示按照本发明第一实施例的薄膜晶体管阵列基板的结构；

图 5 是沿图 4 中 II-II'线提取的薄膜晶体管阵列基板的截面图；

10 图 6A 到图 6C 的截面图表示图 5 中所示的薄膜晶体管阵列基板的一种制造方法；

图 7 的截面图用于解释用于将图 6B 中所示的数据焊盘连接到数据线的接触孔区域的底切现象；

图 8 的平面图表示按照本发明第二实施例的薄膜晶体管阵列基板的结构；

图 9 是沿图 8 中 III-III'线提取的薄膜晶体管阵列基板的截面图；

15 图 10A 和图 10B 的平面图和截面图分别用于解释按照本发明第二实施例的薄膜晶体管阵列基板制造方法中的第一掩模工序；

图 11A 和图 11B 的平面图和截面图分别用于解释按照本发明第二实施例的薄膜晶体管阵列基板制造方法中的第二掩模工序；

20 图 12A 和图 12B 的平面图和截面图分别用于解释按照本发明第二实施例的薄膜晶体管阵列基板制造方法中的第三掩模工序；

图 13A 到图 13E 的截面图用于详细解释图 12A 和图 12B 中所示的第三掩模工序；

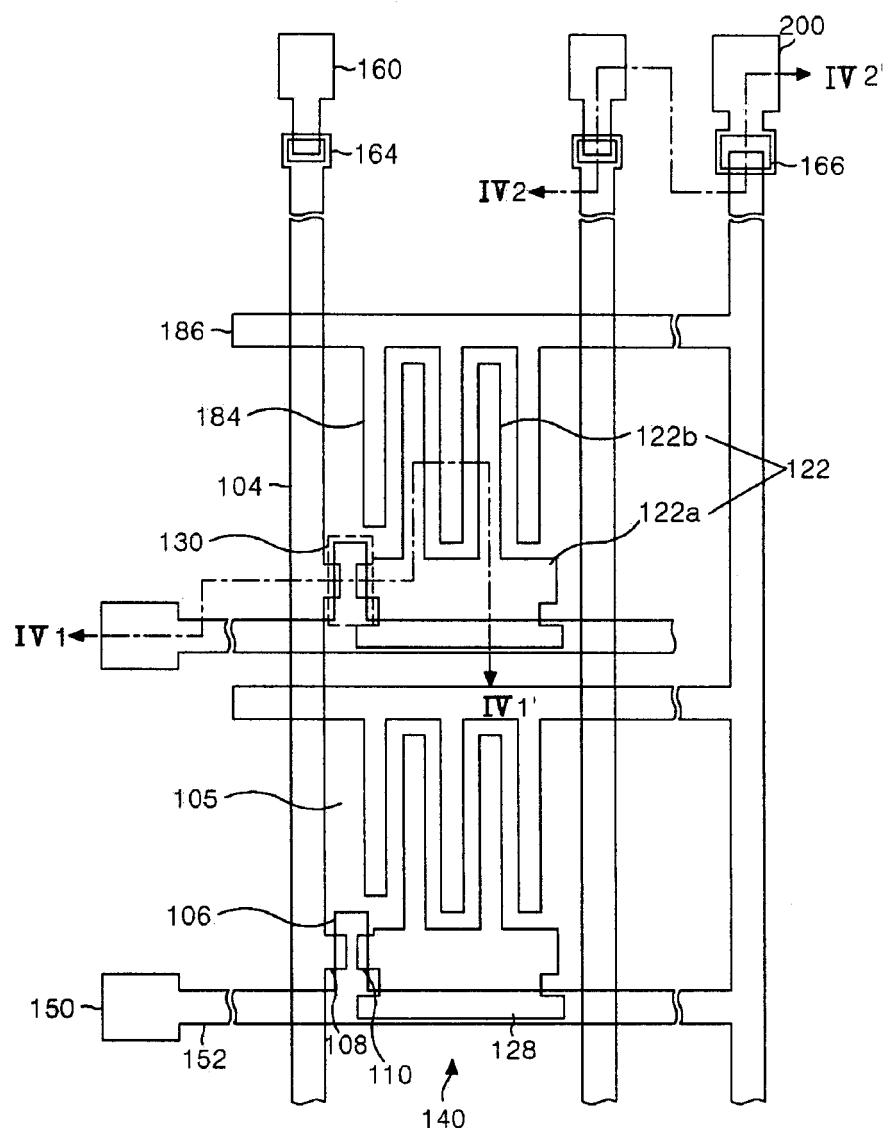

图 14 的平面图表示按照本发明第三实施例的薄膜晶体管阵列基板的结构；

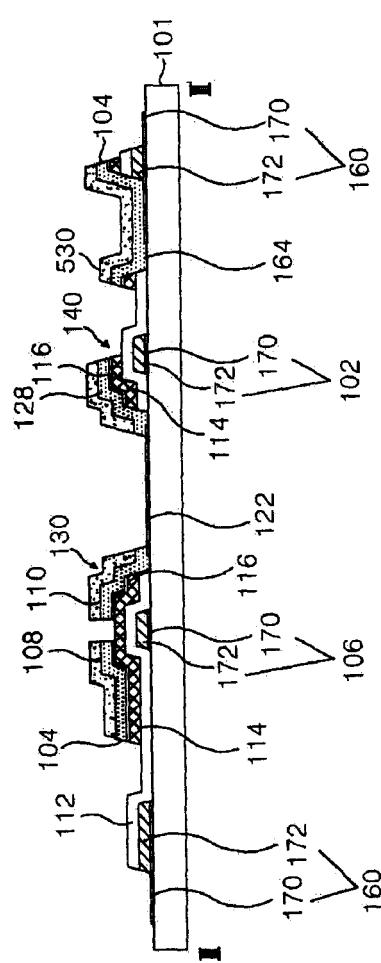

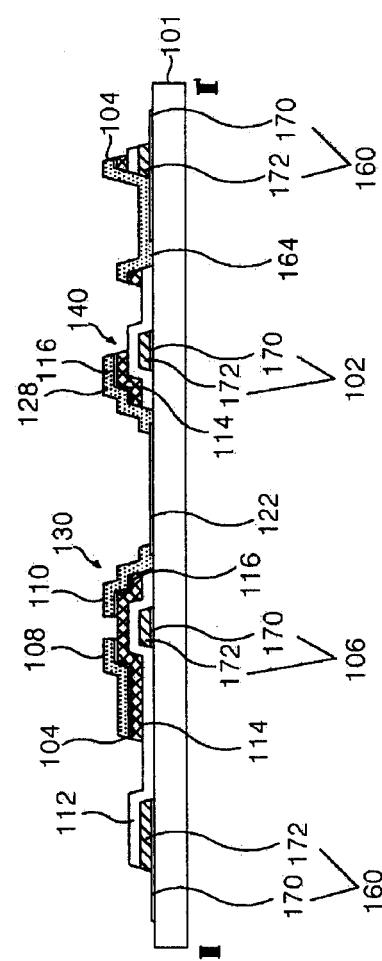

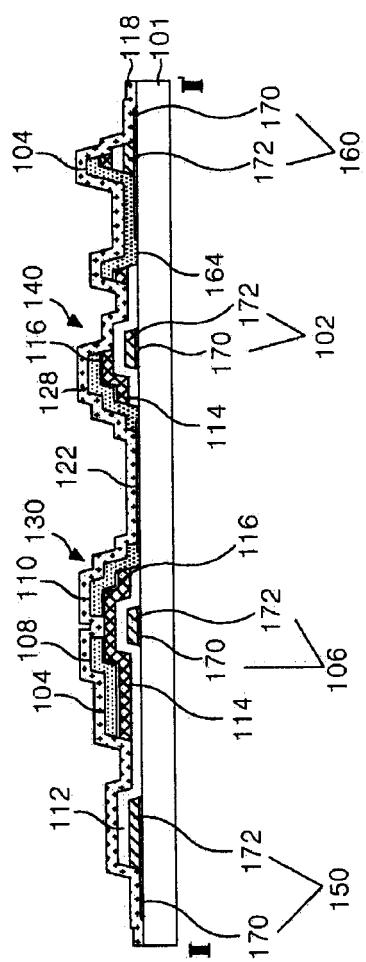

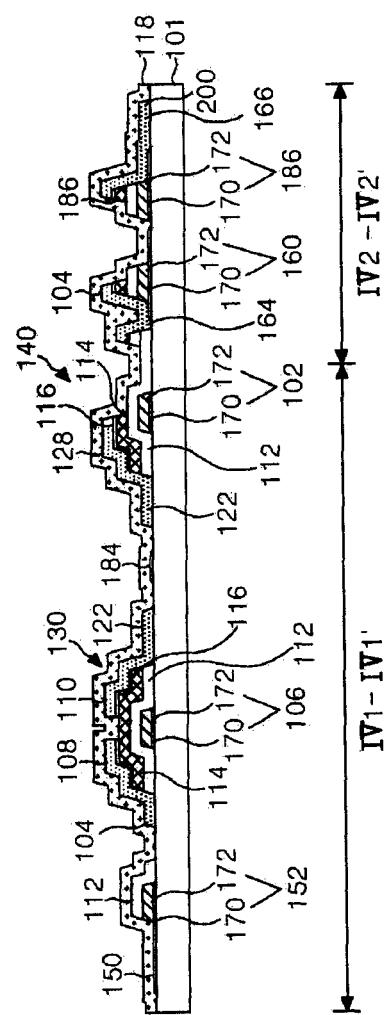

25 图 15 是沿图 14 中 IV1-IV1'线和 IV2-IV2'线提取的薄膜晶体管阵列基板的截面图；

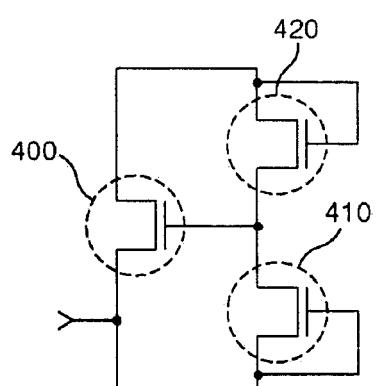

图 16 是防静电装置的等效电路图；

图 17A 和图 17B 的平面图和截面图分别表示薄膜晶体管的防静电装置和短路棒区域；

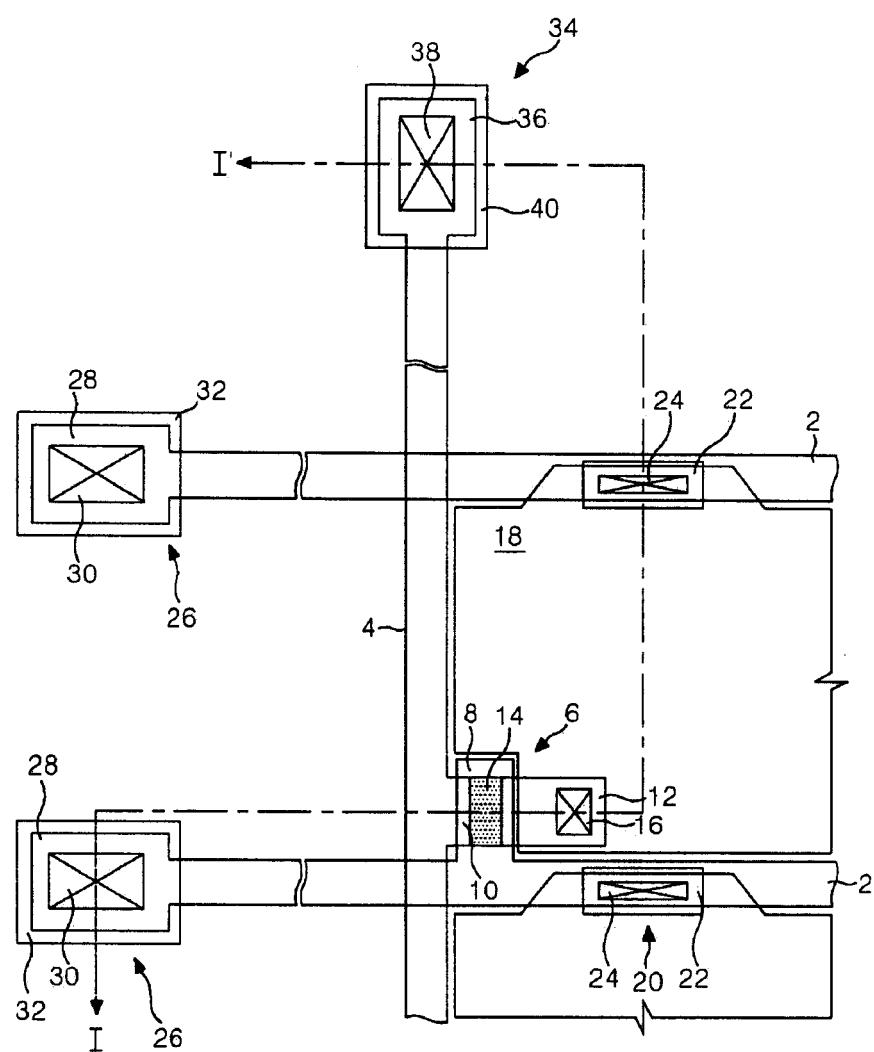

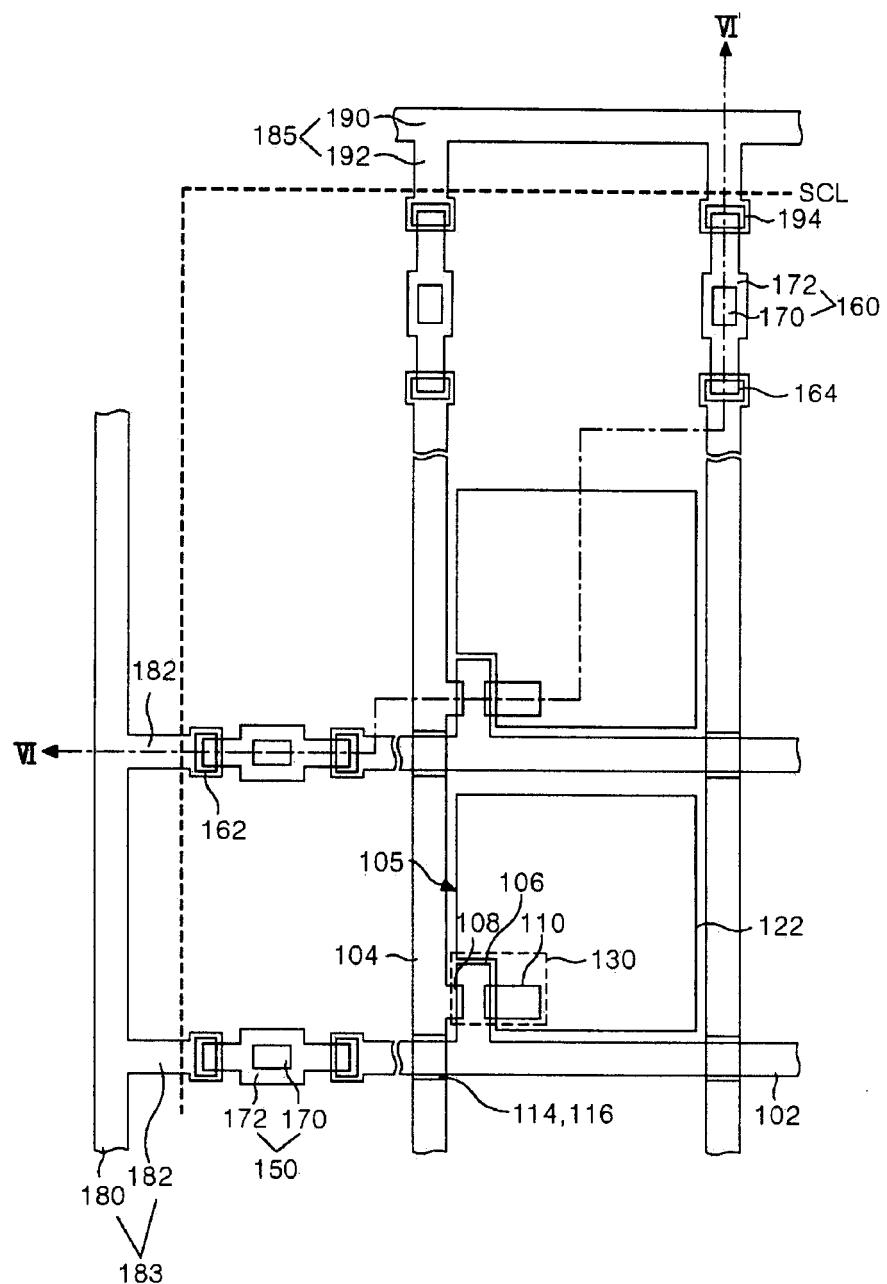

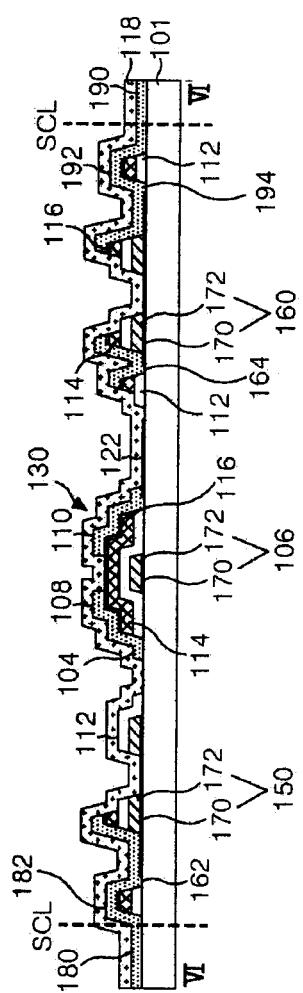

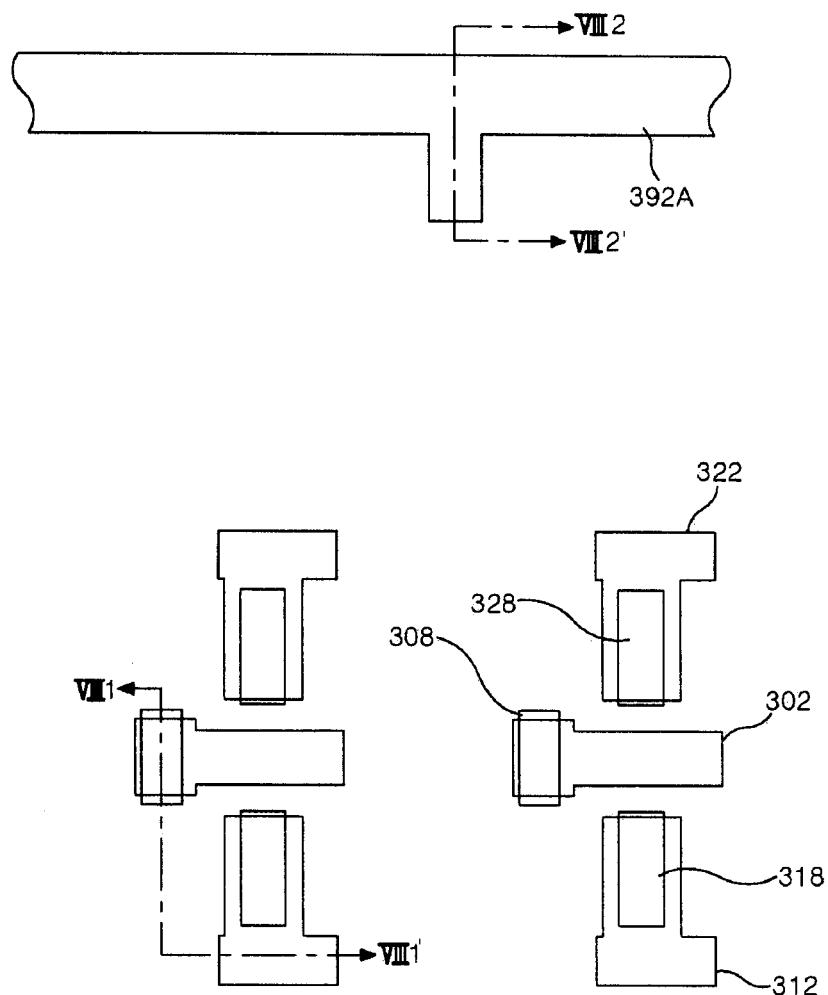

30 图 18 的平面图表示按照本发明第四实施例的薄膜晶体管阵列基板的结

构；

图 19 是沿图 18 中 VI-VI' 线提取的薄膜晶体管阵列基板的截面图；

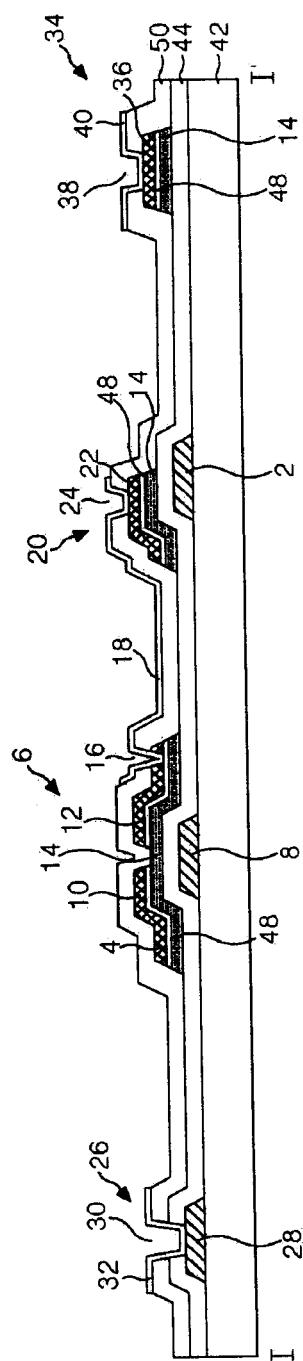

图 20 是包括按照本发明第一到第四实施例的薄膜晶体管阵列基板的一液晶显示面板的截面图；

5 图 21 是包括按照本发明第一到第四实施例的薄膜晶体管阵列基板的另一例液晶显示面板的截面图；

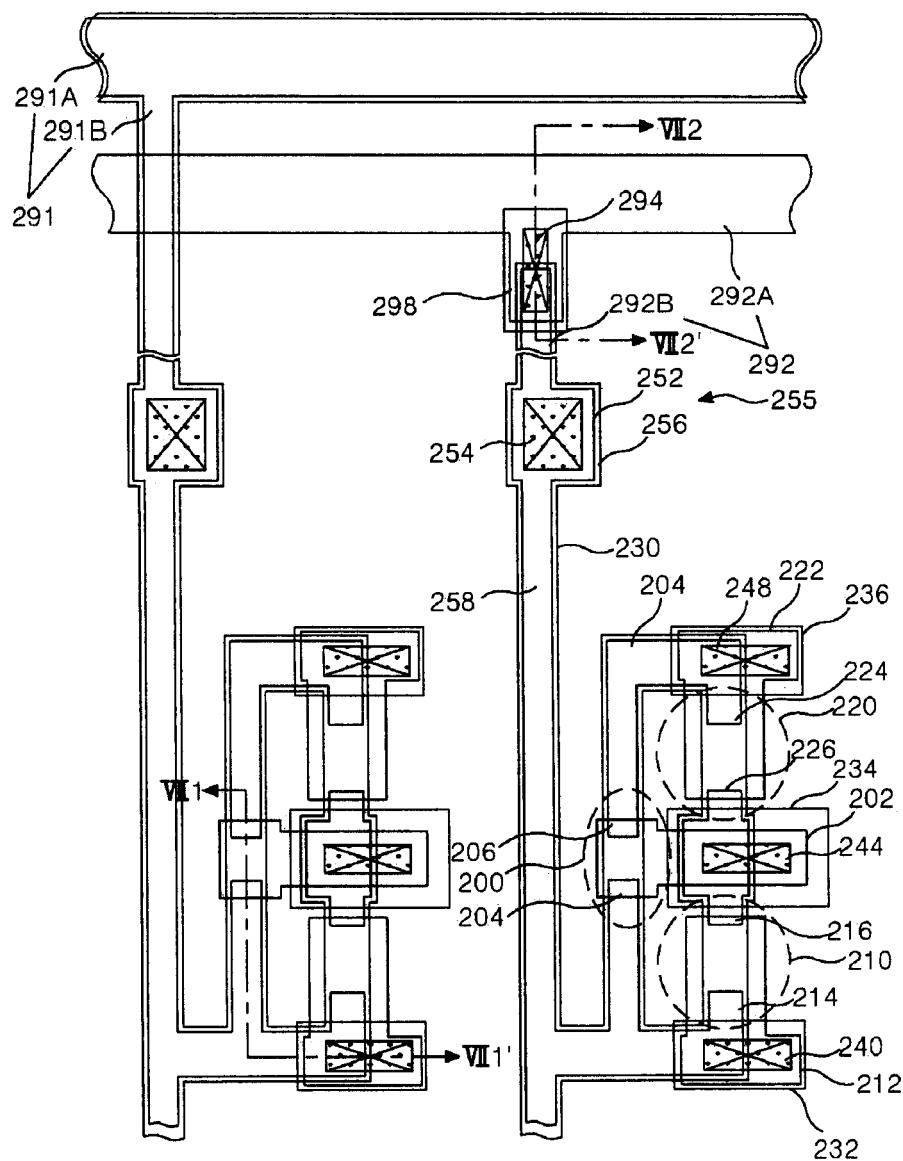

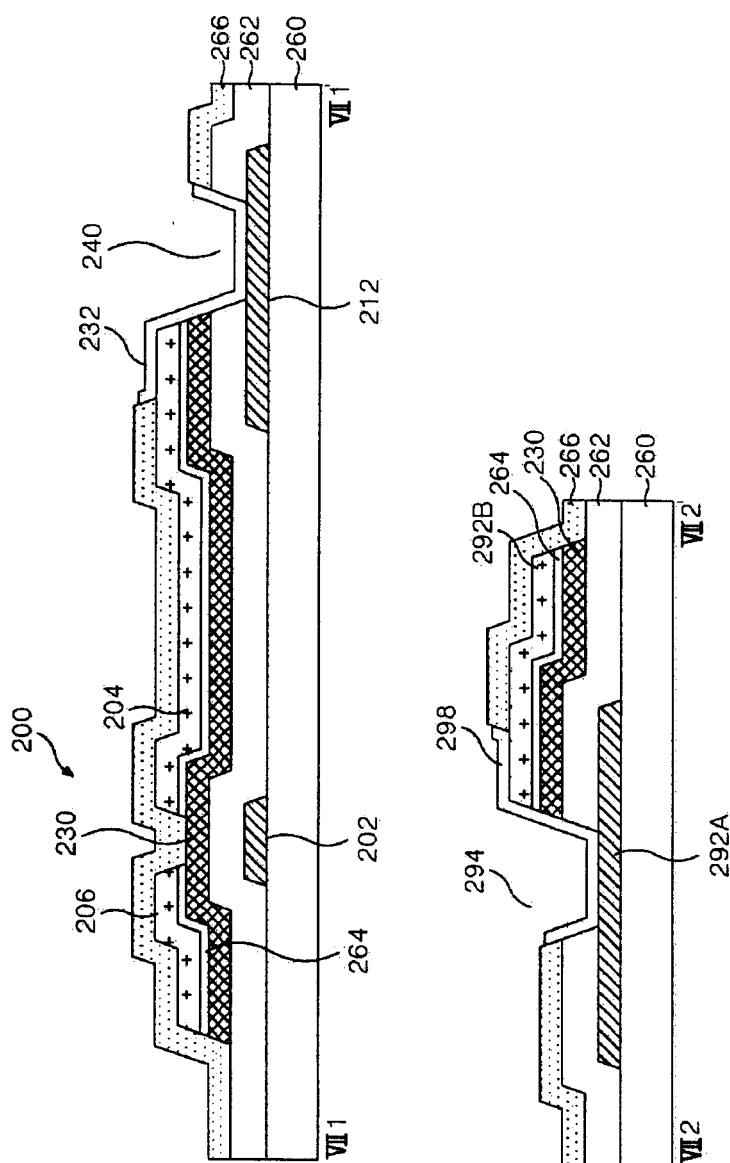

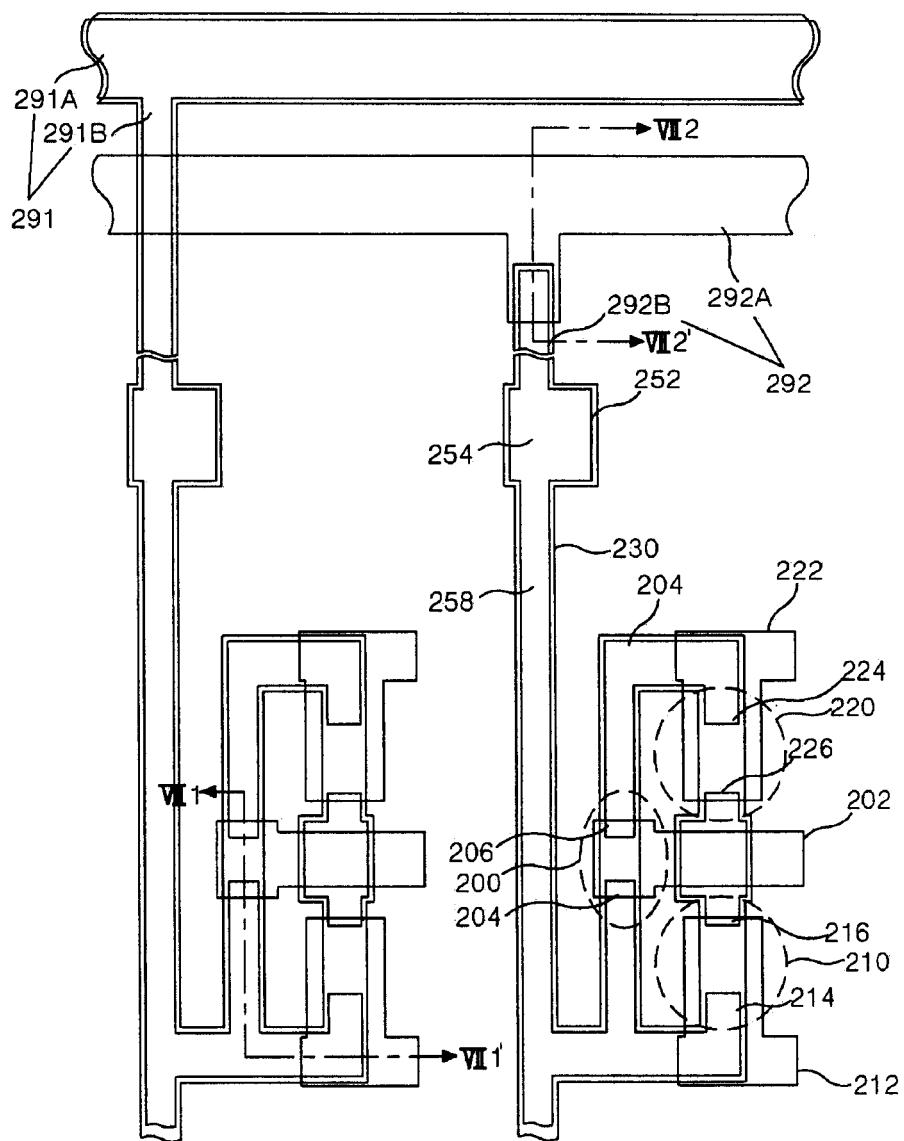

图 22 的平面图表示按照本发明第五实施例的薄膜晶体管阵列基板的防静电装置和短路棒区域；

图 23 是沿图 22 中 VII1-VII1' 线和 VII2-VII2' 线提取的防静电装置和短路

10 棒区域的截面图；

图 24A 和图 24B 的平面图和截面图分别用于解释图 22 和图 23 中所示薄

膜晶体管阵列基板的一种制造方法中的第一掩模工序；

图 25A 和图 25B 的平面图和截面图分别用于解释图 22 和图 23 中所示薄

膜晶体管阵列基板的一种制造方法中的第二掩模工序；

15 图 26A 到图 26D 的截面图用于详细解释第二掩模工序；

图 27A 和图 27B 的平面图和截面图分别用于解释图 22 和图 23 中所示薄

膜晶体管阵列基板的一种制造方法中的第三掩模工序；

图 28A 到图 28D 的截面图用于详细解释第三掩模工序；

图 29 的平面图表示按照本发明第六实施例的薄膜晶体管阵列基板的防静

20 电装置和短路棒区域；

图 30 是沿图 29 中 VIII1-VIII1' 线和 VIII2-VIII2' 线提取的防静电装置和短

路棒区域的截面图；

图 31A 和图 31B 的平面图和截面图分别用于解释图 29 和图 30 中所示薄

膜晶体管阵列基板的一种制造方法中的第一掩模工序；

25 图 32A 和图 32B 的平面图和截面图分别用于解释图 29 和图 30 中所示薄

膜晶体管阵列基板的一种制造方法中的第二掩模工序；

图 33A 和图 33B 的平面图和截面图分别用于解释图 29 和图 30 中所示薄

膜晶体管阵列基板的一种制造方法中的第三掩模工序；

图 34A 和图 34B 的平面图和截面图分别用于解释图 29 和图 30 中所示薄

30 膜晶体管阵列基板的一种制造方法中的第四掩模工序；以及

图 35A 到图 35D 的截面图用于详细解释第四掩模工序。

### 具体实施方式

以下要具体描述在附图中例举的本发明的实施例。

5 以下要具体参照图 4 到 35D 来详细解释本发明的实施例。

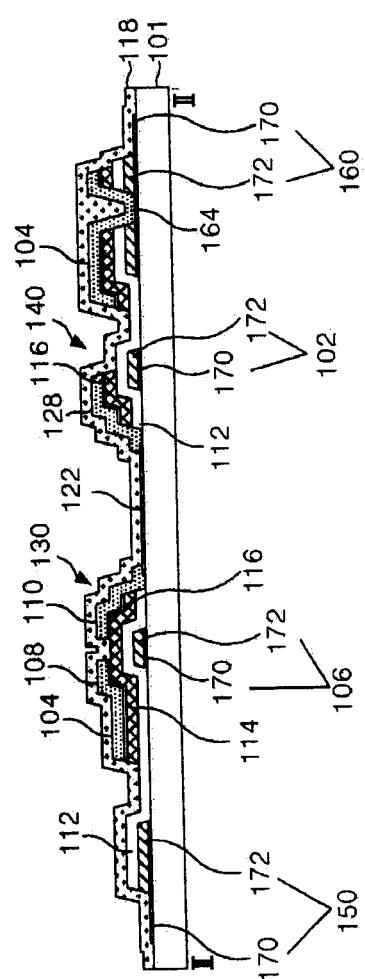

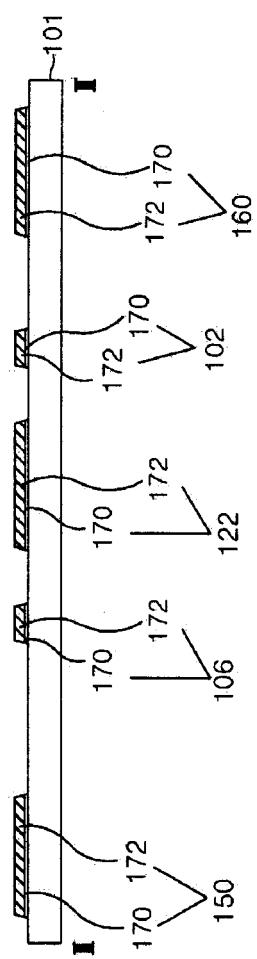

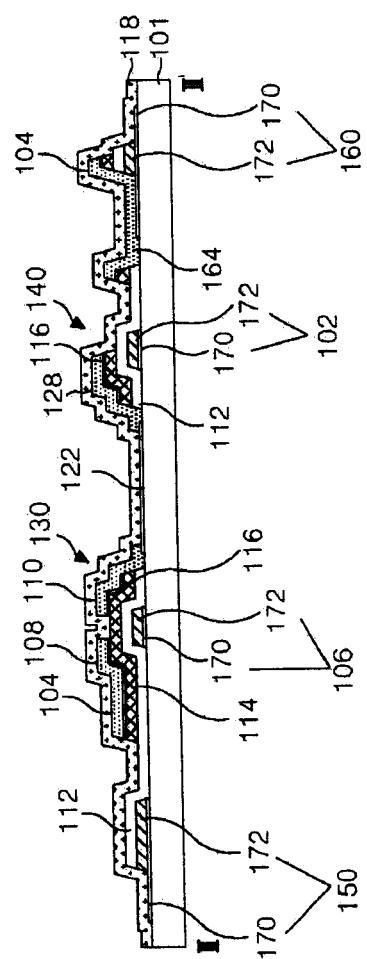

图 4 的平面图表示按照本发明第一实施例的薄膜晶体管阵列基板的结构，而图 5 是沿图 4 中 II-II' 线提取的薄膜晶体管阵列基板的截面图。

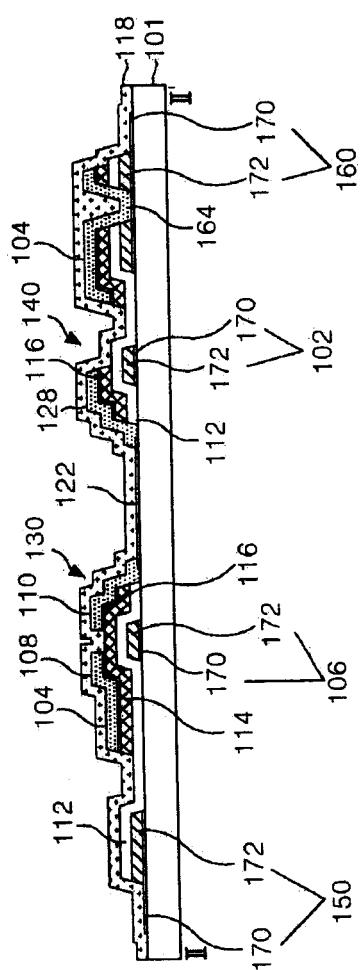

10 参见图 4 和图 5，薄膜晶体管阵列基板包括在下基板 101 上彼此交叉并且中间有一个栅极绝缘膜 112 的栅极线 102 和数据线 104，设在各个交叉点上的薄膜晶体管 130，以及设在具有交叉结构的像素区 105 上的像素电极 122，设在像素电极 122 与栅极线 102 的重叠部分的存储电容 140，从栅极线 102 上延伸的栅极焊盘 150，以及从数据线 104 上延伸的数据焊盘 160。

15 薄膜晶体管 130 响应栅极线 102 上的扫描信号允许将数据线 104 上的数据信号充入像素电极 122 并且保持。为此，薄膜晶体管 130 包括连接到栅极线 102 的栅极 106，连接到数据线 104 的源极 108，以及连接到像素电极 122 的漏极 110。薄膜晶体管 130 还包括与栅极 106 重叠的半导体图案 114 和 116，并且在栅极和半导体图案中间有一栅极绝缘图案 112，并且在源极 108 和漏极 110 之间限定了一沟道。

20 包括栅极 106 和栅极线 102 的栅极图案具有透明导电膜 170，以及设置在透明导电膜 170 上的一栅极金属膜 172 的结构。

25 半导体图案在源极 108 和漏极 110 之间形成一沟道，还包括与栅极图案部分重叠且中间是栅极绝缘膜 112 的一有源层 114。半导体图案形成在有源层 114 上，并且包括数据线 104、存储电极 128、源极 108 和漏极 110 以及欧姆接触层 116。这种半导体图案在单元之间独立形成，可以防止因半导体图案在单元之间造成信号干扰。

在像素区 105 内通过直接连接到薄膜晶体管 130 的漏极 110 的透明导电膜 170 形成像素电极 122。

30 这样就能在通过薄膜晶体管 130 施加像素信号的像素电极 122 和提供参考电压的公共电极（未示出）之间形成一垂直电场。这种电场借助液晶分子的介电各向异性旋转滤色片阵列基板和薄膜晶体管阵列基板之间的液晶分子。透

过像素区 105 的光的透射比随着液晶分子的旋转程度而有所不同，从而获得灰度级比例。

存储电容 140 包括栅极线 102 和与栅极线 102 重叠、且直接连接到像素电极 122 的存储电极 128，在栅极线 102 和存储电极 128 的中间是栅极绝缘膜 112、有源层 114 和欧姆接触层 116。存储电容 140 能够将充入像素电极 122 的像素信号稳定保持到充入下一像素电压。

栅极焊盘 150 连接到一栅极驱动器（未示出），对栅极线 102 施加由栅极驱动器产生的栅极信号。栅极焊盘 150 具有暴露出从栅极线 102 延伸的透明导电膜 170 的结构。

数据焊盘 160 连接到一数据驱动器（未示出），对数据线 104 施加由数据驱动器产生的数据信号。为此，数据焊盘 160 通过数据接触孔 164 电连接到形成于数据金属层的数据线 104。数据焊盘 160 包括透明导电膜 150，以及在形成在与数据线 104 重叠的区域内的透明导电膜 170 上的栅极金属膜 172。数据接触孔 164 的宽度比数据焊盘 160 要窄，并且贯穿欧姆接触层 116、有源层 114、栅极绝缘图案 112 和数据焊盘 160 的栅极金属膜 172，暴露出数据焊盘 160 的透明导电膜 170。

图 6A 到图 6C 的截面图表示按照本发明第一实施例的薄膜晶体管阵列基板的一种制造方法。

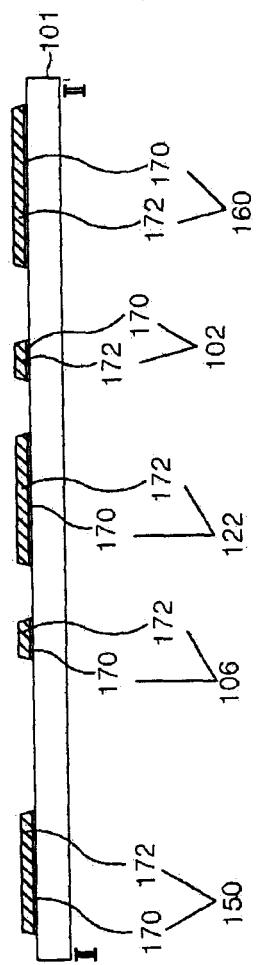

参见图 6A，用第一掩模工序在下基板 101 上形成各自具有双层结构的像素电极 122 和包括栅极线 102，栅极 106，栅极焊盘 150 及数据焊盘 160 的栅极图案。

具体地说，用溅射等淀积技术依次形成透明导电膜 170 和栅极金属膜 172。此处的透明导电膜 170 用诸如 ITO、TO、ITZO、IZO 等透明导电材料制成，而栅极金属膜 172 用诸如铝族金属等金属材料制成，包括铝/钕 (AlNd)、钼 (Mo)、铜 (Cu)、铬 (Cr)、钽 (Ta)、钛 (Ti) 等。然后用光刻术对透明导电膜 170 和栅极金属膜 172 构图，并且用第一掩模进行蚀刻，形成各自具有双层结构的栅极线 102，栅极 106，栅极焊盘 150 和数据焊盘 160，以及包括栅极金属膜 172 的像素电极 122。

参见图 6B，在具有栅极图案的下基板 101 上用第二掩模工序形成栅极绝缘图案 112 和包括有源层 114 和欧姆接触层 116 的半导体图案。去除包含在数

据焊盘 160、栅极焊盘 150 和像素电极 122 中的栅极金属膜 172，暴露出透明导电膜 170。进而形成栅极绝缘图案 112、半导体图案 114 和 116 以及贯穿数据焊盘 160 的栅极金属膜 172 的数据接触孔 164。

具体地说，在设有栅极图案的下基板 101 上用 PECVD、溅射等淀积技术 5 依次形成栅极绝缘膜及第一和第二半导体层。此处的栅极绝缘膜用氮化硅 (SiNx)、氧化硅 (SiOx) 等无机绝缘材料制成。第一半导体层用没有掺杂 (即非掺杂) 的非晶硅制成，而第二半导体层用掺杂有 N-型或 P-型杂质的非晶硅制成。然后用光刻术对栅极绝缘膜及第一和第二半导体层构图，并且用第二掩模进行蚀刻，形成包括有源层 114 和欧姆接触层 116 的半导体图案，以及和半导体图案具有相同图案的栅极绝缘图案 112。在这种情况下，形成的半导体图案和栅极绝缘图案 112 暴露出像素电极 122、栅极焊盘 150 和数据焊盘 160。

接着用栅极绝缘图案 112 及半导体图案 114 和 116 作为掩模用湿蚀刻法去除暴露的栅极金属膜 172。换句话说，就是去除栅极焊盘 150，数据焊盘 160 和像素电极 122 中所包括的栅极金属膜 172，暴露出透明导电膜 170。接着形成数据接触孔 164，暴露出需要连接到数据线 104 的区域内的数据焊盘 160 所包括的那部分透明导电膜 170。

参见图 6C，在设有栅极绝缘图案 112 及半导体图案 114 和 116 的下基板 101 上用第三掩模工序形成包括数据线 104、源极 108、漏极 110 和存储电极 128 的数据图案。

具体地说，在设有半导体图案的下基板 101 上用溅射等淀积技术依次形成数据金属层。数据金属层用钼 (Mo)、铜 (Cu) 等金属制成。然后按湿蚀刻法用光刻胶图案对数据金属层构图，光刻胶图案是采用第三掩模用光刻术形成的阶梯覆层，从而形成包括存储电极 128、数据线 104、连接到数据线 104 的源极 108、以及漏极 110 的数据图案。进而沿着数据图案按干蚀刻法用光刻胶图案形成有源层 114 和欧姆接触层 116。在此时去除位于剩余区域 (有源层 114 和欧姆接触层 116 与数据图案发生重叠的区域以外的区域) 内的有源层 114 和欧姆接触层 116。这样能减少或防止单元之间因包括有源层 114 和欧姆接触层 116 的半导体图案造成的短路。

然后借助于通过灰化已降低高度的光刻胶图案去除在薄膜晶体管沟道部分中形成的数据金属层和欧姆接触层 116，将漏极 110 与源极 108 断开。进而

通过剥离去掉留在数据图案上的光刻胶图案。

接着在设有数据图案的下基板 101 的正面形成一保护膜 118。保护膜 118 用和栅极绝缘膜 112 相同的无机绝缘材料构成，或是一种有机绝缘材料，例如是具有小介电常数的丙烯酸有机化合物，BCB（苯并环丁烯）或是 PFCB（全 5 氟环丁烷）等等。

同时，在按照本发明第一实施例的薄膜晶体管阵列基板制造方法的第二掩模工序中，是用干蚀刻法对栅极绝缘膜及第一和第二半导体层构图，然后用栅极绝缘图案暴露出栅极金属膜并且按湿蚀刻法去除半导体图案。此时，栅极绝缘图案 112、贯穿栅极绝缘图案 112 的数据接触孔 164、半导体图案 114 和 10 116、以及数据焊盘 160 的栅极金属膜 172 将数据线 104 连接到数据焊盘 160。在这种情况下，栅极绝缘图案 112 及半导体图案 114 和 116 具有不同于栅极金属膜的蚀刻特性。因此，如图 7 所示，出现贯穿栅极绝缘图案 112 及半导体图案 114 和 116 的数据接触孔 164 的第一宽度 w1 比贯穿栅极金属膜 172 的数据接触孔 164 的第二宽度 w2 窄的底切现象。由于底切现象会造成数据线 104 在 15 数据接触孔 164 的栅极金属膜 172 附近变短，数据线 104 不能电连接到数据焊盘 160。这样，来自数据焊盘 160 的数据信号就不能提供给数据线 104。

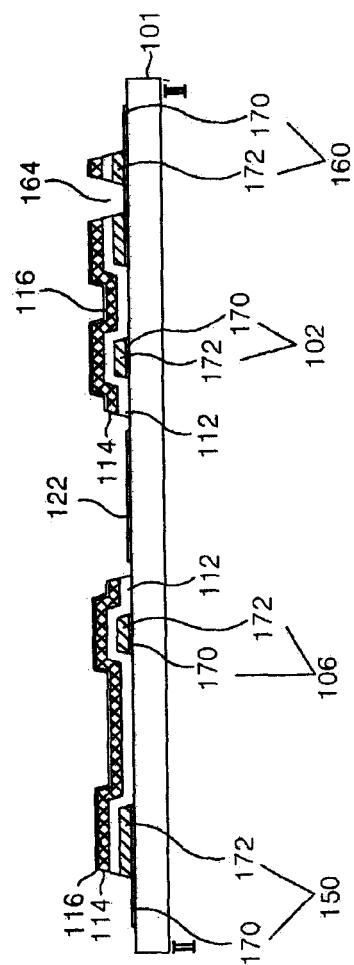

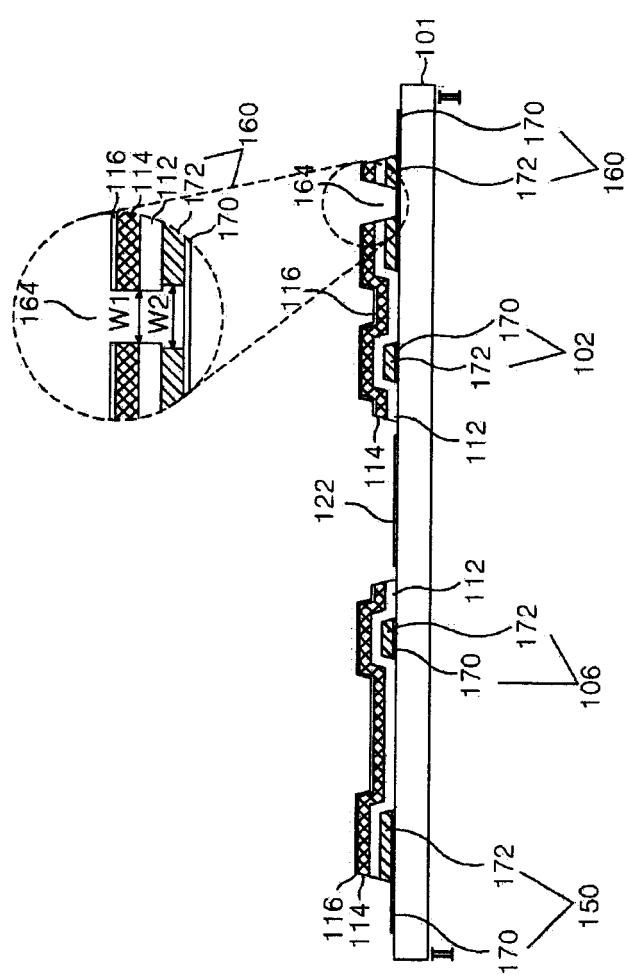

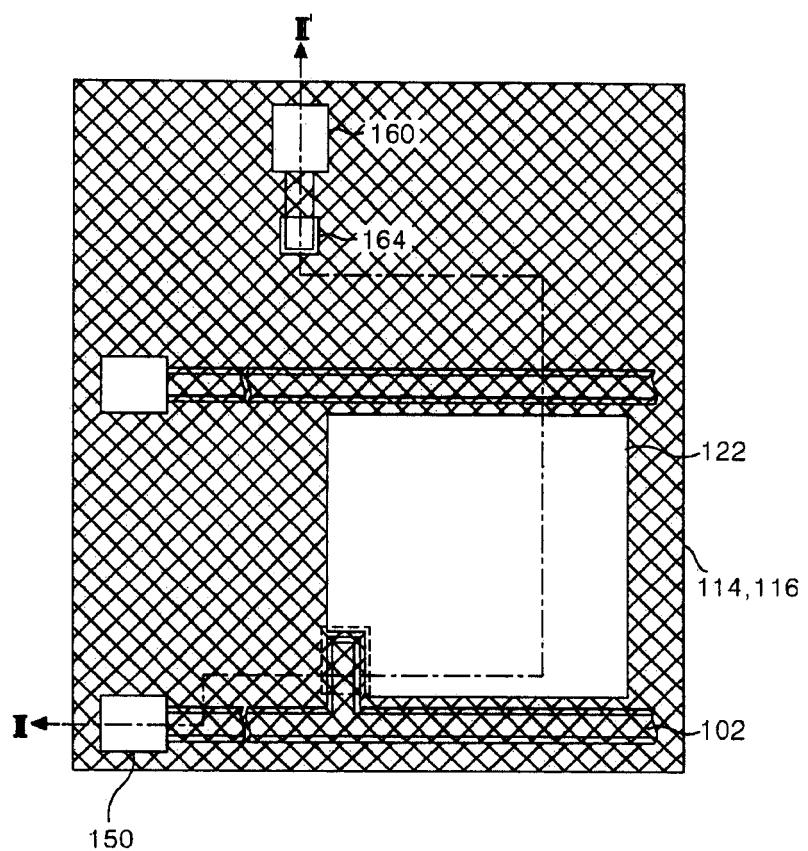

图 8 的平面图表示按照本发明第二实施例的薄膜晶体管阵列基板的结构，而图 9 是沿图 8 中 III-III' 线提取的薄膜晶体管阵列基板的截面图。

图 8 和图 9 中所示的薄膜晶体管阵列基板与图 4 和图 5 所示具有相同的元件，除了用形成的数据接触孔 164 暴露出数据焊盘 160 的端部和下基板 101 的一部分。因此省略了对相同元件的详细描述。

数据焊盘 160 连接到一数据驱动器（未表示），将数据驱动器产生的数据信号提供给数据线 104。为此要将数据焊盘 160 通过数据接触孔 164 电连接到由数据金属层形成的数据线 104。数据焊盘 160 包括透明导电膜 170，以及在 25 与数据线 104 重叠的区域内形成在透明导电膜 170 上的栅极金属膜 172。数据接触孔 164 具有比数据焊盘 160 窄的宽度，并贯穿欧姆接触层 116、有源层 114、栅极绝缘图案 112 和数据焊盘 160 的栅极金属膜 172，暴露出数据焊盘 160 的透明导电膜 170 的端部及其相邻区域。

这样，即便数据接触孔 164 的第二宽度大于数据接触孔 164 因贯穿栅极 30 绝缘图案 112、有源层 114 和欧姆接触层 116 的第一宽度而产生底切现象，数

据线 104 也能连接到通过数据接触孔 164 暴露出的数据焊盘 160 的端部, 由此能防止数据线 104 发生断裂。

图 10A 和图 10B 的平面图和截面图分别用于解释按照本发明第二实施例的薄膜晶体管阵列基板制造方法中的第一掩模工序。

5 如图 10A 和图 10B 中所示, 在下基板 101 上用第一掩模工序形成各自具有双层结构的像素电极 122 和包括栅极线 102、栅极 106、栅极焊盘 150 及数据焊盘 160 的栅极图案。

具体地说, 用溅射等淀积技术依次形成透明导电膜 170 和栅极金属膜 172。此处的透明导电膜 170 用诸如 ITO、TO、ITZO、IZO 等透明导电材料制成, 10 而栅极金属膜 172 用诸如铝族金属等金属材料制成, 包括铝/钕 (AlNd)、钼 (Mo)、铜 (Cu)、铬 (Cr)、钽 (Ta)、钛 (Ti) 等。然后用光刻术对透明导电膜 170 和栅极金属膜 172 构图, 并且用第一掩模进行蚀刻, 形成包括各自具有双层结构的栅极线 102、栅极 106、栅极焊盘 150 和数据焊盘 160 的栅极图案, 以及包括栅极金属膜 172 的像素电极 122。

15 图 11A 和图 11B 的平面图和截面图分别用于解释按照本发明第二实施例的薄膜晶体管阵列基板制造方法中的第二掩模工序。

如图 11A 和图 11B 中所示, 在设有栅极图案的下基板 101 上用第二掩模工序形成栅极绝缘图案 112 和包括有源层 114 及欧姆接触层 116 的半导体图案。去除数据焊盘 160、栅极焊盘 150 和像素电极 122 中所包括的栅极金属膜 20 172 暴露出透明导电膜 170。

具体地说, 在设有栅极图案的下基板 101 上用 PECVD、溅射等淀积技术依次形成栅极绝缘膜及第一和第二半导体层。此处的栅极绝缘膜用氮化硅 (SiNx), 氧化硅 (SiOx) 等无机绝缘材料制成。第一半导体层用不掺杂的非晶硅制成, 而第二半导体层用掺杂有 N-型或 P-型杂质的非晶硅制成。然后用光 25 刻术对栅极绝缘膜及第一和第二半导体层构图, 并且用第二掩模进行蚀刻, 在像素电极 122、栅极焊盘 150 和数据焊盘 160 以及包括有源层 114 和欧姆接触层 116 并且图案与栅极绝缘图案 112 相同的半导体图案以外的剩余区域内形成栅极绝缘图案 112。这样就形成被栅极绝缘图案 112 及半导体图案 114 和 116 暴露出的像素电极 122、栅极焊盘 150 和数据焊盘 160。用栅极绝缘图案 112 30 作为掩模去除像素电极 122、栅极焊盘 150 和数据焊盘的暴露的栅极金属膜

172，暴露出数据焊盘 160，栅极焊盘 150 像素电极 122 所包括的透明导电膜 170。

图 12A 和图 12B 的平面图和截面图分别用于解释按照本发明第二实施例的薄膜晶体管阵列基板制造方法中的第三掩模工序。

5 如图 12A 和图 12B 所示，在设有栅极绝缘图案 112 及半导体图案 114 和 116 的下基板 101 上用第三掩模工序形成包括数据线 104、源极 108、漏极 110 和存储电极 128 的数据图案。进而在其下部沿着数据线 104、源极 108、漏极 110 和存储电极 128 形成半导体图案 114 和 116。

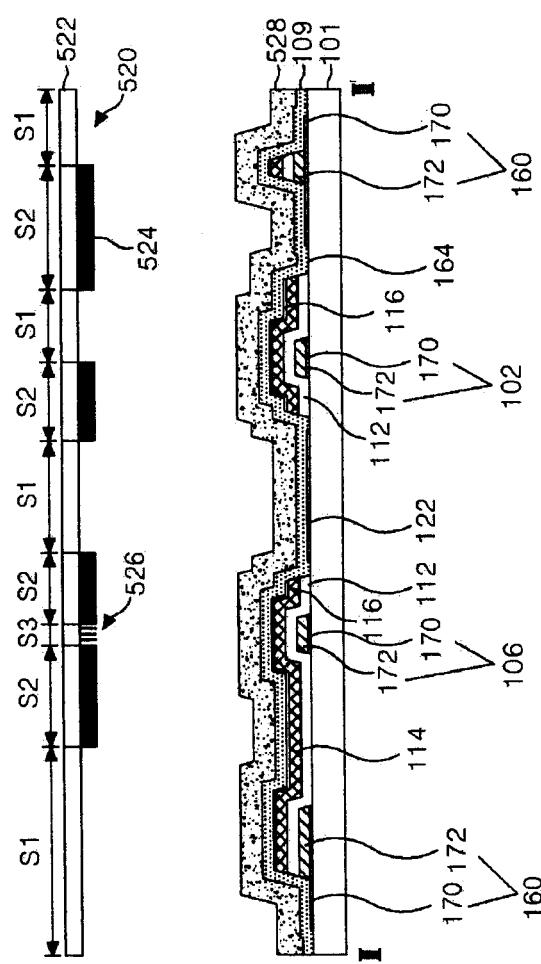

以下要参照图 13A 到图 13E 来详细解释第三掩模工序。

10 如图 13A 所示，在设有半导体图案的下基板 101 上用溅射等淀积技术依次形成数据金属层 109 和光刻胶膜 528。此处的数据金属层 109 用金属钼(Mo) 或铜(Cu) 等形成。

15 然后将一局部曝光掩模即第三掩模 520 对准下基板 101 的上部。第三掩模 520 包括透明材料制成的掩模基板 522，设置在掩模基板 522 的屏蔽区 S2 上的屏蔽部分 524，以及设置在掩模基板 522 的局部曝光区上的衍射曝光部分 (或是半透射部分) 526。掩模基板 522 的曝光区域是曝光区 S1。用第三掩模 520 使光刻胶膜 528 曝光并且显影，如图 13B 所示在对应着第三掩模 520 的屏蔽部分 524 和衍射曝光部分 526 的屏蔽区 S2 和局部曝光区 S3 上形成具有阶梯覆层的光刻胶图案 530。换句话说，设置在局部曝光区 S2 的光刻胶图案 530 所具有的第二高度 h2 低于设置在屏蔽区 S2 的光刻胶图案 530 的第一高度 h1。

20 用光刻胶图案 530 作为掩模按湿蚀刻法对数据金属层 109 构图，形成包括存储电极 128、数据线 104、连接到数据线 104 的源极 108 和漏极 110 的数据图案。

25 接着，用光刻胶图案 530 作为掩模按干蚀刻法沿数据图案形成有源层 114 和欧姆接触层 116。在此时去除位于剩余区域 (有源层 114 和欧姆接触层 116 与数据图案的重叠区以外) 内的有源层 114 和欧姆接触层 116。

30 然后，如图 13C 所示，采用氧(O<sub>2</sub>) 等离子体的灰化工序去掉局部曝光区 S3 上具有第二高度 h2 的光刻胶图案 530，并且局部去除屏蔽区 S2 上具有第一高度 h1 的光刻胶图案 530，留下一高度降低的光刻胶图案 530。用光刻胶图案 530 进行蚀刻去除设在局部曝光区 S3 也就是薄膜晶体管的沟道部分上的

数据金属层和欧姆接触层 116，从源极上断开漏极 110。在图 13D 中通过剥离去掉留在数据图案上的光刻胶图案 530。

接着，如图 13E 所示，在基板 101 设有数据图案的正面上形成一保护膜 118。保护膜 118 用和栅极绝缘图案 112 相同的无机绝缘材料构成，或是一有机绝缘材料，例如是具有小介电常数的丙烯酸有机化合物，BCB(苯并环丁烯)，或是 PFCB (全氟环丁烷) 等。

图 14 的平面图和图 15 的截面图表示按照本发明第三实施例的薄膜晶体管阵列基板。

图 14 和图 15 中所示的薄膜晶体管阵列基板与图 8 和图 9 中所示的元件基本相同，除了用于形成水平电场的公共电极和像素电极设置在下基板上。因此省略了对相同元件的详细描述。

公共电极 184 连接到公共线 186，用于提供驱动液晶的参考电压并且形成在像素区内。具体地，公共电极 184 与像素电极 122 的指部 122b 平行地形成在像素区内。

像素电极 122 连接到漏极 110，在与公共电极 184 二者之间存在电位差时形成一水平电场。像素电极 122 包括与栅极线 102 平行延伸的水平部 122a，以及从水平部 122a 沿垂直方向延伸的指部 122b。

这样，就在通过薄膜晶体管施加像素信号的像素电极 122 和通过公共线 186 施加参考电压的公共电极 184 之间形成一水平电场。水平电场利用液晶的介电各向异性旋转按水平方向设置在下阵列基板和上阵列基板之间的液晶分子。而且，通过像素区的光透射比取决于液晶分子的旋转程度，从而产生图像。

公共焊盘 200 向公共线 186 提供由一外部电压源 (未示出) 产生的参考电压。

如果公共焊盘 200 用与数据线 104 相同的材料形成，通过暴露出公共焊盘 200 端部的公共接触孔 166 将其连接到公共线 186。公共线 186 包括透明导电膜 170 和形成在透明导电膜 170 上的栅极金属膜 172。公共接触孔 166 贯穿欧姆接触层 116、有源层 114、栅极绝缘图案 112 和公共线 186 的栅极金属膜 172，暴露出公共线 186 的透明导电膜 170 的端部及其相邻区域。

如果公共焊盘 200 由透明导电膜 170 和暴露出至少一部分透明导电膜 170 的栅极金属膜 172 组成，就通过暴露出公共焊盘 200 端部及其相邻区域的公共

接触孔 166 将其连接到公共线 186。公共线 186 包括通过公共接触孔 166 连接到公共焊盘 200 并且用与数据线 104 相同的材料制成的第一公共线，以及通过独立的接触孔连接到第一公共线并且用与栅极线 102 相同的金属制成的第二公共线。

5 如上所述，用于连接公共线 186 和公共焊盘 200 的公共接触孔 166 暴露出公共焊盘 200 和/或公共线 186 所包括的透明导电膜 170 的端部。这样，即便贯穿栅极金属膜 172 的公共接触孔 166 的第二宽度大于贯穿栅极绝缘图案 112、有源层 114 和欧姆接触层 116 的公共接触孔 166 的第一宽度而可能发生底切或是断裂现象，公共线（或公共焊盘）的端部也能连接到通过公共接触孔

10 166 暴露出的公共焊盘（或公共线）。

用于将公共线连接到公共焊盘的公共接触孔可以应用于水平电场施加型薄膜晶体管阵列基板以及图 4 中所示的垂直电场施加型薄膜晶体管阵列基板。换句话说，公共电压源线通过暴露出公共电压源线端部的接触孔电连接到公共焊盘，其中公共电压源线的端部通过银点连接到向公共电压源线施加公共电压

15 的公共电极和/或公共焊盘。

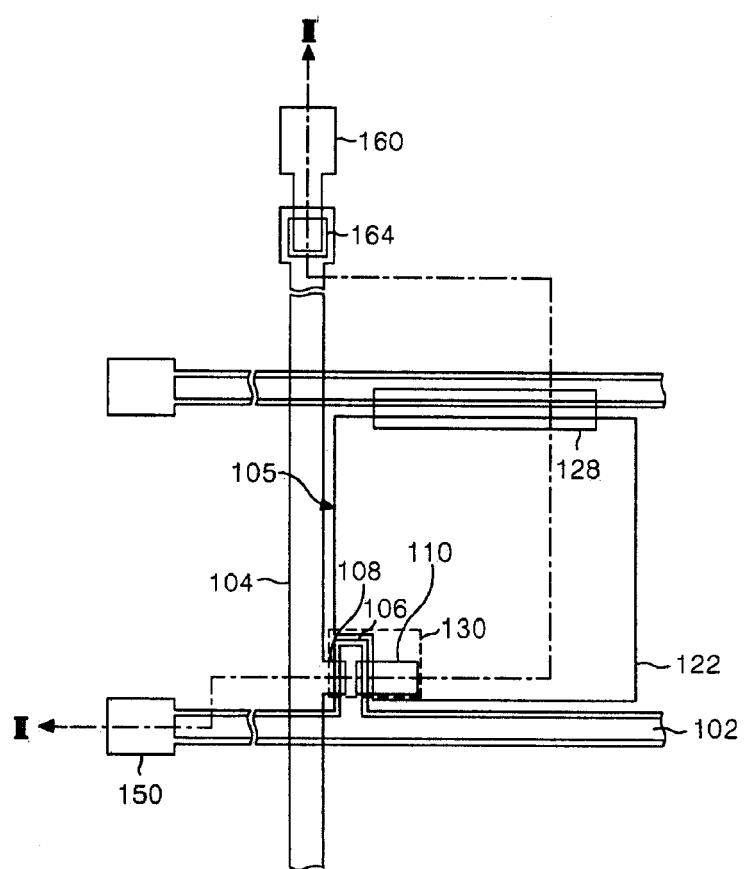

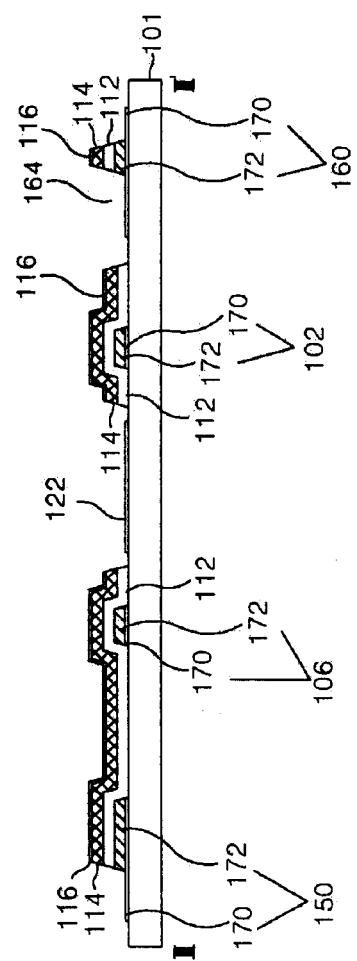

图 18 的平面图表示按照本发明第四实施例的薄膜晶体管阵列基板的结构，而图 19 是沿图 18 中 VI-VI' 线提取的薄膜晶体管阵列基板的截面图。

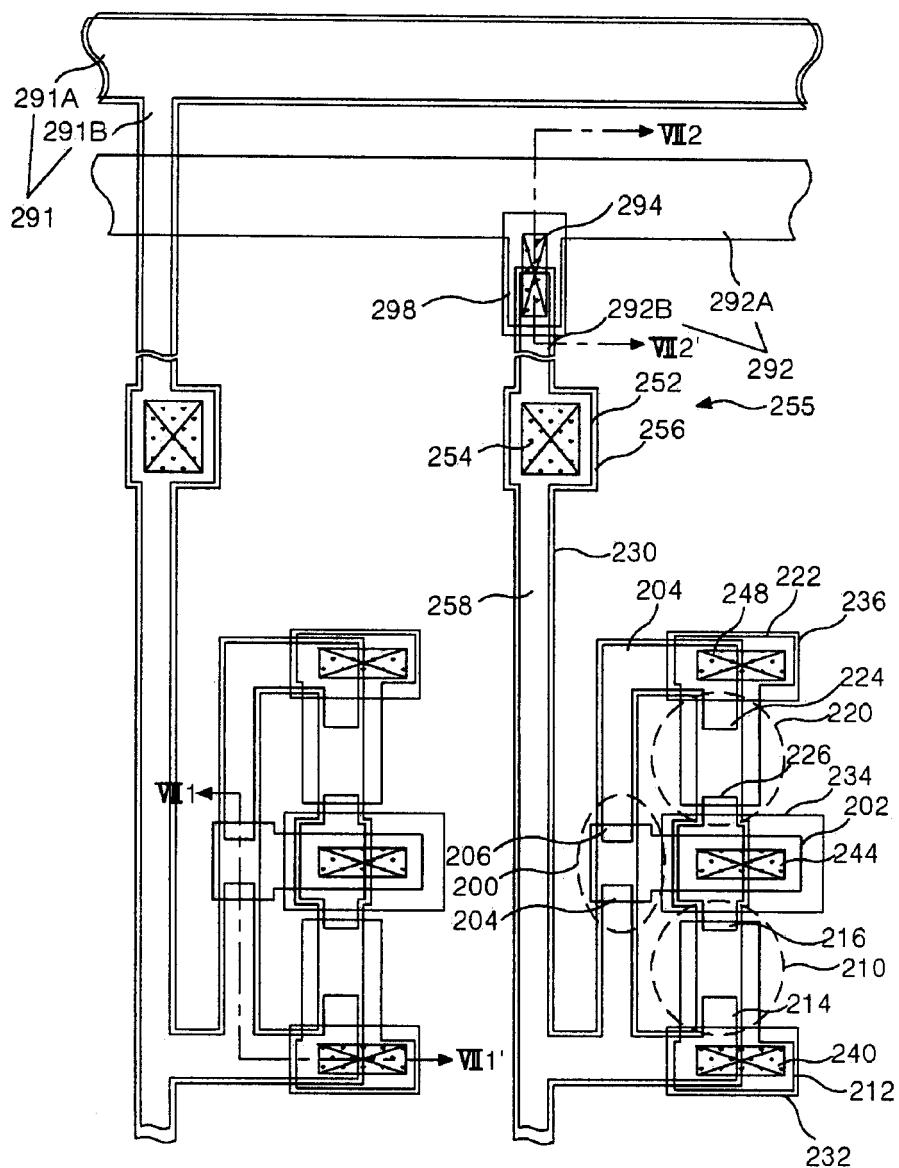

首先，在参照图 18 和图 19 描述本发明的第四实施例之前，先描述一下四轮掩模工序中出现的防静电装置和短路棒结构，以与本发明的第四实施例相

20 比较。

典型的薄膜晶体管阵列基板包括用于排放在非显示区上形成并且输入到显示区的静电的防静电装置。例如，如图 16 所示，防静电装置包括连接到非显示区上的数据线或是栅极线并且具有相互连接关系的多个薄膜晶体管 400、410 和 420。防静电装置在高电压区具有低阻抗，能够排放静电等大电流，防

25 止静电输入，而在正常驱动环境下具有高阻抗（即数十  $M\Omega$ ），对通过数据线或栅极线提供的驱动信号没有影响。图 17A 和图 17B 表示了这种防静电装置的具体结构示例。

参见图 17A 和图 17B，防静电装置包括连接到用于连接数据焊盘 455 和数据线的数据链 458 的第一到第三薄膜晶体管 400，410 和 420。

30 第一薄膜晶体管 400 包括连接到数据链 458 的第一源极 404，面对第一源

极 404 的第一漏极 406, 以及与第一源极和漏极 404 和 406 重叠并且中间有半导体层 430 和 464 以及栅极绝缘膜 462 的第一栅极 402。

第二薄膜晶体管 410 包括连接到第一源极 404 的第二源极 414, 面对第二源极 414 的第二漏极 416, 以及与第二源极和漏极 414 和 416 重叠并且中间有 5 半导体层 430 和 464 以及栅极绝缘膜 462 的第二栅极 412。此处的第二栅极 412 通过在第一和第二接触孔 440 和 442 上面形成的第一接触电极 432 连接到第二源极 414。换句话说, 第一接触电极 432 设置在贯穿保护膜 466 暴露出一部分第二源极 414 的第一接触孔 440 和贯穿保护膜 466 及栅极绝缘膜 462 暴露出一部分第二栅极 412 的第二接触孔 442 的上面, 从而将第二栅极 412 连接到第二 10 源极 414。

第三薄膜晶体管 420 包括连接到第一漏极 406 的第三源极 424, 面对第三源极 424 的第三漏极 426, 以及连接到第三源极和漏极 424 和 426 并且中间有半导体层 430 和 464 以及栅极绝缘膜 462 的第三栅极 422。此处的第三漏极 426 15 连接到第二漏极 416, 并且通过在第三和第四接触孔 444 和 446 上面形成的第一二接触电极 434 连接到第一栅极 402。换句话说, 第二接触电极 434 设置在贯穿保护膜 466 暴露出一部分第二漏极 416 的第三接触孔和贯穿保护膜 466 及栅极绝缘膜 462 暴露出一部分第一栅极 402 的第四接触孔 446 的上面, 从而将第二漏极 416 连接到第一栅极 402。进而通过在第五和第六接触孔 448 和 450 上 20 面的第三接触电极 436 将第三栅极 422 连接到第三源极 424。换句话说, 第三接触电极 436 设置在贯穿保护膜 466 暴露出一部分第三源极 424 的第五接触孔 448 和贯穿保护膜 466 及栅极绝缘膜 462 暴露出一部分第三栅极 422 的第六接触孔 450 的上面, 从而将第三栅极 422 连接到第三源极 424。

在第一到第三薄膜晶体管 400、410 和 420 中, 栅极 402、412 和 422 由 25 基板 460 上的第一导电层 (或栅极金属层) 形成; 源极 404、414 和 424 及漏极 406、416 和 426 由半导体层 430 和 464 上的第二导电层 (或源极/漏极金属层) 形成; 而接触电极 432、434 和 436 由保护膜 466 上的第三导电层 (或是透明导电层或 Ti) 形成。

数据焊盘 455 包括由栅极绝缘膜 462 上的第二导电层形成的下数据焊盘电极 452, 以及通过贯穿保护膜 466 的第九接触孔 454 连接到下数据焊盘电极 30 452 的上数据焊盘电极 456。

数据焊盘 455 连接到设置在非显示区的奇数和偶数短路棒 491 和 492，用于在制成薄膜晶体管阵列基板之后进行测试。奇数短路棒 491 同时连接到多个奇数数据焊盘 455，而偶数短路棒 492 同时连接到多个偶数数据焊盘 455。

奇数短路棒 491 由连接到下奇数数据焊盘电极 452 的第一奇数短路棒 491B 和同时连接到多个第一奇数短路棒 491B 的第二奇数短路棒 491A 组成。奇数短路棒 491 由与下数据焊盘电极 452 相同的第二导电层形成。

偶数短路棒 492 由连接到下偶数数据焊盘电极 452 的第一偶数短路棒 492B 和同时连接到多个第一偶数短路棒 492B 的第二偶数短路棒 492A 组成。此处的第一偶数短路棒 492B 由与下数据焊盘电极 452 相同的第二导电层形成，而与第一奇数短路棒 491B 交叉的第二偶数短路棒 492A 由第一导电层形成。第一和第二偶数短路棒 492A 和 492B 通过形成在第七和第八接触孔 494 和 496 上面的第三导电层的第四接触电极 498 连接。换句话说，第四接触电极 498 设置在贯穿保护膜 466 暴露出一部分第一偶数短路棒 492B 的第七接触孔 496 及贯穿保护膜 466 和栅极绝缘膜 462 暴露出一部分第二偶数短路棒 492A 的第八接触孔 494 的上面，将第一偶数短路棒 492A 连接到第二偶数短路棒 492B。

此处的半导体层包括在第一到第三薄膜晶体管 400, 410 和 420 上各自形成一沟道的有源层 430，以及设置在有源层 430 上沟道部分以外处的欧姆接触层 464，用于与源极 404、414 和 424 及漏极 406、416 和 426 形成欧姆接触。还要沿着包括数据链 458、下数据焊盘电极 452、奇数短路棒 491 和偶数短路棒 492 的垂直部分 492B 的第二导电层形成有源层 430 和欧姆接触层 464。

用常规的四轮掩模工序形成上述的防静电装置和短路棒。具体地说，用第一掩模工序在基板 460 上形成栅极 402、412 和 422 及第一导电层的偶数短路棒 492A。用第二掩模工序在栅极绝缘膜 462 上形成半导体层 430 和 464，源极 404、414 和 424，漏极 406、416 和 426，数据链 458，下数据焊盘电极 452，奇数短路棒 491 以及第二导电层的第一偶数短路棒 492B。用第三掩模工序形成贯穿保护膜 466 和栅极绝缘膜 462 的接触孔 440、442、444、446、448、450、454、494 和 496，并且用第四掩模工序形成接触电极 432、434、436 和 498 以及上数据焊盘电极 456。

此处，暴露出第二导电层的接触孔 440、444、448 和 496 和暴露出第一

导电层的接触孔 442、446、450 和 494 彼此独立地形成以具有不同的阶梯覆层，这样会增大接触电极 432、434、436 和 498 发生断裂的风险。

为了克服这一问题，如图 18 和图 19 所示，按照本发明第四实施例的薄膜晶体管阵列基板提供了暴露出导电层以及导电层相邻区域的接触孔。

5 图 18 和图 19 中所示的薄膜晶体管阵列基板与薄膜晶体管阵列基板具有相同的元件，除了用划线步骤去除的部分，并且还包括分别连接到栅极焊盘和数据焊盘的栅极短路棒和数据短路棒。因而在此省略了对相同元件的详细说明。

10 在将信号线连接到地电压源 GND 的制造工序中，栅极短路棒 183 和数据短路棒 185 能防止静电传导到液晶显示面板的信号线 102、104 上，保护薄膜晶体管 130 不受静电损伤。

栅极短路棒 183 由连接到栅极焊盘 150 的第一栅极短路棒 182 和同时连接到多个第一栅极短路棒 182 的第二栅极短路棒 180 组成。

15 第二栅极短路棒 180 由与数据线 104 相同的金属构成，例如具有强耐腐蚀性的金属钼 (Mo)、铬 (Cr)、钛 (Ti)、钽 (Ta) 或 MoW。第二栅极短路棒 180 通过第一栅极短路棒 182 电连接到栅极焊盘 150。第一栅极短路棒 182 从第一栅极短路棒 180 延伸跨过划线 SCL 并且通过第一短路接触孔 162 连接到栅极焊盘 150。此处的第一短路接触孔 162 的宽度大于栅极焊盘 150，并且贯穿欧姆接触层 116、有源层 114、栅极绝缘图案 112 和栅极焊盘 150 的栅极金属膜 172 暴露出栅极焊盘的透明导电膜 170 的端部及其相邻区域。

数据短路棒 185 由连接到数据焊盘 160 的第一数据短路棒 192 和同时连接到多个第一数据短路棒 192 的第二数据短路棒 190 组成。

25 第二数据短路棒 190 由与数据线 104 相同的金属构成，例如具有强耐腐蚀性的金属钼 (Mo)、铬 (Cr)、钛 (Ti)、钽 (Ta) 或 MoW。第二数据短路棒 190 通过第一数据短路棒 192 电连接到数据焊盘 160。第一数据短路棒 192 从第二数据短路棒 190 延伸跨过划线 SCL 并且通过第二短路接触孔 194 连接到数据焊盘 160。此处的第二短路接触孔 194 的宽度大于数据焊盘 160，并且贯穿欧姆接触层、有源层 114、栅极绝缘图案 112 和数据焊盘 160 的栅极金属膜 172 暴露出数据焊盘 160 的透明导电膜 170 的端部及其相邻区域。

30 如上所述，分别将第一栅极短路棒 182 连接到栅极焊盘 150 并将第一数

据短路棒 192 连接到数据焊盘 160 的第一和第二短路接触孔 162 和 194 暴露出栅极焊盘 150 和数据焊盘 160 所包括的透明导电膜 170 的端部。因此，即便贯穿栅极金属膜 172 的短路接触孔 162 和 194 的第二宽度大于贯穿栅极绝缘图案 112、有源层 114 和欧姆接触层 116 的短路接触孔 162 和 194 的第一宽度有可能造成底切现象，第一短路棒 192 和 182 连接到通过短路接触孔 194 和 162 暴露出的数据和栅极焊盘 160 和 150 的端部，这样就能防止第一短路棒 192 和 182 断裂。

以下要解释制造这种液晶显示面板的薄膜晶体管的一种方法。

用第一掩模工序形成包括栅极线 106、栅极 102，栅极焊盘 150 和数据焊盘 160 的栅极图案以及包括栅极金属膜的像素电极 122。用第二掩模工序去除具有第一短路孔 162 和 194 的栅极绝缘图案 112 及半导体图案 114 和 116，以及栅极焊盘 150、数据焊盘 160 和像素电极 122 所包括的栅极金属膜 172，并且去除通过第一和第二短路接触孔 162 和 194 暴露出的栅极金属膜 172。用第三掩模工序形成包括第二栅极短路棒 180、第二数据短路棒 190、第一栅极短路棒 182、第一数据短路棒 192、源极 108、漏极 110 和数据线 104 的数据图案。然后在下基板 101 的整个表面上形成保护薄膜晶体管 130 的保护膜。

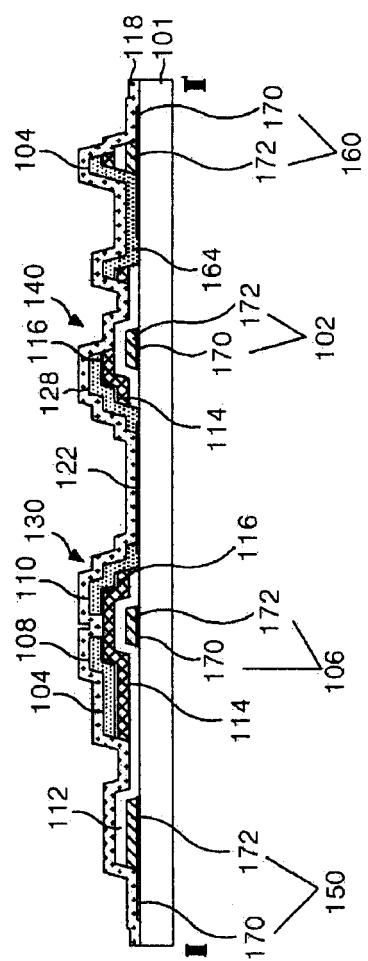

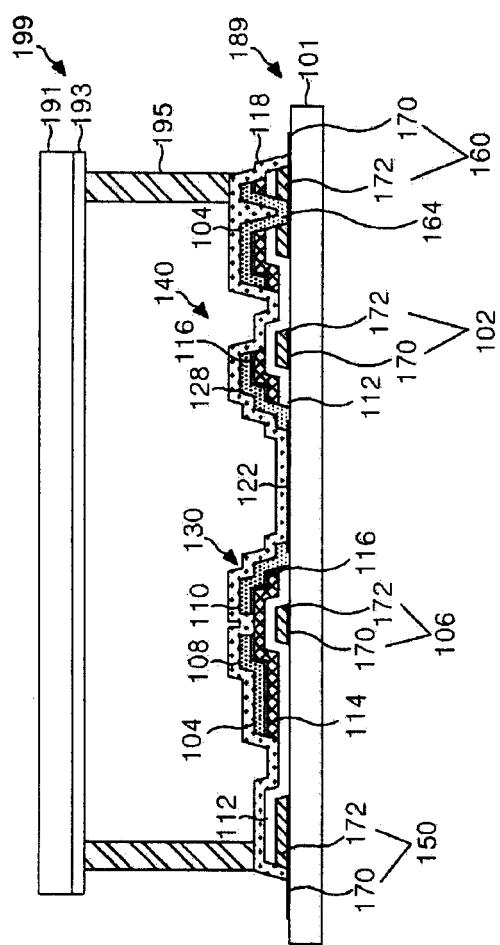

图 20 是包括按照本发明第一到第四实施例的薄膜晶体管阵列基板的液晶显示面板的截面图。

图 20 中所示的液晶显示面板包括用密封剂 195 彼此粘接的滤色片阵列基板 199 和薄膜晶体管阵列基板 189。

滤色片阵列基板 199 包括形成在上基板 191 上的黑矩阵（未示出）和包括滤色片的上阵列 193。

形成的薄膜晶体管阵列基板 189 使得与滤色片阵列基板 199 重叠的区域受到保护膜 118 的保护，并且暴露出与滤色片阵列基板 199 没有重叠的焊盘区上的栅极焊盘 150、数据焊盘 160 和/或公共焊盘（未示出）所包括的透明导电膜 170。

以下要描述这种液晶显示面板的制造方法。

首先单独制备滤色片阵列基板 199 和薄膜晶体管阵列基板 189，然后用密封剂 195 将其彼此粘接。接着用滤色片阵列基板 199 作为掩模按焊盘打开工序对薄膜晶体管阵列基板 189 的保护膜 118 进行构图。这样会暴露出焊盘区上的

栅极焊盘 150、数据焊盘 160 和/或公共焊盘（未示出）所包括的透明导电膜 170。

焊盘开放工序同时用一空气等离子体发生器产生的等离子体依次扫描或集中扫描被滤色片阵列基板 199 暴露出的各个焊盘，从而暴露出栅极焊盘 150、

5 数据焊盘 160 和公共焊盘（未示出）的透明导电膜 170。或是，将各自具有与

薄膜晶体管阵列基板 189 粘接的滤色片阵列基板 199 的多个液晶显示面板插入

一腔室，然后用常压等离子体蚀刻被滤色片阵列基板 199 暴露出的焊盘区上的

保护膜 118，从而暴露出栅极焊盘 150、数据焊盘 160 和公共焊盘（未示出）

10 的透明导电膜 170。或是将具有与薄膜晶体管阵列基板 189 粘接的滤色片阵列

基板 199 的整个液晶显示面板浸入一种蚀刻液中，或是仅仅将包括栅极焊盘

150、数据焊盘 160 和公共焊盘（未示出）的焊盘区浸入蚀刻液中，从而暴露出

栅极焊盘 150、数据焊盘 160 和公共焊盘（未示出）的透明导电膜 170。

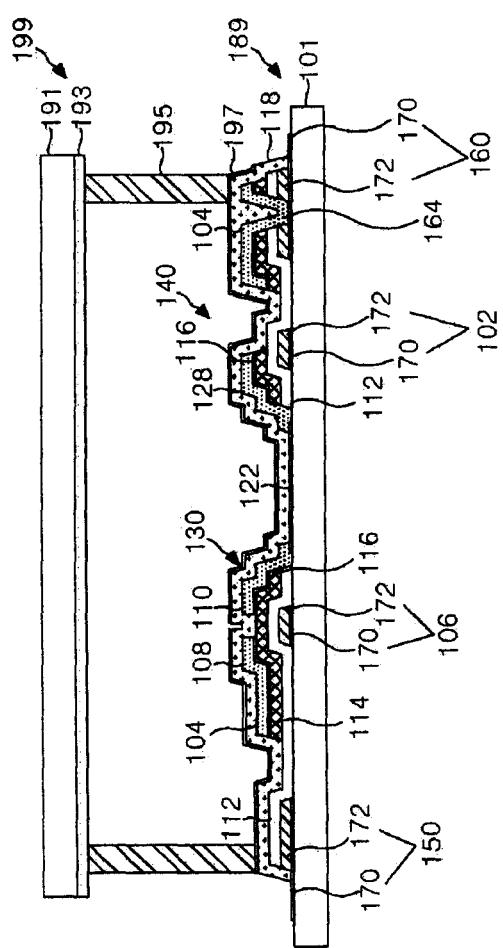

图 21 是包括按照本发明第一到第四实施例的薄膜晶体管阵列基板的另一

例液晶显示面板的截面图。

15 图 21 中所示的液晶显示面板包括用密封剂 195 彼此接合的滤色片阵列基

板 199 和薄膜晶体管阵列基板 189。

在薄膜晶体管阵列基板 189 中，由定向膜 197 限定的显示区受到保护膜

118 的保护，并且暴露出与定向膜 197 没有重叠的区域内的焊盘区上的栅极焊

盘 150、数据焊盘 160 和/或公共焊盘（未示出）所包括的透明导电膜 170。在

20 这种情况下，用定向膜 197 作为掩模按蚀刻工序构图并且形成保护膜 118。

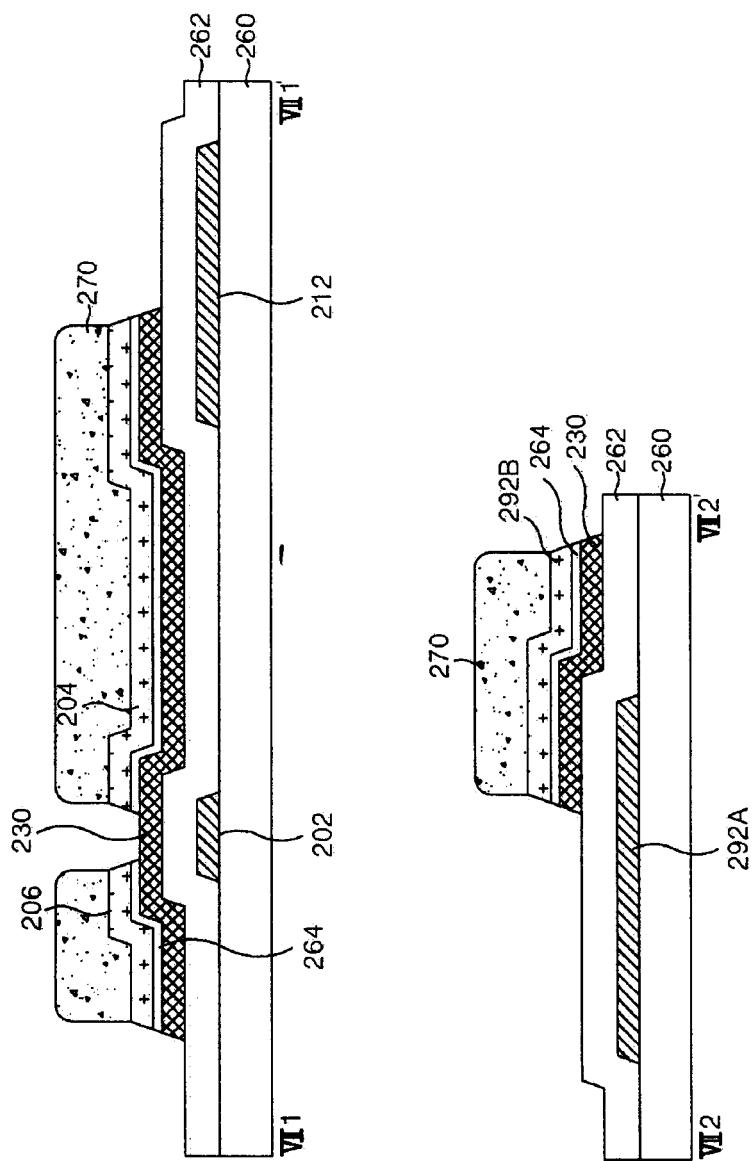

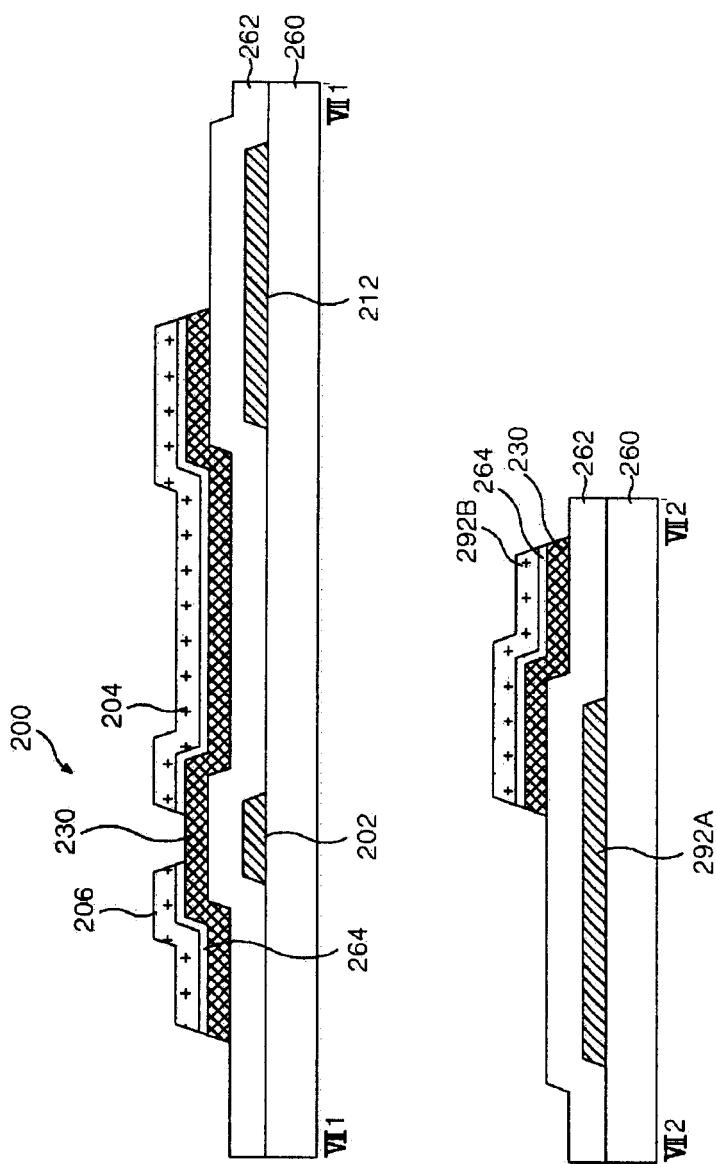

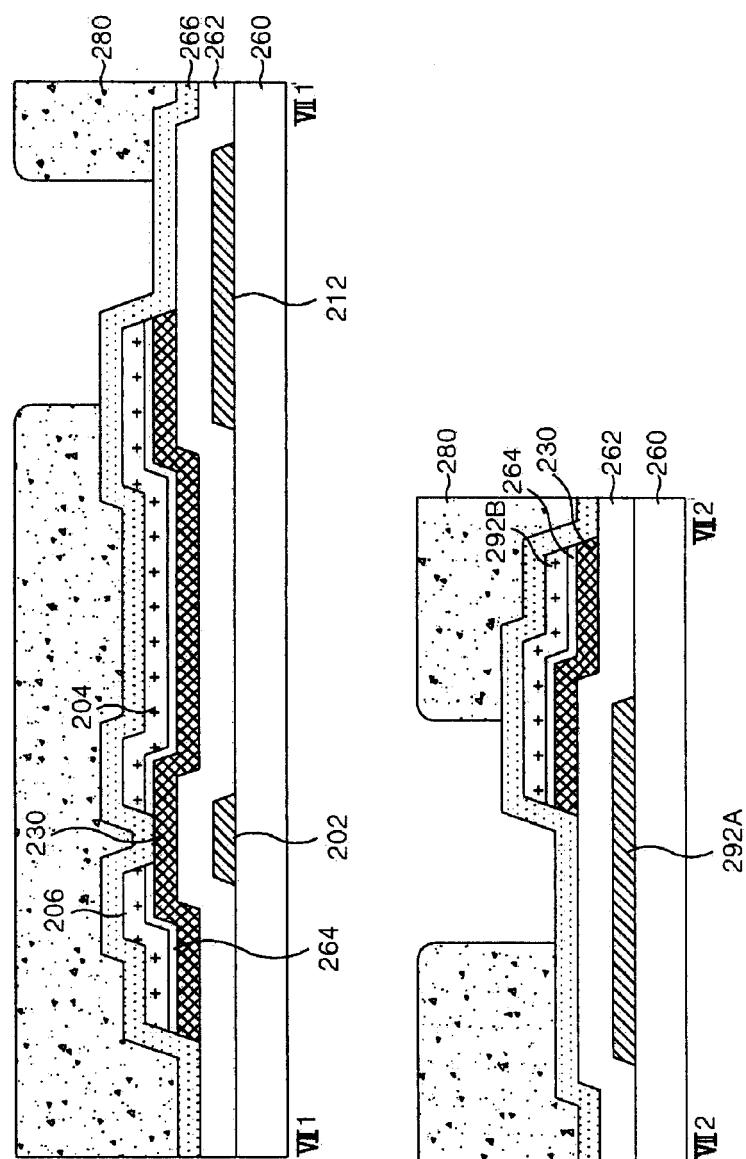

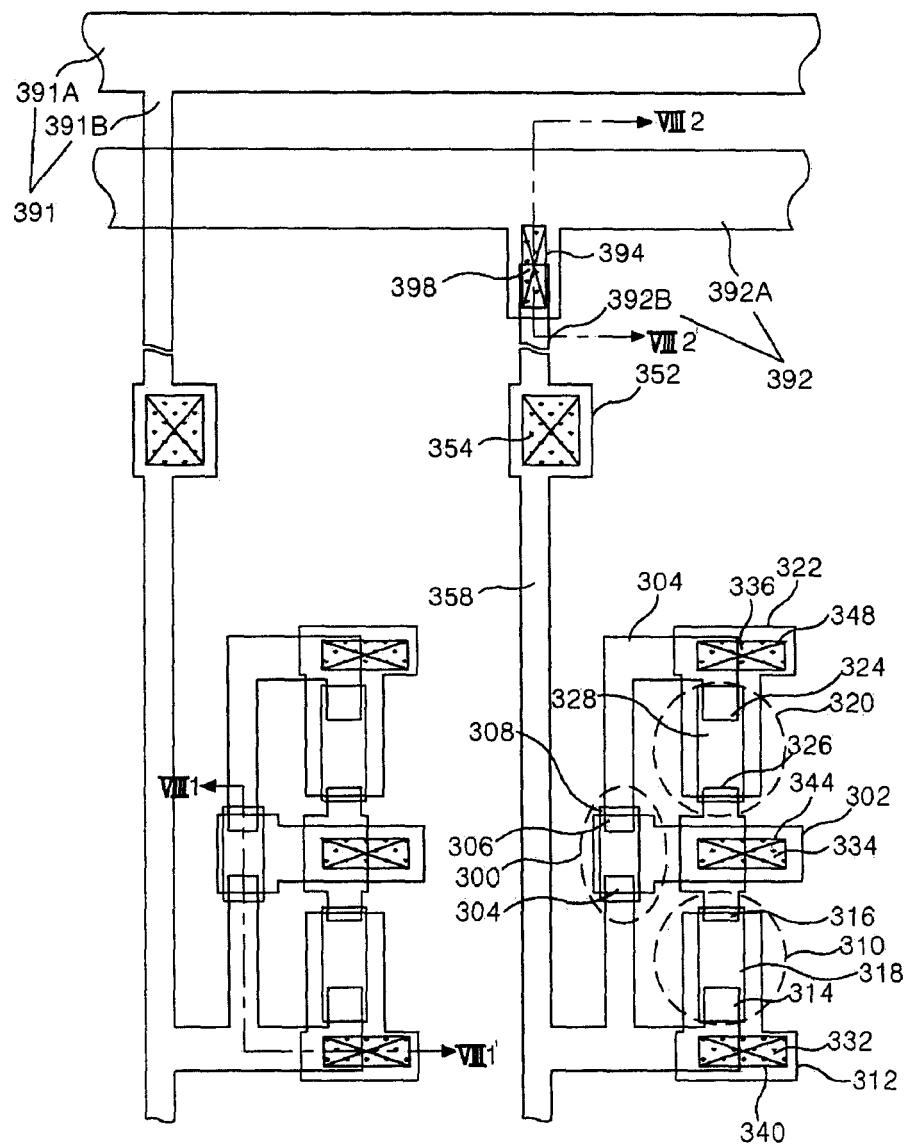

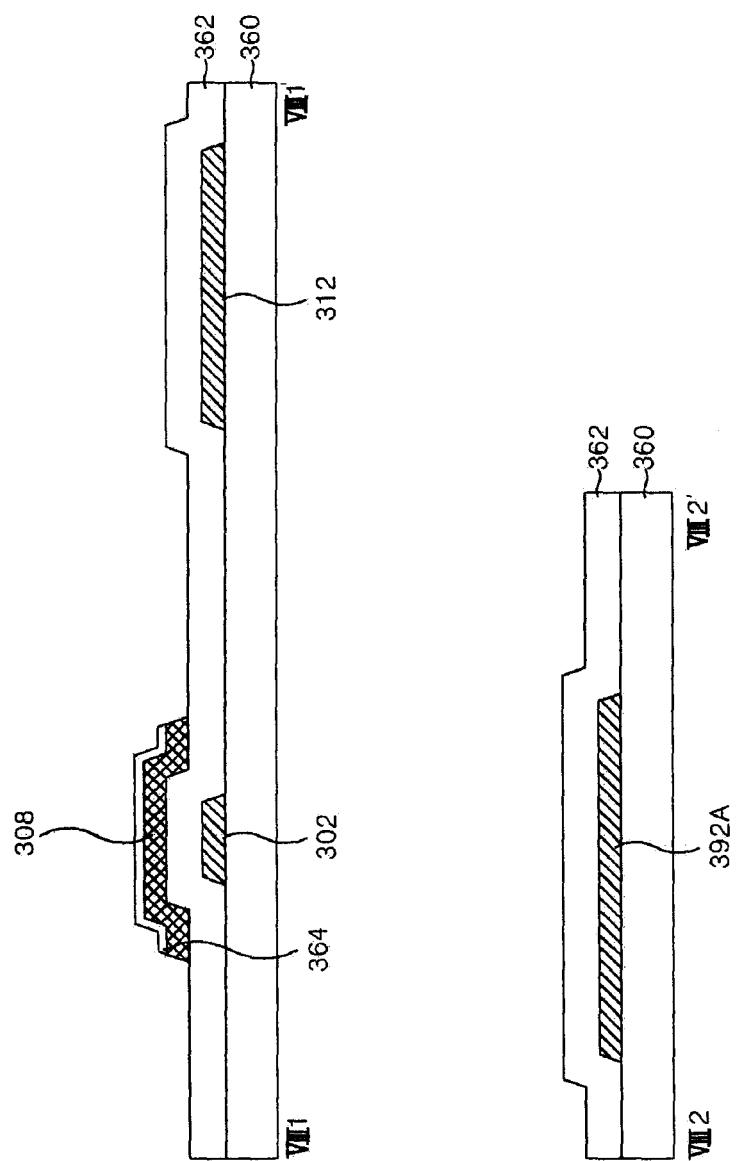

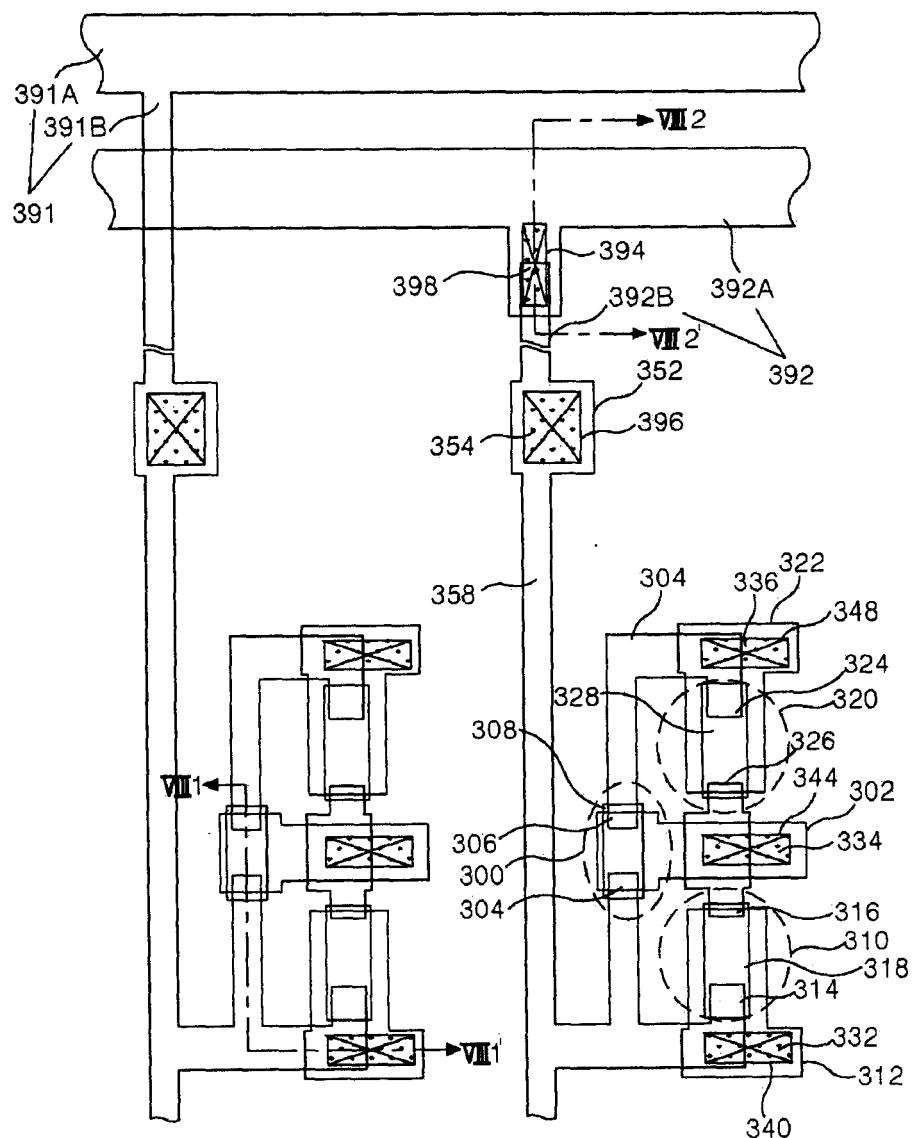

图 22 的平面图表示按照本发明第五实施例的薄膜晶体管阵列基板的防静电

装置和短路棒区域，而图 23 是沿图 22 中 VII1-VII1'线和 VII2-VII2'线提取

的防静电装置和短路棒区域的截面图。

在描述本发明的第五实施例之前，首先要说明本发明所采用的一种提升

25 工序。

本申请人先前提交的 2002-88323 号韩国专利申请（以下称为“在先发明”

并作为参考资料）业已提出了采用提升的三轮掩模工序制造薄膜晶体管阵列基

板。在先发明采用提升，用单一掩模工序实现贯穿保护膜和栅极绝缘膜的通孔

的限定工序以及第三导电层的构图工序，从而减少了掩模工序的数量。按照在

30 先发明，仅仅在光刻胶图案限定了保护膜和栅极绝缘膜内的通孔的区域上形成

构图的第三导电层，使其接触到孔内的保护膜。然而，如果如图 17A 和图 17B 所示，要在防静电装置和短路棒区域上各自形成暴露出第一和第二导电层的两个接触孔，接触电极就不能将第一导电层连接到第二导电层。

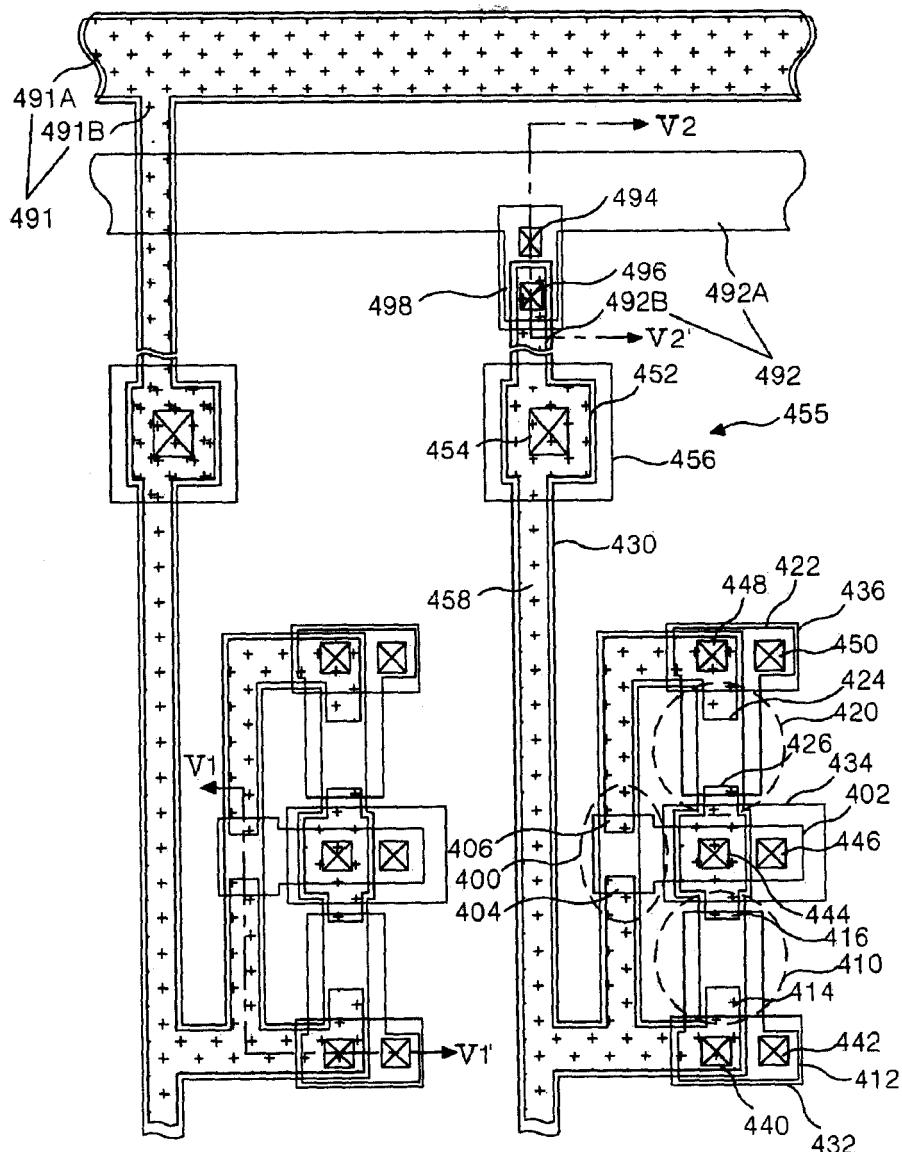

或者，按照图 22 和图 23 所示的本发明第五实施例的薄膜晶体管阵列基板，一体地限定暴露出第一和第二导电层的接触孔。

参见图 22 和图 23，防静电装置包括连接到数据链 258 用于将数据焊盘 255 连接到数据线的第一到第三薄膜晶体管 200、210 和 220。

第一薄膜晶体管 200 包括连接到数据链 258 的第一源极 204、面对第一源极 204 的第一漏极 206 以及与第一源极和漏极 204 和 206 重叠并且中间有半导体层 230 和 264 以及栅极绝缘膜 262 的第一栅极 202。

第二薄膜晶体管 210 包括连接到第一源极 204 的第二源极 214，面对第二源极 214 的第二漏极 216，以及与第二源极和漏极 214 和 216 重叠并且中间有半导体层 230 和 264 以及栅极绝缘膜 262 的第二栅极 212。此处的第二栅极 212 通过形成在第一接触孔 240 上面的第一接触电极 232 连接到第二源极 214。换句话说，第一接触电极 232 设置在贯穿保护膜 266 和栅极绝缘膜 262 的第一接触孔 240 内，同时暴露出第二栅极和毗邻第二栅极 212 的一部分第二源极 214，从而将第二栅极 212 连接到第二源极 214。

第三薄膜晶体管 220 包括连接到第一漏极 206 的第三源极 224，面对第三源极 224 的第三漏极 226，以及连接到第三源极和漏极 224 和 226 并且中间有半导体层 230 和 264 以及栅极绝缘膜 262 的第三栅极 222。此处的第三漏极 226 也连接到第二漏极 216，并且同时通过在第二接触孔 244 内形成的第二接触电极 234 连接到第一栅极 202。换句话说，第二接触电极 234 设置在贯穿保护膜 266 和栅极绝缘膜 262 的第二接触孔 244 内，同时暴露出第二漏极 226 和一部分第一栅极 202，从而将第二漏极 216 连接到第一栅极 202。进而，第三栅极 212 通过在第三接触孔 248 内形成的第三接触电极 236 连接到第三源极 224。

换句话说，第三接触电极 236 设置在贯穿保护膜 266 和栅极绝缘膜 262 的第三接触孔 248 内，同时暴露出第三源极 224 和毗邻第三源极 224 的一部分第三栅极 222，从而将第三源极 224 连接到第三栅极 222。

在第一到第三薄膜晶体管 200、210 和 220 中，栅极 202、212 和 222 由基板 260 上的第一导电层（或栅极金属层）形成；源极 204、214 和 224 以及

漏极 206、216 和 226 由半导体层 230 和 264 上的第二金属层（或源极/漏极金属层）形成；而接触电极 232、234 和 236 由保护膜 266 上的第三导电层（或是透明导电层或 Ti）形成。

数据焊盘 255 包括由栅极绝缘膜 262 上的第二导电层形成的下数据焊盘电极 252，以及通过贯穿保护膜 266 的第五接触孔 256 连接到下数据焊盘电极 252 的上数据焊盘电极 254。

数据焊盘 255 连接到在非显示区上形成的奇数和偶数短路棒 291 和 292，在制成薄膜晶体管阵列基板之后执行信号测试。奇数短路棒 291 同时连接到多个奇数数据焊盘 255，而偶数短路棒 292 同时连接到多个偶数数据焊盘 255。

奇数短路棒 291 包括连接到下奇数数据焊盘电极 252 的第一奇数短路棒 291B 和同时连接到多个第一奇数短路棒 291B 的第二奇数短路棒 291A。奇数短路棒 291 由与下数据焊盘电极 252 相同的第二导电层形成。

偶数短路棒 292 包括连接到下偶数数据焊盘电极 252 的第一偶数短路棒 292B 和同时连接到多个第一偶数短路棒 292B 的第二偶数短路棒 292A。此处的第一偶数短路棒 292B 由与下数据焊盘电极 252 相同的第二导电层形成，而与第一奇数短路棒 291B 交叉的第二偶数短路棒 292A 由第一导电层形成。第一和第二偶数短路棒 292B 和 292A 通过形成在第四孔 294 上方的第三导电层的第四接触电极 298 连接。换句话说，第四接触电极 298 设置在贯穿保护膜 266 和栅极绝缘膜 262 的第四接触孔 294 内，同时暴露出第一偶数短路棒 292B 和毗邻第一偶数短路棒 292B 的第二偶数短路棒 292A，从而将第一偶数短路棒 292B 连接到第二偶数短路棒 292A。

此处的半导体层包括在第一到第三薄膜晶体管 200、210 和 220 上各自形成沟道的有源层 230，以及设置在沟道部分以外的有源层 230 上用于与源极 204、214、224 和漏极 206、216、226 形成欧姆接触的欧姆接触层 264。还沿着包括数据链 258、下数据焊盘电极 252、奇数短路棒 291 和第一偶数短路棒 292B 的第二导电层形成有源层 230 和欧姆接触层 264。

在按照本发明第五实施例的薄膜晶体管阵列基板中，第一到第四接触孔 240、244、248 和 294 同时暴露出第一和第二导电层，用形成在各个接触孔 240、244、248 和 294 内的接触电极 232、234 和 236 将第一导电层连接到第二导电层。在这种情况下，第一到第四接触孔 240、244、248 和 294 依次暴露出第二

导电层、半导体层和第一导电层以降低阶梯覆层，由此防止接触电极 232、234 和 236 发生断裂。接触电极 232、234 和 236 是通过去除用于对保护膜 266 和 栅极绝缘膜 262 连同上数据焊盘电极 254 构图的光刻胶图案用提升方法制成的。这样就能如下所述用三轮掩模工序形成按照本发明第五实施例的薄膜晶体管阵列基板。

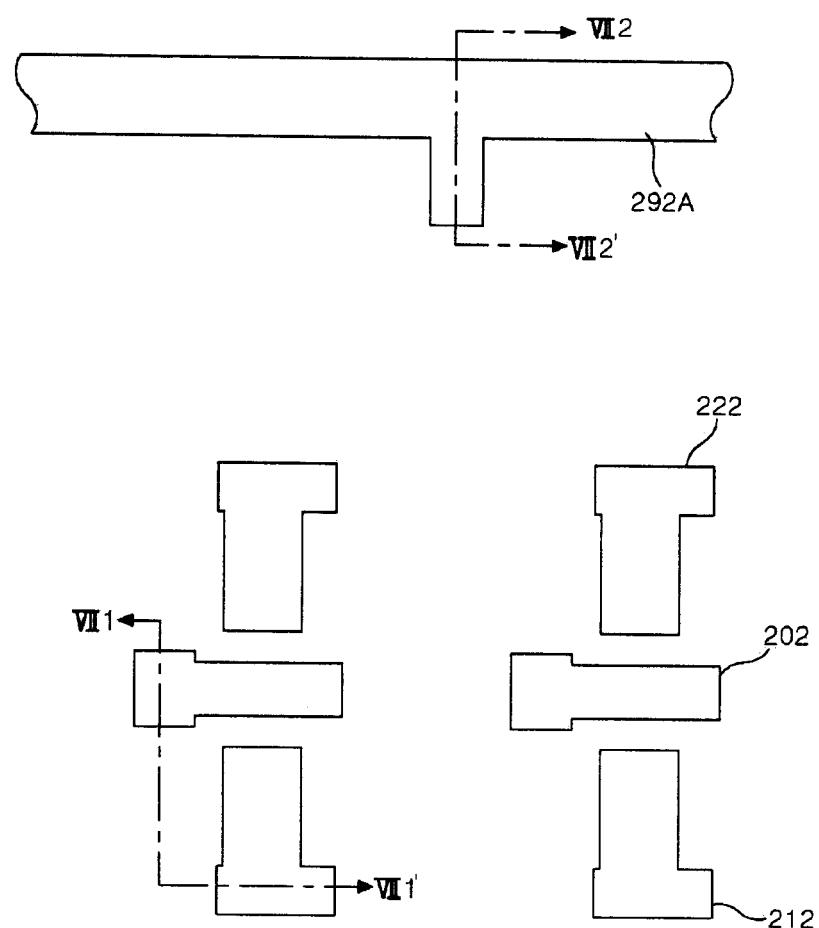

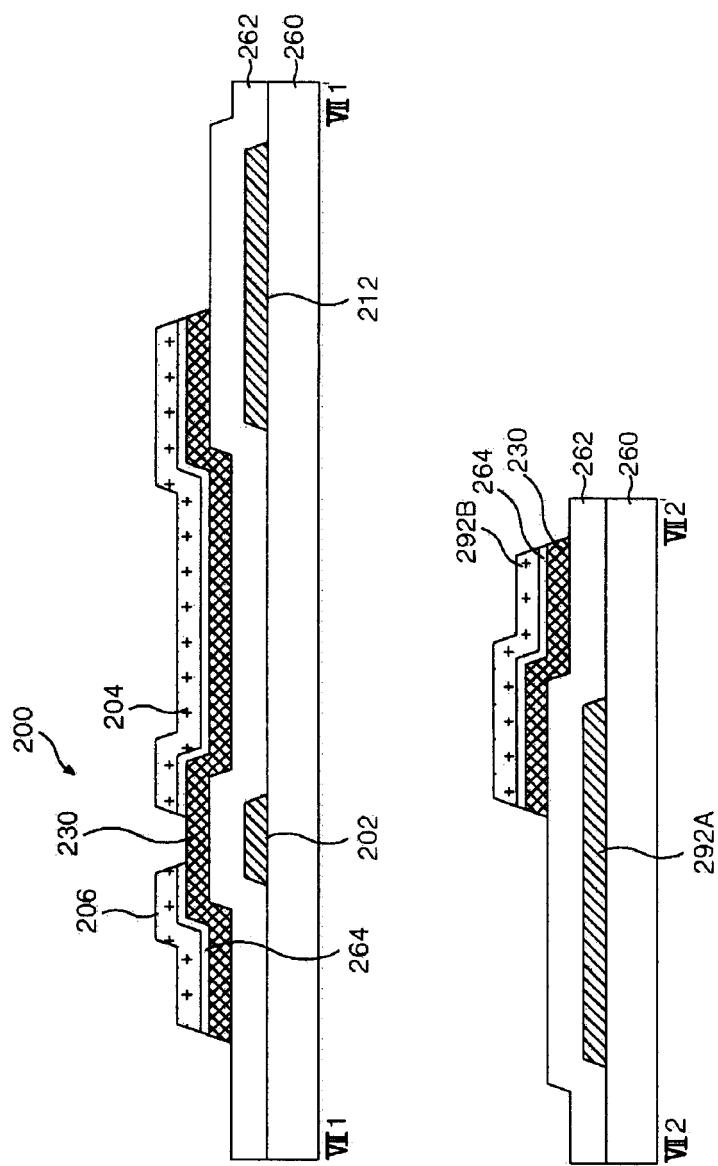

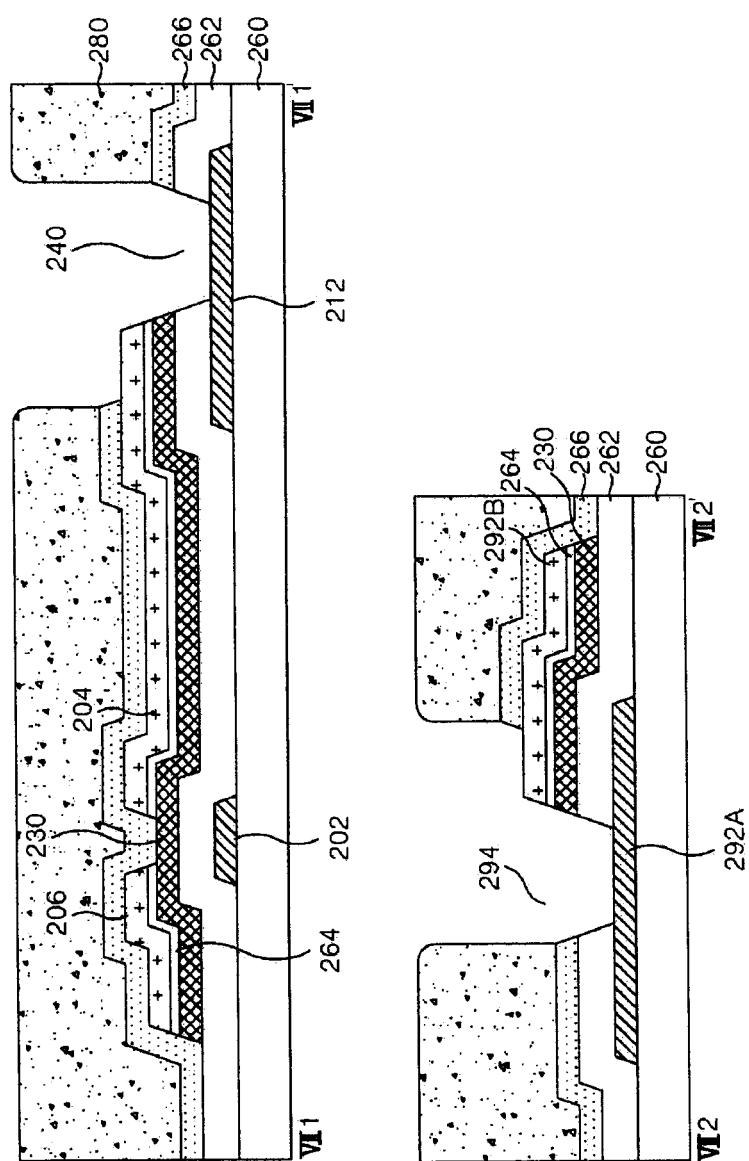

图 24A 和图 24B 的平面图和截面图分别用于解释按照本发明第五实施例的薄膜晶体管阵列基板的一种制造方法中的第一掩模工序。

在下基板 260 上用第一掩模工序形成包括栅极 202、212 和 222 的第一导电图案和第二偶数短路棒 292A。

具体地说，用诸如溅射等淀积技术在下基板 260 上形成栅极金属层。然后用光刻术对第一导电层构图并且用第一掩模蚀刻，形成包括栅极 202、212 和 222 的第一导电图案和第二偶数短路棒 292A。此处的第一导电层由 Cr、MoW、Cr/Al、Cu、Al (Nd)、Mo/Al、Mo/Al (Nd)、Cr/Al (Nd) 等形成。

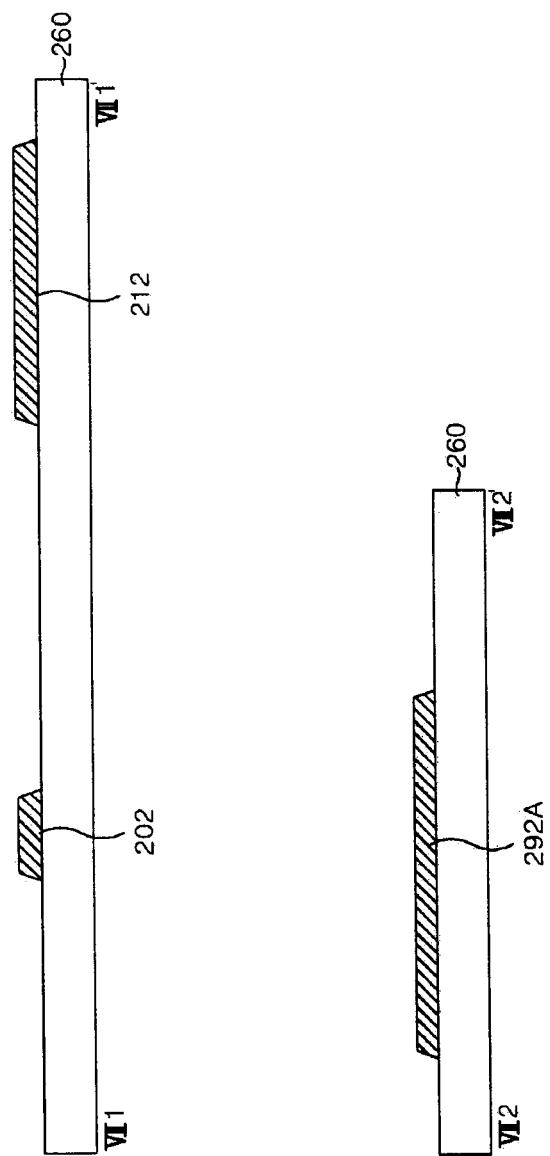

图 25A 和图 25B 的平面图和截面图分别用于解释按照本发明第五实施例的薄膜晶体管阵列基板的一种制造方法中的第二掩模工序，而图 26A 到图 26D 的截面图用于详细解释第二掩模工序。

首先在设有第一导电图案的下基板 260 上用诸如 PECVD、溅射等淀积技术形成整个栅极绝缘膜 262。栅极绝缘膜 262 由诸如氮化硅 (SiNx) 或氧化硅 (SiOx) 等无机绝缘材料形成。

接着用第二掩模工序形成设置在栅极绝缘膜 262 上并包括有源层 230 和 欧姆接触层 262 的半导体图案以及包括源极 204、214 和 224，漏极 206、216 和 226 及数据链 258，下数据焊盘电极 252，奇数短路棒 291 和第一偶数短路棒 292B 的第二导电图案。

具体地说，如图 26A 中所示，用诸如 PECVD、溅射等淀积技术在栅极绝缘膜 262 上依次形成非晶硅层 230A、n+非晶硅层 264A 和第二导电层 272。第二导电层由 Cr、MoW、Cr/Al、Cu、Al (Nd)、Mo/Al、Mo/Al (Nd)、Cr/Al (Nd) 等形成。然后在整个第二导电层 272 上涂覆一层光刻胶，然后用一局部曝光掩模即第二掩模采用光刻术形成如图 26A 所示具有阶梯覆层的光刻胶图案 270。在这种情况下，在需要形成薄膜晶体管沟道的部分具有一衍射曝光部分（或是半透射部分）的局部曝光掩模被用作第二掩模。这样，对应着第二

掩模的衍射曝光部分（或是半透射部分）的光刻胶图案 270 所具有的高度低于对应着第二掩模的透射部分（或屏蔽部分）的光刻胶图案 270 的高度。换句话说，沟道部分的光刻胶图案的高度要低于源极/漏极金属图案部分的光刻胶图案的高度。

5 采用光刻胶图案 270 按湿蚀刻法对第二导电层 272 构图，形成如图 26B 所示的包括源极 204、214 和 224，与源极 204、214 和 224 成一体的漏极 206、216 和 226，数据链 258，下数据焊盘电极 252，奇数短路棒 291 和第一偶数短路棒 292B 的第二导电图案。进而用同一光刻胶图案 270 按干蚀刻法对 n+ 非晶硅层 264A 和非晶硅层 230A 同时构图，如图 26B 所示，沿着第二导电图案形成欧姆接触层 264 和有源层 230 的结构。

10

接着，如图 26C 所示，采用氧 (O<sub>2</sub>) 等离子体的灰化工序去除高度比较低的沟道部位上的光刻胶图案 270，并且去除源极/漏极金属图案部位上高度降低的光刻胶图案 270。如图 26C 所示用剩余的光刻胶图案 270 按干法蚀刻从需要形成沟道的部位蚀刻第二导电层和欧姆接触层 264，使源极 204、214 和 224 与漏极 206、216 和 226 分离，并且暴露出有源层 230。这样就能在各个源极 204、214 和 224 与各个漏极 206、216 和 226 之间限定一由有源层 230 构成的沟道。

15

接着通过剥离完全去除第二导电图案部分上的剩余光刻胶图案 270。

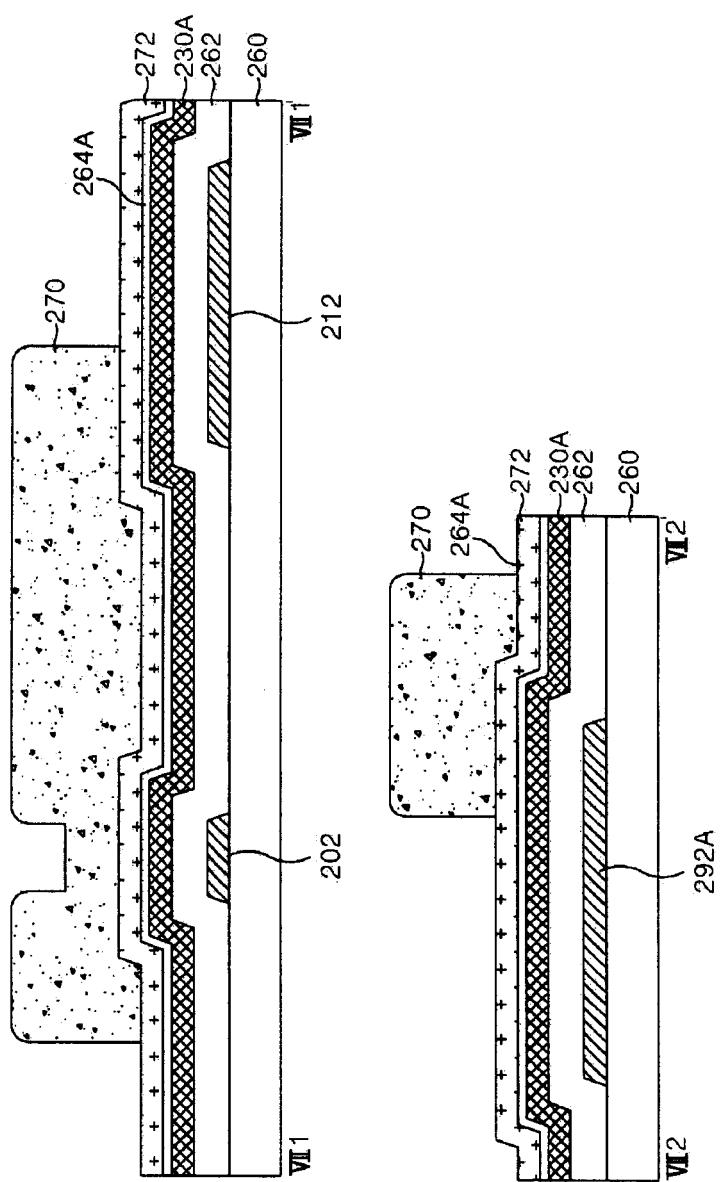

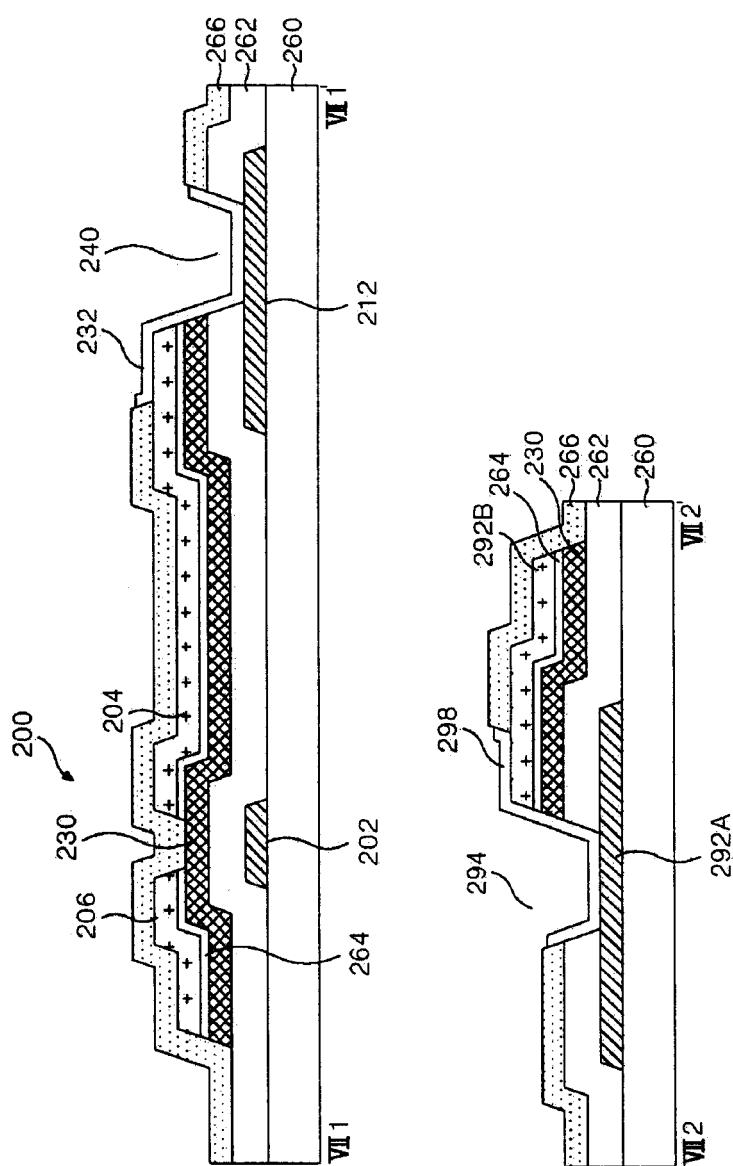

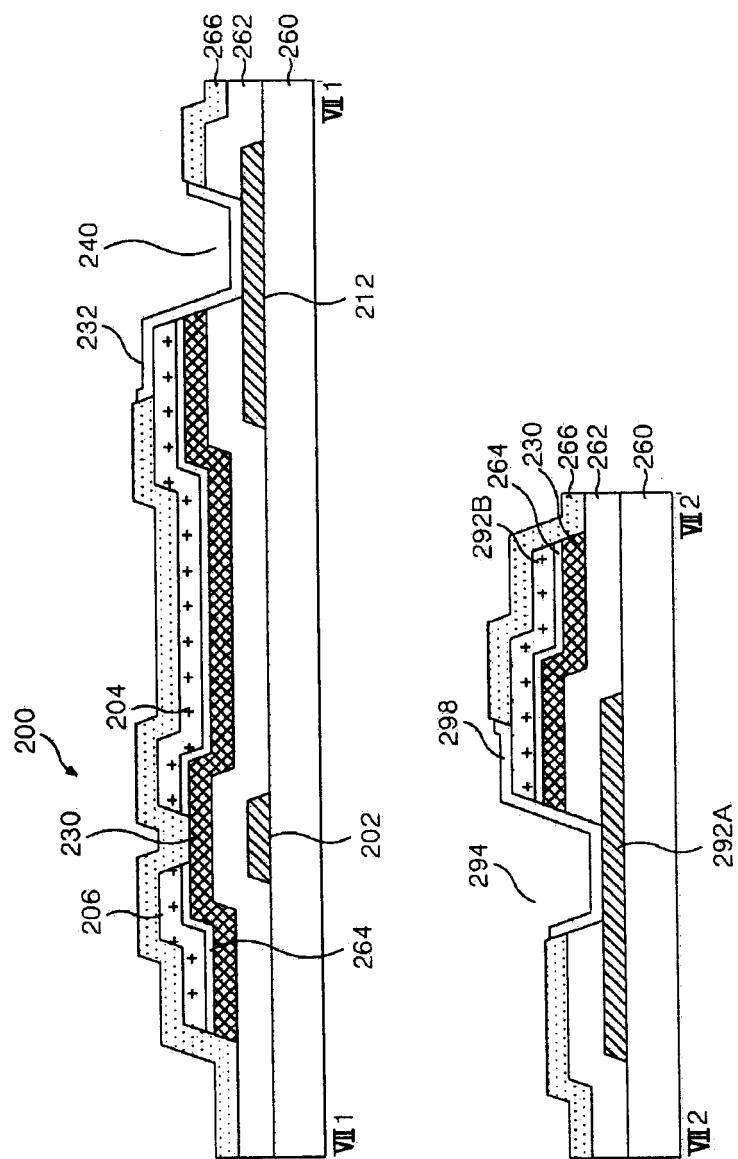

图 27A 和图 27B 的平面图和截面图分别用于解释按照本发明第五实施例 20 的薄膜晶体管阵列基板的一种制造方法中的第三掩模工序，而图 28A 到图 28D 的截面图用于详细解释第三掩模工序。

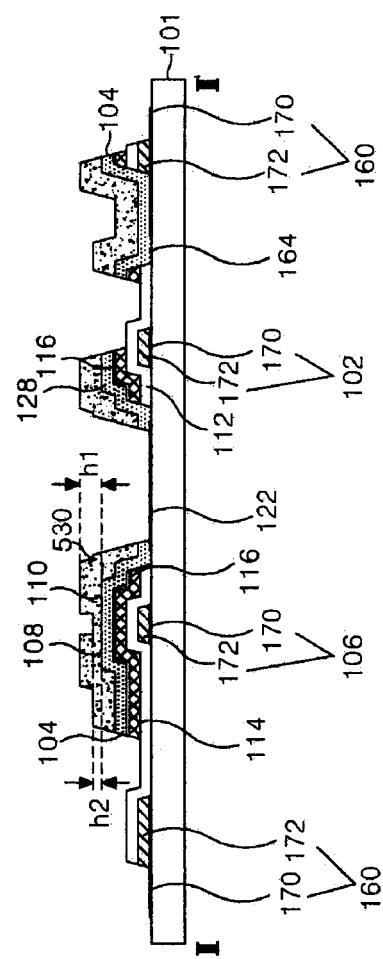

采用第三掩模工序对整个保护膜 266 和栅极绝缘膜 262 构图，限定接触孔 240、244、248 和 294，并且连同上数据焊盘电极 254 形成包括接触电极 232、234、236 和 298 的第三导电图案。第三导电图案接触到构图的保护膜 266。

25

具体地说，如图 28A 所示，在设有第二导电图案的整个栅极绝缘膜 262 上形成保护膜 266。保护膜 266 由类似于栅极绝缘膜 262 的无机绝缘材料或有机绝缘材料制成。进而，如图 28A 所示，用第三掩模按光刻术在存在保护膜 266 的部分的整个保护膜 266 上形成光刻胶图案 280。

30

接着用光刻胶图案 280 进行蚀刻，如图 28B 所示，对保护膜 266 和栅极绝缘膜 262 构图形成第一到第四接触孔 240、244、248 和 294 连同第五接触孔。

第一接触孔 240 暴露出第二源极 214 和栅极 212；第二接触孔 244 暴露出第三漏极 226 和第一栅极 202；第三接触孔 248 暴露出第三源极 224 和栅极 222；第四接触孔 294 暴露出第一和第二偶数短路棒 292A 和 292B；而第五接触孔暴露出下数据焊盘电极 252。

5 如图 28C 所示，在淀积完光刻胶图案 280 之后，在整个薄膜晶体管阵列基板上用溅射等淀积技术形成第三导电层 282。第三导电层 282 由透明导电材料制成，包括 ITO、TO、IZO、SnO<sub>2</sub> 等，或是具有强耐腐蚀性和高机械强度的钛 (Ti)。

接着，采用提升工序，同时去除光刻胶图案 280 及其上的第三导电层 282

10 以构图第三导电层 282。这样，如图 28D 所示，在第一到第四接触孔 240、244、

248 和 294 内形成接触电极 232、234、236 和 298，同时在第五接触孔内形成

15 上数据焊盘电极 254。第一接触电极 232 将第二源极 214 连接到栅极 212；第

二接触电极 234 将第三漏极 226 连接到第一栅极 202；第三接触电极 236 将第

三源极 224 连接到栅极 222；第四接触电极 298 将第一偶数短路棒 292B 连接

到第二偶数短路棒 292A；而第五接触孔将上数据焊盘电极 254 连接到下数据

焊盘电极 252。

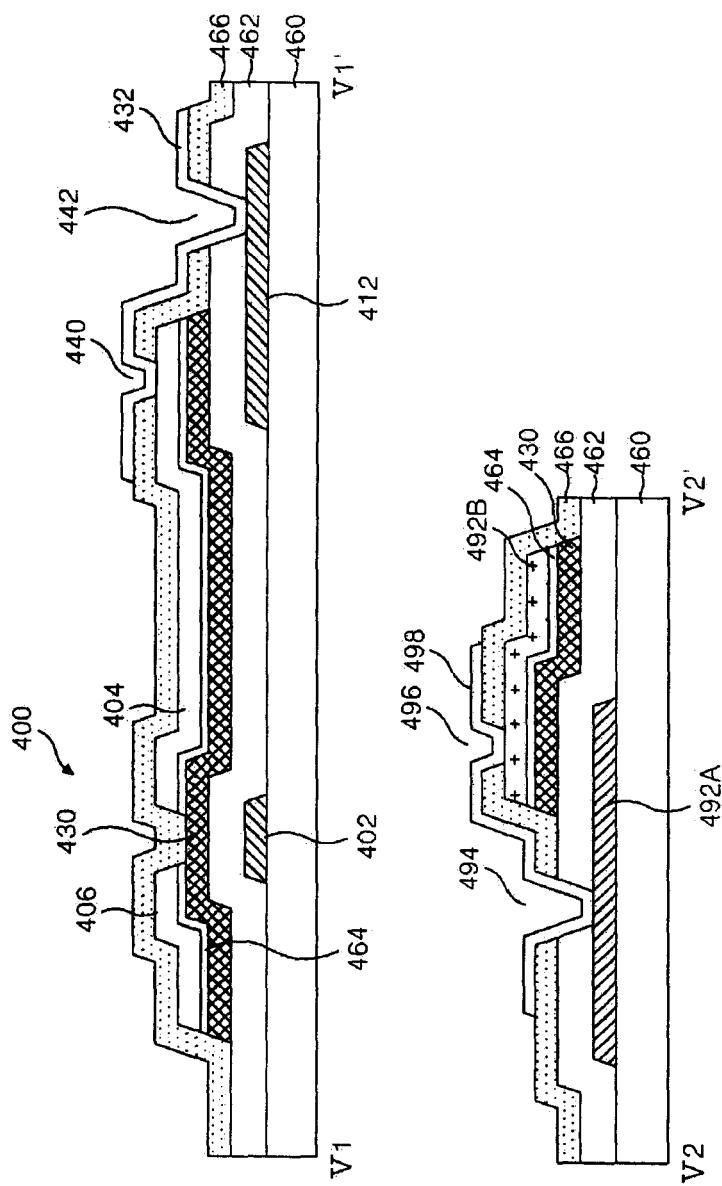

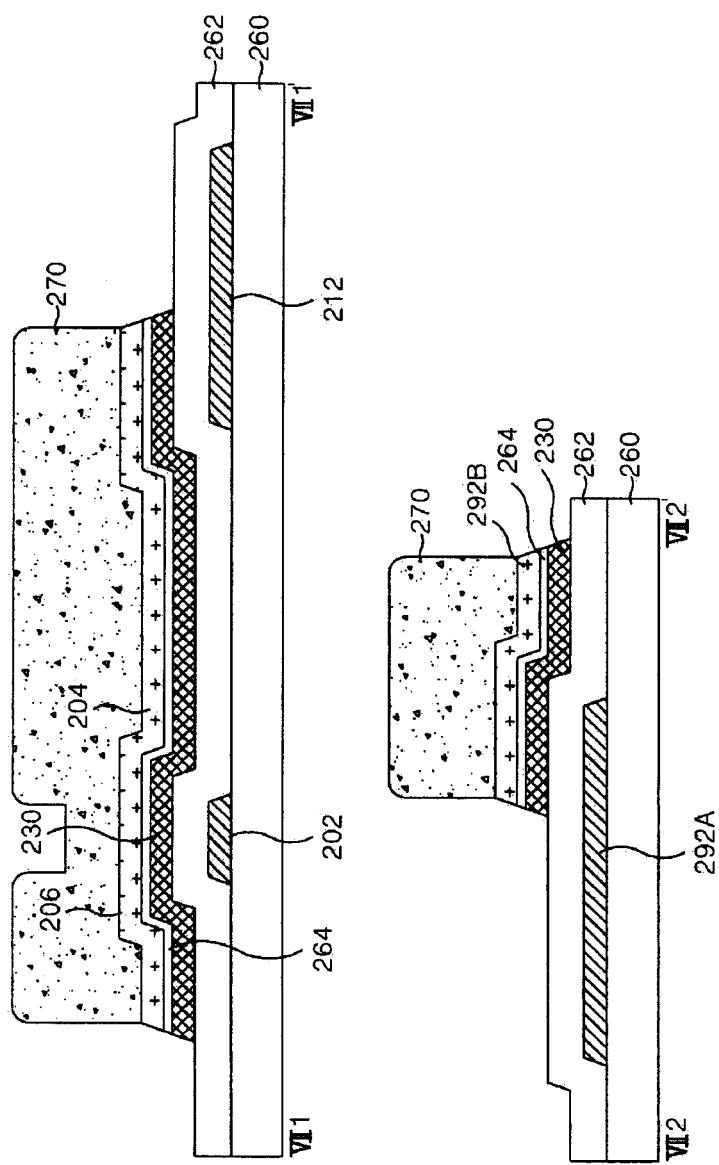

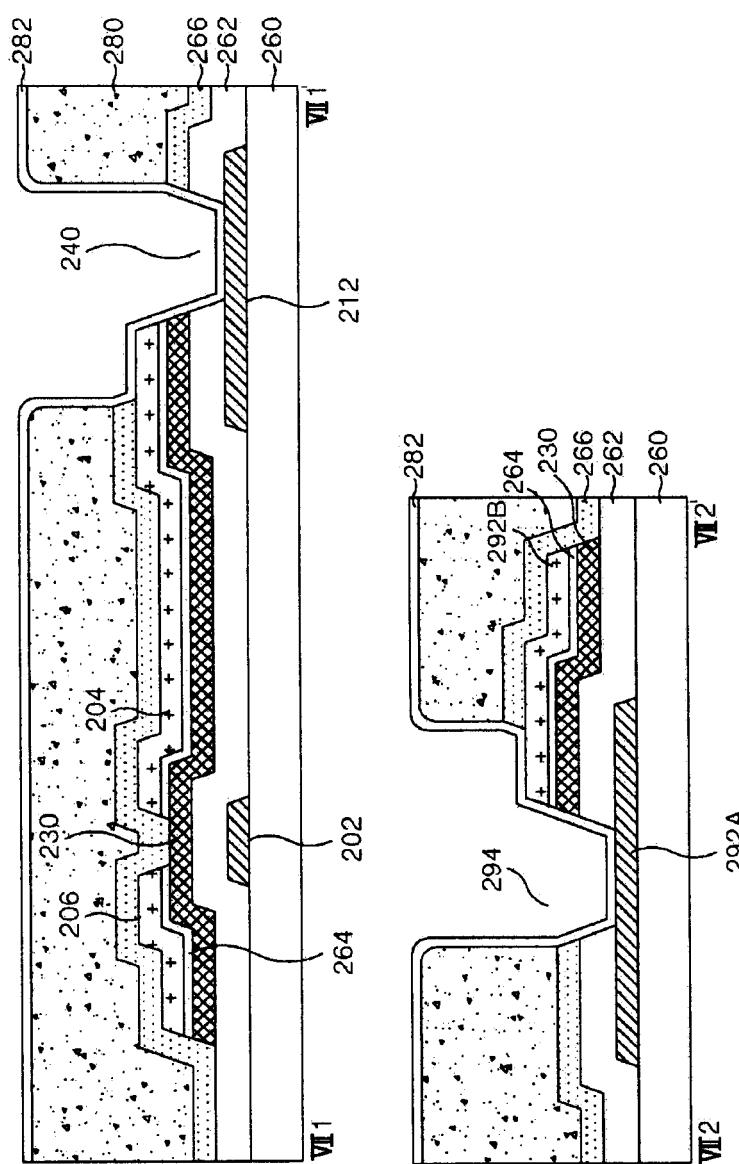

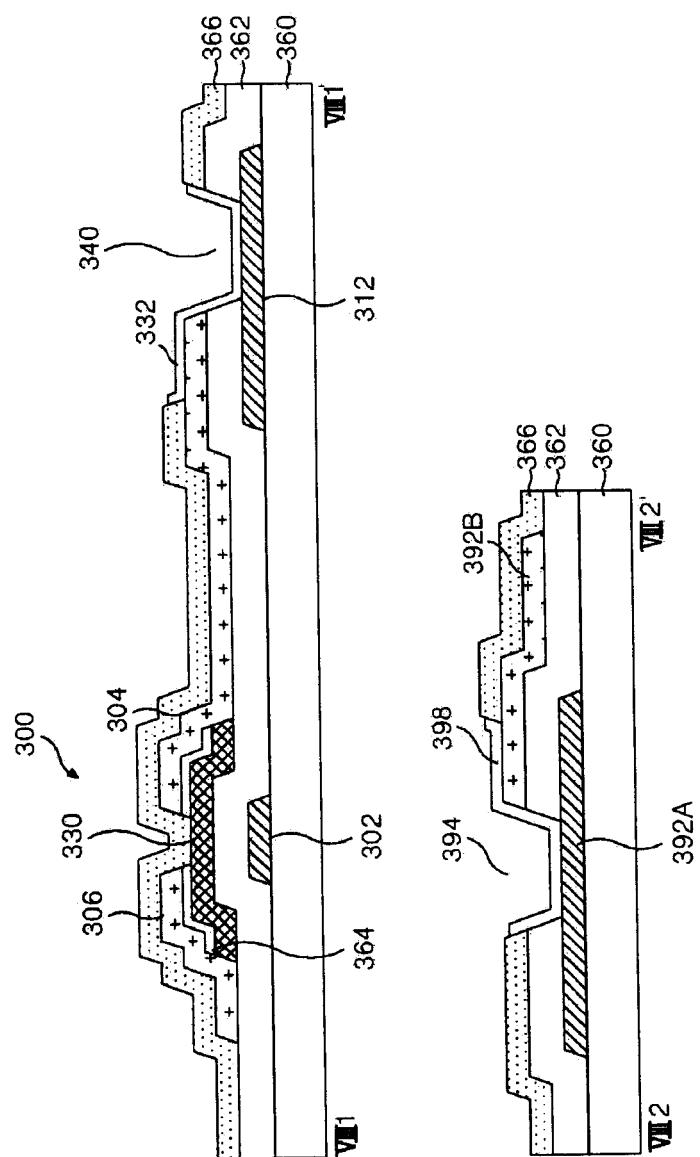

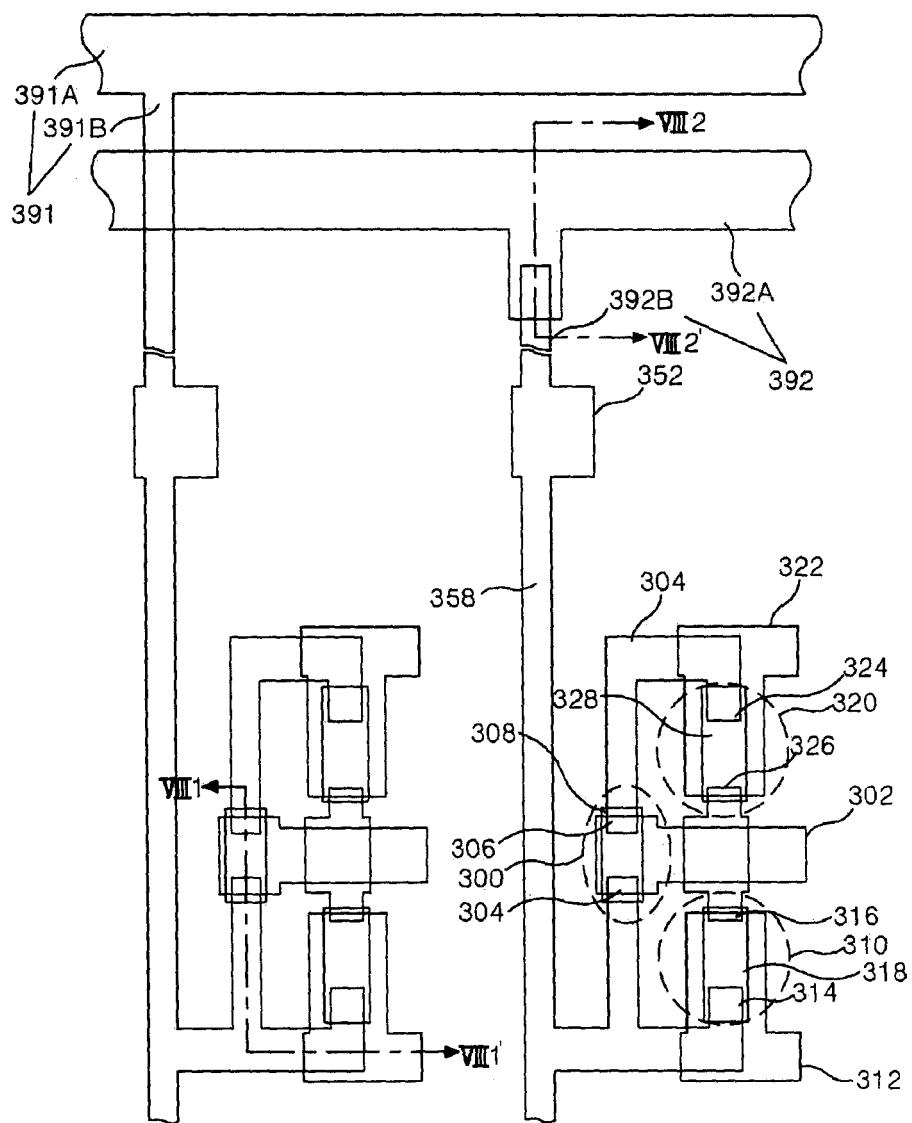

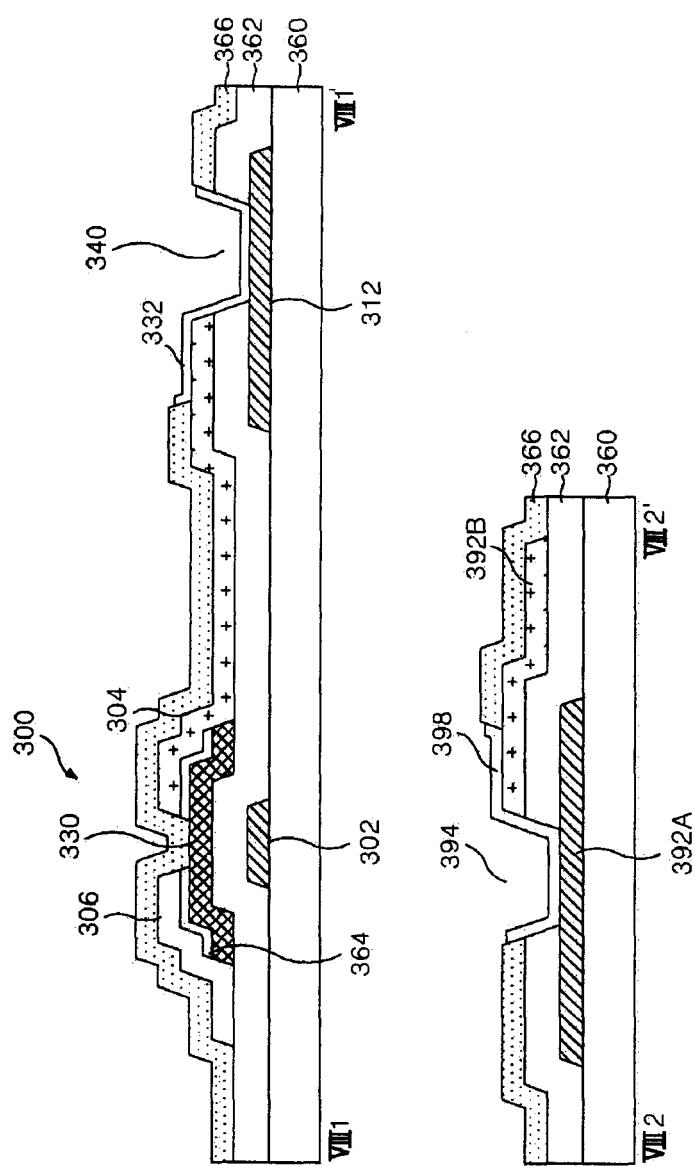

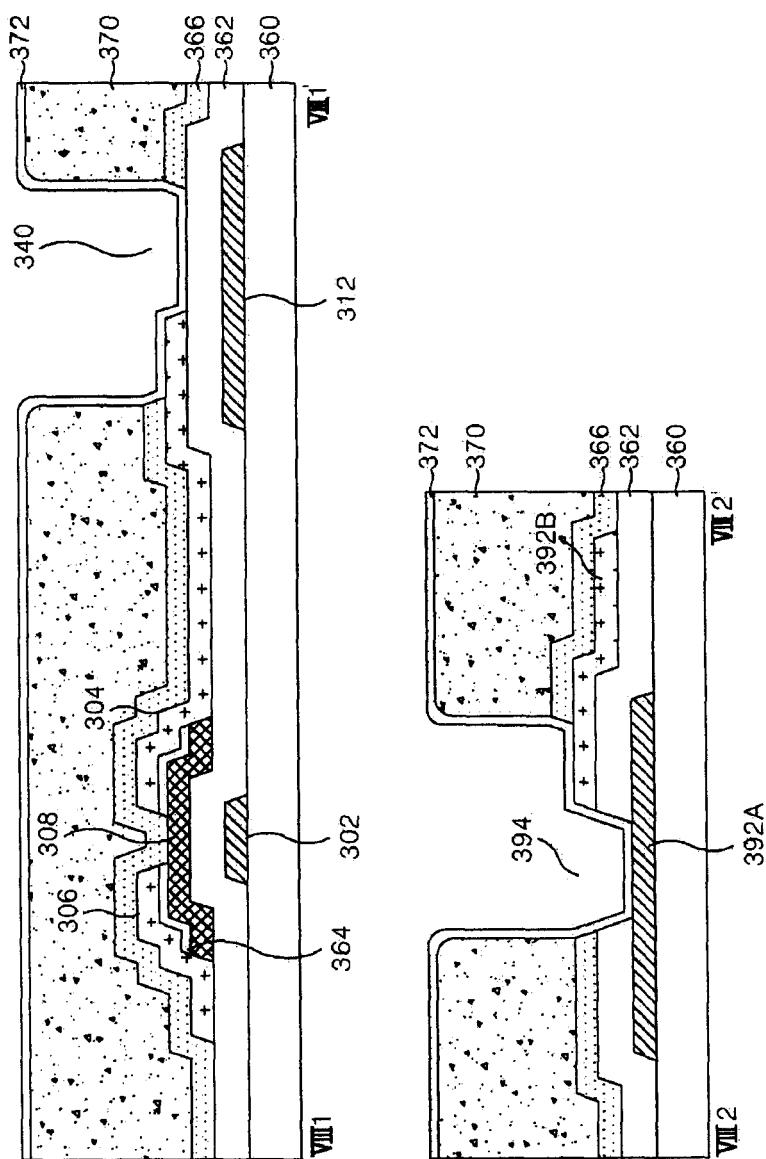

图 29 的平面图表示按照本发明第六实施例的薄膜晶体管阵列基板的防静电装置和短路棒区域，而图 30 是沿图 29 中 VIII1-VIII1' 线和 VIII2-VIII2' 线提取的防静电装置和短路棒区域的截面图。

20 图 29 和图 30 中所示的薄膜晶体管阵列基板与图 22 和图 23 中所示的元件基本相同，除了因其具有按四轮掩模工序形成的结构，仅仅在薄膜晶体管区上形成半导体层。因此省略了对相同元件的详细描述。

图 29 和图 30 中所示的防静电装置的第一到第三薄膜晶体管 300、310 和

25 320 包括独立的有源层 308、318 和 328，也就是说，仅在用于形成沟道的对应

区域上具有岛型有源层。还在有源层 308、318、328，源极 304、314、324 和

漏极 306、316、326 中的重叠部分形成欧姆接触层。

在第一接触孔 340 内形成将第二栅极 312 连接到源极 314 的第一接触电

极 332。在第二接触孔 344 内形成将第二漏极 326 连接到第一栅极 302 的第二

接触电极 334。在第三接触孔 348 内形成将第三源极 324 连接到栅极 322 的第

30 三接触电极 336。在第四接触孔 394 内形成将第一偶数短路棒 392B 连接到第

二偶数短路棒 392A 的第四接触电极 398。用提升方法去除用于对保护膜 366 和栅极绝缘膜 362 连同上数据焊盘电极 354 构图的光刻胶图案, 形成这些接触电极 332, 334 和 336。由此按如下所述用四轮掩模工序形成按照本发明第六实施例的薄膜晶体管阵列基板。

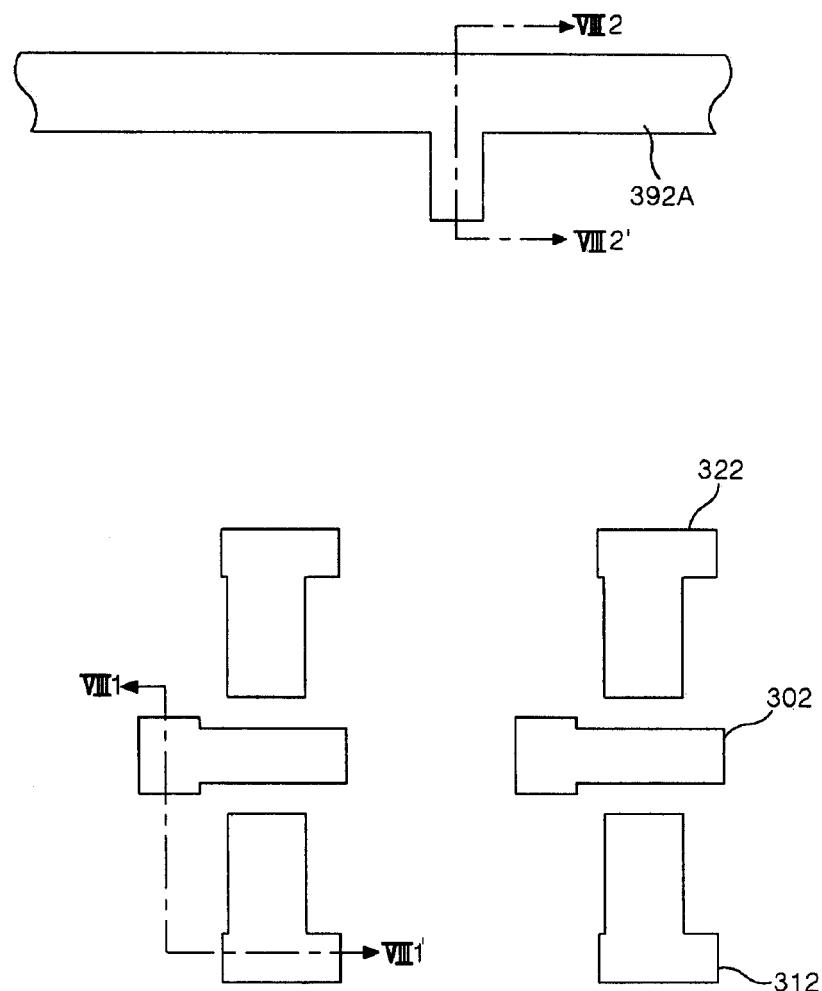

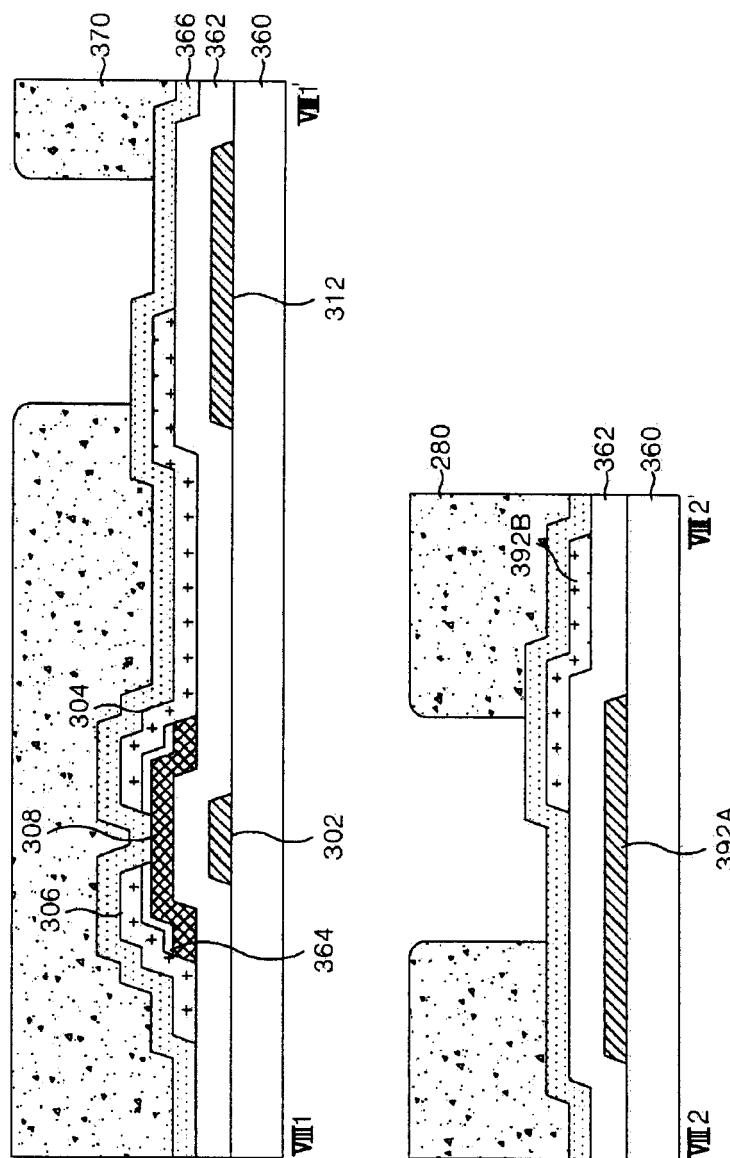

5 图 31A 和图 31B 的平面图和截面图分别用于解释按照本发明第六实施例的薄膜晶体管阵列基板的一种制造方法中的第一掩模工序。

用第一掩模工序在下基板 360 上形成包括栅极 302、312、322 和第二偶数短路棒 392A 的第一导电图案。具体地说, 在下基板 360 上用溅射等淀积技术形成第一导电图案。然后按光刻术对第一导电层构图并且用第一掩模蚀刻, 10 形成包括栅极 302、312、322 和第二偶数短路棒 392A 的第一导电图案。

图 32A 和图 32B 的平面图和截面图分别用于解释按照本发明第六实施例的薄膜晶体管阵列基板的一种制造方法中的第二掩模工序。

首先用诸如 PECVD、溅射等淀积技术在设有第一导电图案的整个下基板 360 上形成栅极绝缘膜 362。接着, 用第二掩模工序在栅极绝缘膜 362 上形成 15 包括第一到第三有源层 308、318、328 和欧姆接触层 364 的半导体图案。具体地说, 用诸如 PECVD、溅射等淀积技术在栅极绝缘膜 362 上形成非晶硅层和 n+ 非晶硅层。按光刻术对半导体图案构图并且用第二掩模蚀刻, 在对应着薄膜晶体管区的位置上形成半导体图案, 第一到第三有源层 308、318、328 和欧姆接触层 364。

20 图 33A 和图 33B 的平面图和截面图分别用于解释按照本发明第六实施例的薄膜晶体管阵列基板的一种制造方法中的第三掩模工序。

采用第三掩模工序在设有半导体图案的栅极绝缘膜 362 上形成包括源极 304、314 和 324, 漏极 306、316 和 326, 数据链 358, 下数据焊盘电极 352, 奇数短路棒 391 和第一偶数短路棒 392B 的第二导电图案。具体地说, 用诸如 25 PECVD、溅射等淀积技术在栅极绝缘膜 362 上形成第二导电层。按光刻术对第二导电层构图, 并且用第三掩模蚀刻, 形成源极 304、314 和 324, 漏极 306、316 和 326, 数据链 358, 下数据焊盘电极 352, 奇数短路棒 391 和第一偶数短路棒 392B。

然后, 用第二导电图案作为掩模干蚀刻暴露在源极 304、314 和 324 与漏 30 极 306、316 和 326 之间的欧姆接触层 364, 从而暴露出相应的有源层 308、318

和 328。

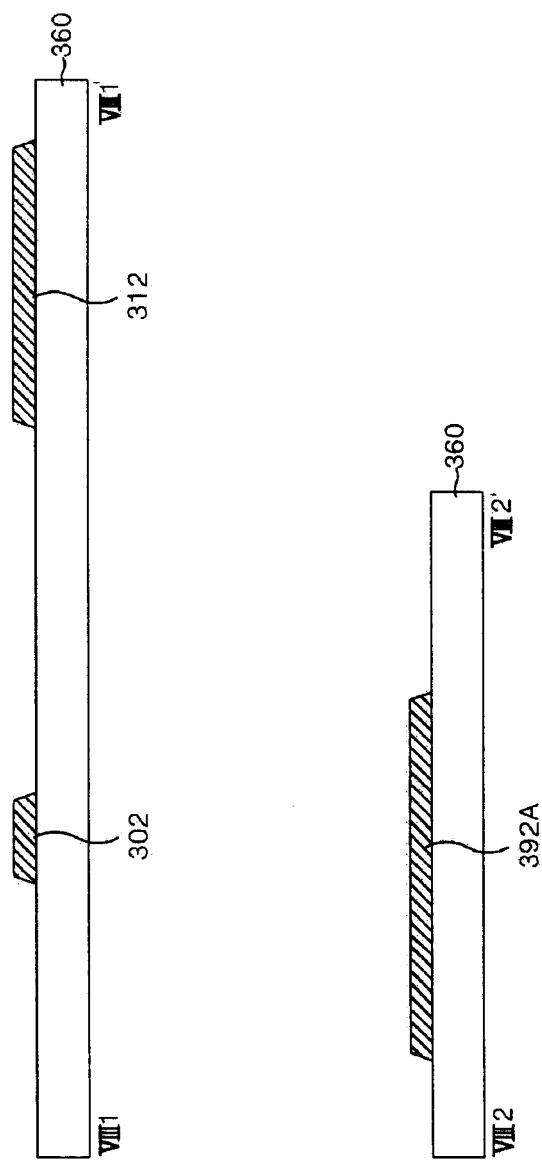

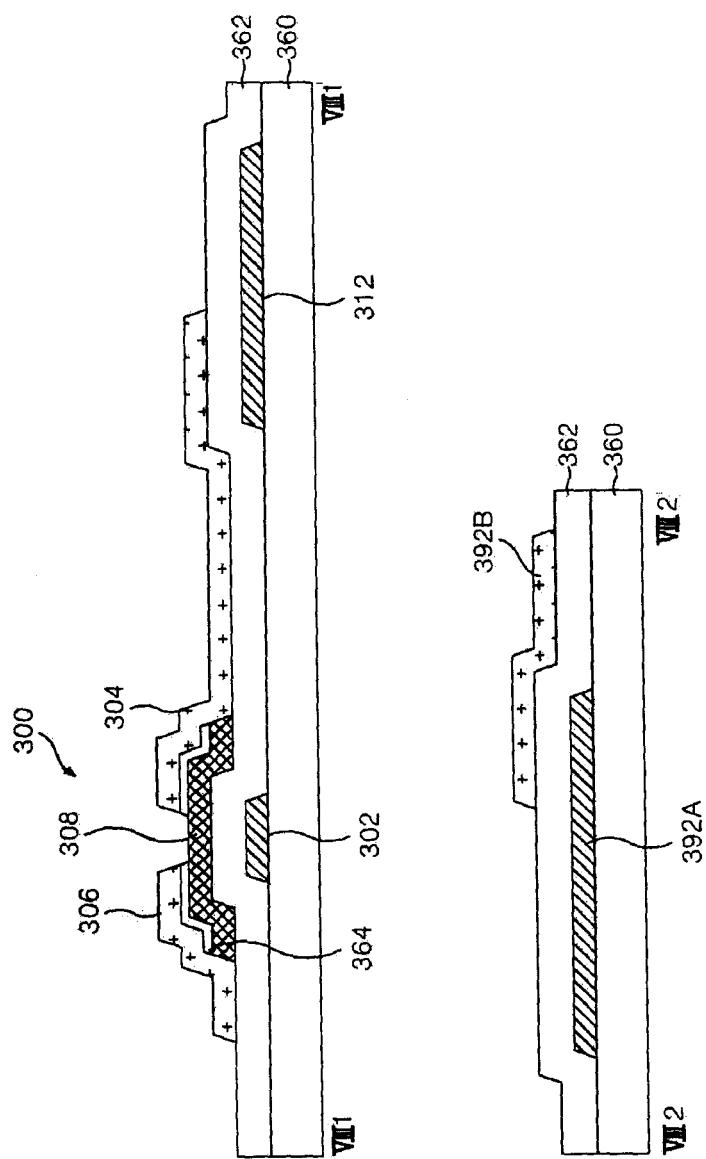

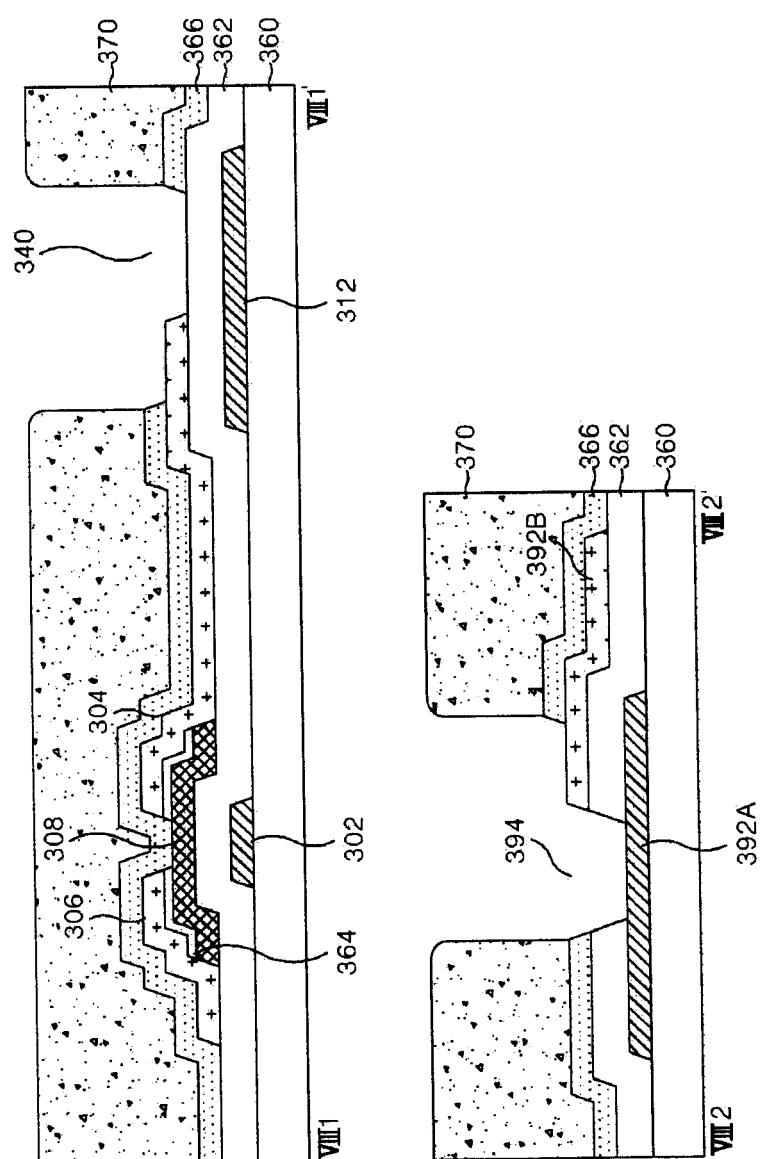

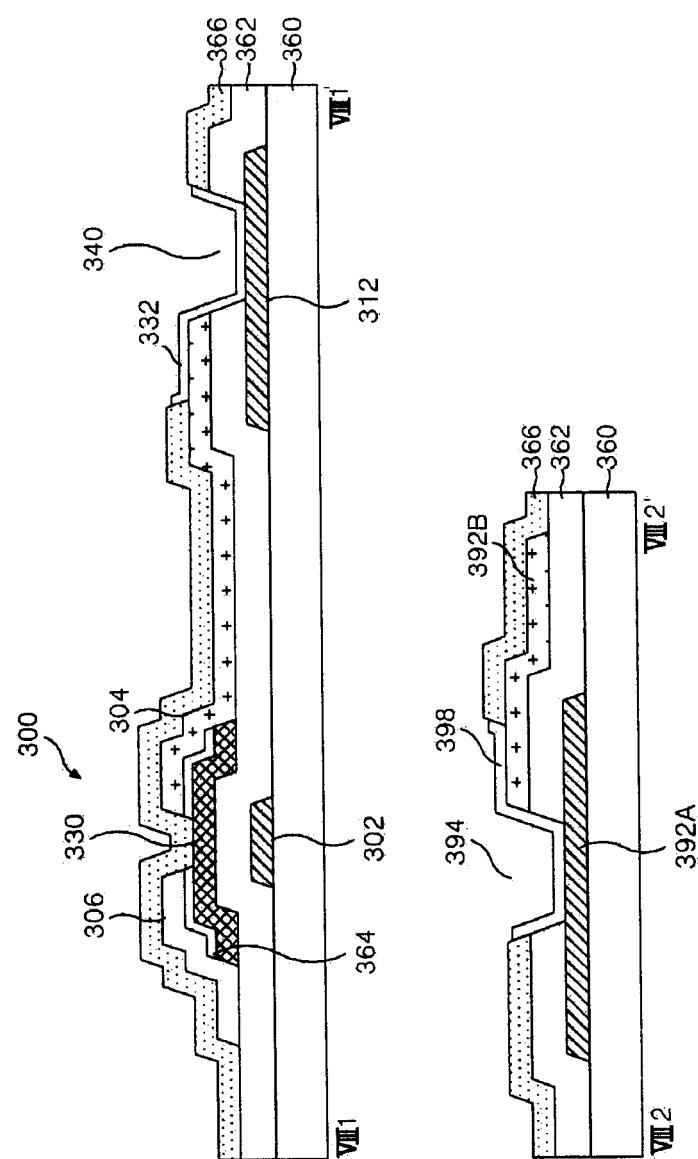

图 34A 和图 34B 的平面图和截面图分别用于解释按照本发明第六实施例的薄膜晶体管阵列基板的一种制造方法中的第四掩模工序, 而图 35A 到图 35D 的截面图用于详细解释第四掩模工序。

5 采用第四掩模工序对整个保护膜 366 和栅极绝缘膜 362 构图, 限定接触孔 340、344、348 和 394, 并且形成包括接触电极 332、334、336 和 398 的第三导电图案连同上数据焊盘电极 354。

具体地说, 如图 35A 所示, 在设有第二导电图案的整个栅极绝缘膜 362 上形成保护膜 366。进而, 如图 35A 所示, 用第三掩模按光刻术在存在保护膜 10 366 的部分的整个保护膜 366 上形成光刻胶图案 370。

接着, 如图 35B 所示, 用光刻胶图案 370 进行蚀刻, 对保护膜 366 和栅极绝缘膜 362 构图以形成第一到第四接触孔 340、344、348 和 394 连同第五接触孔。第一接触孔 340 暴露出第二源极 314 和栅极 312; 第二接触孔 344 暴露出第三漏极 326 和第一栅极 302; 第三接触孔 348 暴露出第三源极 324 和栅极 15 322; 第四接触孔 394 暴露出第一和第二偶数短路棒 392B 和 392A; 而第五接触孔暴露出下数据焊盘电极 352。

如图 35C 所示, 在形成光刻胶图案 370 之后, 在整个薄膜晶体管阵列基板上用溅射等淀积技术形成第三导电层 372。第三导电层 372 由透明导电层制成, 包括 ITO、TO、IZO、SnO<sub>2</sub> 等, 或是具有强耐腐蚀性和高机械强度的钛 20 (Ti)。

接着, 采用提升方法同时去除光刻胶图案 370 及其上的第三导电层 372 以构图第三导电层 372。这样, 如图 35D 所示, 在第一到第四接触孔 340、344、348 和 394 内形成接触电极 332、334、336 和 398, 同时在第五接触孔内形成上数据焊盘电极 354。

25 如上所述, 按照本发明, 薄膜晶体管阵列基板用三轮掩模工序形成, 这样能简化结构和制造工序以降低成本并提高产量。另外, 按照本发明, 如果用不同的金属形成信号线和信号焊盘, 形成接触孔可以暴露出信号线和/或信号焊盘的端部及其相邻区域。信号线通过接触孔电连接到信号焊盘, 能防止信号线和/或信号焊盘断裂。另外, 按照本发明, 暴露出第一和第二导电层的接触 30 孔一体形成。因此, 通过设在相应的接触孔内的接触电极暴露出来的第一和第

---

二导电层能够彼此连接并且具有降低的阶梯覆层，这样就能防止其断裂。

尽管以上按照附图的实施例解释了本发明，本领域的技术人员都能理解，本发明并不局限于这些实施例，无需脱离本发明的原理还能作出各种各样的修改和变更。因此，本发明的范围应该仅由权利要求书及其等同物限定。

图 1

图 2

图 3A

图 3B

30

图 3D

图 4

图 5

四

圖

图 6B

图 6C

图 7

图 8

6

图 10A

图 10B

图 11A

图 11B

图 12A

12B

图 13A

图 13C

图 13D

13E

冬

图 14

图 15

图 16

图 17A

图 17B

图 18

19

图 20

图 21

图 22

图 23

图 24A

图 24B

图 25A

图 25B

图 26A

图 26B

图 26C

图 26D

图 27A

图 27B

28A

图 28B

图 28C

图 28D

图 29

图 30

图 31A

图 31B

图 32A

图 32B

图 33A

图 33B

图 34A

图 34B

图 35A

图 35B

图 35C

图 35D

|                |                                                                                    |         |            |

|----------------|------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 薄膜晶体管阵列基板和液晶显示面板及它们的制造方法                                                           |         |            |

| 公开(公告)号        | <a href="#">CN1607432A</a>                                                         | 公开(公告)日 | 2005-04-20 |

| 申请号            | CN200410083701.2                                                                   | 申请日     | 2004-10-14 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                           |         |            |

| 申请(专利权)人(译)    | LG. 菲利浦LCD株式会社                                                                     |         |            |

| 当前申请(专利权)人(译)  | 乐金显示有限公司                                                                           |         |            |

| [标]发明人         | 南承熙<br>柳洵城<br>张允琼<br>赵兴烈                                                           |         |            |

| 发明人            | 南承熙<br>柳洵城<br>张允琼<br>赵兴烈                                                           |         |            |

| IPC分类号         | G02F1/1345 G02F1/1362 G02F1/1335 G02F1/136 G02F1/133 H01L29/786 H01L21/00 G02B5/20 |         |            |

| CPC分类号         | G02F1/136204 G02F1/1345 G02F2001/136231 H01L27/0296 H01L27/1244 H01L27/1288        |         |            |

| 代理人(译)         | 徐金国                                                                                |         |            |

| 优先权            | 1020030077660 2003-11-04 KR<br>1020030071403 2003-10-14 KR                         |         |            |

| 其他公开文献         | CN100335959C                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                     |         |            |

### 摘要(译)

本发明公开了一种基板，该基板具有交叉的、中间是栅极绝缘膜的栅极和数据线，设置在栅极和数据线交叉点上的薄膜晶体管，连接到晶体管的像素电极，通过接触孔连接到信号线并且包含有透明导电膜的焊盘，以及与滤色片阵列基板重叠并暴露出该膜的保护膜。所述接触孔暴露出焊盘和/或信号线的端部及其相邻区域。栅极、源极和漏极以及接触电极分别由第一、第二和第三导电层形成。接触孔暴露出一个晶体管的第一导电层和另一晶体管的第二导电层的相邻部分。接触电极连接暴露的第一和第二导电层。制造这种基板仅仅需要三轮掩模工序。