(12) 发明专利申请

(10) 申请公布号 CN 104614902 A

(43) 申请公布日 2015.05.13

(21) 申请号 201510094507.2

(51) Int. Cl.

(22) 申请日 2008.12.09

G02F 1/1343(2006.01)

(30) 优先权数据

G02F 1/1362(2006.01)

10-2008-0060328 2008.06.25 KR

G02F 1/1368(2006.01)

10-2008-0082964 2008.08.25 KR

H01L 27/12(2006.01)

(62) 分案原申请数据

200810183824.1 2008.12.09

(71) 申请人 乐金显示有限公司

地址 韩国首尔

(72) 发明人 宋相武 黄仁镐 朴大林 柳基贤

(74) 专利代理机构 北京三友知识产权代理有限公司 11127

代理人 黄纶伟

权利要求书3页 说明书15页 附图12页

(54) 发明名称

边缘场切换模式的液晶显示装置及其阵列基板

(57) 摘要

本发明提供了边缘场切换模式的液晶显示装置及其阵列基板。本发明的阵列基板包括：位于基板上的多条选通线；位于多条选通线上的栅绝缘层；多条数据线，该多条数据线位于栅绝缘层上，并且与多条选通线交叠以限定多个像素区域；电连接到选通线和数据线并且位于各像素区域内的薄膜晶体管；板状并且位于各像素区域内的像素电极，像素电极连接到薄膜晶体管的一部分；位于像素电极上并且位于薄膜晶体管上方的第一钝化层；和公共电极，该公共电极位于第一钝化层上并且具有位于各像素区域内的条状的多个开口，各开口具有沿数据线的长轴和沿选通线的短轴，其中各开口的中部与像素电极交叠，并且各开口的沿长轴的两个端部突出到像素电极之外。

1. 一种用于边缘场切换模式的液晶显示装置的阵列基板, 该阵列基板包括:

- 位于基板上的多条选通线;

- 位于所述多条选通线上的栅绝缘层;

- 多条数据线, 所述多条数据线位于所述栅绝缘层上并且与所述多条选通线交叉以限定多个像素区域;

- 电连接到所述选通线和所述数据线并且位于各像素区域内的薄膜晶体管;

- 板状并且位于所述各像素区域内的像素电极, 所述像素电极连接到所述薄膜晶体管的一部分;

- 第一钝化层, 所述第一钝化层位于所述栅绝缘层与所述像素电极之间, 并且所述第一钝化层具有露出所述薄膜晶体管的所述一部分的接触孔, 其中位于所述第一钝化层上的所述像素电极通过所述接触孔连接到所述薄膜晶体管的所述一部分,

- 位于所述像素电极上并且位于所述薄膜晶体管上方的第二钝化层; 以及

- 公共电极, 所述公共电极位于所述第二钝化层上, 并且具有位于所述各像素区域内的条状的多个开口, 各所述开口具有沿所述数据线的长轴和沿所述选通线的短轴, 其中各所述开口的中部与所述像素电极交叠, 而各所述开口的沿长轴的两个端部突出到所述像素电极之外,

- 其中所述多个开口中最外端的开口的沿短轴的端部突出到所述像素电极之外,

- 其中所述公共电极进一步包括对应于所述薄膜晶体管的另一开口,

- 其中, 所述薄膜晶体管的栅极是所述选通线的一部分, 使得所述薄膜晶体管形成在所述选通线上,

- 其中, 沿着所述短轴方向的所述像素电极的端部位于所述最外端的开口中。

2. 根据权利要求 1 所述的阵列基板, 其中各所述开口沿各条数据线穿过所述像素区域。

3. 一种用于边缘场切换模式的液晶显示装置的阵列基板, 该阵列基板包括:

- 位于基板上的多条选通线;

- 位于所述多条选通线上的栅绝缘层;

- 多条数据线, 所述多条数据线位于所述栅绝缘层上并且与所述多条选通线交叉以限定多个像素区域;

- 电连接到所述选通线和所述数据线并且位于各像素区域内的薄膜晶体管;

- 板状并且位于各像素区域内的像素电极, 所述像素电极连接到所述薄膜晶体管的一部分;

- 第一钝化层, 所述第一钝化层位于所述栅绝缘层与所述像素电极之间, 并且所述第一钝化层具有露出所述薄膜晶体管的所述一部分的接触孔, 其中位于所述第一钝化层上的所述像素电极通过所述接触孔连接到所述薄膜晶体管的所述一部分,

- 位于所述像素电极上并且位于所述薄膜晶体管上方的第二钝化层; 以及

- 位于所述第二钝化层上并且具有位于各像素区域内的条状的多个开口的公共电极, 各所述开口具有沿所述数据线的长轴和沿所述选通线的短轴, 其中各所述开口的中部与所述像素电极交叠, 而所述多个开口中最外端的开口的沿短轴的端部突出到所述像素电极之外,

其中所述公共电极进一步包括对应于所述薄膜晶体管的另一开口，

其中，所述薄膜晶体管的栅极是所述选通线的一部分，使得所述薄膜晶体管形成在所述选通线上，

其中，沿着所述短轴方向的所述像素电极的端部位于所述最外端的开口中。

4. 一种边缘场切换模式的液晶显示装置，该液晶显示装置包括：

彼此面对的第一基板和第二基板；

位于所述第一基板上的多条选通线；

位于所述多条选通线上的栅绝缘层；

多条数据线，所述多条数据线位于所述栅绝缘层上，并且与所述多条选通线交叉以限定多个像素区域；

电连接到所述选通线和所述数据线并且位于各像素区域内的薄膜晶体管；

板状并且位于各像素区域内的像素电极，所述像素电极连接到所述薄膜晶体管的一部分；

第一钝化层，所述第一钝化层位于所述栅绝缘层与所述像素电极之间，并且所述第一钝化层具有露出所述薄膜晶体管的所述一部分的接触孔，其中位于所述第一钝化层上的所述像素电极通过所述接触孔连接到所述薄膜晶体管的所述一部分，

位于所述像素电极上并且位于所述薄膜晶体管上方的第二钝化层；

位于所述第二钝化层上并且具有位于各像素区域内的条状的多个开口的公共电极，各所述开口具有沿所述数据线的长轴和沿所述选通线的短轴，其中各开口的中部与所述像素电极交叠，并且各开口的沿长轴的两个端部突出到所述像素电极之外；

位于所述第二基板上并且围绕各像素区域的黑底；

位于所述第二基板上并且对应于各像素区域的滤色层；以及

位于所述第一基板与所述第二基板之间的液晶层，

其中所述多个开口中最外端的开口的沿短轴的端部突出到所述像素电极之外，

其中，所述薄膜晶体管的栅极是所述选通线的一部分，使得所述薄膜晶体管形成在所述选通线上，

其中，沿着所述短轴方向的所述像素电极的端部位于所述最外端的开口中。

5. 根据权利要求 4 所述的液晶显示装置，其中各所述开口沿各数据线穿过所述像素区域。

6. 一种边缘场切换模式的液晶显示装置，该液晶显示装置包括：

彼此面对的第一基板和第二基板；

位于所述第一基板上的多条选通线；

位于所述多条选通线上的栅绝缘层；

多条数据线，所述多条数据线位于所述栅绝缘层上，并且与所述多条选通线交叉以限定多个像素区域；

电连接到所述选通线和所述数据线并且位于各像素区域内的薄膜晶体管；

板状并且位于各像素区域内的像素电极，所述像素电极连接到所述薄膜晶体管的一部分；

第一钝化层，所述第一钝化层位于所述栅绝缘层与所述像素电极之间，并且所述第一

钝化层具有露出所述薄膜晶体管的所述一部分的接触孔,其中位于所述第一钝化层上的所述像素电极通过所述接触孔连接到所述薄膜晶体管的所述一部分,

位于所述像素电极上并且位于所述薄膜晶体管上方的第二钝化层;

位于所述第二钝化层上并且具有位于各像素区域内的条状的多个开口的公共电极,各所述开口具有沿所述数据线的长轴和沿所述选通线的短轴,其中各开口的中部与所述像素电极交叠,并且所述多个开口中最外端的开口的沿短轴的端部突出到所述像素电极之外;

位于所述第二基板上并且围绕各像素区域的黑底;

位于所述第二基板上并且对应于各像素区域的滤色层;以及

位于所述第一基板与所述第二基板之间的液晶层,

其中所述公共电极进一步包括对应于所述薄膜晶体管的另一开口,其中,所述薄膜晶体管的栅极是所述选通线的一部分,使得所述薄膜晶体管形成在所述选通线上,

其中,沿着所述短轴方向的所述像素电极的端部位于所述最外端的开口中。

## 边缘场切换模式的液晶显示装置及其阵列基板

[0001] 本申请是原案申请号为 200810183824.1 的发明专利申请（申请日：2008 年 12 月 9 日，发明名称：边缘场切换模式的液晶显示装置及其阵列基板）的分案申请。

### 技术领域

[0002] 本发明涉及边缘场切换 (FFS) 模式的液晶显示 (LCD) 装置，尤其涉及一种用于能够改进透光率和孔径比的 FFS 模式的 LCD 装置的阵列基板和包含该阵列基板的 FFS 模式的 LCD 装置。该 FFS 模式的 LCD 装置能够显示高质量图像。

### 背景技术

[0003] 本申请要求分别在 2008 年 6 月 25 日和 2008 年 8 月 25 日提交的韩国专利申请第 10-2008-0060328 号和第 10-2008-0082964 号的优先权，在此以引证的方式并入其全部内容，就像在此进行了完整阐述一样。

[0004] 相关技术液晶显示 (LCD) 装置利用液晶分子的光学各向异性和极化特性。由于液晶分子形状细而长，所以液晶分子具有确定的取向方向。通过施加横跨液晶分子的电场控制液晶分子的取向方向。当电场的强度或方向改变时，液晶分子的取向也发生改变。由于液晶分子光学各向异性之缘故，入射光线基于液晶分子的取向发生折射，因此能够通过控制光线的透射率来显示图像。

[0005] 由于包含薄膜晶体管 (TFT) 作为开关元件的 LCD 装置（称为有源矩阵 LCD (AM-LCD)）具有高分辨率和显示运动图像的优越特性，AM-LCD 装置已得到了广泛使用。

[0006] AM-LCD 装置包括阵列基板、滤色基板和夹在阵列基板与滤色基板之间的液晶层。阵列基板可以包括像素电极和 TFT，并且滤色基板可以包括滤色层和公共电极。AM-LCD 装置由像素电极与公共电极之间的电场驱动，从而产优良的透光率特性和孔径比特性。然而，因为 AM-LCD 装置使用垂直电场，因此 AM-LCD 装置具有较差的视角。

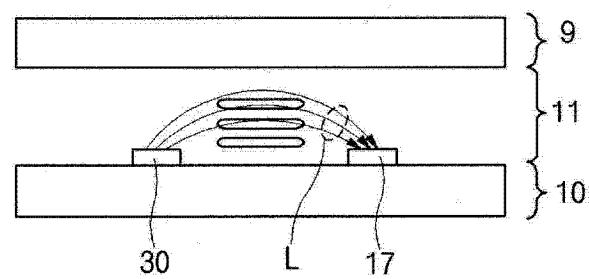

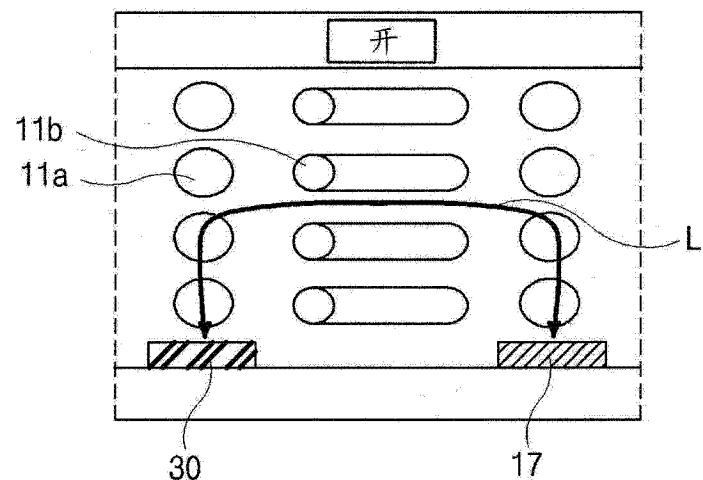

[0007] 利用面内切换 (IPS) 模式的 LCD 装置可解决上述限制。图 1 为相关技术 IPS 模式的 LCD 装置的截面图。如图 1 所示，阵列基板与滤色基板互相分离并且互相面对。阵列基板包括第一基板 10、公共电极 17 和像素电极 30。虽然未示出，阵列基板可以包括比如 TFT、选通线、数据线。滤色基板包括比如第二基板 9、滤色层（未示出）。液晶层 11 夹在第一基板 10 与第二基板 9 之间。因为公共电极 17 与像素电极 30 在第一基板 10 上在相同的水平面上形成，因此在公共电极 17 与像素电极 30 之间产生了水平电场为“L”。

[0008] 图 2A 和图 2B 为示出相关技术 IPS 模式的 LCD 装置的开 / 关状态的截面图。如图 2 所示，当向 IPS 模式的 LCD 装置施加电压的时候，公共电极 17 和像素电极 30 上的液晶分子 11a 没有变化。但是由于水平电场“L”的原因，公共电极 17 与像素电极 30 之间的液晶分子 11b 水平排列。因为液晶分子通过水平电场排列，因此 IPS 模式的 LCD 装置具有宽视角的特性。图 2B 示出了当没有向 IPS 模式的 LCD 装置施加电压时的状态。因为公共电极 17 与像素电极 30 之间没有产生电场，因此液晶分子 11 的排列没有变化。然而，IPS 模式的 LCD 装置具有较差的孔径比和透光率。

[0009] 为了克服上述限制已经引入了边缘场切换 (FFS) 模式的 LCD 装置。在 FFS 模式的 LCD 装置中, 液晶分子通过边缘场驱动。

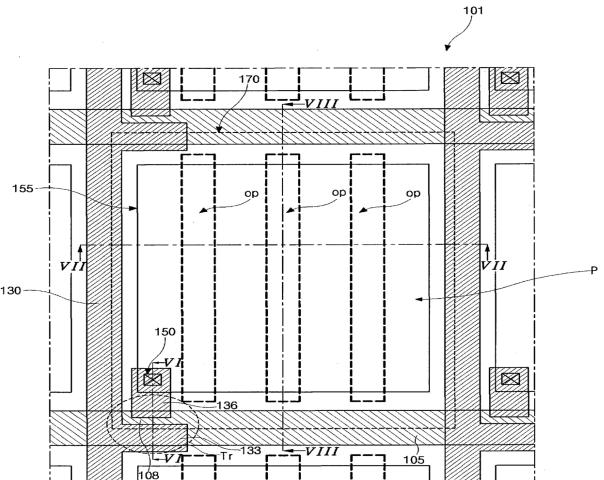

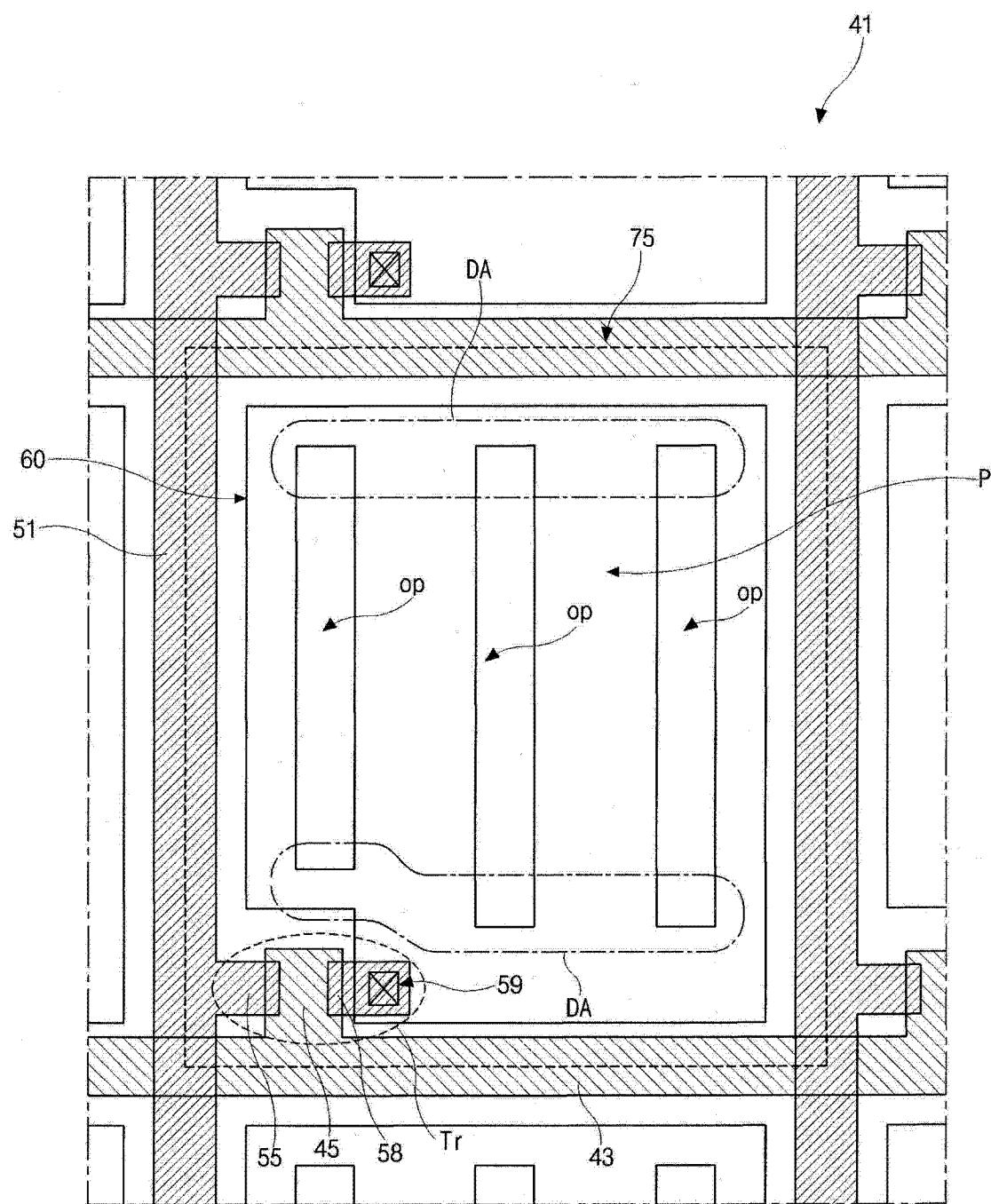

[0010] 图 3 为用于相关技术 FFS 模式的 LCD 装置的阵列基板的平面图。如图 3 所示, 阵列基板包括基板 41、选通线 43、数据线 51、薄膜晶体管 (TFT) “Tr”、公共电极 75 和像素电极 60。选通线 43 和数据线 51 形成于基板 41 上, 并且两者互相交叉以限定像素区域“P”。选通线 43 由于栅绝缘层 (未示出) 与数据线 51 绝缘。TFT “Tr” 形成于各像素区域“P”内, 并且连接到选通线 43 和数据线 51。TFT “Tr” 包括栅极 45、栅绝缘层、半导体层 (未示出)、源极 55 和漏极 58。栅极 45 连接到选通线 43, 而源极 55 连接到数据线 51。

[0011] 像素电极 60 形成于各像素区域“P”内。像素电极 60 通过漏接触孔 59 电连接到 TFT “Tr”的漏极 58。像素电极 60 为板状 (plate shape), 并且包括多个开口“op”。各开口“op”为条状。此外, 板状的公共电极 75 形成于基板 41 的显示区域的整个表面上。公共电极 75 与像素电极 60 交叠。虽然公共电极 75 形成于基板 41 的显示区域的整个表面上, 但是用虚线标示对应于一个像素区域“P”的公共电极 75。

[0012] 在具有以上结构的用于 FFS 模式的 LCD 装置的阵列基板内, 当电压施加至公共电极 75 与像素电极 60 上时, 在像素电极 60 与公共电极 75 之间产生边缘场。

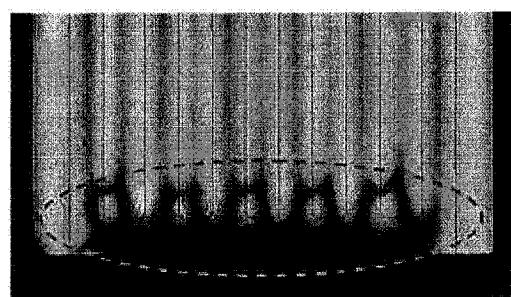

[0013] 在以上用于 FFS 模式的 LCD 装置的阵列基板内, 像素电极 60 的开口“op”与公共电极 75 完全交叠。在这种情况下, 在开口“op”沿开口“op”长轴的两个端部不能产生均匀电场。可以将产生非均匀电场的端部称为向错区域“DA”(disclination area)。也就是说, 向错区域“DA”内的液晶分子具有非均匀的排列。因为 FFS 模式的 LCD 装置在开状态下在向错区域“DA”内的透光率比其他区域低, 因此在向错区域“DA”内具有暗的图像 (dark image), 如图 4 所示, 该图示出了用于相关技术 FFS 模式的 LCD 装置的阵列基板的像素区域。

[0014] 由于向错区域的原因, FFS 模式的 LCD 装置的透光率和显示质量较低。

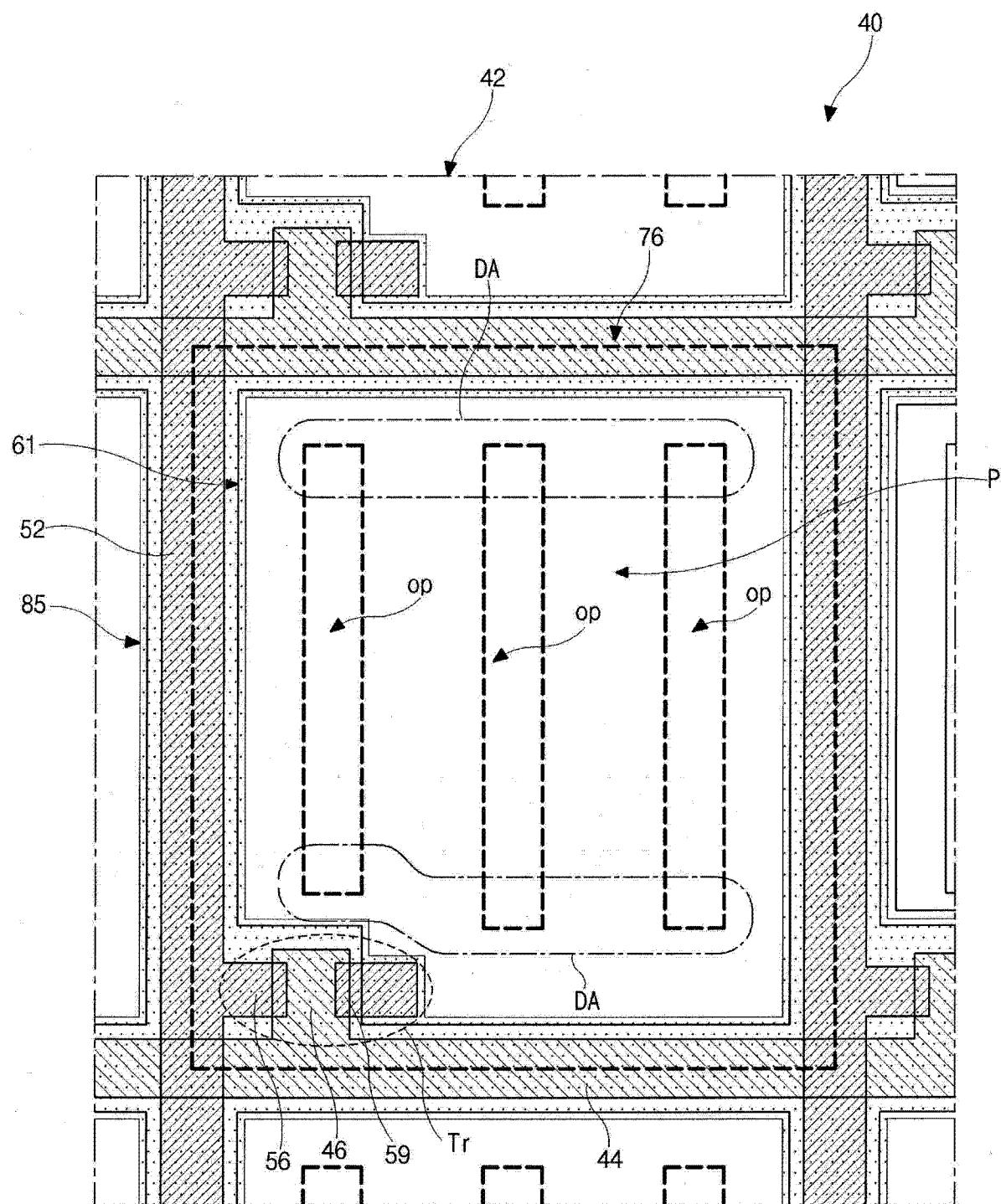

[0015] 图 5 为相关技术 FFS 模式的 LCD 装置的平面图。如图 5 所示, FFS 模式的 LCD 装置 40 包括第一基板 42、第二基板 (未示出) 和夹在两者之间的液晶层 (未示出)。

[0016] 第一基板 42 上形成有选通线 44、数据线 52、薄膜晶体管 (TFT) “Tr”、公共电极 76 和像素电极 61。选通线 44 与数据线 52 形成于第一基板 42 上, 并且互相交叉以限定像素区域“P”。选通线 44 由于栅绝缘层 (未示出) 与数据线 52 绝缘。TFT “Tr” 形成于各像素区域“P”内, 并且连接到选通线 44 和数据线 52。TFT “Tr” 包括栅极 46、栅绝缘层、半导体层 (未示出)、源极 56 和漏极 59。栅极 46 连接到选通线 44, 而源极 56 连接到数据线 52。

[0017] 像素电极 61 形成于各像素区域“P”内。像素电极 61 电连接到 TFT “Tr”的漏极 59。像素电极 61 为板状并且包括多个开口“op”。各开口“op”为条状。像素电极 61 设置在像素区域“P”的内部。也就是说, 像素电极 61 与选通线 44 和数据线 52 不交叠, 而且与选通线 44 和数据线 52 隔开预定距离。像素电极与选通线 44 和数据线 52 不交叠的原因在于: 当像素电极与选通线 44 和数据线 52 交叠并且两者之间设置有栅绝缘层 (未示出) 时, 选通线 44 与像素电极 61 之间以及数据线 52 与像素电极 61 之间存在寄生电容, 从而在电场内产生失真。因此, 为了避免这些问题, 像素电极与选通线 44 和数据线 52 不交叠。

[0018] 此外, 板状的公共电极 76 形成于第一基板 42 的显示区域的整个表面上。公共电极 76 与像素电极 61 交叠。虽然公共电极 76 形成于第一基板 42 的显示区域的整个表面上, 但是用虚线标示对应于一个像素区域“P”的公共电极 76。可以将在其上形成有选通线 44、

数据线 52、TFT “Tr”、像素电极 61 和公共电极 76 的第一基板 42 称为阵列基板。

[0019] 在具有上述结构的用于 FFS 模式的 LCD 装置的阵列基板内,当电压施加至公共电极 76 和像素电极 61 时,在像素电极 61 与公共电极 76 之间产生边缘场。

[0020] 在面对第一基板 42 的第二基板 (未示出) 上形成有滤色层 (未示出) 和黑底 85。滤色层包括红色、绿色和蓝色的滤色器图案。滤色器图案对应于像素区域“P”。黑底 85 设置为对应于像素区域“P”的边界。也就是说,黑底 85 对应于选通线 44、数据线 52 和 TFT “Tr”。

[0021] 在用于 FFS 模式的 LCD 装置的上述阵列基板内,像素电极 60 的开口“op”与公共电极 75 完全交叠。在这种情况下,在开口“op”沿开口“op”长轴的两个端部无法产生均匀电场。将产生非均匀电场的端部称为向错区域“DA”。也就是说,液晶分子在向错区域“DA”内具有非均匀排列。因为 FFS 模式的 LCD 装置在开状态下在向错区域“DA”的透光率比其他区域低,因此在向错区域“DA”内具有暗的图像。

[0022] 因为光线在向错区域内异常透射,因此显示质量降低。因此,将黑底 85 进行延伸以遮蔽向错区域“DA”。当黑底 85 具有较宽区域时,孔径比和透射率降低。

## 发明内容

[0023] 因此,本发明涉及用于 FFS 模式的 LCD 装置的阵列基板和包括该阵列基板的 FFS 模式的 LCD 装置,其基本上消除了由相关技术的限制和缺点所导致的一个或者多个问题。

[0024] 本发明的其它特征和优点将在下面的描述阐述中,并且从该说明部分地变得清楚,或者可通过本发明的实施而获知。通过在文字说明及其权利要求以及附图中具体指出的结构可以认识并实现本发明的这些目的和其他优点。

[0025] 为了实现这些目的和其它优点并且根据本发明的目的,如在此具体实施和广泛描述的,一种用于边缘场切换模式的液晶显示装置的阵列基板包括:位于基板上的多条选通线;位于所述多条选通线上的栅绝缘层;多条数据线,所述多条数据线位于所述栅绝缘层上并且与所述多条选通线交叉以限定多个像素区域;电连接到所述选通线和所述数据线并且位于各像素区域内的薄膜晶体管;板状并且位于所述各像素区域内的像素电极,所述像素电极连接到所述薄膜晶体管的一部分;第一钝化层,所述第一钝化层位于所述栅绝缘层与所述像素电极之间,并且所述第一钝化层具有露出所述薄膜晶体管的所述一部分的接触孔,其中位于所述第一钝化层上的所述像素电极通过所述接触孔连接到所述薄膜晶体管的所述一部分,位于所述像素电极上并且位于所述薄膜晶体管上方的第二钝化层;以及公共电极,所述公共电极位于所述第二钝化层上,并且具有位于所述各像素区域内的条状的多个开口,各所述开口具有沿所述数据线的长轴和沿所述选通线的短轴,其中各所述开口的中部与所述像素电极交叠,而各所述开口的沿长轴的两个端部突出到所述像素电极之外,其中所述多个开口中最外端的开口的沿短轴的端部突出到所述像素电极之外,其中所述公共电极进一步包括对应于所述薄膜晶体管的另一开口在本发明的另一方面中,一种用于边缘场切换模式的液晶显示装置的阵列基板包括:位于基板上的多条选通线;位于所述多条选通线上的栅绝缘层;多条数据线,所述多条数据线位于所述栅绝缘层上,并且与所述多条选通线交叉以限定多个像素区域;电连接到所述选通线和所述数据线并且位于各像素区域内的薄膜晶体管;板状并且位于各像素区域内的像素电极,所述像素电极连接到所述薄膜晶体管的一部分。

晶体管的一部分，并且与所述选通线的一部分交叠；第一钝化层，所述第一钝化层位于所述栅绝缘层与所述像素电极之间，并且所述第一钝化层具有露出所述薄膜晶体管的所述一部分的接触孔，其中位于所述第一钝化层上的所述像素电极通过所述接触孔连接到所述薄膜晶体管的所述一部分，位于所述像素电极上并且位于所述薄膜晶体管上方的第二钝化层；以及位于所述第二钝化层上并且具有位于各像素区域内的条状的多个开口的公共电极，各所述开口具有沿所述数据线的长轴和沿所述选通线的短轴，其中各开口的中部与所述像素电极交叠，并且各开口的沿长轴的两个端部与所述选通线交叠，其中所述公共电极进一步包括对应于所述薄膜晶体管的另一开口。

[0026] 在本发明另一方面中，一种用于边缘场切换模式的液晶显示装置的阵列基板包括：位于基板上的多条选通线；位于所述多条选通线上的栅绝缘层；多条数据线，所述多条数据线位于栅绝缘层上，并且与所述多条选通线交叉以限定多个像素区域；电连接到所述选通线和所述数据线并且位于各像素区域内的薄膜晶体管；板状并且位于各像素区域内的像素电极，所述像素电极连接到所述薄膜晶体管的一部分，并且与所述选通线的一部分交叠；第一钝化层，所述第一钝化层位于所述栅绝缘层与所述像素电极之间，并且所述第一钝化层具有露出所述薄膜晶体管的所述一部分的接触孔，其中位于所述第一钝化层上的所述像素电极通过所述接触孔连接到所述薄膜晶体管的所述一部分，位于所述像素电极上并且位于所述薄膜晶体管上方的第二钝化层；以及位于所述第二钝化层上并且具有位于各像素区域内的条状的多个开口的公共电极，各所述开口沿各数据线穿过所述像素区域，其中所述公共电极进一步包括对应于所述薄膜晶体管的另一开口。

[0027] 在本发明另一方面中，一种用于边缘场切换模式的液晶显示装置的阵列基板包括：位于基板上的多条选通线；位于所述多条选通线上的栅绝缘层；多条数据线，所述多条数据线位于所述栅绝缘层上，并且与所述多条选通线交叉以限定多个像素区域；电连接到所述选通线和所述数据线并且位于各像素区域内的薄膜晶体管；板状并且位于各像素区域内的像素电极，所述像素电极连接到所述薄膜晶体管的一部分，并且与所述选通线的一部分交叠；第一钝化层，所述第一钝化层位于所述栅绝缘层与所述像素电极之间，并且所述第一钝化层具有露出所述薄膜晶体管的所述一部分的接触孔，其中位于所述第一钝化层上的所述像素电极通过所述接触孔连接到所述薄膜晶体管的所述一部分，位于所述像素电极上并且位于所述薄膜晶体管上方的第二钝化层；以及位于所述第二钝化层上并且具有位于各像素区域内的条状的多个开口的公共电极，各所述开口具有沿所述数据线的长轴和沿所述选通线的短轴，其中各开口的中部与所述像素电极交叠，并且各开口的沿长轴的两个端部与所述选通线交叠，其中所述公共电极进一步包括对应于所述薄膜晶体管的另一开口。

[0028] 在本发明另一方面中，一种边缘场切换模式的液晶显示装置包括：彼此面对的第一基板和第二基板；位于所述第一基板上的多条选通线；位于所述多条选通线上的栅绝缘层；多条数据线，所述多条数据线位于所述栅绝缘层上，并且与所述多条选通线交叉以限定多个像素区域；电连接到所述选通线和所述数据线并且位于各像素区域内的薄膜晶体管；板状并且位于各像素区域内的像素电极，所述像素电极连接到所述薄膜晶体管的一部分；第一钝化层，所述第一钝化层位于所述栅绝缘层与所述像素电极之间，并且所述第一钝化层具有露出所述薄膜晶体管的所述一部分的接触孔，其中位于所述第一钝化层上的所述像素电极通过所述接触孔连接到所述薄膜晶体管的所述一部分，位于所述像素电极上并且位

于所述薄膜晶体管上方的第二钝化层；位于所述第二钝化层上并且具有位于各像素区域内的条状的多个开口的公共电极，各所述开口具有沿所述数据线的长轴和沿所述选通线的短轴，其中各开口的中部与所述像素电极交叠，并且各开口的沿长轴的两个端部突出到所述像素电极之外；位于所述第二基板上并且围绕各像素区域的黑底；位于所述第二基板上并且对应于各像素区域的滤色层；以及位于所述第一基板与所述第二基板之间的液晶层，其中所述多个开口中最外端的开口的沿短轴的端部突出到所述像素电极之外。

[0029] 在本发明另一方面中，一种边缘场切换模式的液晶显示装置包括：彼此面对的第一基板和第二基板；位于所述第一基板上的多条选通线；位于所述多条选通线上的栅绝缘层；多条数据线，所述多条数据线位于所述栅绝缘层上，并且与所述多条选通线交叉以限定多个像素区域；电连接到所述选通线和所述数据线并且位于各像素区域内的薄膜晶体管；板状并且位于各像素区域内的像素电极，所述像素电极连接到所述薄膜晶体管的一部分；第一钝化层，所述第一钝化层位于所述栅绝缘层与所述像素电极之间，并且所述第一钝化层具有露出所述薄膜晶体管的所述一部分的接触孔，其中位于所述第一钝化层上的所述像素电极通过所述接触孔连接到所述薄膜晶体管的所述一部分，位于所述像素电极上并且位于所述薄膜晶体管上方的第二钝化层；位于所述第二钝化层上并且具有位于各像素区域内的条状的多个开口的公共电极，各所述开口具有沿所述数据线的长轴和沿所述选通线的短轴，其中各开口的中部与所述像素电极交叠，并且所述多个开口中最外端的开口的沿短轴的端部突出到所述像素电极之外；位于所述第二基板上并且围绕各像素区域的黑底；位于所述第二基板上并且对应于各像素区域的滤色层；以及位于所述第一基板与所述第二基板之间的液晶层，其中所述公共电极进一步包括对应于所述薄膜晶体管的另一开口。

[0030] 在本发明另一方面中，一种边缘场切换模式的液晶显示装置包括：彼此面对的第一基板和第二基板；位于所述第一基板上的多条选通线；位于所述多条选通线上的栅绝缘层；多条数据线，所述多条数据线位于所述栅绝缘层上，并且与所述多条选通线交叉以限定多个像素区域；电连接到所述选通线和所述数据线并且位于各像素区域内的薄膜晶体管；板状并且位于各像素区域内的像素电极，所述像素电极连接到所述薄膜晶体管的一部分并且与所述选通线的一部分交叠；位于所述像素电极上并且位于所述薄膜晶体管上方的钝化层；位于所述钝化层上并且具有位于各像素区域内的条状的多个开口的公共电极，各所述开口具有沿所述数据线的长轴和沿所述选通线的短轴，其中各开口的中部与所述像素电极交叠，并且各开口的沿长轴的两个端部与所述选通线交叠；位于所述第二基板上并且遮蔽所述数据线和所述薄膜晶体管但不遮蔽所述选通线的黑底；位于所述第二基板上并且对应于各像素区域的滤色层；以及位于所述第一基板与所述第二基板之间的液晶层。

[0031] 在本发明另一方面中，一种边缘场切换模式的液晶显示装置包括：彼此面对的第一基板和第二基板；位于所述第一基板上的多条选通线；位于所述多条选通线上的栅绝缘层；多条数据线，所述多条数据线位于所述栅绝缘层上，并且与所述多条选通线交叉以限定多个像素区域；电连接到所述选通线和所述数据线并且位于各像素区域内的薄膜晶体管；板状并且位于各像素区域内的像素电极，所述像素电极连接到所述薄膜晶体管的一部分并且与所述选通线的一部分交叠；位于所述像素电极上并且位于所述薄膜晶体管上方的钝化层；位于所述钝化层上并且具有位于各像素区域内的条状的多个开口的公共电极，各所述开口沿各数据线穿过所述像素区域；位于所述第二基板上并且遮蔽所述数据线和所述薄膜

晶体管而不遮蔽所述选通线的黑底；位于所述第二基板上并且对应于各像素区域的滤色层；以及位于所述第一基板与所述第二基板之间的液晶层。

[0032] 应当理解：以上概述性描述及接下来的详细描述都是示例性和解释性的，并用于以所要求保护的发明作进一步解释。

## 附图说明

[0033] 附图被包括进来以提供对本发明的进一步理解，并且被并入并构成本申请的一部分，附图例示了本发明的实施方式，并与说明书一起用于解释本发明的原理。

[0034] 在附图中：

[0035] 图 1 为相关技术 FFS 模式的 LCD 装置的截面图；

[0036] 图 2A 和图 2B 为示出相关技术 FFS 模式的 LCD 装置的开 / 关状态的截面图；

[0037] 图 3 为用于相关技术 FFS 模式的 LCD 装置的阵列基板的平面图；

[0038] 图 4 示出了相关技术 FFS 模式的 LCD 装置的阵列基板的像素区域；

[0039] 图 5 为相关技术 FFS 模式的 LCD 装置的平面图；

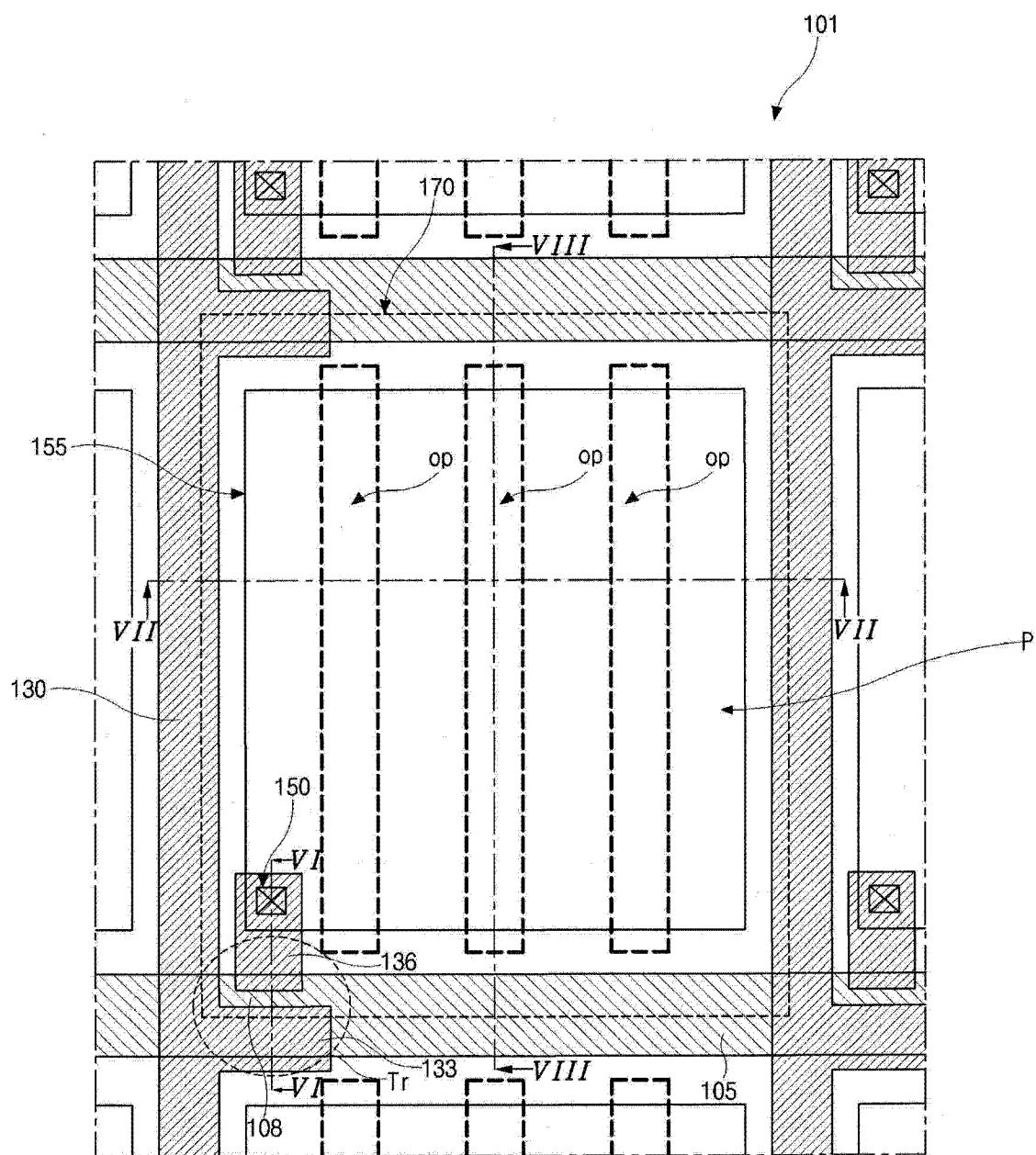

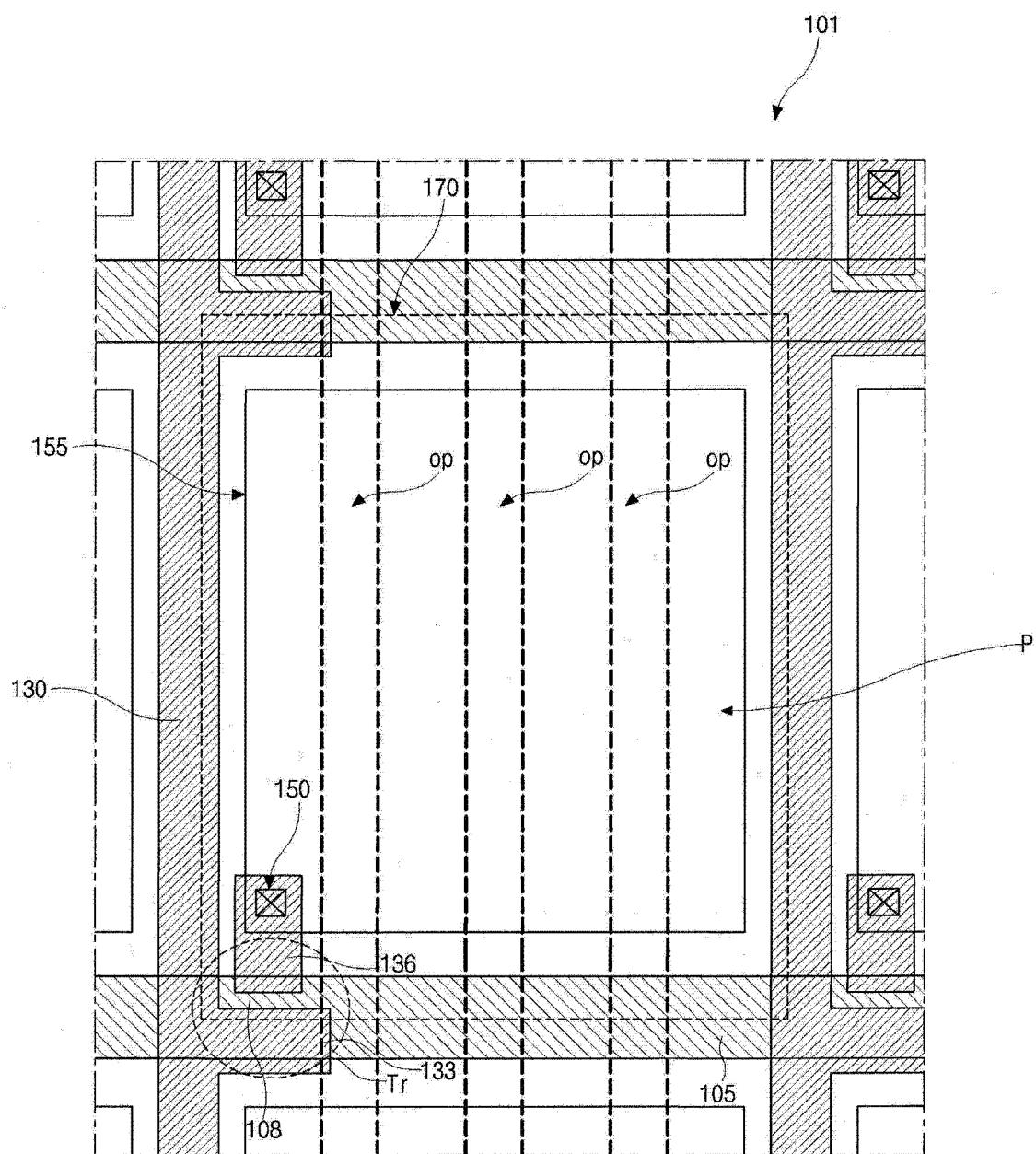

[0040] 图 6 为根据本发明第一实施方式的用于 FFS 模式的 LCD 装置的阵列基板的平面图；

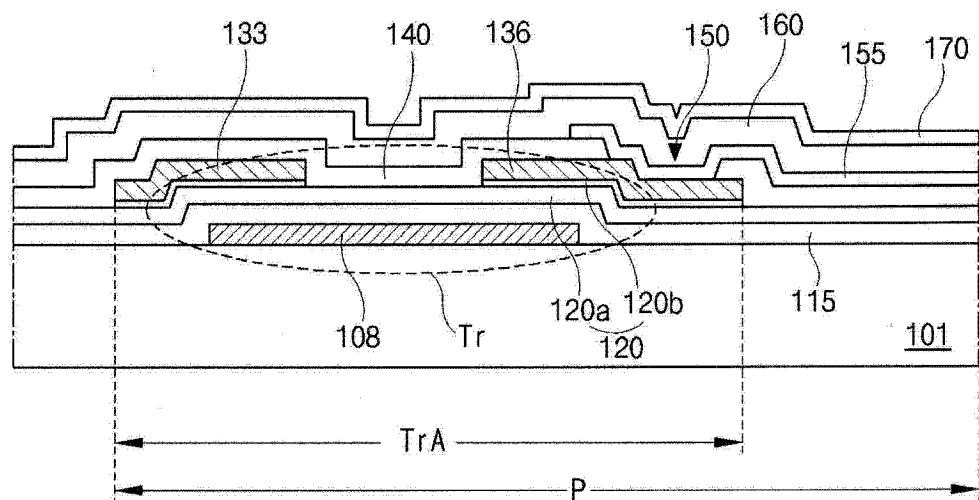

[0041] 图 7 为沿图 6 中的线 VI-VI 提取的截面图；

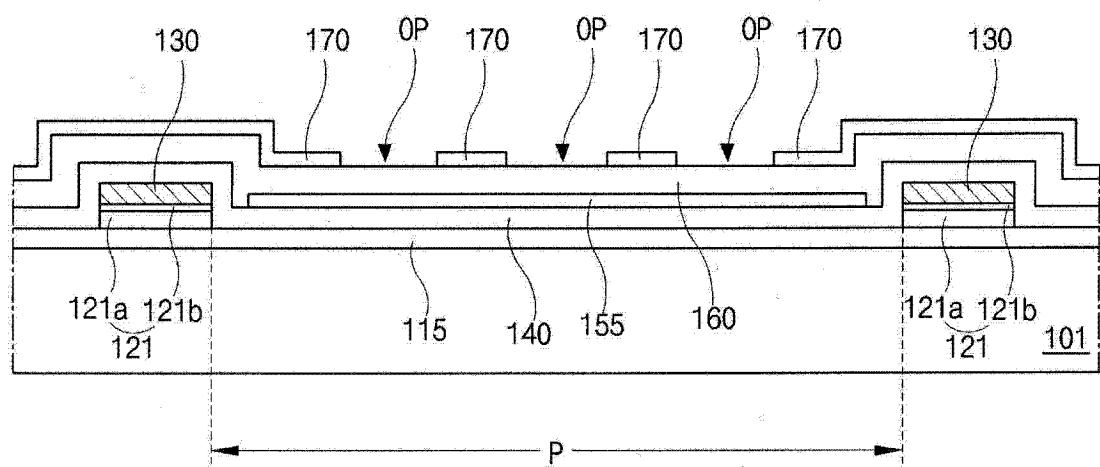

[0042] 图 8 为沿图 6 中的线 VII-VII 提取的截面图；

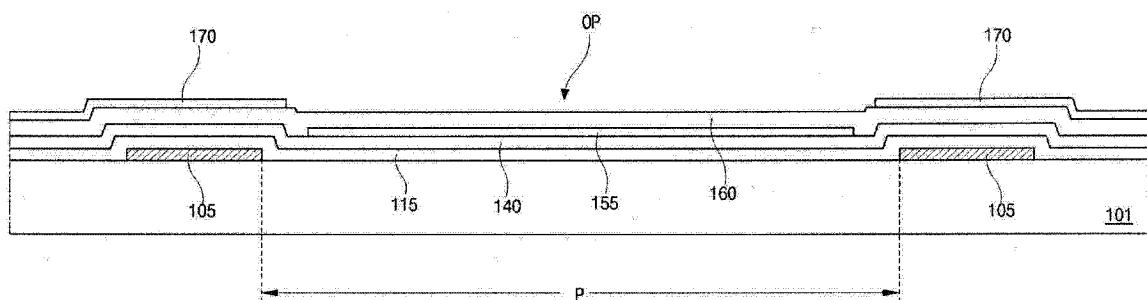

[0043] 图 9 为沿图 6 中的线 VIII-VIII 提取的截面图；

[0044] 图 10 为根据本发明第一实施方式的改进实施方式的用于 FFS 模式的 LCD 装置的阵列基板的平面图；

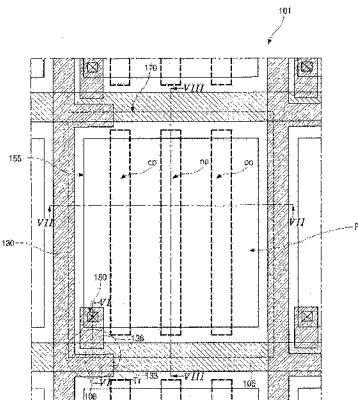

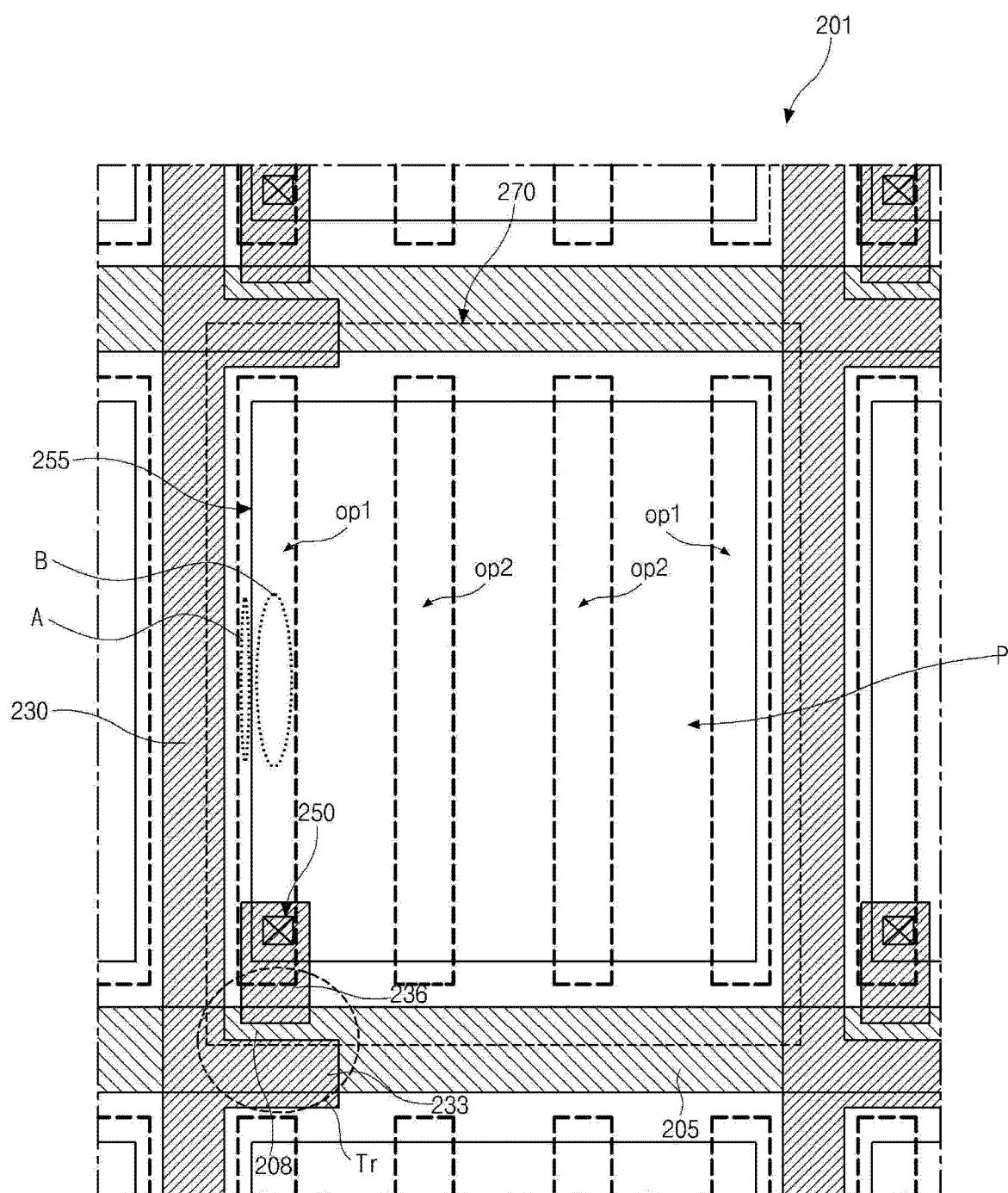

[0045] 图 11 为根据本发明第二实施方式的用于 FFS 模式的 LCD 装置的阵列基板的平面图；

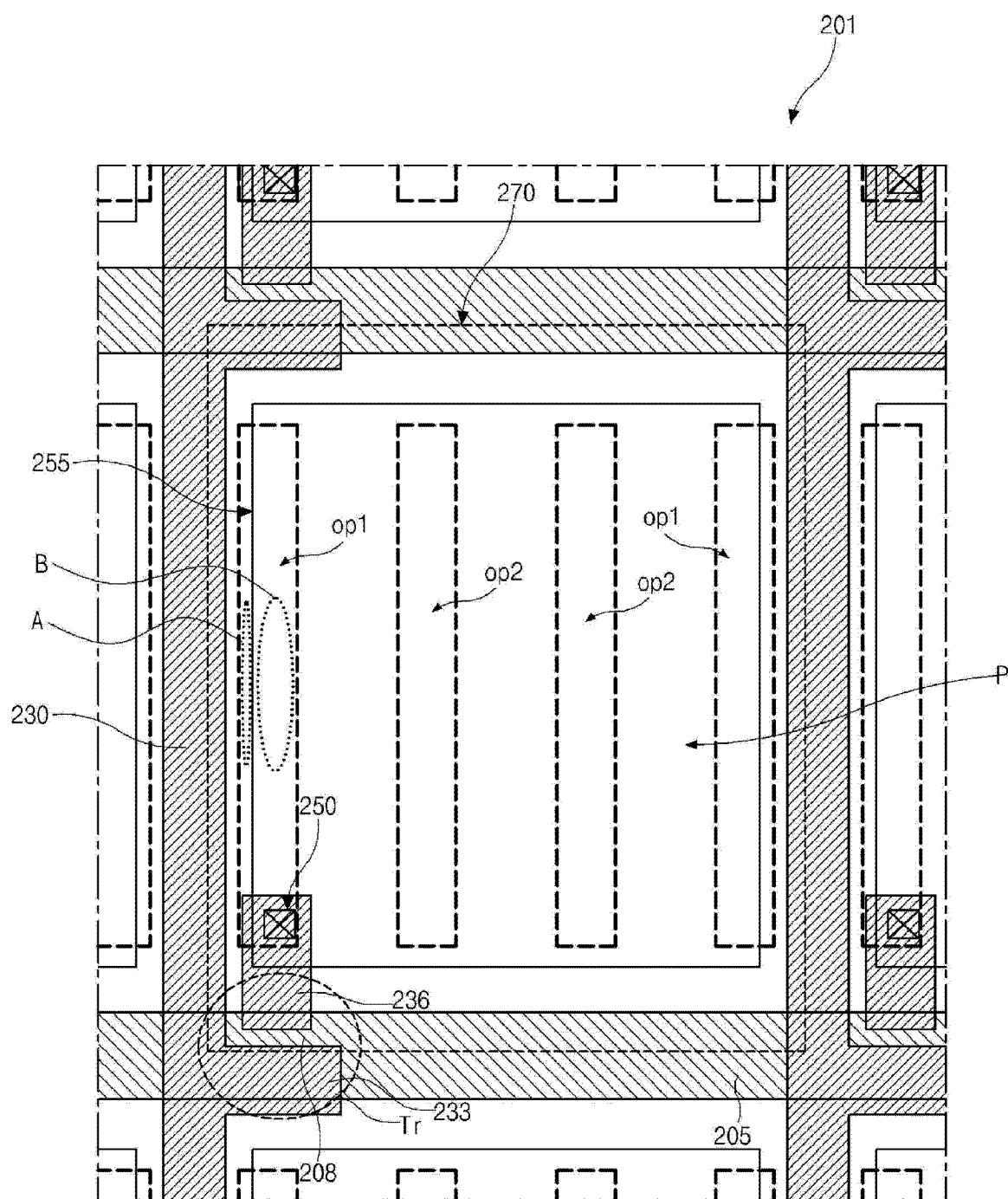

[0046] 图 12 为根据本发明第二实施方式的改进实施方式的用于 FFS 模式的 LCD 装置的阵列基板的平面图；

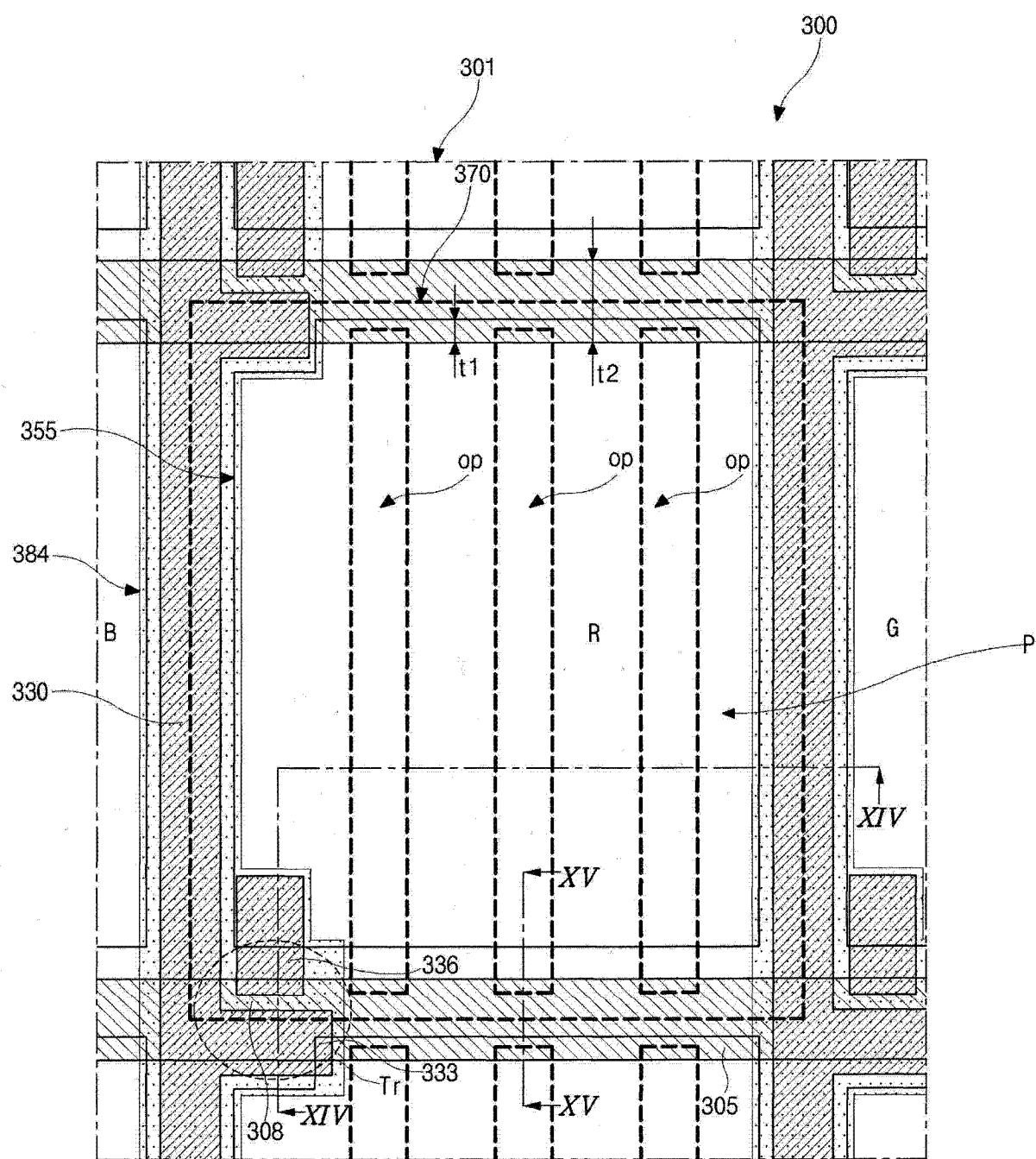

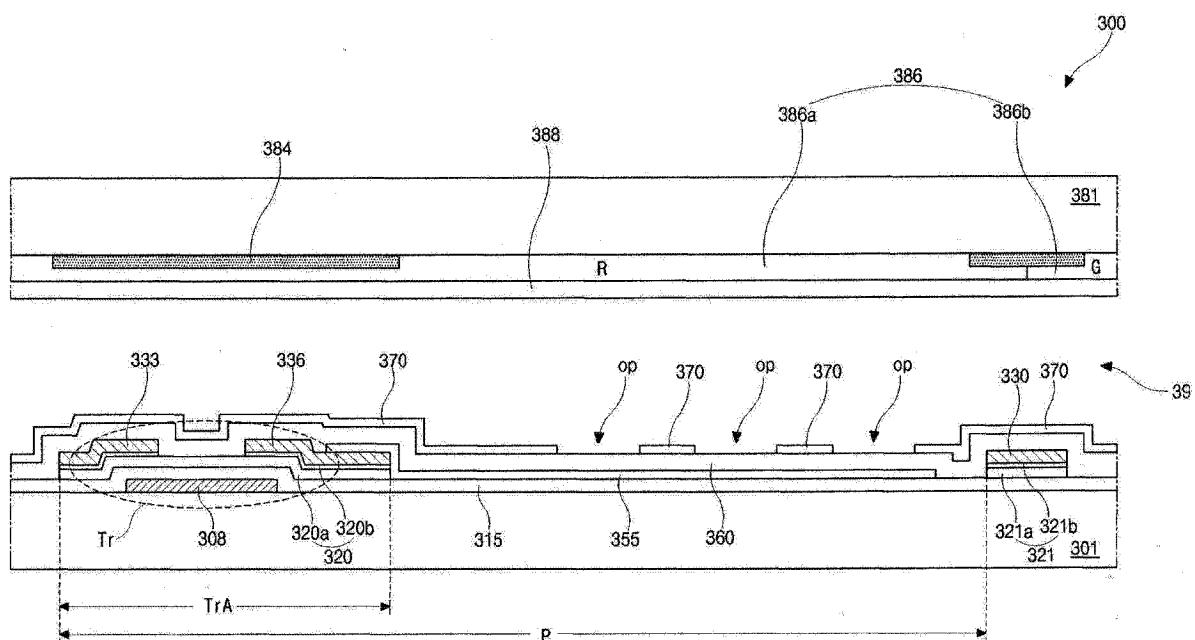

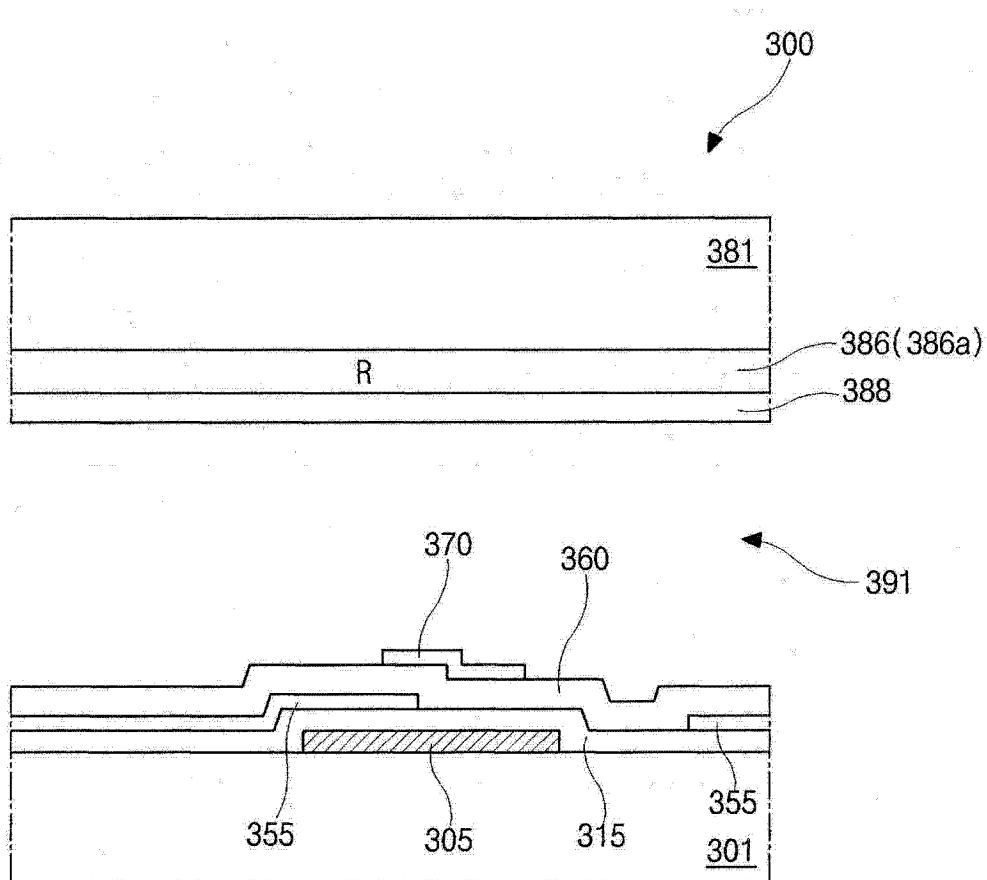

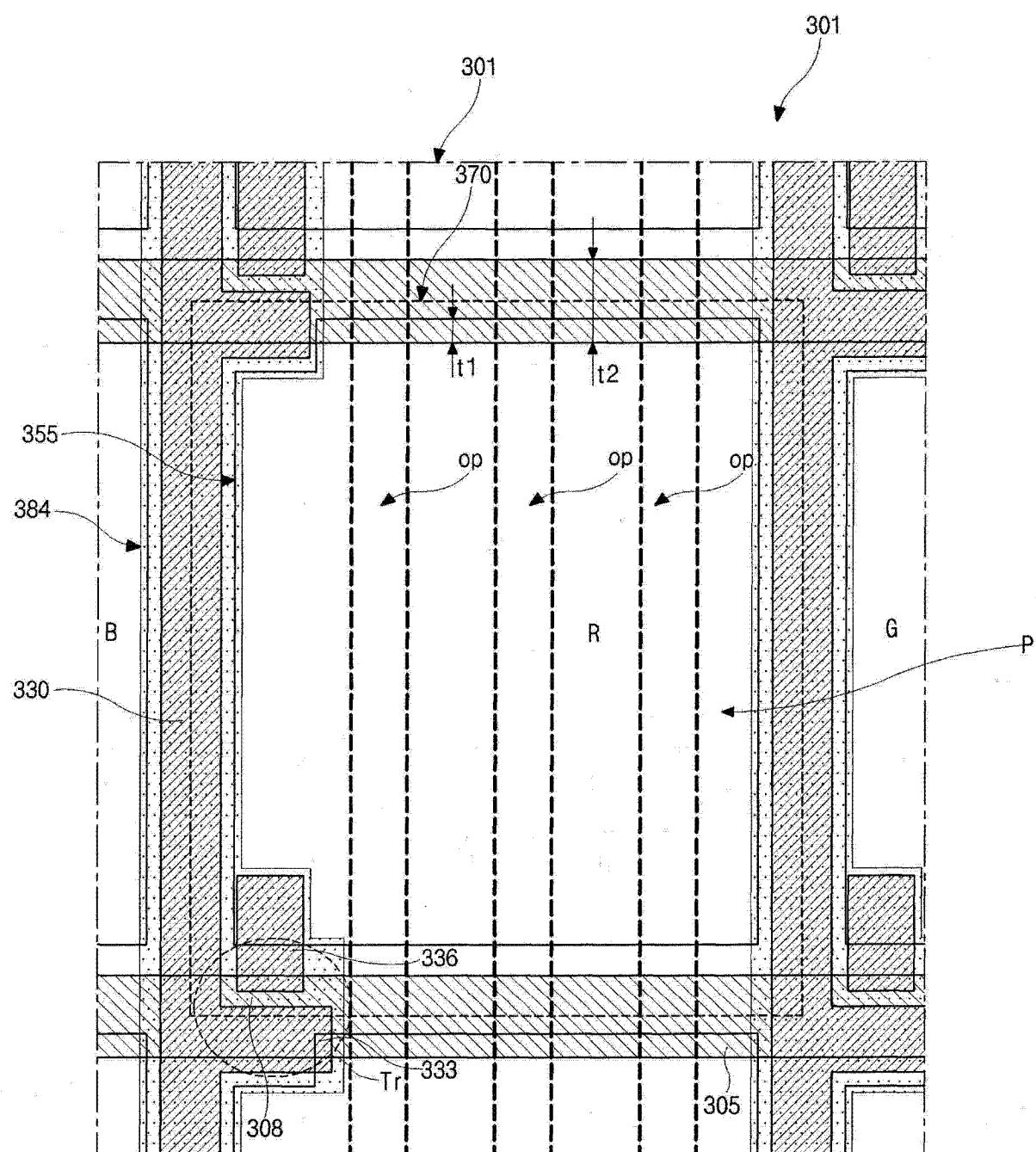

[0047] 图 13 为根据本发明第三个实施方式的 FFS 模式的 LCD 装置的平面图；

[0048] 图 14 为沿着图 13 中的线 XIV-XIV 提取的截面图；

[0049] 图 15 为沿着图 13 中的线 XV-XV 提取的截面图；以及

[0050] 图 16 为根据本发明第三实施方式的改进实施方式的 FFS 模式的 LCD 装置的平面图。

## 具体实施方式

[0051] 现在详细地描述本发明的优选实施方式，附图示出了其实例。

[0052] 图 6 为根据本发明第一实施方式的用于 FFS 模式的 LCD 装置的阵列基板的平面图，而图 7 为沿着图 6 中的线 VI-VI 提取的截面图。图 8 为沿着图 6 中的线 VII-VII 提取的截面图，而图 9 为沿着图 6 中的线 VIII-VIII 提取的截面图。在阵列基板上限定了形成有多个像素区域的显示区域、形成有焊盘区域的非显示区域和形成有作为开关元件的 TFT 的开关区域。非显示区域设置在显示区域的外围，而开关区域则设置在像素区域内。

[0053] 在图 6 中，选通线 105 沿着第一方向形成于基板 101 上。数据线 130 沿着第二方

向与选通线 105 交叉,从而限定像素区域“P”。

[0054] 在像素区域“P”内,形成有连接到选通线 105 和数据线 130 的 TFT“Tr”。TFT“Tr”包括栅极 108、栅绝缘层(未示出)、包括本征非晶硅的有源层(未示出)和掺杂非晶硅的欧姆接触层(未示出)的半导体层(未示出)、源极 133 和漏极 136。源极 133 与漏极 136 隔开。在图 6 中,为了提高孔径比,栅极 108 为选通线 105 的一部分,从而使 TFT“Tr”形成在选通线 105 上。然而,栅极 108 可以从选通线 105 突出并且进入到像素区域“P”内。

[0055] 板状的像素电极 155 设置在像素区域“P”内。像素电极 155 通过漏接触孔 150 连接到 TFT“Tr”的漏极 136。此外,具有多个开口“op”的公共电极 170 形成于显示区域的整个表面上。各开口“op”具有条状。用虚线标示出对应于一个像素区域“P”的公共电极 170。

[0056] 开口“op”位于像素区域“P”内,以与像素电极 155 交叠。各开口“op”具有沿数据线 130 的长轴和沿选通线 105 的短轴。开口“op”的中部与像素电极 155 交叠,而开口“op”的沿长轴的两个端部则突出到像素电极 155 之外。也就是说,开口“op”的沿长轴的两个端部被示出为位于像素电极 155 的外部,而开口“op”的其它部分被示为位于像素电极 155 的内部。公共电极 170 的各开口“op”具有大于像素电极 155 的主长度(major length),从而使开口“op”的沿长轴的两个端部与像素电极 155 不交叠。对于上述结构来说,开口“op”应该形成于公共电极上,而不是形成于像素电极上。在图 6 中,公共电极 170 覆盖了 TFT“Tr”。然而,公共电极 170 上对应于 TFT“Tr”的部分可以去掉,从而露出第二钝化层 160 的一部分。

[0057] 在开口“op”的沿长轴的两个端部中,在开口“op”的短边表面没有产生电场或者具有非常弱的电场。位于开口“op”的沿长轴的两个端部的液晶分子是由在开口“op”的长边表面产生的电场驱动的,从而具有均匀的排列。结果,在相关技术 FFS 模式的 LCD 装置中所示出的向错区域“DA”可能不会在根据本发明的 FFS 模式的 LCD 装置中产生。或者,即使在 FFS 模式的 LCD 装置中存在向错区域,因为向错区域与选通线 105 交叠,所以也不会降低孔径比。因此,FFS 模式的 LCD 装置具有提高的孔径比和透光率。

[0058] 参照图 10,该图示出了根据本发明第一实施方式的改进实施方式的用于 FFS 模式的 LCD 装置的阵列基板的平面图,在像素区域内沿着数据线 130 彼此相邻的开口“op”彼此连接在一起。也就是说,在沿着数据线 130 彼此相邻的像素区域内的开口“op”穿过选通线 105。开口“op”形成为以单条形状的方式贯穿沿单条数据线 130 的像素区域“P”。根据第一实施方式的改进实施方式的 FFS 模式的 LCD 装置也具有提高的孔径比和透光率。

[0059] 因为在除显示区域边缘的像素区域“P”之外的像素区域“P”中的开口“op”没有端部,因此不存在由开口“op”的短边表面产生的电场。因此,像素区域“P”所有表面上的液晶分子都具有均匀的排列。此外,在最外端像素区域(未示出)内开口“op”的沿长轴的端部突出到像素电极之外,从而可以防止产生向错区域或使产生的向错区域减至最小。

[0060] 参照图 7 到图 9,解释根据本发明第一实施方式的用于 FFS 模式的 LCD 装置的阵列基板的截面结构。与根据第一实施方式的用于 FFS 模式的 LCD 装置的阵列基板相比,用于 FFS 模式的 LCD 装置的阵列基板在沿着线 VIII-VIII 提取的截面结构上具有不同之处。

[0061] 在图 7 到图 9 中,根据本发明第一实施方式的用于 FFS 模式的 LCD 装置的阵列基板包括位于基板 101 上的选通线 105 和栅极 108。基板 101 可以为透明的。选通线 105 和

栅极 108 中的每个是由具有较低电阻特性的金属材料形成的。比如,该金属材料可以包括铝 (Al)、铝合金 (AlNd)、铜 (Cu)、铜合金、铬 (Cr) 和钼 (Mo) 其中之一。栅极 108 连接到选通线 105,并且设置在开关区域 “TrA” 内。

[0062] 虽然在图 7 和图 9 中选通线 105 和栅极 108 中的每个具有单层结构,但是选通线 105 和栅极 108 中的每个可具有双层结构。在这种情况下,双层结构的下层可以由具有低电阻特性的金属材料形成,比如铝、铝合金、铜和铜合金,而双层结构的上层可以由钼形成。

[0063] 在选通线 105 和栅极 108 上形成有由诸如氧化硅 ( $\text{SiO}_2$ ) 和氮化硅 ( $\text{SiN}_x$ ) 的无机绝缘材料的栅绝缘层 115。包括本征非晶硅的有源层 120a 和掺杂非晶硅的欧姆接触层 120b 的半导体层 120 形成于栅绝缘层 115 上且在开关区域 “TrA” 内。彼此分开的源极 133 和漏极 136 形成于半导体层 120 上。欧姆接触层 120b 的一部分被蚀刻掉,从而使有源层 120a 的一部分露在源极 133 与漏极 136 之间。

[0064] 此外,与选通线 105 交叉以限定像素区域 “P”的数据线 130 形成于栅绝缘层 115 上。TFT “Tr”的源极 133 连接到数据线 130。

[0065] 包括第一图案 121a 和第二图案 121b 的半导体图案 121 设置在数据线 130 与栅绝缘层 115 之间。半导体图案 121 是由与半导体层 120 相同的材料形成的。是否形成半导体图案 121 是根据制造方法确定的。

[0066] 也就是说,当通过单掩模工序形成半导体层 120、数据线 130、源极 133 和漏极 136 时,数据线 130 的下方存在半导体图案 121,如图 8 所示。然而,如果半导体层 120 是通过与用于数据线 130、源极 133 和漏极 136 的掩模工艺不同的掩模工艺形成的,则数据线 130 的下方不存在半导体图案 121。

[0067] 覆盖数据线 130 和 TFT “Tr”的第一钝化层 140 是由无机绝缘材料和有机绝缘材料中的其中一种材料形成的。无机绝缘材料包括氧化硅 ( $\text{SiO}_2$ ) 和氮化硅 ( $\text{SiN}_x$ ) 中的其中一种材料,而有机绝缘材料包括苯并环丁烯和感光压克力 (photoacryl) 中的其中一种材料。在图 7 到图 9 中,因为第一钝化层 140 是由无机绝缘材料形成的,因此第一钝化层 140 具有台阶差 (step difference)。然而当第一钝化层 140 是由有机绝缘材料形成的时候,第一钝化层 140 具有平坦的顶表面。第一钝化层 140 具有露出 TFT “Tr”的漏极 136 的一部分的漏接触孔 150。

[0068] 板状的像素电极 155 形成于各像素区域 “P” 内,并且形成于具有漏接触孔 150 的第一钝化层 140 上。像素电极 155 通过漏接触孔 150 与漏极 136 接触,并且像素电极 155 是由诸如铟锡氧化物 (ITO) 和铟锌氧化物 (IZO) 的透明导电材料形成的。

[0069] 另一方面,像素电极 155 可以直接接触 TFT “Tr”的漏极 136,并且直接设置在栅绝缘层 115 上。在这种情况下,可以省略掉具有漏接触孔 150 的第一钝化层 140。

[0070] 第二钝化层 160 形成于像素电极 155 上。第二钝化层 160 由无机绝缘材料和有机绝缘材料中的其中一种材料形成的。透明导电材料的公共电极 170 形成于第二钝化层 160 上并且在基板 101 的显示区域的整个表面上。公共电极 170 为板状并且在各像素区域 “P” 内具有彼此分开的多个开口 “op”。各开口 “op” 具有条状,并且具有沿数据线 130 的长轴。开口 “op”的主长度大于像素电极 155 的长度。因此,开口 “op”的中部与像素电极 155 交叠,而开口 “op” 沿长轴的两个端部则突出到像素电极 155 之外。换句话说,开口 “op” 沿长轴的各端部比像素电极 155 更加靠近选通线 105。

[0071] 在根据第一实施方式的改进实施方式的用于 FFS 模式的 LCD 装置的阵列基板内，开口“op”延伸以沿数据线 130 穿过相邻的像素区域“P”。也就是说，开口“op”在整个显示区域具有单条形状。因此在图 8 中没有示出公共电极。在这种情况下，因为在最外端像素区域（未示出）内存在开口沿长轴的端部，因此在最外端像素区域（未示出）内开口沿长轴的端部突出到像素电极之外。

[0072] 在各像素区域“P”内有三个开口“op”。此外，开口“op”之间彼此分开相同的距离。然而，为了获得高效的边缘场，公共电极 170 可具有 2 ~ 10 个开口“op”。

[0073] 在位于显示区域外围的非显示区域内具有栅焊盘区域（未示出）和数据焊盘区域（未示出）。在栅焊盘区域内设置有连接到选通线 105 的栅焊盘电极（未示出）。在数据焊盘区域内设置有连接到数据线 130 的数据焊盘电极（未示出）。此外，非显示区域内形成有连接到公共电极 170 以将公共电压施加至公共电极 170 的公共焊盘电极（未示出）。

[0074] 将栅焊盘电极上的栅绝缘层 115 和第一钝化层 140 及第二钝化层 160 去除，从而形成露出栅焊盘电极的栅焊盘接触孔（未示出）。数据焊盘电极上的第一、第二钝化层 140、160 去除，从而形成露出数据焊盘电极的数据焊盘接触孔（未示出）。

[0075] 此外，通过栅焊盘接触孔与栅焊盘电极接触的栅辅助焊盘电极（未示出）形成于第二钝化层 160 上且在栅焊盘区域内。通过数据焊盘接触孔与数据焊盘电极接触的数据辅助焊盘电极（未示出）形成于第二钝化层 160 上且在数据焊盘区域内。栅辅助焊盘电极和数据辅助焊盘电极中的每个是由与公共电极 170 相同的材料形成的。公共焊盘电极设置在栅焊盘区域和数据焊盘区域中的其中一个区域内。公共焊盘电极从公共电极 170 以直线形状的方式延伸。

[0076] 在根据本发明第二实施方式的用于 FFS 模式的 LCD 装置的阵列基板内，唯一的区别在于公共电极内的开口与像素电极之间的位置关系。因此主要描述区别之处。

[0077] 虽然未示出，但是上述阵列基板与包括黑底和滤色层的滤色基板粘接从而获得 FFS 模式的 LCD 装置。

[0078] 图 11 为根据本发明第二实施方式的用于 FFS 模式的 LCD 装置的阵列基板的平面图。虽然在图 6 中仅公共电极内开口“op”的沿长轴的两个端部示出为位于像素电极的外部，但是在图 11 中不仅公共电极 270 内开口“op”沿长轴的两个端部而且在各像素区域“P”内最外端开口“op1”的沿短轴的端部也示出为位于像素电极 255 的外部。也就是说，沿着各像素区域“P”内最外端开口“op1”的沿短轴的端部突出到像素电极 255 之外。像素区域“P”中部的其他开口“op2”的短轴的端部没有突出到像素电极 255 之外，而是与像素电极 255 交叠。

[0079] 各像素区域“P”内最外端开口“op1”的沿短轴的端部突出到像素电极 255 之外的原因是：在最外端开口“op1”处产生沿像素区域“P”中部的均匀边缘场。结果，在最外端的开口“op1”处没有产生呈边缘场的电场，或者呈边缘场的电场非常弱。此外，由于最外端开口“op1”的短轴突出到像素电极 255 之外，所以在短轴方向的端部，公共电极 270 不与像素电极 255 交叠，从而提高透射率。更具体地，在短轴方向的端部，公共电极 270 和像素电极 255 都没有设置在“A”部分中，并且像素电极 255 设置在“B”部分中，而公共电极 270 没有设置在“B”部分中。结果，在具有均匀边缘场的短轴方向的端部提高了阵列基板的透射率。

[0080] 另一方面，参考图 12，该图为根据本发明第二实施方式的改进实施方式的用于

FFS 模式的 LCD 装置的阵列基板的平面图,各像素区域“P”内开口“op1”和“op2”的沿长轴的两个端部与像素电极 255 交叠,而最外端开口“op1”的沿短轴的端部则定位成设置在像素电极 255 的外部。也就是说,开口“op1”和“op2”各具有小于像素电极的主轴向长度。结果,中部开口“op2”与像素电极 255 完全交叠。然而,最外端开口“op1”的沿短轴的端部突出到像素电极 255 之外。此外,由于最外端开口“op1”的短轴突出到像素电极 255 之外,所以在短轴方向的端部,公共电极 270 不与像素电极 255 交叠,从而提高透射率。更具体地,在短轴方向的端部,公共电极 270 和像素电极 255 都没有设置在“A”部分中,并且像素电极 255 设置在“B”部分中,而公共电极 270 没有设置在“B”部分中。结果,在具有均匀边缘场的短轴方向的端部提高了阵列基板的透射率。

[0081] 与图 10 所示的第一实施方式的改进实施方式类似,在根据第二实施方式的用于 FFS 模式的 LCD 装置的阵列基板和根据第二实施方式的改进实施方式的用于 FFS 模式的 LCD 装置的阵列基板内,开口“op1”和“op2”可以沿各数据线 230 穿过像素区域。

[0082] 虽然未示出,但是上述阵列基板粘接到包括黑底和滤色层的滤色基板,从而得到 FFS 模式的 LCD 装置。

[0083] 下面参照图 6 到图 9 简要地解释根据第一实施方式的用于 FFS 模式的 LCD 装置的阵列基板的制造方法。第二实施方式和第二实施方式的改进实施方式的不同之处在于:公共电极的开口与像素电极之间的位置关系。因此,将重点放在解释第一实施方式的制造过程。在各像素区域“P”内限定了形成有 TFT “Tr”的开关区域“TrA”。

[0084] 首先,将具有低电阻特性的第一金属材料设置在基板 101 上,以形成第一金属层(未示出)。比如,第一金属层包括铝 (Al)、铝合金 (AlNd)、铜 (Cu)、铜合金、铬 (Cr) 和钼 (Mo) 中的其中之一。通过掩模工艺对第一金属层进行构图,从而形成沿第一方向的选通线 105 以及在开关区域“TrA”内的栅极 108。栅极 108 连接到选通线 105。掩模工艺包括将光刻胶 (PR) 层涂覆在第一金属层上的步骤;使用掩模对 PR 层进行曝光的步骤;对曝光后的 PR 层进行显影以形成 PR 图案的步骤;使用 PR 图案作为蚀刻掩模对第一金属层进行蚀刻并且剥离剩余的光阻图案的步骤。同时,在栅焊盘区域(未示出)内形成连接到选通线 105 一个端部的栅焊盘电极(未示出)。

[0085] 虽然示出了具有单层结构的选通线 105 和栅极 108,但是选通线 105 和栅极 108 中的每一个可具有双层结构。比如,双层结构的下层可以由铝合金形成,而双层结构的上层可以由钼形成。

[0086] 接下来通过沉积比如氧化硅 ( $SiO_2$ ) 和氮化硅 ( $SiN_x$ ) 的无机绝缘材料而在选通线 105 和栅极 108 上形成栅绝缘层 115。接下来,在栅绝缘层 115 上顺序层叠本征非晶硅层(未示出)、掺杂非晶硅层(未示出)和第二金属层(未示出)叠压。通过沉积铝 (Al)、铝合金 (AlNd)、铜 (Cu) 和铜合金中的其中之一形成第二金属层。然后,在第二金属层上形成光刻胶层(未示出),并且通过半色调曝光法或者折射曝光法对 PR 层进行曝光,以便形成厚度不同的第一 PR 图案和第二 PR 图案(未示出)。

[0087] 接下来,对通过第一 PR 图案和第二 PR 图案露出的第二金属层以及位于露出的第二金属层下方的掺杂非晶硅层和本征非晶硅层进行顺序蚀刻,以形成沿第二方向的数据线 130。数据线 130 与选通线 105 交叉,以限定像素区域“P”。同时,在栅绝缘层 115 上且开关区域“TrA”层叠有有源层 120a、欧姆接触图案(未示出)和源-漏图案(未示出)。此

外,数据焊盘区域(未示出)内形成有连接到数据线130一个端部的数据焊盘电极(未示出)。

[0088] 接下来,执行灰化工艺,以将厚度小于第一PR图案的第二PR图案去除。通过去除第二PR图案露出源-漏图案的中部。对源-漏图案的中部和位于源-漏图案中部下方的欧姆接触图案进行蚀刻,以便形成源极133和漏极136,以及位于源极133和漏极136下方的欧姆接触层120b。有源层120a的一部分露出来。栅极108、栅绝缘层115、包括有源层120a和欧姆接触层120b的半导体层120、源极133和漏极136构成了开关区域“TrA”内的TFT“Tr”。因为半导体层120与源极133和漏极136是通过单一掩模工艺形成的,因此在数据线130的下方具有包括第一图案121a和第二图案121b的半导体图案121,第一图案121a和第二图案121b分别由与有源层120a和欧姆接触层120b相同的材料形成,而数据线130由与源极133和漏极136相同的材料形成,并且与源极133和漏极136位于相同的层上。

[0089] 另一方面,可以通过与源极133和漏极136的掩模工艺不同的掩模工艺形成半导体层120。也就是说,可以通过两个掩模工艺形成半导体层120和源极133与漏极136。在这种情况下,通过一个掩模工艺对层叠在栅绝缘层上的本征非晶硅层和掺杂非晶硅层进行蚀刻,以便形成有源层120a和欧姆接触图案。然后,在欧姆接触图案上形成第二金属层。接下来,通过另一个掩模工艺对第二金属层上进行构图,以便形成数据线130、源极133和漏极136,并且去除欧姆接触图案中在源极133与漏极136之间露出的部分,以便露出有源层120a的一部分并且形成欧姆接触层120b。在这种情况下,数据线130的下方不存在半导体图案。

[0090] 接下来,在TFT“Tr”和数据线130上沉积比如氧化硅( $SiO_2$ )和氮化硅( $SiN_x$ )的无机绝缘材料,或者在TFT“Tr”和数据线130上涂覆比如苯并环丁烯(BCB)和感光压克力(photoacryl)的有机绝缘材料,以便形成第一钝化层140。然后,对第一钝化层140进行构图,从而形成露出部分漏极136的漏接触孔150。如上所述,可以省略掉第一钝化层140。

[0091] 接下来,在包括漏接触孔150的第一钝化层140上沉积比如ITO和IZO的透明导电材料,从而形成第一透明导电材料层。通过掩模工艺对第一透明导电材料层进行构图,以便形成像素电极155,该像素电极155为板状并且通过漏接触孔150连接到漏极136。如果省略掉第一钝化层140,则像素电极155直接设置在栅绝缘层115上,并且与漏极136直接接触。

[0092] 接下来,在像素电极155上沉积比如氧化硅( $SiO_2$ )和氮化硅( $SiN_x$ )的无机绝缘材料,或者在像素电极155上涂覆比如苯并环丁烯(BCB)和感光压克力(photoacryl),以便形成第二钝化层160。

[0093] 去除栅焊盘区域内的第二钝化层160、第一钝化层140和栅绝缘层115,从而形成露出栅焊盘电极的栅焊盘接触孔(未示出)。此外,去除数据焊盘区域内的第二钝化层160和第一钝化层140,以便形成露出数据焊盘电极的数据焊盘接触孔(未示出)。

[0094] 接下来在包括栅焊盘接触孔和数据焊盘接触孔的第二钝化层160上沉积比如ITO和IZO的透明导电材料,以便形成第二透明导电材料层。通过掩模工艺对第二透明导电材料层进行构图,以便在显示区域的整个表面内形成公共电极170。公共电极170为板状。同时,在栅焊盘区域内形成通过栅焊盘接触孔与栅焊盘电极接触的栅辅助焊盘电极(未示

出),并且在数据焊盘区域内形成通过数据焊盘接触孔与数据焊盘电极接触的数据辅助焊盘电极(未示出)。公共电极170具有如图5、9、10和11所示的开口。

[0095] 图13为根据本发明第三实施方式的FFS模式的LCD装置的平面图,图14为沿着图13中的线XIV-XIV提取的截面图,而图15为沿着图13中的线XV-XV提取的截面图。为方便解释,将具有多个像素区域的区域定义为显示区域。

[0096] 在图13中,FFS模式的LCD装置300包括第一基板301、面对第一基板301的第二基板(未示出)和设置在第一基板与第二基板之间的液晶层(未示出)。

[0097] 在第一基板301上,选通线305沿第一方向形成。沿第二方向的数据线330与选通线305交叉,从而限定像素区域“P”。

[0098] 在像素区域“P”内,形成有连接到选通线305和数据线330的TFT“Tr”。TFT“Tr”包括栅极308、栅绝缘层(未示出)、包括本征非晶硅的有源层(未示出)和掺杂非晶硅的欧姆接触层(未示出)的半导体层(未示出)、源极333和漏极336。源极333与漏极336分开。在图13中,为了提高孔径比,栅极308为选通线305的一部分,从而TFT“Tr”形成于选通线305上。然而,栅极305可以从选通线305突出到并且进入像素区域“P”。

[0099] 板状的像素电极355设置在像素区域“P”内。像素电极355连接到TFT“Tr”的漏极336。像素电极355与前一选通线305的一部分交叠。当选通线305具有第二宽度“t2”时,像素电极355与前一选通线305之间交叠的部分具有第一宽度“t1”,该第一宽度“t1”的范围小于第二宽度“t2”的大约50%。也就是说,第一宽度“t1”等于或者小于第二宽度“t2”的一半。选通线305的第二宽度“t2”可以为大约8微米至大约12微米,而像素电极355与前一选通线305之间的交叠部分的第一宽度“t1”可以为大约4微米至大约6微米。第一宽度“t1”等于或者小于第二宽度“t2”的一半的原因是:能够防止由相邻像素电极305间的耦合问题引起的电场失真。在相关技术FFS模式的LCD装置中,像素电极设置在像素区域的内部,以便防止由相邻像素电极间的耦合问题引起的电场失真。然而通过仿真可以知道:很少产生由交叠的像素电极355与交叠的前一选通线305之间的寄生电容或者由相邻像素电极355间的耦合问题引起的电场失真。考虑到仿真结果,在根据本发明的FFS模式的LCD装置中,像素电极355与选通线305之间的交叠部分的第一宽度“t1”等于或者小于选通线305的第二宽度“t2”的一半。

[0100] 此外,在第一基板301的整个表面上形成了具有多个位于各像素区域内的开口“op”的公共电极370。开口“op”与像素电极355交叠,并且具有条状。通过虚线标示对应于一个像素区域“P”的公共电极370。

[0101] 开口“op”具有沿数据线330的长轴和沿选通线305的短轴。开口“op”的沿长轴的两个端部与选通线305的一部分交叠。各开口“op”具有相对较大的主轴向长度,从而使FFS模式的LCD装置具有提高的透光率。

[0102] 因为开口“op”的沿长轴的两个端部与选通线305的一部分交叠,因此光线无法通过两个端部。因此,即使在开口“op”的沿长轴的端部产生了向错区域,由于选通线305遮蔽向错区域,因此也不会降低显示质量。

[0103] 另一方面,参照图16,该图为根据本发明第三实施方式的改进实施方式的FFS模式LCD装置的平面图,各开口“op”沿数据线330穿过像素区域“P”。也就是说,公共电极370内的各开口“op”在沿数据线330的整个显示区域上具有单条形状。

[0104] 在图 16 中的 FFS 模式的 LCD 装置中, 在显示区域的最外端像素区域(未示出)内, 开口“op”沿长轴仅具有一个端部。因此, 在中部像素区域“P”(除了最外端像素区域)内, 沿开口“op”长轴不存在由短边产生的电场。中部像素区域“P”内的液晶分子是由沿着开口“op”长轴的长边产生的电场驱动的, 从而液晶分子具有所需要的均匀排列。

[0105] 结果, 因为没有产生向错区域, 因此 FFS 模式的 LCD 装置的透光率和孔径比得到提高。即使产生了向错区域, 与向错区域交叠的选通线 305 也遮蔽向错区域, 从而使 FFS 模式的 LCD 装置的透光率和孔径比得到提高。

[0106] 再次参照图 13, 虽然包括条状开口“op”的公共电极 370 覆盖了整个显示区域, 但是公共电极 370 也可以具有对应于 TFT “Tr”的其它开口(未示出), 以便防止当公共电极 370 与 TFT “Tr”交叠时在 TFT “Tr”的栅极 308 与公共电极 370 之间产生寄生电容。寄生电容对 TFT “Tr”的开关操作具有不良影响。

[0107] 上述包括选通线 305、数据线 330、TFT “Tr”、像素电极 355 和公共电极 370 的第一基板 301 可称为阵列基板。

[0108] 在面对第一基板 301 的第二基板(未示出)上形成有滤色层(未示出)、黑底 384 和保护层(未示出)。滤色层包括红色、绿色和蓝色滤色器图案, 并且对应于第一基板 301 的各像素区域“P”。黑底 384 对应于 TFT “Tr”的数据线 330。保护层形成于滤色层上。此外, 液晶层设置在第一基板 301 与第二基板之间。

[0109] 相关技术 FFS 模式的 LCD 装置中的黑底对应于选通线、数据线和 TFT。也就是说, 黑底围绕各像素区域。然而, 因为根据本发明的 FFS 模式的 LCD 装置中的黑底 384 对应于数据线 330 和 TFT “Tr”, 而不对应于选通线 305, 因此进一步提高了 FFS 模式的 LCD 装置的孔径比。

[0110] 在根据本发明的 FFS 模式的 LCD 装置, 像素电极 335 以预定宽度与前一选通线 305 交叠。此外, 如图 13 所示, 在公共电极 370 中开口“op”的沿长轴的端部也与选通线 305 交叠。或者, 如图 16 所示, 单条形状的开口“op”沿数据线 330 穿过像素区域“P”。结果, 在开口“op”的沿长轴的端部没有产生向错区域或者使向错区域减至最小。因此, 即使黑底 384 不遮蔽选通线 305, 也不存在显示质量问题。

[0111] 参照图 14 和图 15 解释根据本发明第三实施方式的 FFS 模式的 LCD 装置的截面结构。因为根据本发明第三实施方式的改进实施方式的 FFS 模式的 LCD 装置的区别仅在于: 公共电极中的开口与选通线之间的位置关系, 因此将重点解释根据第三实施方式的 FFS 模式的 LCD 装置。为方便解释, 形成有 TFT 的区域定义为像素区域中的开关区域。

[0112] 在图 14 和图 15 中, 用于 FFS 模式的 LCD 装置 300 的阵列基板包括第一基板 301。第一基板 301 可以为透明的。选通线 305 和栅极 308 形成于第一基板 301 上。选通线 305 和栅极 308 中的每一个是由具有低电阻特性的金属材料形成的。比如, 该金属材料可以包括铝(A1)、铝合金(A1Nd)、铜(Cu) 和铜合金中的其中之一。栅极 308 连接到选通线 305 并且设置在开关区域“TrA”内。

[0113] 虽然选通线 305 和栅极 308 中的每一个在图 14 和图 15 中具有单层结构, 但是选通线 305 和栅极 308 中的每一个可具有双层结构。在这种情况下, 双层结构的下层可以由比如铝、铝合金、铜和铜合金的具有低电阻特性的金属材料形成, 而双层结构的上层可以由钼形成。

[0114] 在选通线 305 和栅极 308 上形成有由比如氧化硅 ( $\text{SiO}_2$ ) 和氮化硅 ( $\text{SiN}_x$ ) 的无机绝缘材料的栅绝缘层 315。

[0115] 包括本征非晶硅的有源层 320a 和掺杂非晶硅的欧姆接触层 320b 的半导体层 320 形成于栅绝缘层 315 上且在开关区域“TrA”内。彼此分开的源极 333 和漏极 336 形成于半导体层 320 上。欧姆接触层 320b 的一部分被蚀刻掉, 从而使有源层 320a 的一部分露在源极 333 与漏极 336 之间。源极 333 与漏极 336 中的每一个可以由金属材料形成, 该金属材料为比如钼 (Mo)、铬 (Cr)、铝 (Al)、铝合金 (AlNd)、铜 (Cu) 和铜合金。栅极 308、栅绝缘层 315、半导体层 320、源极 333 和漏极 336 构成了在开关区域“TrA”内的 TFT “Tr”。

[0116] 此外, 与选通线 305 交叉以限定像素区域“P”的数据线 330 形成于栅绝缘层 315 上。TFT “Tr”的源极 333 连接到数据线 330。数据线 330、源极 333 和漏极 336 中的每一个可具有双层结构。

[0117] 包括第一图案 321a 和第二图案 321b 的半导体图案 321 设置在数据线 330 与栅绝缘层 315 之间。半导体图案 321 是由与半导体层 320 相同的材料形成的。是否形成半导体图案 321 是由制造方法确定的。

[0118] 也就是说, 如图 14 所示, 当半导体层 320、数据线 330 和源极 333 与漏极 336 是由单个掩模工艺形成时, 在数据线 330 的下方存在半导体图案 321。然而, 如果半导体层 320 是通过与用于数据线 330、源极 333 和漏极 336 的掩模工艺不同的掩模工艺形成的, 则在数据线 330 的下方不存在半导体图案 321。

[0119] 板状的像素电极 355 形成于各像素区域“P”内并且在栅绝缘层 315 上。像素电极 355 是由比如铟锡氧化物 (ITO) 和铟锌氧化物 (IZO) 的透明导电材料形成的。像素电极 355 与漏极 336 直接接触, 并且以预定宽度与前一选通线 305 交叠。像素电极 355 与选通线 305 之间交叠的部分的宽度可以小于选通线 305 宽度的大约 50%。

[0120] 钝化层 160 形成于数据线 330、TFT “Tr”和像素电极 355 上。钝化层 160 由比如氧化硅 ( $\text{SiO}_2$ ) 和氮化硅 ( $\text{SiN}_x$ ) 的无机绝缘材料形成或者由比如苯并环丁烯 (BCB) 和感光压克力 (photoacryl) 的有机绝缘材料形成。在图 14 和图 15 中, 因为钝化层 160 是由无机绝缘材料形成的, 因此钝化层 160 具有台阶差。然而, 当钝化层 160 是由有机绝缘材料形成时, 钝化层 160 具有平坦的顶表面。

[0121] 比如 ITO 和 IZO 的透明导电材料的公共电极 370 形成于钝化层 360 上且在基板 301 的显示区域的整个表面上。公共电极 370 为板状并且具有在各像素区域“P”内彼此分开的多个开口“op”。各开口“op”具有条状并且具有沿数据线 330 的长轴。各像素区域“P”内具有三个开口“op”。此外, 开口“op”彼此分开相同距离。然而, 为了获得有效的边缘场, 公共电极 370 可具有 2 到 10 个开口“op”。

[0122] 在图 14 中, 公共电极 370 覆盖 TFT “Tr”。然而, 可以将公共电极 370 中对应于 TFT “Tr”的部分去除, 从而露出钝化层 360 的一部分。

[0123] 在面对第一基板 301 的第二基板 381 上形成有对应于第一基板 301 上的数据线 330 和 TFT “Tr”的黑底 384。在第二基板 381 上形成有包括红滤色器图案 386a、绿滤色器图案 386b 和蓝滤色器图案 (未示出) 并且对应于第一基板 301 的各像素区域“P”的滤色层 386。在滤色层 386 上形成由透明无机绝缘材料的保护层 388。保护层 388 具有平坦的顶表面。可以省略掉保护层 388。

[0124] 此外,液晶层 391 设置在第一基板 301 与第二基板 381 之间。

[0125] 本领域技术人员应当明白:在不脱离本发明精神或范围的情况下,在本发明中可以做出许多改进和变型。因此,本发明旨在落入所附权利及其等同范围之内的本发明的改进和变型。

图 1

图 2A

图 2B

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

图 12

图 13

图 14

图 15

图 16

|                |                                                            |         |            |

|----------------|------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 边缘场切换模式的液晶显示装置及其阵列基板                                       |         |            |

| 公开(公告)号        | <a href="#">CN104614902A</a>                               | 公开(公告)日 | 2015-05-13 |

| 申请号            | CN201510094507.2                                           | 申请日     | 2008-12-09 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                   |         |            |

| 申请(专利权)人(译)    | 乐金显示有限公司                                                   |         |            |

| 当前申请(专利权)人(译)  | 乐金显示有限公司                                                   |         |            |

| [标]发明人         | 宋相武<br>黄仁镐<br>朴大林<br>柳基贤                                   |         |            |

| 发明人            | 宋相武<br>黄仁镐<br>朴大林<br>柳基贤                                   |         |            |

| IPC分类号         | G02F1/1343 G02F1/1362 G02F1/1368 H01L27/12                 |         |            |

| CPC分类号         | G02F1/133707 G02F2001/134372                               |         |            |

| 优先权            | 1020080082964 2008-08-25 KR<br>1020080060328 2008-06-25 KR |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>             |         |            |

## 摘要(译)

本发明提供了边缘场切换模式的液晶显示装置及其阵列基板。本发明的阵列基板包括：位于基板上的多条选通线；位于多条选通线上的栅绝缘层；多条数据线，该多条数据线位于栅绝缘层上，并且与多条选通线交叠以限定多个像素区域；电连接到选通线和数据线并且位于各像素区域内的薄膜晶体管；板状并且位于各像素区域内的像素电极，像素电极连接到薄膜晶体管的一部分；位于像素电极上并且位于薄膜晶体管上方的第一钝化层；和公共电极，该公共电极位于第一钝化层上并且具有位于各像素区域内的条状的多个开口，各开口具有沿数据线的长轴和沿选通线的短轴，其中各开口的中部与像素电极交叠，并且各开口的沿长轴的两个端部突出到像素电极之外。