[19] 中华人民共和国国家知识产权局

[51] Int. Cl.

[12] 发明专利申请公布说明书

[21] 申请号 200710105864.X

[43] 公开日 2007 年 12 月 26 日

[11] 公开号 CN 101093329A

[22] 申请日 2007.5.31

[21] 申请号 200710105864.X

[30] 优先权

[32] 2006. 6. 21 [33] KR [31] 10 - 2006 - 0055781

[71] 申请人 LG. 菲利浦 LCD 株式会社

地址 韩国首尔

[72] 发明人 徐范植 金志源

[74] 专利代理机构 北京律诚同业知识产权代理有限公司

代理人 徐全国 沈 振

代理人 徐金国 梁 挥

权利要求书 3 页 说明书 12 页 附图 7 页

[54] 发明名称

# 用于共平面开关模式液晶显示器的阵列基板及其制造方法

[57] 摘要

本发明涉及用于共平面开关模式液晶显示器件的阵列基板，包括：在基板上的栅线；与栅线交叉的数据线；设置在数据线之上并连接到数据线上的辅助数据线；连接到栅线和数据线上的薄膜晶体管；设置在像素区中并连接到薄膜晶体管上的多个像素电极；以及多个公共电极，包括邻近数据线的第一公共电极和第二公共电极，以及在第一公共电极和第二公共电极之间的第三公共电极，所述第三公共电极与多个像素电极交替排列。

1、一种用于共平面开关模式液晶显示器件的阵列基板，包括：

在基板上的栅线；

与栅线交叉的数据线；

设置在数据线之上并连接到数据线上的辅助数据线；

连接到栅线和数据线上的薄膜晶体管；

设置在像素区中并连接到薄膜晶体管上的多个像素电极；以及

多个公共电极，包括邻近数据线的第一公共电极和第二公共电极，以及在第一公共电极和第二公共电极之间的第三公共电极，所述第三公共电极与多个像素电极交替排列。

2、根据权利要求 1 所述的阵列基板，其特征在于，第一公共电极和第二公共电极形成在与数据线和辅助数据线不同的层中。

3、根据权利要求 2 所述的阵列基板，其特征在于，所述第一公共电极和第二公共电极是由与栅线相同的材料形成，并与栅线形成在同一层中。

4、根据权利要求 2 所述的阵列基板，其特征在于，所述第三公共电极、多个像素电极和辅助数据线是由相同的材料形成，并形成在同一层中。

5、根据权利要求 4 所述的阵列基板，其特征在于，所述第三公共电极包括氧化铟锡和氧化铟锌中的一种。

6、根据权利要求 1 所述的阵列基板，其特征在于，多个公共电极、多个像素电极以及辅助数据线是由相同的材料形成，并形成在同一层中。

7、根据权利要求 6 所述的阵列基板，其特征在于，多个公共电极包括氧化铟锡和氧化铟锌中的一种。

8、根据权利要求 1 所述的阵列基板，其特征在于，所述辅助数据线具有等于或小于数据线的宽度。

9、根据权利要求 1 所述的阵列基板，其特征在于，多个像素电极和多个公共电极基本平行于数据线。

10、根据权利要求 1 所述的阵列基板，其特征在于，多个像素电极和多个公共电极具有至少一个弯曲部分。

11、根据权利要求 1 所述的阵列基板，其特征在于，进一步包括具有至少

两个数据接触孔并置于数据线和辅助数据线之间的钝化层，其中，两个数据接触孔对应于数据线的两端，辅助数据线通过两个数据接触孔连接到数据线上。

12、根据权利要求 1 所述的阵列基板，其特征在于，进一步包括基本平行于栅线的公共线，其中，多个公共电极连接到公共线上。

13、根据权利要求 12 所述的阵列基板，其特征在于，进一步包括具有暴露第一公共电极和第二公共电极的公共接触孔的钝化层，其中，第一和第二公共电极从公共线延伸出，在钝化层上的第三公共电极通过公共接触孔连接到第一公共电极和第二公共电极上。

14、根据权利要求 12 所述的阵列基板，其特征在于，进一步包括连接到薄膜晶体管上并与公共线交叠的第一电容电极，其中，第一电容电极、公共线的交叠部分以及在所述第一电容电极和所述公共线的交叠部分之间的绝缘层构成存储电容。

15、根据权利要求 1 所述的阵列基板，其特征在于，所述薄膜晶体管包括连接到栅线上的栅极、在栅极上的栅绝缘层、在栅绝缘层上的半导体层、在半导体层上并连接到数据线的源极、以及在半导体层上并与源极间隔开的漏极。

16、一种制造用于共平面开关模式液晶显示器件的阵列基板的方法，包括：

在基板上形成栅线、栅极、公共线、第一公共电极和第二公共电极，栅极连接到栅线上，第一公共电极和第二公共电极连接到公共线上；

在栅线、栅极、公共线、第一公共电极和第二公共电极上形成栅绝缘层；

形成在栅绝缘层上的半导体层、在半导体层上并彼此间隔开的源极和漏极、和连接到源极上并与栅线交叉的数据线；

在源极、漏极和数据线上形成钝化层，钝化层具有暴露数据线的数据接触孔、暴露漏极的漏接触孔、和暴露第一公共电极和第二公共电极的公共接触孔；以及

在钝化层上形成多个像素电极、第三公共电极和辅助数据线，多个像素电极和第三公共电极设置在第一公共电极和第二公共电极之间，并彼此交替排列，多个像素电极通过漏接触孔连接到漏极上，第三公共电极通过公共接触孔连接到第一公共电极和第二公共电极上，辅助数据线通过数据接触孔连接到数据线上。

17、一种制造用于共平面开关模式液晶显示器件的阵列基板的方法，包括：

在基板上形成栅线、连接到栅线上的栅极以及公共线；

在栅线、栅极和公共线上形成栅绝缘层；

形成在栅绝缘层上的半导体层、在半导体层上并彼此间隔开的源极和漏极、和连接到源极上并与栅线交叉的数据线；

在源极、漏极和数据线上形成钝化层，钝化层具有暴露数据线的数据接触孔、暴露漏极的漏接触孔、和暴露公共线的公共接触孔；以及

在钝化层上形成多个像素电极、第一公共电极、第二公共电极、第三公共电极以及辅助数据线，多个像素电极和第三公共电极设置在第一公共电极和第二公共电极之间并彼此交替排列，多个像素电极通过漏接触孔连接到漏极上，第一公共电极和第二公共电极通过公共接触孔连接到公共线上，第三公共电极连接到第一公共电极和第二公共电极上，辅助数据线通过数据接触孔连接到数据线上。

## 用于共平面开关模式液晶显示器的阵列基板及其制造方法

本申请要求享有 2006 年 6 月 21 日在韩国递交的韩国专利申请 2006-0055781 号的权益，在此引用其全部内容作为参考。

### 技术领域

本发明涉及用于共平面开关 (IPS) 模式液晶显示 (LCD) 器件的阵列基板，更具体地涉及具有修复图案的用于 IPS 模式 LCD 器件的阵列基板以及该阵列基板的制造方法。

### 背景技术

相关技术的液晶显示 (LCD) 器件利用液晶分子的光学各向异性和极化特性。由于液晶分子具有细而长的形状，液晶分子具有确定的排列方向。能够通过施加穿过液晶分子的电场来控制液晶分子的排列方向。换句话说，当电场的强度或方向改变时，液晶分子的排列也改变。由于液晶分子的光学各向异性，入射光基于液晶分子的取向而折射，所以能够通过控制光的透射率来显示图像。

最近，由于被称作有源矩阵 LCD (AM-LCD) 器件的包括作为开关元件的薄膜晶体管 (TFT) 的 LCD 器件具有高分辨率和显示动态图像的极好特性，因此 AM-LCD 器件已经得到广泛应用。

AM-LCD 器件包括阵列基板、滤色片基板以及置于其间的液晶层。阵列基板可以包括像素电极和 TFT，滤色片基板可以包括滤色片层和公共电极。通过像素电极和公共电极之间的电场来驱动 AM-LCD 器件。然而，由于 AM-LCD 器件使用垂直电场，因此 AM-LCD 器件具有很差的视角。

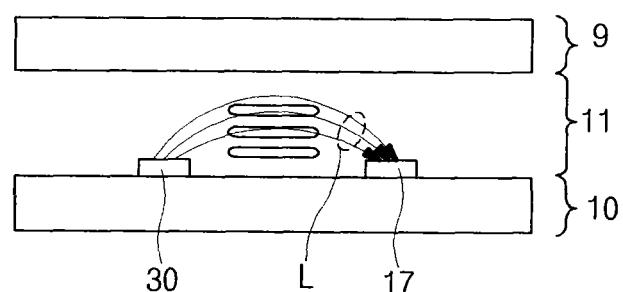

IPS 模式 LCD 器件可以用于解决上述问题。图 1 为根据相关技术的 IPS 模式 LCD 器件的横截面图。如图 1 所示，阵列基板和滤色片基板间隔开并彼此相对。阵列基板包括第一基板 10、公共电极 17 以及像素电极 30。尽管未示出，阵列基板可以包括 TFT、栅线以及数据线。滤色片基板包括第二基板 9、

滤色片层（未示出），等等。液晶层 11 置于第一基板 10 和第二基板 9 之间。由于公共电极 17 和像素电极 30 在同一水平面上形成在第一基板 10 上，因此在公共电极 17 和像素电极 30 之间产生水平电场“L”。

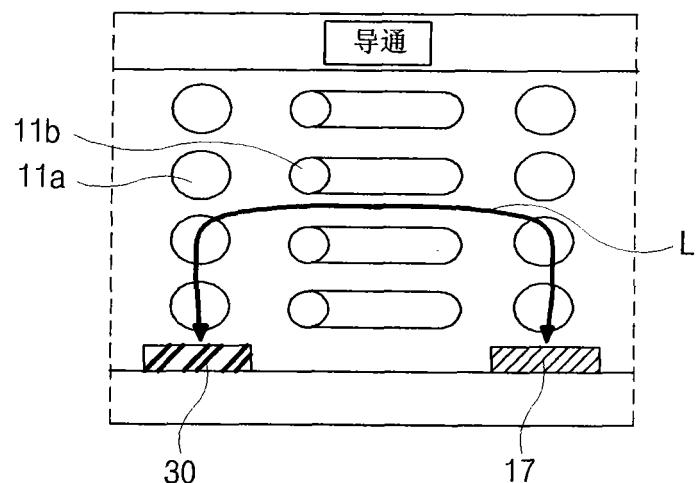

图 2A 和 2B 为显示根据相关技术的 IPS 模式 LCD 器件开/关状态的横截面图。如图 2A 所示，当将电压施加于 IPS 模式 LCD 器件时，在公共电极 17 和像素电极 30 上方的液晶分子 11a 不改变。但是，由于水平电场“L”，在公共电极 17 和像素电极 30 之间的液晶分子 11b 水平排列。由于液晶分子按照水平电场排列，因此 IPS 模式 LCD 器件具有宽视角的特性。图 2B 示出了当未将电压施加于 IPS 模式 LCD 器件时的状态。因为在公共电极 17 和像素电极 30 之间未产生电场，所以液晶分子 11 的排列不改变。

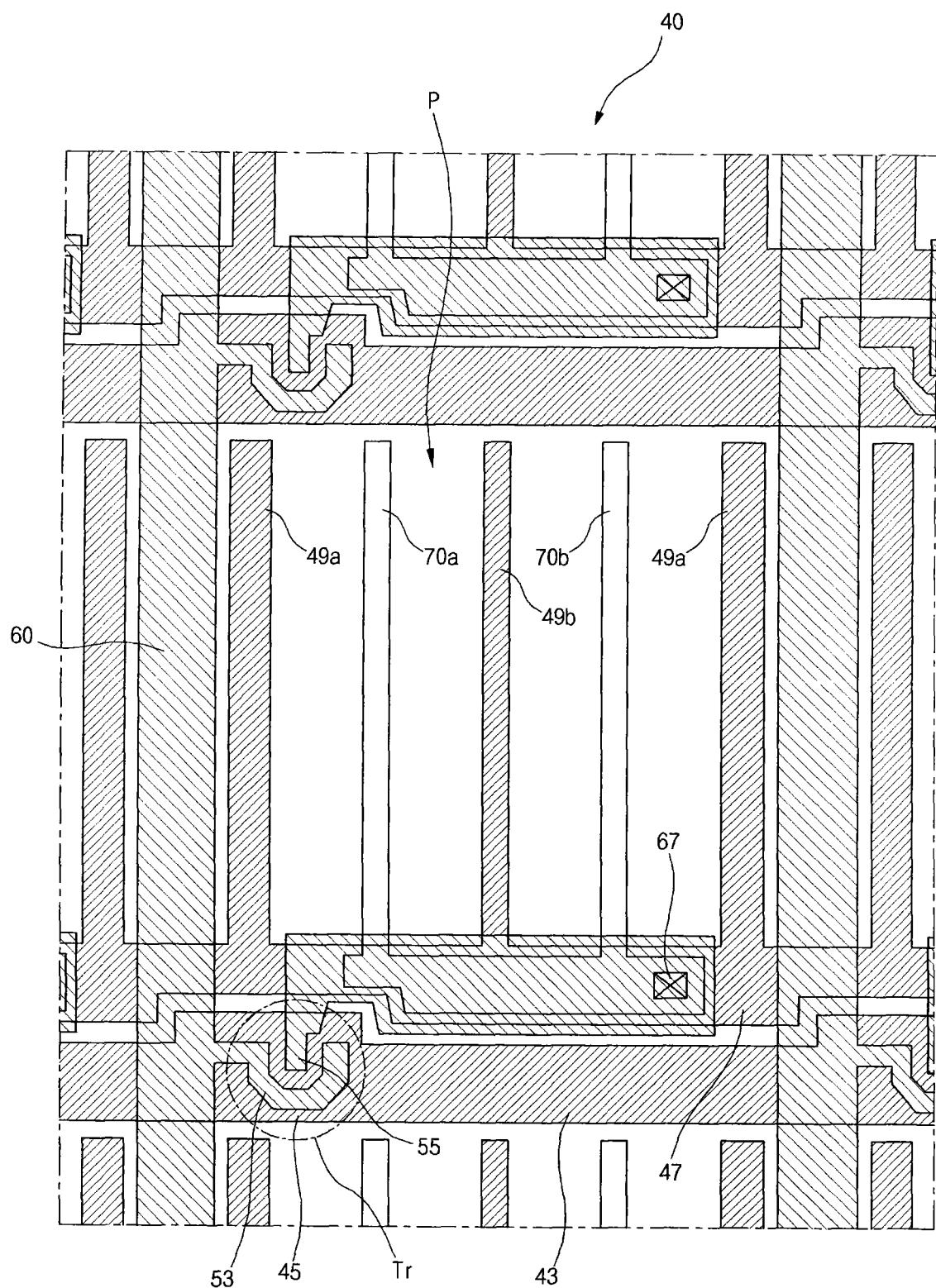

图 3 为示出根据相关技术的用于 IPS 模式 LCD 器件的阵列基板的平面图。如图 3 所示，栅线 43、公共线 47 和数据线 60 形成在第一基板 40 上。公共线 47 平行于栅线 43 并与栅线 43 间隔开。数据线 60 与栅线 43 交叉以限定像素区 P。

TFT Tr 包括栅极 45、半导体层（未示出）、源极 53 和漏极 55 并且形成在栅线 43 和数据线 60 的交叉点上。栅极 45 连接到栅线 43。栅极 45 可以为一部分栅线 43。源极 53 连接到数据线 60 上并与漏极 55 间隔开。此外，多个像素电极 70a 和 70b 以及多个公共电极 49a 和 49b 形成在像素区 p 中。多个像素电极 70a 和 70b 以及多个公共电极 49a 和 49b 彼此平行并交替排列。多个像素电极 70a 和 70b 通过漏接触孔 67 连接到漏极 55 上。多个公共电极 49a 和 49b 连接到公共线 47 上。多个公共电极 49a 和 49b 可以从公共线 47 延伸出。

如上所述，由于公共电极和像素电极之间的水平电场，图 3 的 IPS 模式 LCD 器件具有宽视角。然而，这存在一些问题。具体地说，当在制造过程中例如数据线的电线断开时，很难修复断开的数据线，于是产品率降低。而且，尽管在图 3 中未示出，但是由于栅绝缘层和钝化层置于公共电极和像素电极之间，因此在公共电极和像素电极之间的电场未完全水平，从而将液晶分子驱动成难以预料的排列。此外，因为由栅绝缘层和钝化层而引起的公共电极和像素电极之间大量电场减少，所以耗电量增加。

## 发明内容

因此，本发明致力于提供一种用于 IPS 模式 LCD 器件的阵列基板及其制造方法，其能够基本上克服因相关技术的局限和缺点而带来的一个或多个问题。

本发明的附加优点和特征将在后面的说明书中得以阐明，部分从说明书中会显而易见地得到，或者可通过本发明的实践得知。本发明的目的和其他优点可通过书面说明书及其权利要求以及附图中具体指出的结构来实现和得到。

为了实现这些和其它优点，按照本发明的目的，在此作为具体和广义的描述，一种用于共平面开关模式液晶显示器件的阵列基板包括：在基板上的栅线；与栅线交叉的数据线；设置在数据线上并连接到数据线上的辅助数据线；连接到栅线和数据线上的薄膜晶体管；设置在像素区中并连接到薄膜晶体管上的多个像素电极；以及多个公共电极，包括邻近数据线的第一公共电极和第二公共电极，以及在第一公共电极和第二公共电极之间的第三公共电极，所述第三公共电极与多个像素电极交替排列。

根据本发明的另一方面，一种制造用于共平面开关模式液晶显示器件的阵列基板的方法，包括：在基板上形成栅线、栅极、公共线、第一公共电极和第二公共电极，栅极连接到栅线上，第一公共电极和第二公共电极连接到公共线上；在栅线、栅极、公共线、第一公共电极和第二公共电极上形成栅绝缘层；形成在栅绝缘层上的半导体层、在半导体层上并彼此间隔开的源极和漏极、和连接到源极上并与栅线交叉的数据线；在源极、漏极和数据线上形成钝化层，钝化层具有暴露数据线的数据接触孔、暴露漏极的漏接触孔、和暴露第一公共电极和第二公共电极的公共接触孔；以及在钝化层上形成多个像素电极、第三公共电极和辅助数据线，多个像素电极和第三公共电极设置在第一公共电极和第二公共电极之间并彼此交替排列，多个像素电极通过漏接触孔连接到漏极上，第三公共电极通过公共接触孔连接到第一公共电极和第二公共电极上，辅助数据线通过数据接触孔连接到数据线上。

根据本发明的再一方面，一种制造用于共平面开关模式液晶显示器件的阵列基板的方法，包括：在基板上形成栅线、连接到栅线上的栅极以及公共线；在栅线、栅极和公共线上形成栅绝缘层；形成在栅绝缘层上的半导体层、在半导体层上并彼此间隔开的源极和漏极、和连接到源极上并与栅线交叉的数据

线；在源极、漏极和数据线上形成钝化层，钝化层具有暴露数据线的数据接触孔、暴露漏极的漏接触孔、和暴露公共线的公共接触孔；以及在钝化层上形成多个像素电极、第一公共电极、第二公共电极、第三公共电极以及辅助数据线，多个像素电极和第三公共电极设置在第一公共电极和第二公共电极之间并彼此交替排列，多个像素电极通过漏接触孔连接到漏极上，第一公共电极和第二公共电极通过公共接触孔连接到公共线上，第三公共电极连接到第一公共电极和第二公共电极上，辅助数据线通过数据接触孔连接到数据线上。

应该理解，上面的概括性描述和下面的详细描述都是示意性和解释性的，意欲对本发明的权利要求提供进一步的解释。

## 附图说明

本申请所包括的附图用于提供对本发明的进一步理解，并且包括在该申请中而作为本申请的一部分，示出了本发明的实施方式并且连同说明书一起用于解释本发明的原理。

图 1 为根据相关技术的 IPS 模式 LCD 器件的横截面图。

图 2A 和 2B 为示出根据相关技术的 IPS 模式 LCD 器件的开/关状态的横截面图。

图 3 为示出根据相关技术的用于 IPS 模式 LCD 器件的阵列基板的平面图。

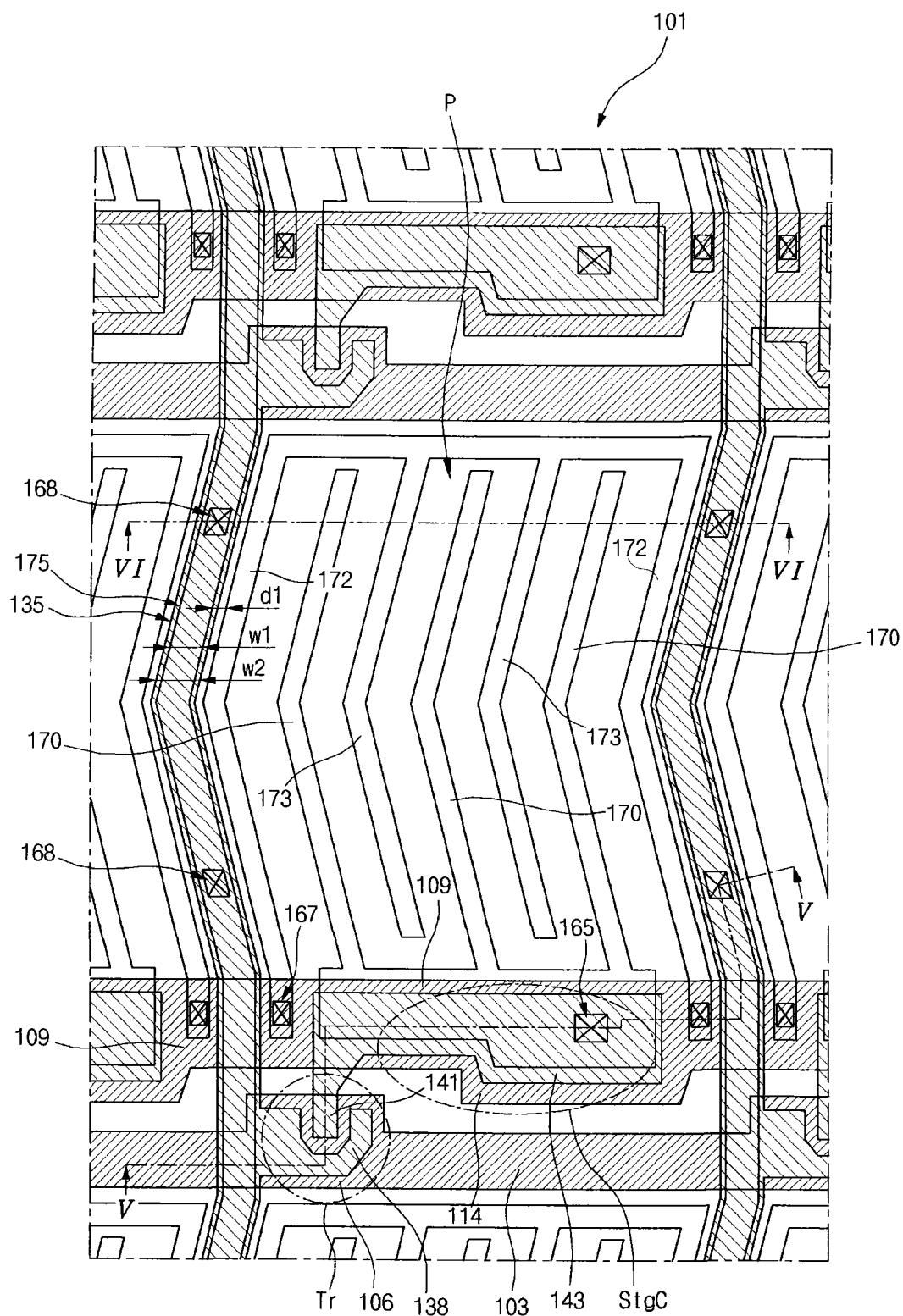

图 4 为示出根据本发明第一个实施方式的用于 IPS 模式 LCD 器件的阵列基板的平面图。

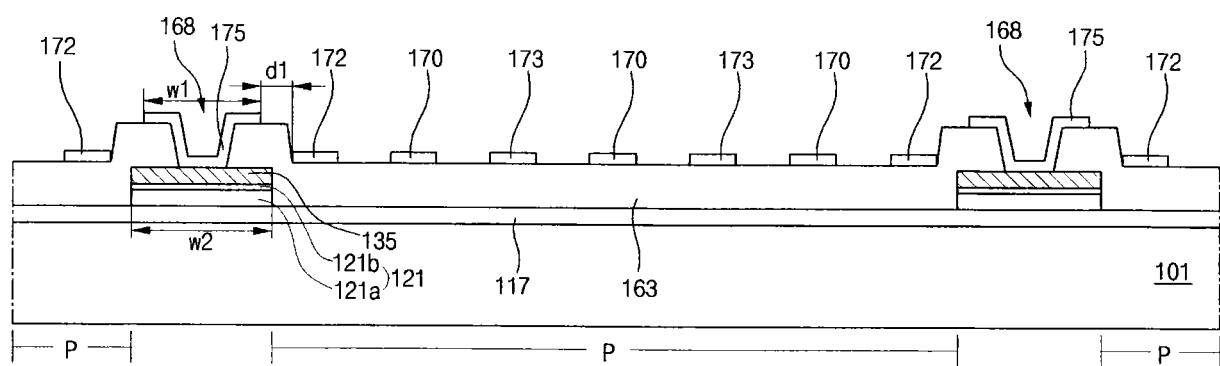

图 5 为沿图 4 的线 V-V 提取的横截面图。

图 6 为沿图 4 的线 VI-VI 提取的横截面图。

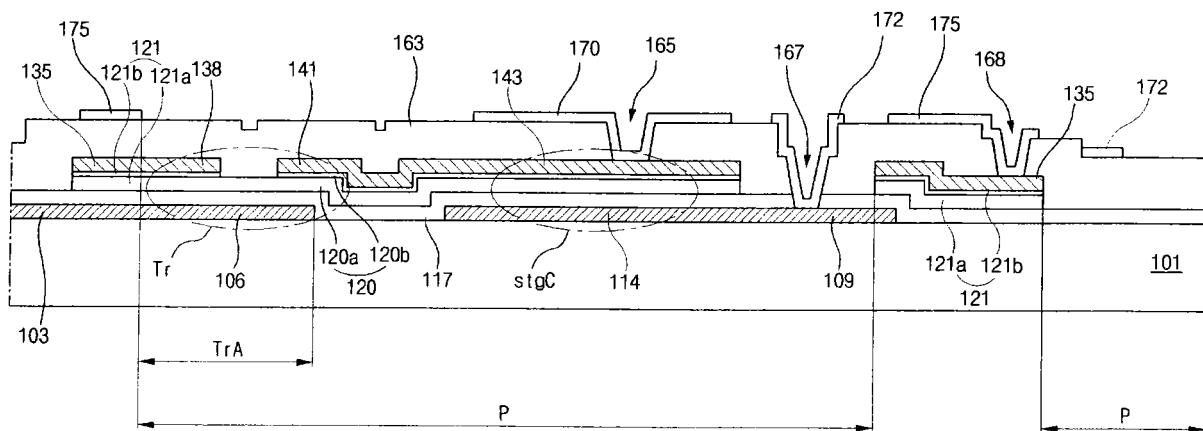

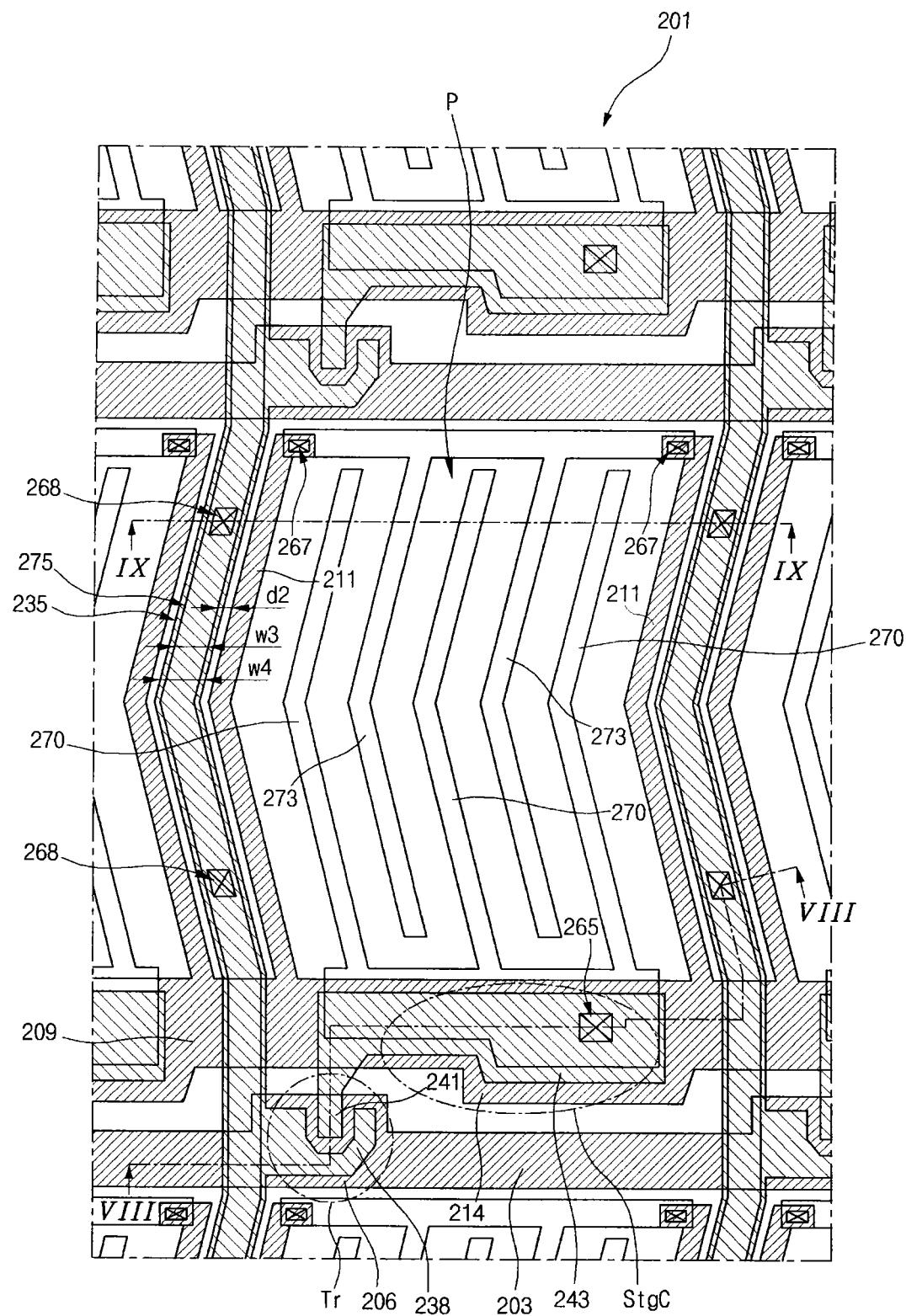

图 7 为示出根据本发明第二个实施方式的用于 IPS 模式 LCD 器件的阵列基板的平面图。

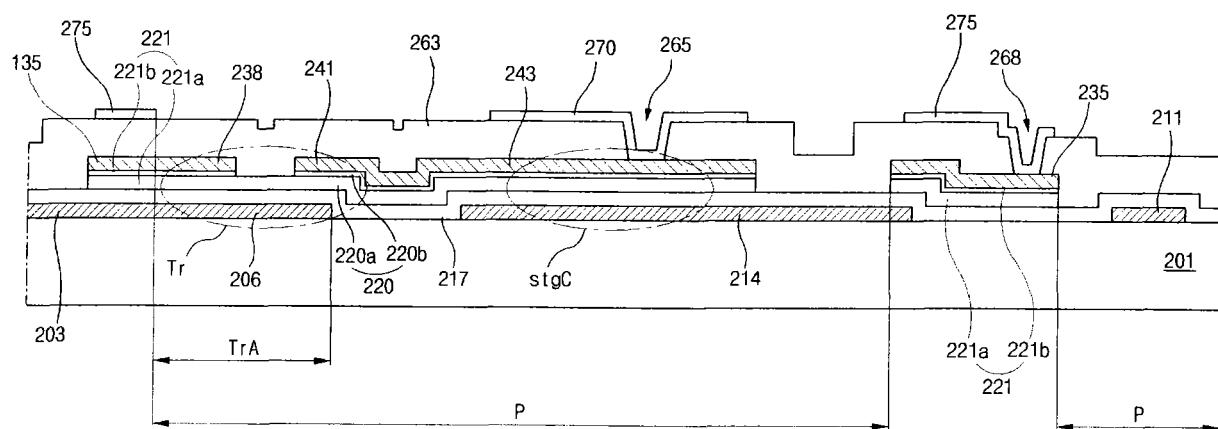

图 8 为沿图 7 的线 VIII-VIII 提取的横截面图。

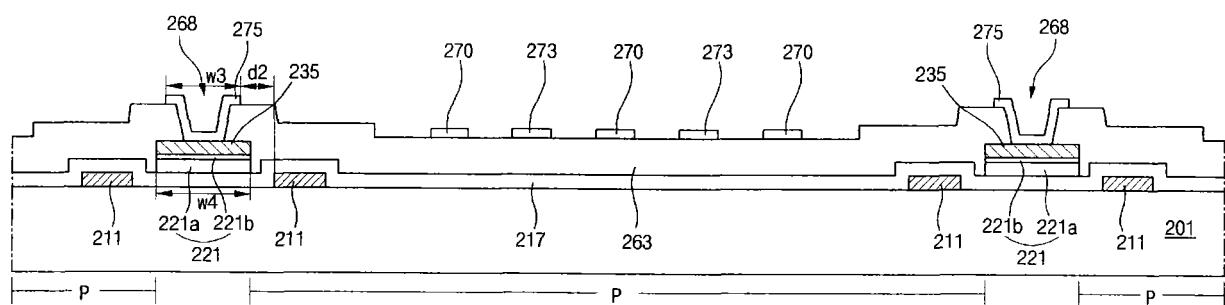

图 9 为沿图 7 的线 IX-IX 提取的横截面图。

## 具体实施方式

以下将详细涉及本发明的优选实施方式，其实施例在附图中示出。

用于 IPS 模式 LCD 器件的阵列基板具有在数据线之上的辅助数据线。钝

化层置于辅助数据线和数据线之间，辅助数据线通过钝化层上的数据接触孔连接到数据线上。而且，像素电极和公共电极在同一水平面上形成在基板上。

图 4 为示出根据本发明第一个实施方式的用于 IPS 模式 LCD 器件的阵列基板的平面图。如图 4 所示，栅线 103 和数据线 135 形成在基板 101 上。栅线 103 和数据线 135 彼此交叉以限定像素区 P。公共线 109 形成在基板 101 上。公共线 109 基本平行于栅线 103 并与栅线 103 间隔开。TFT Tr 包括栅极 106、栅绝缘层（未示出）、半导体层（未示出）、源极 138 和漏极 141 并且形成在栅线 103 和数据线 135 的交叉点上。栅极 106 连接到栅线 103 上，栅绝缘层（未示出）形成在栅极 106 上。栅极 106 可以为一部分栅线 103。半导体层（未示出）形成在栅绝缘层（未示出）上并对应于栅极 106。源极 138 和漏极 141 形成在半导体层（未示出）上并彼此间隔开。源极 138 连接到数据线 135 上。

通过公共接触孔 167 连接到公共线 109 上的第一公共电极 172 和第二公共电极 173 形成在像素区 P 中。第一公共电极 172 设置在像素区 P 的边界部分。即，第一公共电极 172 邻近数据线 135。第二公共电极 173 设置在第一公共电极 172 之间。第一公共电极 172 和第二公共电极 173 基本平行于数据线 135。第一公共电极 172 的一端连接到公共线 109 上，而第一公共电极 172 的另一端与第二公共电极 173 的一端彼此连接在一起。此外，通过漏接触孔 165 连接到漏极 141 的多个像素电极 170 形成在像素区 P 中。多个像素电极 170 基本平行于第一公共电极 172 和第二公共电极 173。多个像素电极 170 可以置于一个第一公共电极 172 和一个第二公共电极 173 之间以及置于第二公共电极 173 之间。即，多个像素电极 170 与第一公共电极 172 和第二公共电极 173 交替排列。第一公共电极 172、第二公共电极 173 和多个像素电极 170 基本平行于数据线 135。第一公共电极 172、第二公共电极 173 和多个像素电极 170 可以是由例如铟锡氧化物（ITO）和铟锌氧化物（IZO）的透明导电物质形成，并设置在同一水平面上。在图 4 中，数据线 135、第一公共电极 172、第二公共电极 173 以及多个像素电极 170 各具有弯曲部分以产生多畴。然而，在形状上并没有限制。数据线 135、第一公共电极 172、第二公共电极 173 以及多个像素电极 170 可以具有线形或者 Z 字形。

辅助数据线 175 沿着数据线 135 形成。辅助数据线 175 设置在数据线 135 之上，并具有与数据线 135 基本相同的形状。辅助数据线 175 通过数据连接孔

168 连接到数据线 135 上。在每个像素区 P 中，至少两个数据连接孔 168 形成在数据线 135 的两端。辅助数据线 175 可以是由例如铟锡氧化物 (ITO) 和铟锌氧化物 (IZO) 的透明导电物质形成。辅助数据线的宽度 w1 等于或者小于数据线 135 的宽度 w2。第一公共电极 172 与辅助数据线 175 间隔第一距离 d1，以防止辅助数据线 175 和第一公共电极 172 之间的短路缺陷。

此外，漏极 141 延伸出并与公共线 109 交叠。公共线 109 的交叠部分用作第一电容电极 114，漏极 141 的交叠部分用作第二电容电极 143。置于第一电容电极 141 和第二电容电极 143 之间的栅绝缘层（未示出）和半导体层（未示出）用作介电材料。第一电容电极 114、第二电容电极 143、栅绝缘层以及半导体层构成存储电容 StgC。

图 5 为沿图 4 的线 V-V 提取的横截面图，图 6 为沿图 4 的线 VI-VI 提取的横截面图。如图 5 和图 6 所示，多个像素区 P 和开关区 TrA 限定在基板 101 上。栅线 103、栅极 106、公共线 109 和第一电容电极 114 形成在基板 101 上。在开关区 TrA 中的栅线 103 用作栅极 106。即，栅极 106 为一部分栅线 103。公共线 109 平行于栅线 103 并与栅线 103 间隔开。一部分公共线 109 用作第一电容电极 114。栅绝缘层 117 形成在栅线 103、栅极 106、公共线 109 和第一电容电极 114 上。半导体层 120，包括本征非晶硅的有源层 120a 和掺杂非晶硅的欧姆接触层 120b，形成在栅绝缘层 117 上并对应于栅极 106。源极 138 和漏极 141 形成在半导体层 120 上并彼此间隔开。在欧姆接触层 120b 下方的有源层 120a 通过源极 138 和漏极 141 暴露。栅极 106、包括有源层 120a 和欧姆接触层 120b 的半导体层 120、源极 138 和漏极 141 构成开关区 TrA 中的 TFT Tr。数据线 135 连接到源极 138 上并与栅线 103 交叉以限定像素区 P。由于采用单一掩模对本征非晶硅层、掺杂非晶硅层和导电金属层蚀刻以形成源极 138、漏极 141、数据线 135、欧姆接触层 120b 和有源层 120a，因此包括本征非晶硅图案 121a 和掺杂非晶硅图案 121b 的半导体图案 121 设置在数据线 135 之下。本征非晶硅构图 121a 和掺杂非晶硅构图 121b 分别从有源层 120a 和欧姆接触层 120b 延伸出。然而，当采用与有源层和欧姆接触层不同的掩模工序形成源极、漏极和数据线时，在数据线 135 之下不存在本征非晶硅构图 121a 和掺杂非晶硅构图 121b。漏极 141 延伸出并与公共线 109 交叠以限定第一电容电极 114 和第二电容电极 143。如上所述，第一电容电极 114、第二电容电

极 143、在第一电容电极 114 和第二电容电极 143 之间的栅绝缘层 117 和半导体层 120 构成存储电容 StgC。当采用与有源层和欧姆接触层不同的掩模工序形成源极、漏极和数据线时，于第一电容电极 114 和第二电容电极 143 之间存在栅绝缘层的单一介电材料。

钝化层 163 具有漏接触孔 165、公共接触孔 167 和数据接触孔 168，并且形成在源极 138、漏极 141 和数据线 135 上。漏接触孔 165 暴露出源极 141，公共接触孔 167 暴露公共线 109，数据接触孔 168 暴露数据线 135。严格地说，漏接触孔 165 暴露第二电容电极 143。多个像素电极 170、第一公共电极 172、第二公共电极 173 以及辅助数据线 175 形成在钝化层 163 上。多个像素电极 170 通过漏接触孔 165 连接到漏极 141 上，第一公共电极 172 通过公共接触孔 167 连接到公共线 109 上，辅助数据线 175 通过数据接触孔 168 连接到数据线 135 上。第一公共电极 172 形成在像素区 P 的边界部分，而第二公共电极 173 设置在第一公共电极 172 之间。多个像素电极 170 设置在一个第一公共电极 172 和一个第二公共电极 173 之间以及在第二公共电极 173 之间。换句话说，多个像素电极 170 与第一公共电极 172 和第二公共电极 173 交替排列。多个像素电极 170、第一公共电极 172 和第二公共电极 173 是由例如铟锡氧化物(ITO)和铟锌氧化物 (IZO) 的透明导电材料形成，并平行于数据线 135。多个像素电极 170、第一公共电极 172 和第二公共电极 173 可以具有弯曲形状以产生多畴。辅助数据线 175 也是由例如铟锡氧化物 (ITO) 和铟锌氧化物 (IZO) 的透明导电材料形成，并设置在数据线 135 之上。辅助数据线 175 具有与数据线 135 基本相同的形状。辅助数据线 175 的宽度 w1 等于或者小于数据线 135 的宽度 w2。辅助数据线 175 与第一公共电极 172 间隔第一距离 d1，以防止辅助数据线 175 和第一公共电极 172 之间的短路缺陷。

TFT Tr 通过数据线 135 接收信号。当数据线 135 断开时，TFT Tr 不能够接收信号。在根据本发明第一个实施方式的用于 IPS 模式 LCD 器件的阵列基板中，由于在数据线 135 之上设置有与数据线 135 连接的辅助数据线 175，当数据线 135 断开时，由于辅助数据线 175，TFT Tr 能够接收信号。即，辅助数据线 175 用作自修复线。

而且，由于多个像素电极 170、第一公共电极 172、以及第二公共电极 173 形成在同一水平面上，在像素电极 170 和第一公共电极 172 之间以及在像素电

极 170 和第二公共电极 173 之间产生极好的水平电场，从而 IPS 模式 LCD 器件显示改善的图像。此外，由于在公共电极和像素电极之间没有例如栅线和钝化层的绝缘层，所以耗电量降低。

在根据本发明第一实施方式的用于 IPS 模式 LCD 器件的阵列基板中，由于辅助数据线和公共电极形成在同一水平面上，因此要求在辅助数据线和第一公共电极之间有足够的距离以防止短路缺陷。而且，因为由辅助数据线和第一公共电极之间的电场而引起液晶分子难以预料的排列，所以在滤色片层上的黑矩阵遮住辅助数据线和第一公共电极之间的部分，从而孔径率降低。当在辅助数据线和第一公共电极之间的距离增加以防止短路缺陷时，孔径率进一步降低。

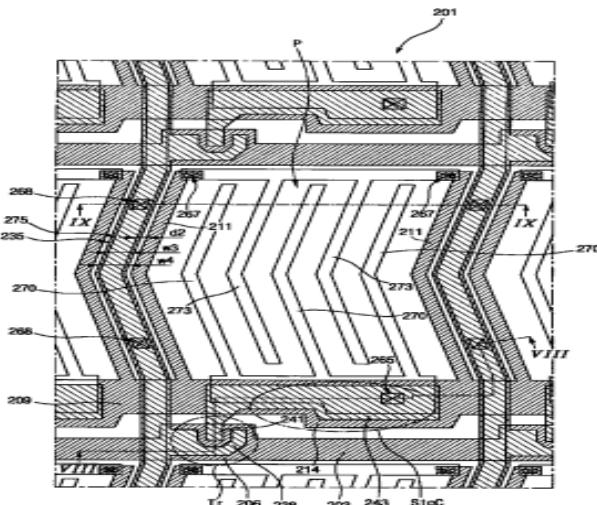

在本发明的第二个实施方式中，不存在短路缺陷并且孔径率提高。图 7 为示出根据本发明第二个实施方式的用于 IPS 模式 LCD 器件的阵列基板的平面图。如图 7 所示，栅线 203 和数据线 235 形成在基板 201 上，栅线 203 和数据线 235 彼此交叉以限定像素去 P。公共线 209 形成在基板 201 上。公共线 209 基本平行于栅线 203 并与栅线 203 间隔开。第一公共电极 211 从公共线 209 延伸出以基本平行于数据线 235。第一公共电极 211 设置在像素区 P 的边界部分。TFT Tr 包括栅极 206、栅绝缘层（未示出）、半导体层（未示出）、源极 238 和漏极 241，并且形成在栅线 203 和数据线 235 的交叉点上。栅极 206 连接到栅线 203 上，栅绝缘层（未示出）形成在栅极 206 上。栅极 206 可以为一部分栅线 203。半导体层（未示出）形成在栅绝缘层（未示出）上并对应于栅极 206。源极 238 和漏极 241 形成在半导体层（未示出）上并彼此间隔开。源极 238 连接到数据线 235 上。

通过公共接触孔 267 连接到第一公共电极 211 的第二公共电极 273 形成在像素区 P 中。第二公共电极 273 设置在第一公共电极 211 之间并基本平行于第一公共电极 211。此外，通过漏接触孔 265 连接到漏极 241 的多个像素电极 270 形成在像素区 P 中。多个像素电极 270 基本平行于第一公共电极 211 和第二公共电极 273。多个像素电极 270 可以设置在一个第一公共电极 211 和一个第二公共电极 273 之间以及第二公共电极 273 之间。即，多个像素电极 270 与第一公共电极 211 和第二公共电极 273 交替排列。第二公共电极 273 和多个像素电极 270 可以是由例如铟锡氧化物（ITO）和铟锌氧化物（IZO）的透明导电材

料形成，并设置在同一水平面上。在图 7 中，数据线 235、第一公共电极 211、第二公共电极 273 和多个像素电极 270 各具有弯曲部分以产生多畴。然而，在形状上并没有限制。数据线 235、第一公共电极 272、第二公共电极 273 和多个像素电极 270 可以具有直线形或 Z 字形。

辅助数据线 275 沿着数据线 235 形成。辅助数据线 275 设置在数据线 235 之上，并基本上具有与数据线 235 相同的形状。辅助数据线 275 通过数据连接孔 268 连接到数据线 235 上。在每个像素区 P 中，至少两个数据接触孔 268 形成在数据线 235 的两端。辅助数据线 275 可以是由例如铟锡氧化物 (ITO) 和铟锌氧化物 (IZO) 的透明导电材料形成。辅助数据线 275 的宽度 w3 等于或者小于数据线 235 的宽度 w4。第一公共电极 211 与辅助数据线 275 间隔第二距离 d2。由于第一公共电极 211 形成在与数据线 235 和辅助数据线 275 不同的层中，因此不需要在第一公共电极 211 和数据线 235 和辅助数据线中之一之间有足够的距离，并且没有短路的可能性。相应地，第二距离 d2 小于在图 5 中的第一距离 d1，并且在滤色片基板上的黑矩阵具有相对小的宽度来遮盖第一公共电极 211 和辅助数据线 275 之间的部分。作为结果，孔径率提高。

此外，漏极 241 延伸并与公共线 209 交叠。公共线 209 的交叠部分用作第一电容电极 241，漏极 241 的交叠部分用作第二电容电极 243。置于第一电容电极 241 和第二电容电极 243 之间的栅绝缘层（未示出）和半导体层（未示出）用作介电材料。第一电容电极 214、第二电容电极 243、栅绝缘层以及半导体层构成存储电容 StgC。

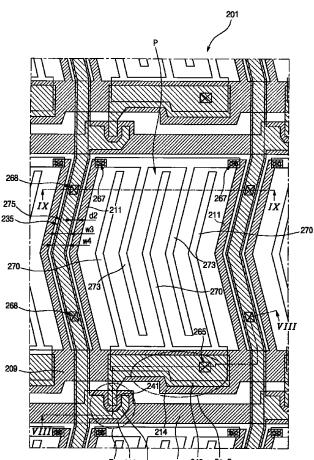

图 8 为沿图 7 的线 VIII-VIII 提取的横截面图，图 9 为沿图 7 的线 IX-IX 提取的横截面图。如图 8 和图 9 所示，在基板 201 上限定多个像素区 P 和开关区 TrA。栅线 203、栅极 206、公共线 209、第一电容电极 214 以及第一公共电极 211 形成在基板 201 上。在开关区 TrA 中的栅线 203 用作栅极 206。即，栅极 206 为一部分栅线 203。公共线 209 平行于栅线 203 并与栅线 203 间隔开。一部分公共线 209 用作第一电容电极 214。第一公共电极 211 形成在像素区 P 的边界部分。第一公共电极 211 基本垂直于栅线 203。栅绝缘层 217 形成在栅线 203、栅极 206、公共线 209、第一电容电极 214 和第一公共电极 211 上。半导体层 220 包括本征非晶硅的有源层 220a 和掺杂非晶硅的欧姆接触层 220b，并且形成在栅绝缘层 217 上，并对应于栅极 206。源极 238 和漏极 241 形成在

半导体层 220 上并彼此间隔开。在欧姆接触层 220b 之下的有源层 220a 通过源极 238 和漏极 241 暴露。在开关区 TrA 中，栅极 206、包括有源层 220a 和欧姆接触层 220b 的半导体层 220、源极 238 和漏极 241 构成 TFT Tr。数据线 235 连接到源极 238 上，并与栅线 203 交叉以限定像素区 P。由于采用单一掩模对本征非晶硅层、掺杂非晶硅层和导电金属层蚀刻以形成源极 238、漏极 241、数据线 235、欧姆接触层 220b 和有源层 220a，因此包括本征非晶硅图案 221a 和掺杂非晶硅图案 221b 的半导体图案 221 设置在数据线 235 之下。本征非晶硅图案 221a 和掺杂非晶硅图案 221b 分别从有源层 220a 和欧姆接触层 220b 延伸出。然而，当采用与有源层和欧姆接触层不同的掩模工序形成源极、漏极和数据线时，在数据线 235 之下不存在本征非晶硅图案 221a 和掺杂非晶硅图案 221b。漏极 241 延伸并与公共线 209 交叠以限定第一电容电极 214 和第二电容电极 243。如上所述，第一电容电极 214、第二电容电极 243、在第一电容电极 214 和第二电容电极 243 之间的栅绝缘层 217 和半导体层 220 构成存储电容 StgC。当采用与有源层和欧姆接触层不同的掩模工序形成源极、漏极和数据线时，在第一电容电极 214 和第二电容电极 243 之间存在栅绝缘层的单一介电材料。

钝化层 263 具有漏接触孔 265、公共接触孔 267(图 7)和数据接触孔 268，并且形成在源极 238、漏极 241 和数据线 235 上。漏接触孔 265 暴露源极 241，公共接触孔 267(图 7 中)暴露第一公共电极 211，数据接触孔 268 暴露数据线 235。严格地说，漏接触孔 265 暴露第二电容电极 243。多个像素电极 270、第二公共电极 273 和辅助数据线 275 形成在钝化层 263 上。多个像素电极 270 通过漏接触孔 265 连接到漏极 241 上，第二公共电极 273 通过公共接触孔 267(图 7 中)连接到第一公共电极 211 上，辅助数据线 275 通过数据接触孔 268 连接到数据线 235 上。第二公共电极 273 设置在第一公共电极 211 之间。多个像素电极 270 设置在一个第一公共电极 211 和一个第二公共电极 273 之间以及第二公共电极 273 之间。换句话说，多个像素电极 270 与第一公共电极 211 和第二公共电极 273 交替排列。多个像素电极 270 和第二公共电极 273 是由例如铟锡氧化物 (ITO) 和铟锌氧化物 (IZO) 的透明导电材料形成。多个像素电极 270、第一公共电极 211 和第二公共电极 273 基本上平行于数据线 235。多个像素电极 270、第一公共电极 211 和第二公共电极 273 可以具有弯曲的形状

以产生多畴。辅助数据线也可以由例如铟锡氧化物(ITO)和铟锌氧化物(IZO)的透明导电材料形成，并且设置在数据线235上。辅助数据线275具有与数据线235基本相同的形状。辅助数据线275的宽度w3等于或者小于数据线235的宽度w4。辅助数据线275与第一公共电极211间隔第二距离d2。如上所述，由于第一公共电极211形成在与数据线235和辅助数据线275不同的层上，因此不存在短路缺陷。相应地，由于第二距离d2小于第一距离d1，因此孔径率提高。

而且，在根据本发明第二个实施方式的用于IPS模式LCD器件的阵列基板中，由于在数据线235之上设置有与数据线235连接的辅助数据线275，因此当数据线235断开时，由于辅助数据线275，TFT Tr能够接收信号。即，辅助数据线275用作自修复线。

此外，由于多个像素电极270和第二公共电极273形成在同一水平面上，因此在像素电极270和第二公共电极273之间产生极好的水平电场，从而IPS模式LCD器件显示改善的图像。另外，由于在第二公共电极和像素电极之间没有例如栅线和钝化层的绝缘层，因此耗电量减少。

以下不用附图来解释根据本发明第二个实施方式的阵列基板的制造方法。

首先，通过沉积包括铝(Al)、合金铝(AlNd)、铜(Cu)、铜(Cu)合金、铬(Cr)和钼(Mo)的导电金属材料，在基板上形成第一导电金属层。对第一导电金属层构图，以形成栅线、公共线和第一公共电极。在开关区中的栅线用作栅极，一部分公共线用作第一电容电极。在第一个实施方式中，第一公共电极不是由第一导电金属层构成。

接着，通过沉积包括氧化硅(SiO<sub>2</sub>)和硅的氮化物(SiNx)的无机介电材料和包括苯并环丁烯(BCB)和光敏压克力的有机绝缘材料中的一种，在栅线、公共线和第一公共电极上形成栅绝缘层。

接着，在栅绝缘层上依次形成本征非晶硅层、掺杂非晶硅层和第二导电金属层。采用折射曝光掩模和半色调掩模中的一种，对本征非晶硅层、掺杂非晶硅层和第二导电金属层构图，以形成有源层、欧姆接触层、源极、漏极和数据线。在开关区中，栅极、有源层、欧姆接触层、源极和漏极构成TFT。源极连接到数据线上，并与漏极间隔开。采用源极和漏极作为蚀刻掩模对欧姆接触

层蚀刻，以暴露有源层。数据线与栅线交叉以限定像素区。漏极延伸并与第一电容电极交叠以形成存储电容。由于采用单一掩模对本征非晶硅层、掺杂非晶硅层和第二导电金属层构图，因此数据线之下存在本征非晶硅图案和欧姆接触图案。然而，当采用不同掩模对本征非晶硅层、掺杂非晶硅层和第二导电层构图时，在数据线之下不存在本征非晶硅图案和欧姆接触图案。

接着，通过沉积包括氧化硅（ $\text{SiO}_2$ ）和硅的氮化物（ $\text{SiN}_x$ ）的无机介电材料和包括苯并环丁烯（BCB）和光敏压克力的有机介电材料中的一种，在源极、漏极和数据线上形成钝化层。对钝化层构图以形成漏接触孔、公共接触孔和数据接触孔。漏接触孔暴露漏极，公共接触孔暴露第一公共电极，数据接触孔暴露数据线。由于在第二个实施方式中，第一公共电极形成在栅绝缘层之下，因此，用钝化层对栅绝缘层构图以暴露第一公共电极。在第一个实施方式中，由于第一公共电极形成在钝化层之下，因此公共接触孔暴露公共线。

接着，通过沉积包括氧化铟锡（ITO）和氧化铟锌（IZO）的透明导电材料，在钝化层上形成透明导电金属层。对透明导电层构图以形成第二公共电极、多个像素电极和辅助数据线。第二公共电极通过公共接触孔连接到第一公共电极上，多个像素电极通过漏接触孔连接到漏极上，辅助数据线通过数据接触孔连接到数据线上。多个像素电极与第一公共电极和第二公共电极交替排列。多个像素电极、第一公共电极和第二公共电极基本平行于数据线。辅助数据线具有等于或者小于数据线的宽度。在第一个实施方式中，第一公共电极是由透明导电金属材料形成。第一公共电极通过公共接触孔连接到公共线上。

从而，在根据本发明的用于 LCD 器件的阵列基板中，由于连接到数据线的辅助数据线形成在数据线之上，因此辅助数据线用作断开数据线时的自修复线。而且，由于像素电极和公共电极形成在同一水平上，因此 IPS 模式 LCD 器件能够显示改善的图像，并且耗电量减少。

对于本领域技术人员显而易见的是，在不背离本发明精神或范围的条件下对本发明的用于共平面开关模式液晶显示器的阵列基板及其制造方法可以做出各种变型和修改。因此，倘若本发明的修改和变型在权利要求及其等同物的范围之内，本发明应包括这些修改和变型。

图 1

图 2A

图 2B

图 3

图 4

图 5

图 6

图 7

图 8

图 9

|                |                                                           |         |            |

|----------------|-----------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于共平面开关模式液晶显示器的阵列基板及其制造方法                                 |         |            |

| 公开(公告)号        | <a href="#">CN101093329A</a>                              | 公开(公告)日 | 2007-12-26 |

| 申请号            | CN200710105864.X                                          | 申请日     | 2007-05-31 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                  |         |            |

| 申请(专利权)人(译)    | LG. 菲利浦LCD株式会社                                            |         |            |

| 当前申请(专利权)人(译)  | LG. 菲利浦LCD株式会社                                            |         |            |

| [标]发明人         | 徐范植<br>金志源                                                |         |            |

| 发明人            | 徐范植<br>金志源                                                |         |            |

| IPC分类号         | G02F1/1362 H01L27/12                                      |         |            |

| CPC分类号         | G02F1/134363 G02F1/136259 G02F2001/136263 G02F2001/136272 |         |            |

| 代理人(译)         | 徐金国                                                       |         |            |

| 优先权            | 1020060055781 2006-06-21 KR                               |         |            |

| 其他公开文献         | CN101093329B                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>            |         |            |

## 摘要(译)

本发明涉及用于共平面开关模式液晶显示器件的阵列基板，包括：在基板上的栅线；与栅线交叉的数据线；设置在数据线之上并连接到数据线上的辅助数据线；连接到栅线和数据线上的薄膜晶体管；设置在像素区内并连接到薄膜晶体管上的多个像素电极；以及多个公共电极，包括邻近数据线的第一公共电极和第二公共电极，以及在第一公共电极和第二公共电极之间的第三公共电极，所述第三公共电极与多个像素电极交替排列。