[19] 中华人民共和国国家知识产权局

[51] Int. Cl.

## 〔12〕发明专利说明书

专利号 ZL 200610087803.0

*G02F 1/133 (2006. 01 )

G09G 3/36 (2006. 01 )

G02F 1/1333 (2006. 01 )

G02F 1/136 (2006. 01 )

H01L 27/00 (2006. 01 )*

[45] 授权公告日 2009 年 9 月 2 日

[11] 授权公告号 CN 100535714C

〔22〕申请日 2006.6.9

[21] 申请号 200610087803.0

[30] 优先权

〔32〕 2005. 12. 20 〔33〕 KR 〔31〕 10-2005-0126256

[73] 专利权人 乐金显示有限公司

地址 韩国首尔

[72] 发明人 李建熙 朴星一

[56] 参考文献

CN1266199A 2000.9.13

JP7-294898A 1995.11.10

IP8 - 95076A 1996.4.12

US2004/0150771A1 2004.8.5

JP2001 = 100217A 2001-4-13

审查员 彭志红

[74] 专利代理机构 北京三友知识产权代理有限公司

代理人 李 磊

代理人 李 辉

权利要求书 3 页 说明书 15 页 附图 15 页

〔54〕发明名称

液晶显示器件及其制造方法

〔57〕 摘要

本发明涉及一种适于减小其上安装有驱动电路的液晶显示器件的处理时间和防止滤色器阵列基板的公共电极和薄膜晶体管阵列基板的驱动电路之间的短路的液晶显示器件及其制造方法。根据本发明实施例的液晶显示器件包括：形成在上基板上的公共电极；形成在与上基板相对的下基板上的选通驱动器；形成在与选通驱动器相对的公共电极上的绝缘图案；以及用于接合上基板和下基板的导电密封剂。

1、一种液晶显示器件，其包括：

形成在上基板上的公共电极；

在与所述上基板相对的下基板上的薄膜晶体管阵列；

形成在所述下基板上的选通驱动器，该选通驱动器包括形成在所述下基板上的信号线组，用于提供电源信号和选通控制信号；

所述薄膜晶体管阵列包括与所述信号线组中的至少一个相连的多个薄膜晶体管，其中，所述信号线组和所述薄膜晶体管通过第一连接图案和第二连接图案连接；

形成在与所述第一连接图案和第二连接图案对应的公共电极上的绝缘图案；以及

用于接合所述上基板和所述下基板的导电密封剂，用于将公共电压施加给所述公共电极，并设置在所述绝缘图案和所述第一连接图案、第二连接图案之间。

2、根据权利要求 1 所述的液晶显示器件，其中，所述绝缘图案的厚度被形成为等于或小于所述上基板和所述下基板之间的单元间隙。

3、根据权利要求 1 所述的液晶显示器件，还包括：

覆盖所述信号线组的栅极绝缘膜；

覆盖所述栅极绝缘膜和所述薄膜晶体管的钝化膜；

贯穿所述栅极绝缘膜和所述钝化膜以暴露出所述信号线组的第一接触孔；

贯穿所述栅极绝缘膜和所述钝化膜以暴露出所述薄膜晶体管的第二接触孔；其中

所述第一连接图案和第二连接图案形成在所述钝化膜上，用于通过所述第一接触孔和所述第二接触孔将所述信号线组连接到所述薄膜晶体管。

4、根据权利要求 3 所述的液晶显示器件，其中，所述绝缘图案与所述第一连接图案和第二连接图案重叠。

5、根据权利要求 1 所述的液晶显示器件，该液晶显示器件还包括：

覆盖所述信号线组的栅极绝缘膜；

形成在所述栅极绝缘膜上的附加连接图案；

覆盖所述栅极绝缘膜和所述薄膜晶体管的钝化膜；

贯穿所述栅极绝缘膜和所述钝化膜以暴露出所述信号线组的第一接触孔；

贯穿所述栅极绝缘膜和所述钝化膜以暴露出所述薄膜晶体管的第二接触孔；

贯穿所述钝化膜以暴露出所述附加连接图案的第三和第四接触孔；

其中

所述第一连接图案形成在所述钝化膜上，用于通过所述第一接触孔和所述第三接触孔将所述信号线组连接到所述附加连接图案；以及

所述第二连接图案形成在所述钝化膜上，用于通过所述第二接触孔和所述第四接触孔将所述薄膜晶体管连接到所述附加连接图案。

6、根据权利要求 5 所述的液晶显示器件，其中，所述绝缘图案与所述第一和第二连接图案重叠。

7、一种液晶显示器件的制造方法，所述方法包括以下步骤：

在下基板上设置薄膜晶体管阵列而形成为薄膜晶体管阵列基板，该薄膜晶体管阵列基板具有多条选通线，形成在所述下基板上的选通驱动器，其包括向所述选通线提供电源信号和选通控制信号的信号线组；所述薄膜晶体管阵列包括与所述信号线组中的至少一个相连的多个薄膜晶体管，其中，所述信号线组和所述薄膜晶体管通过第一连接图案和第二连接图案连接；

在上基板上设置滤色器阵列而形成为滤色器阵列基板，该滤色器阵列基板具有用于接收公共电压的公共电极，以及在所述公共电极的与所述第一连接图案和第二连接图案相对应的区域上形成的绝缘图案；以及

使用导电密封剂接合所述薄膜晶体管阵列基板和所述滤色器阵列基板，该导电密封剂设置在所述绝缘图案和所述第一连接图案、第二连接图案之间。

8、根据权利要求 7 所述的制造方法，其中，与用于保持所述薄膜晶体管阵列基板和所述滤色器阵列基板之间的单元间隙的间隔物一起同时形成所述绝缘图案。

9、根据权利要求 8 所述的制造方法，其中，所述绝缘图案的厚度被形成为等于或小于所述单元间隙。

10、一种液晶显示器件的制造方法，包括以下步骤：

在下基板上设置薄膜晶体管阵列而形成为薄膜晶体管阵列基板，所述薄膜晶体管阵列基板包括相互交叉的多条选通线和数据线、形成在所述交叉部分处的薄膜晶体管、与所述薄膜晶体管相连的像素电极、以及选通驱动器，所述选通驱动器包括向所述选通线提供电源信号和选通控制信号的信号线组；

所述薄膜晶体管与所述信号线组中的至少一个相连，其中，所述信号线组和所述薄膜晶体管通过第一连接图案和第二连接图案连接；

在上基板上设置滤色器阵列而形成为滤色器阵列基板，其包括黑底、滤色器、用于与所述像素电极一起形成垂直电场的接收公共电压的公共电极、用于保持所述薄膜晶体管阵列基板和所述滤色器阵列基板之间的单元间隙厚度的间隔物、以及在所述公共电极的与所述第一连接图案和第二连接图案相对应的区域上形成的绝缘图案，其中所述绝缘图案的厚度被形成为不大于所述间隔物的厚度；以及

使用导电密封剂接合所述薄膜晶体管阵列基板和所述滤色器阵列基板，该导电密封剂设置在所述绝缘图案和所述第一连接图案、第二连接图案之间。

11、根据权利要求 10 所述的制造方法，其中，与用于保持所述薄膜晶体管阵列基板和所述滤色器阵列基板之间的单元间隙的间隔物一起同时形成所述绝缘图案。

12、根据权利要求 10 所述的制造方法，其中，所述绝缘图案的厚度被形成为等于或小于所述上基板和所述下基板之间的单元间隙。

## 液晶显示器件及其制造方法

### 技术领域

本发明涉及一种液晶显示器件及其制造方法，更具体地，涉及一种适于减小其上安装有驱动电路的液晶显示器件的处理时间和防止上板的公共电极和下板的驱动电路之间的短路的液晶显示器件及其制造方法。

### 背景技术

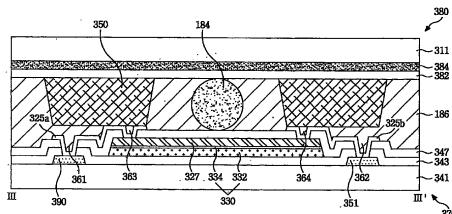

液晶显示器件通过使用电场来控制液晶的透光率，由此显示图片。液晶显示器件包括彼此面对并且其间具有液晶 50 的薄膜晶体管阵列基板 70 和滤色器阵列基板 80，如图 1 和 2 所示。

薄膜晶体管阵列基板 70 包括：在下基板 1 上彼此交叉的选通线 2 和数据线 4；形成在选通线 2 和数据线 4 的交叉部分中的薄膜晶体管 30；连接到薄膜晶体管 30 的像素电极 22；涂覆在其上的用于对准液晶的下配向膜。

滤色器阵列基板 80 包括：形成在上基板 11 上的用于防止光泄漏的黑底；用于实现颜色的滤色器 12；用于与像素电极 22 形成垂直电场的公共电极 14；以及涂覆在其上的用于对准液晶的上配向膜。

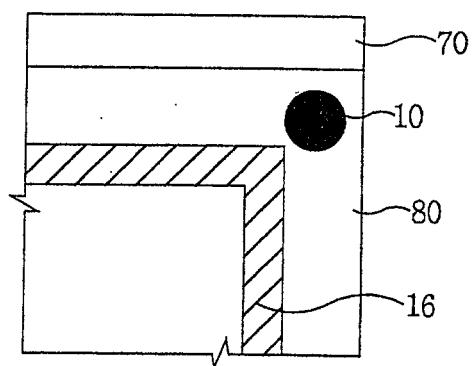

另一方面，为了向滤色器阵列基板 80 的公共电极 14 施加公共电压，在密封剂 16 的向外方向形成有银点 10，如图 2 所示。银点 10 以膏剂状态点在薄膜晶体管阵列基板 70 和滤色器阵列基板 80 之间，然后通过使用密封剂来接合两个基板 70、80。通过在接合这些基板时施加给基板 1、11 的压力使银点 10 扩散到相邻区域。此时，为了使扩展到相邻区域的银点 10 不被划片工艺损坏，在划片线的向内方向需要较多的银点区域。为了形成银点 6，在形成液晶显示板之后，应该在所有面板区域中执行银点工艺，因此，存在工艺复杂并且需要更多处理时间的问题。

此外，为了将信号提供给设置在薄膜晶体管阵列基板 70 中的选通线

2 和数据线 4，液晶显示器件还应该包括选通驱动器和数据驱动器。

选通驱动器和数据驱动器被分为以芯片形式制造的多个集成电路（下面称为“IC”）。各个驱动 IC 都被安装在 TCP（带载封装）上的开口 IC 区域中或通过 COF（膜上芯片）方法安装在 TCP 基膜上，并且通过 TAB（带自动接合）方法电连接到液晶显示板。通过这种方式，现有技术的液晶显示器件的制造方法包括分别制造驱动 IC 以及通过 TCP 接合到液晶显示板的工艺，因此其制造工艺复杂，并且其成为液晶显示器件的制造成本增加的因素。

### 发明内容

因此，本发明的目的是提供一种适于简化工艺的液晶显示器件及其制造方法。

为了实现本发明这些和其他目的，根据本发明的一个方面的液晶显示器件包括：形成在上基板上的公共电极；在与所述上基板相对的下基板上的薄膜晶体管阵列；形成在所述下基板上的选通驱动器，该选通驱动器包括形成在所述下基板上的信号线组，用于提供电源信号和选通控制信号；所述薄膜晶体管阵列包括与所述信号线组中的至少一个相连的多个薄膜晶体管，其中，所述信号线组和所述薄膜晶体管通过第一连接图案和第二连接图案连接；形成在与所述第一连接图案和第二连接图案对应的公共电极上的绝缘图案；以及用于接合上基板和下基板的导电密封剂，用于将公共电压施加给所述公共电极，并设置在所述绝缘图案和所述第一连接图案、第二连接图案之间。

在该液晶显示器件中，绝缘图案的厚度被形成为等于或小于上基板和下基板之间的单元间隙。该液晶显示器件还包括：覆盖该信号线组的栅极绝缘膜；覆盖栅极绝缘膜和薄膜晶体管的钝化膜；贯穿栅极绝缘膜和钝化膜以暴露出信号线组的第一接触孔；贯穿所述栅极绝缘膜和钝化膜以暴露出薄膜晶体管的第二接触孔；其中，所述第一连接图案和第二连接图案形成在钝化膜上，用于通过第一接触孔和第二接触孔将信号线组连接到薄膜晶体管。

在该液晶显示器件中，绝缘图案与所述第一连接图案和第二连接图案重叠。

该液晶显示器件还包括：覆盖信号线组的栅极绝缘膜；形成在栅极绝缘膜上的附加连接图案；覆盖栅极绝缘膜和薄膜晶体管的钝化膜；贯穿栅极绝缘膜和钝化膜以暴露出信号线组的第一接触孔；贯穿钝化膜以暴露出薄膜晶体管的第二接触孔；贯穿所述栅极绝缘膜和钝化膜以暴露出附加连接图案的第三和第四接触孔；其中，所述第一连接图案形成在钝化膜上，用于通过第一接触孔和第三接触孔将信号线组连接到附加连接图案；以及所述第二连接图案形成在钝化膜上，用于通过第二接触孔和第四接触孔将薄膜晶体管连接到附加连接图案。

在该液晶显示器件中，绝缘图案与第一和第二连接图案重叠。

根据本发明另一方面的液晶显示器件的制造方法包括以下步骤：在下基板上设置薄膜晶体管阵列而形成为薄膜晶体管阵列基板，该薄膜晶体管阵列基板具有多条选通线，形成在所述下基板上的选通驱动器，其包括向选通线提供电源信号和选通控制信号的信号线组，所述薄膜晶体管阵列包括与所述信号线组中的至少一个相连的多个薄膜晶体管，其中，所述信号线组和所述薄膜晶体管通过第一连接图案和第二连接图案连接；在上基板上设置滤色器阵列而形成为滤色器阵列基板，该滤色器阵列基板具有用于接收公共电压的公共电极，以及在该公共电极上的与所述第一连接图案和第二连接图案相对应的区域上形成的绝缘图案；以及使用导电密封剂接合该薄膜晶体管阵列基板和滤色器阵列基板，该导电密封剂设置在所述绝缘图案和所述第一连接图案、第二连接图案之间。

在该制造方法中，与间隔物一起形成该绝缘图案，该间隔物用于保持薄膜晶体管阵列基板和滤色器阵列基板之间的单元间隙。

在该制造方法中，绝缘图案的厚度被形成为等于或小于该单元间隙。

根据本发明再一方面的液晶显示器件的制造方法包括以下步骤：在下基板上设置薄膜晶体管阵列而形成为薄膜晶体管阵列基板，所述薄膜晶体管阵列基板包括相互交叉的多条选通线和数据线、形成在所述交叉部分处的薄膜晶体管、与所述薄膜晶体管相连的像素电极、以及选通驱

动器，所述选通驱动器包括向所述选通线提供电源信号和选通控制信号的信号线组；所述薄膜晶体管与所述信号线组中的至少一个相连，其中，所述信号线组和所述薄膜晶体管通过第一连接图案和第二连接图案连接；在上基板上设置滤色器阵列而形成为滤色器阵列基板，其包括黑底、滤色器、用于与所述像素电极一起形成垂直电场的接收公共电压的公共电极、用于保持所述薄膜晶体管阵列基板和所述滤色器阵列基板之间的单元间隙厚度的间隔物、以及在所述公共电极的与所述第一连接图案和第二连接图案相对应的区域上形成的绝缘图案，其中所述绝缘图案的厚度被形成为不大于所述间隔物的厚度；以及利用导电密封剂来接合薄膜晶体管阵列基板和滤色器阵列基板，该导电密封剂设置在所述绝缘图案和所述第一连接图案、第二连接图案之间。

在该制造方法中，与间隔物一起形成该绝缘图案，该间隔物用于保持薄膜晶体管阵列基板和滤色器阵列基板之间的单元间隙。

在该制造方法中，绝缘图案的厚度被形成为等于或小于所述上基板和所述下基板之间的单元间隙。

#### 附图说明

参照附图，根据本发明实施例的下列详细描述将明白本发明的这些及其他目的，附图中：

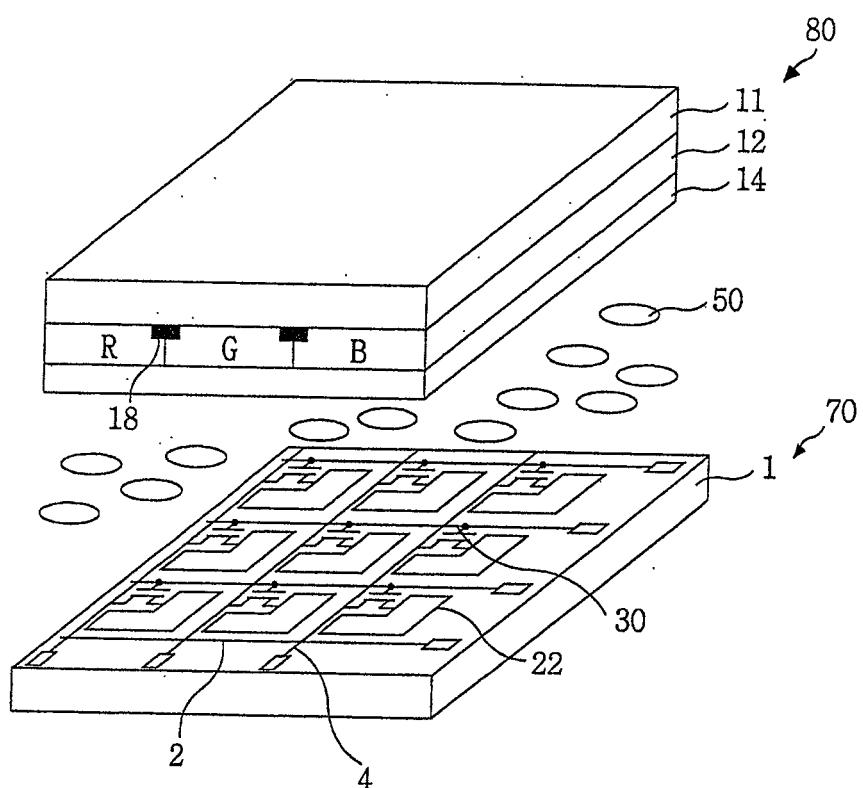

图 1 是表示现有技术的液晶显示器件的平面图；

图 2 是表示用于向图 1 所示的公共电极提供公共电压的银点的平面图；

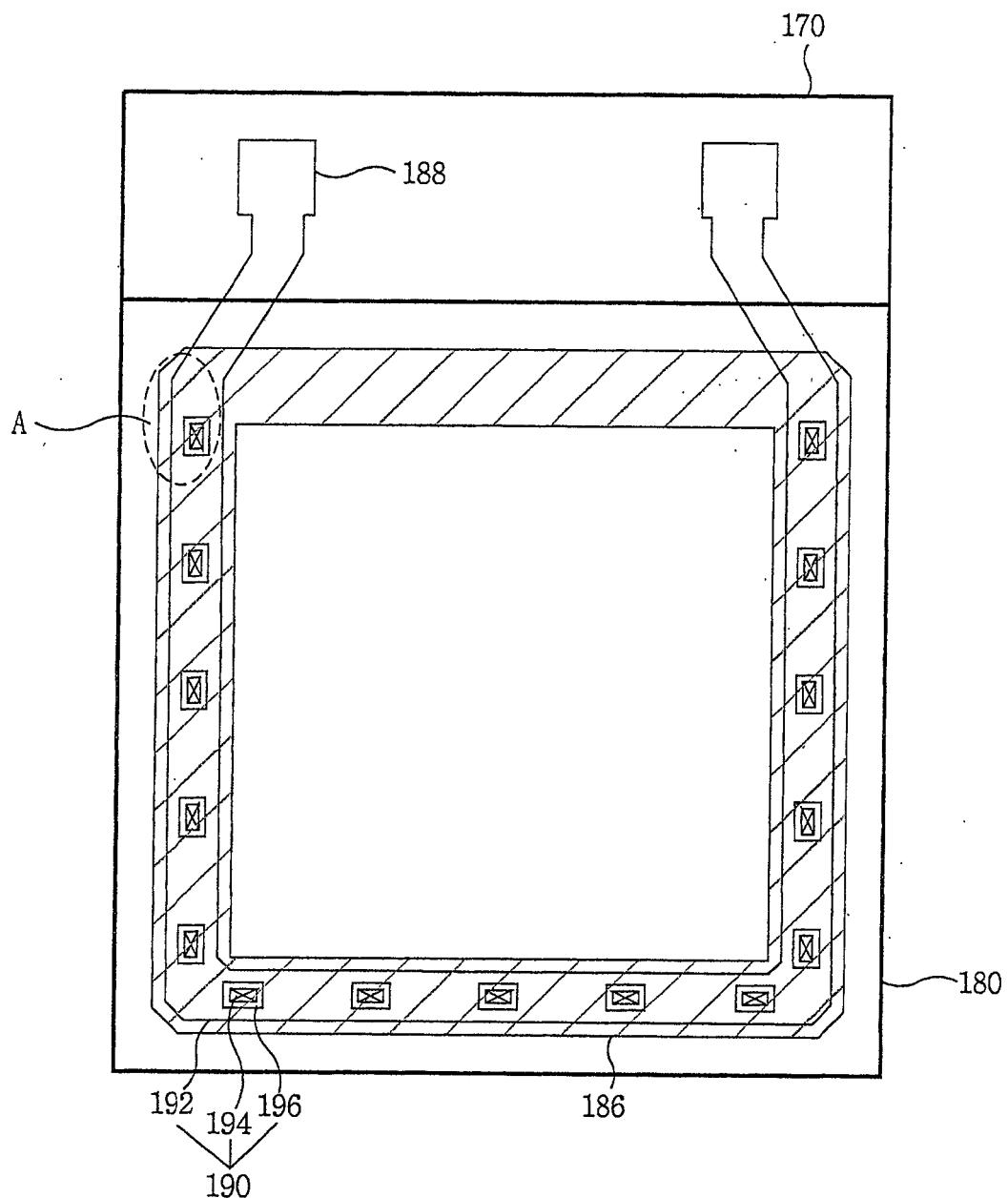

图 3 是表示根据本发明第一实施例的液晶显示器件的平面图；

图 4 是表示图 3 的经放大的 A 区域的平面图；

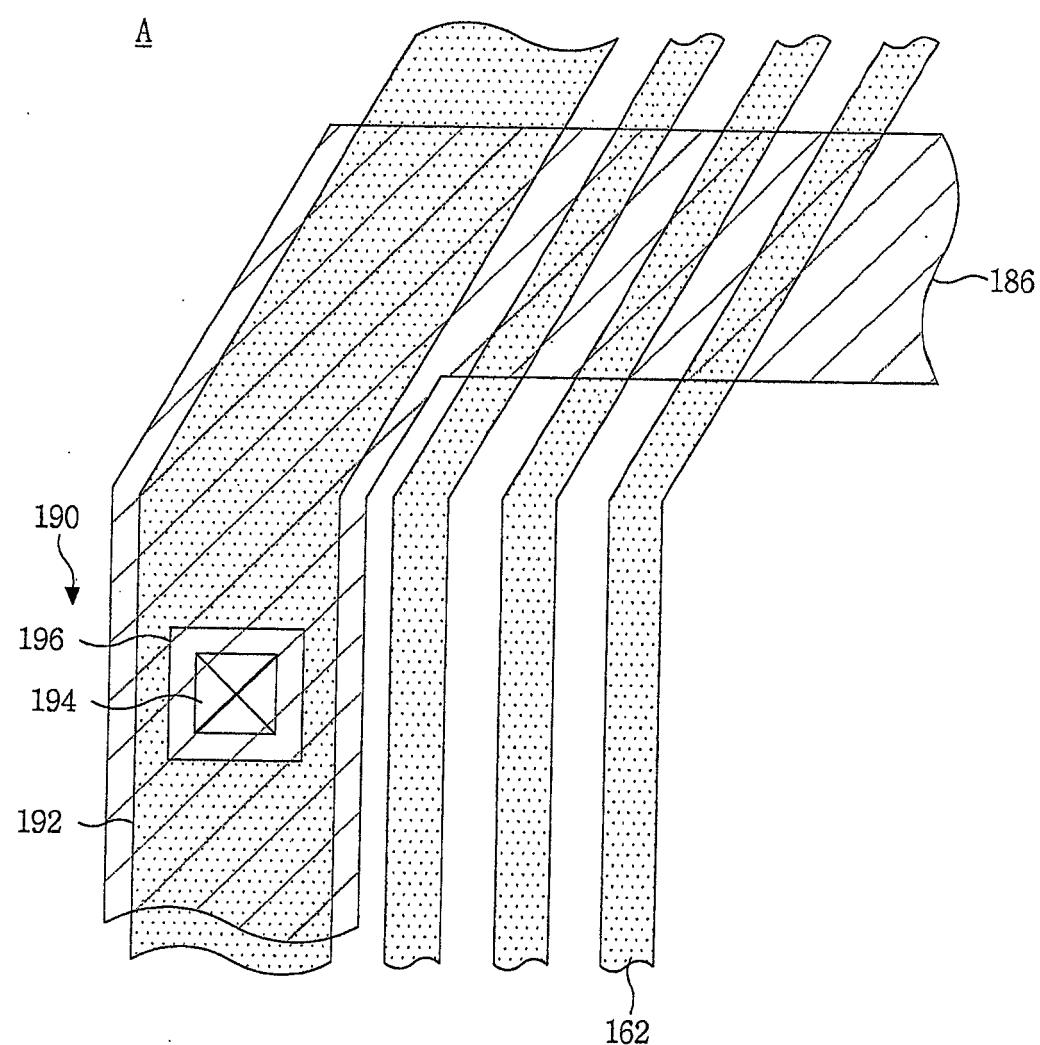

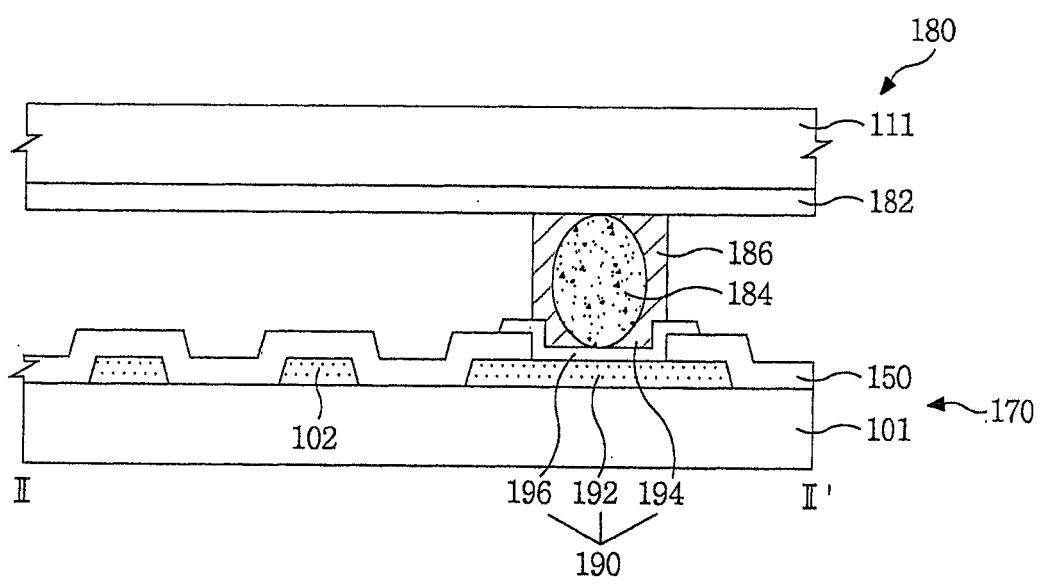

图 5 是表示沿图 4 的线 I-I' 截取的液晶显示器件的剖面图；

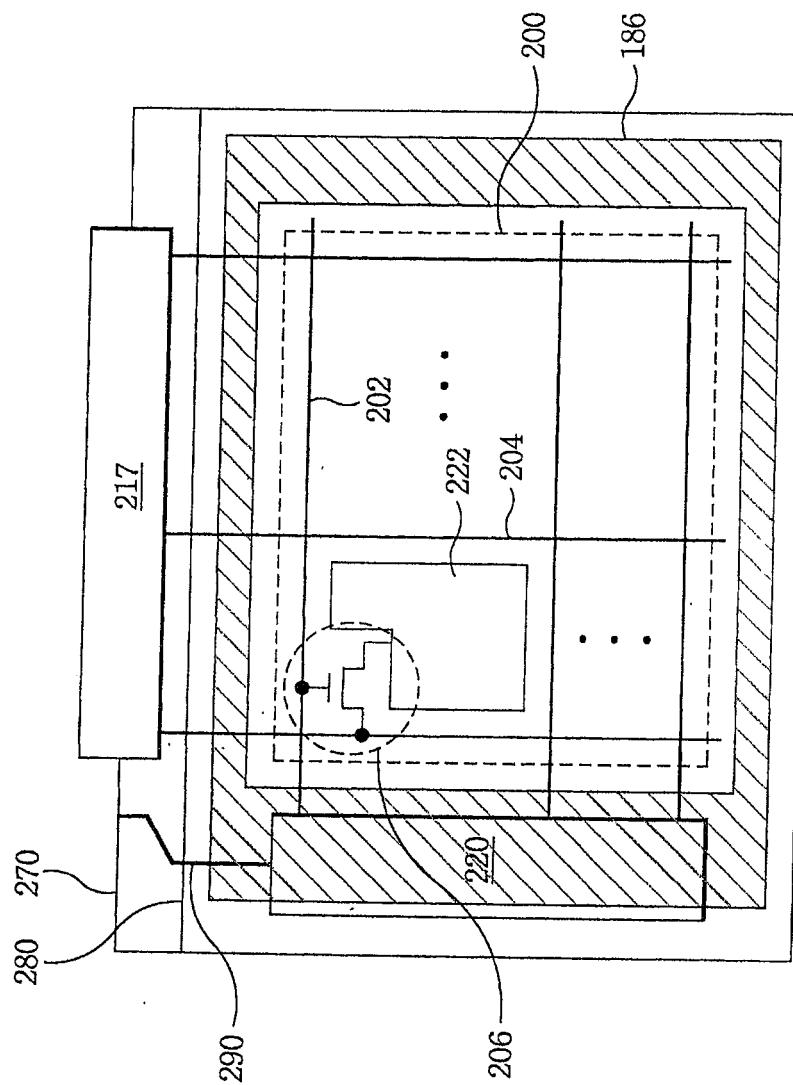

图 6 是表示根据本发明第二实施例的液晶显示器件的视图；

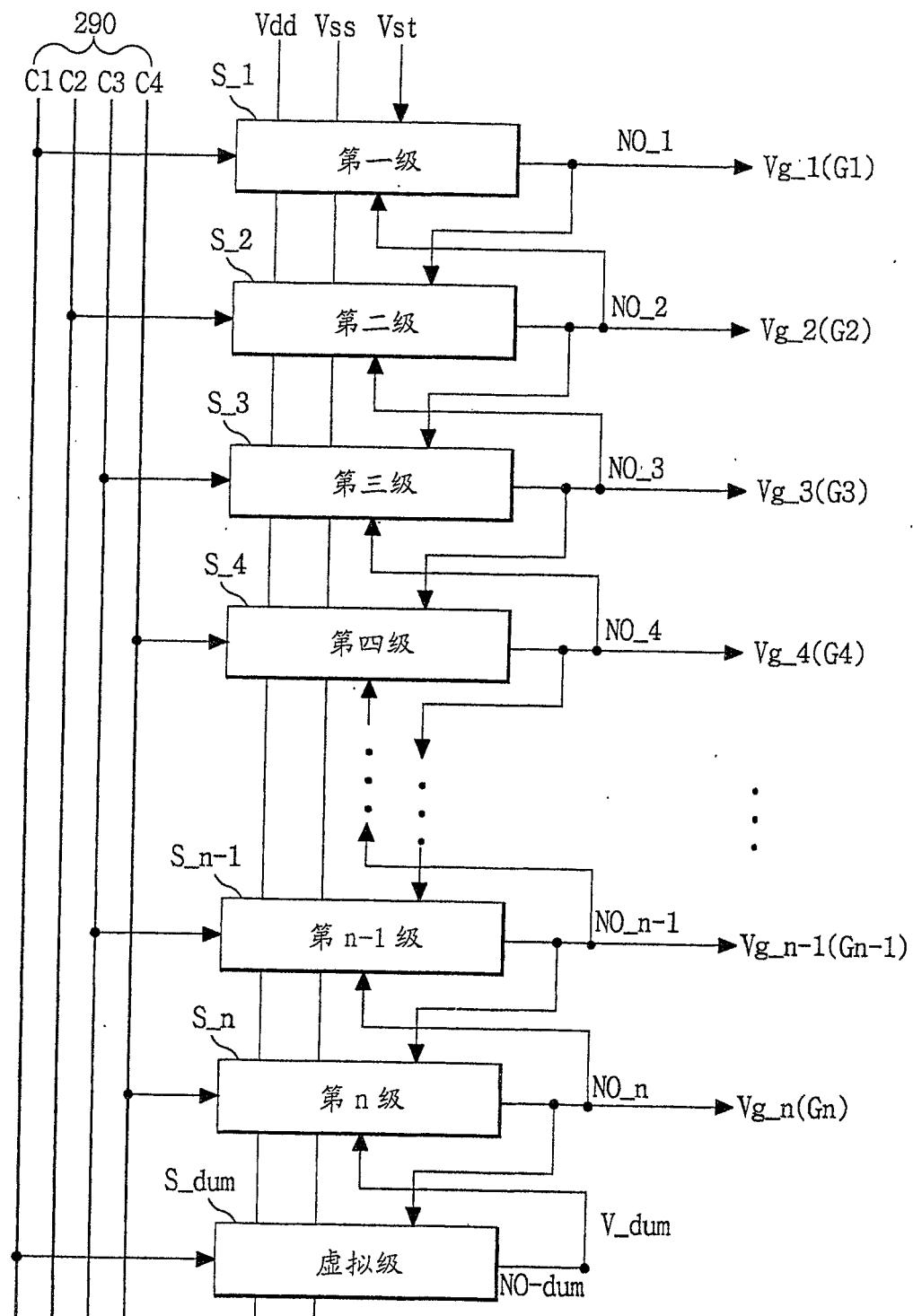

图 7 是用于详细说明图 6 所示的液晶显示器件的选通驱动器的视图；

图 8 是用于说明图 7 所示的级和 LOG 线组的连接关系的视图；

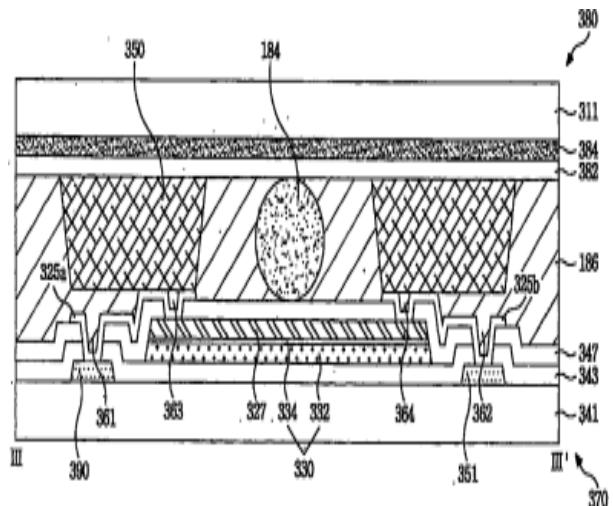

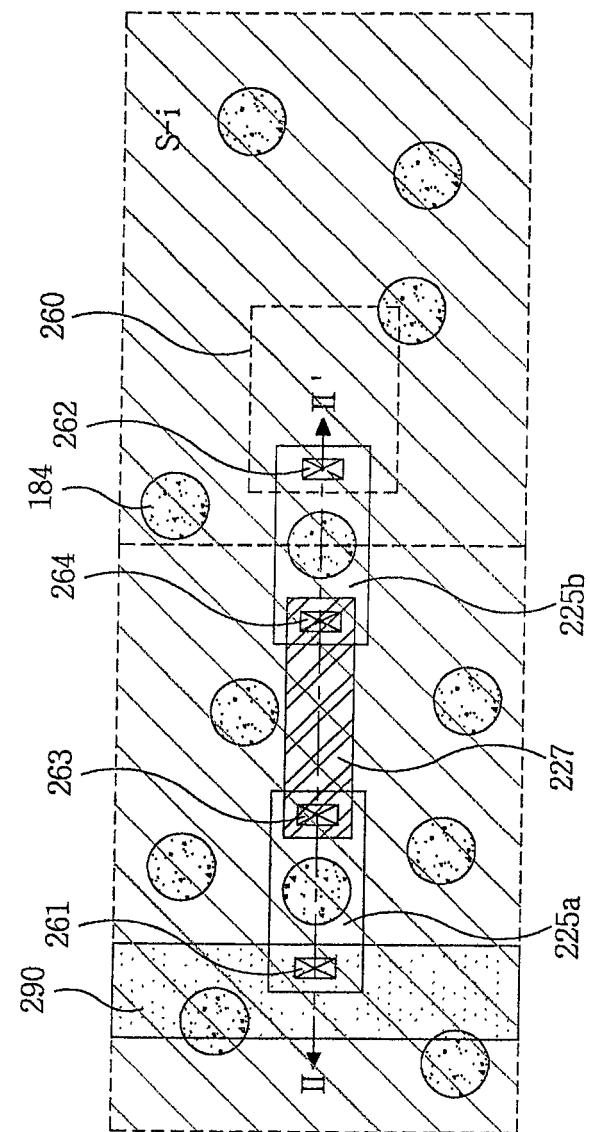

图 9 是沿图 8 所示的线 II-II' 截取的液晶显示器件的剖面图；

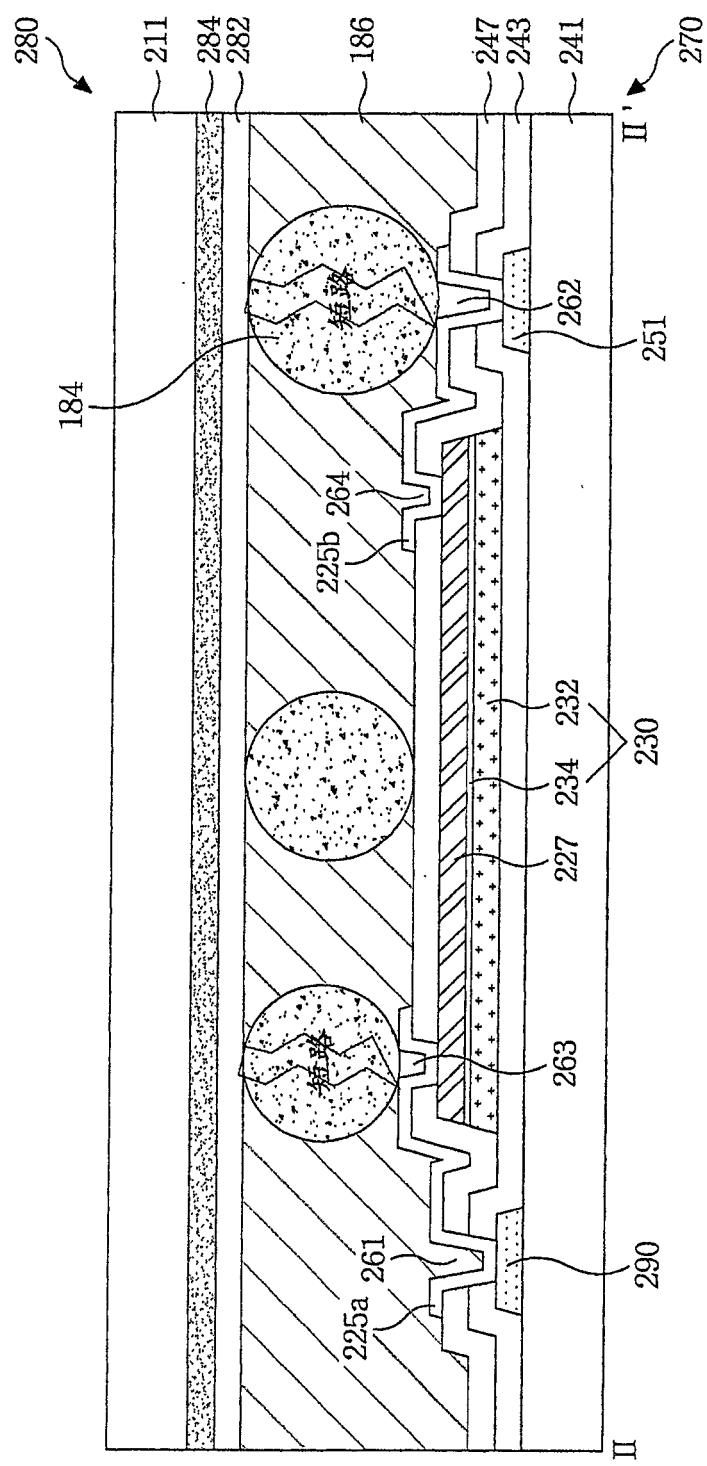

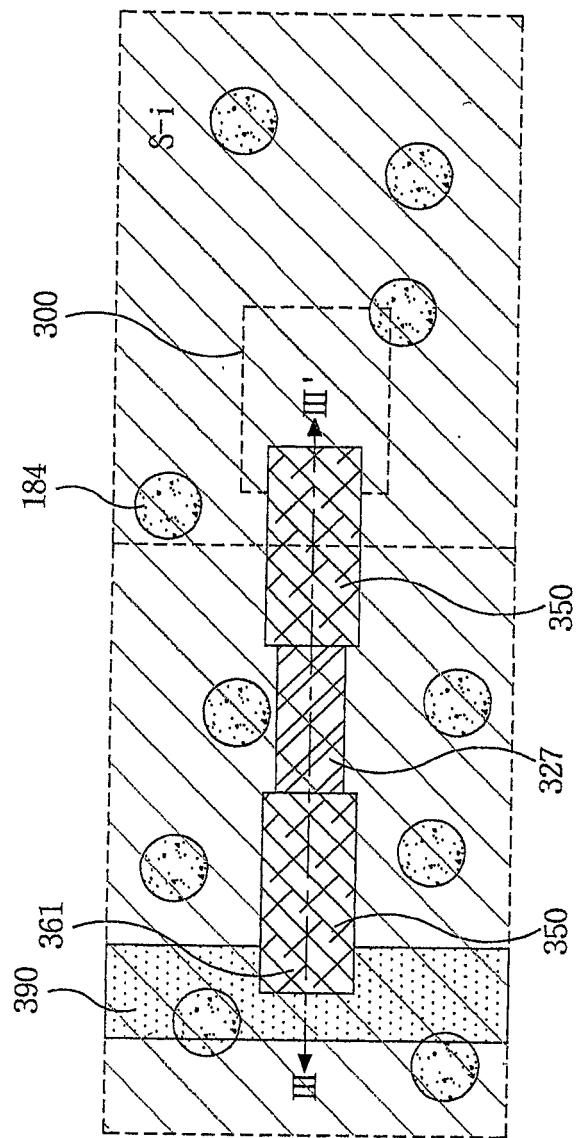

图 10 是表示根据本发明第三实施例的液晶显示器件的视图；

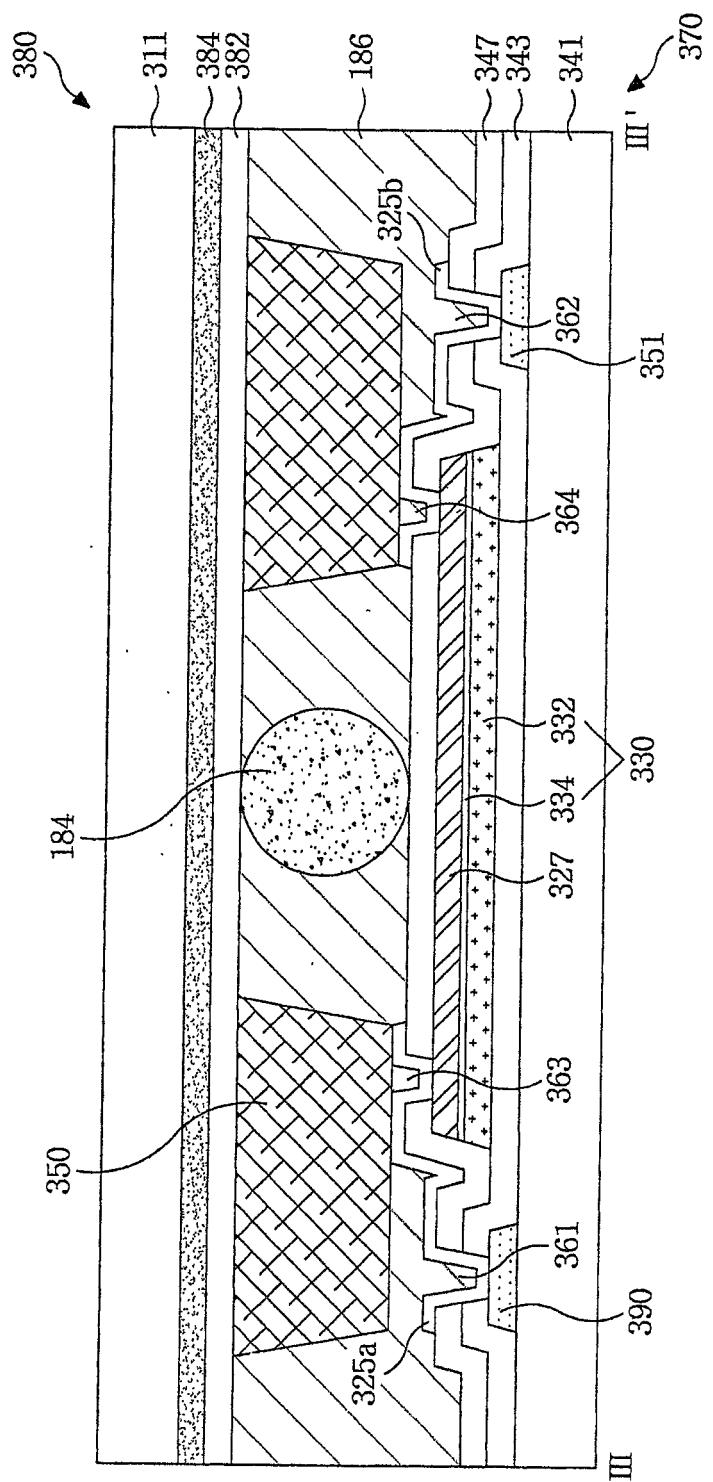

图 11 是沿图 10 所示的线 III-III' 截取的液晶显示器件的剖面图；

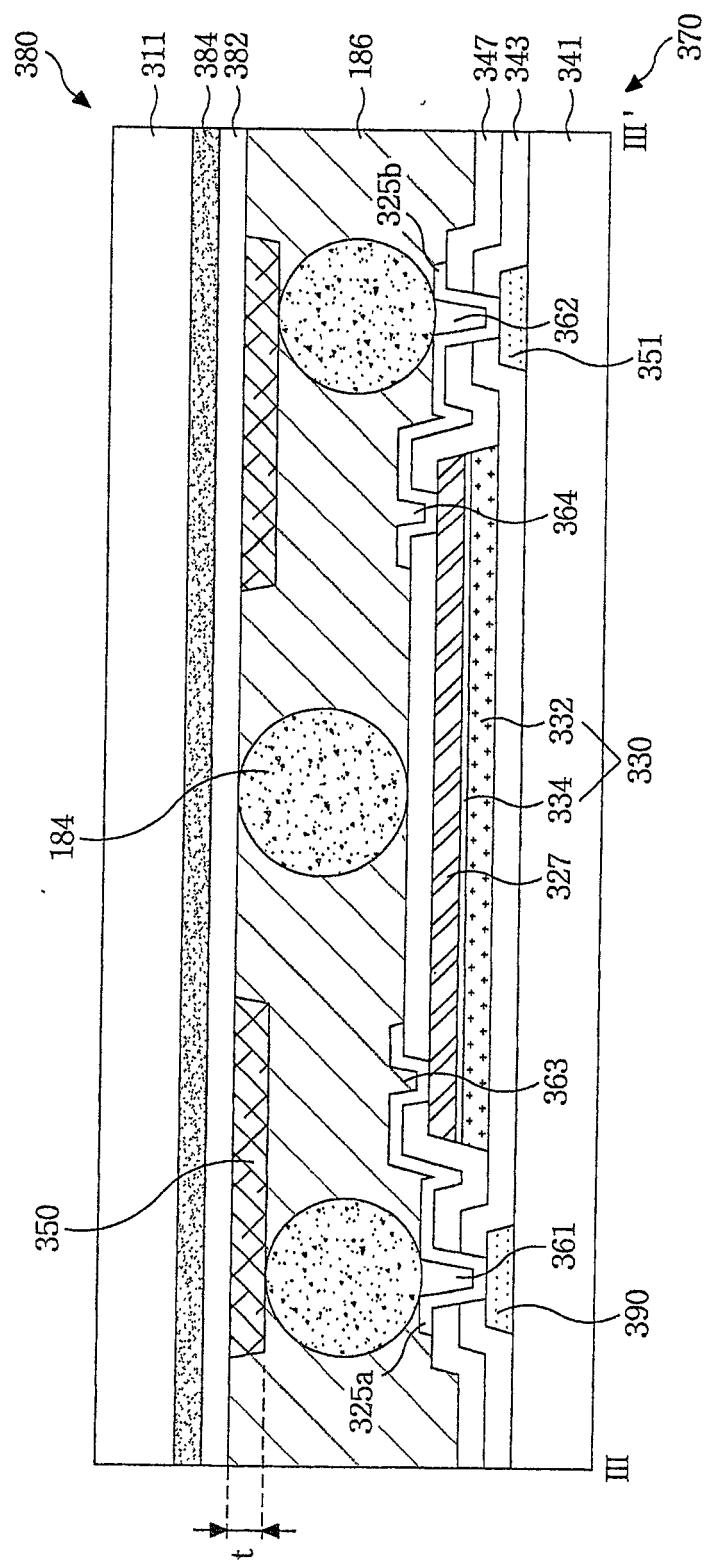

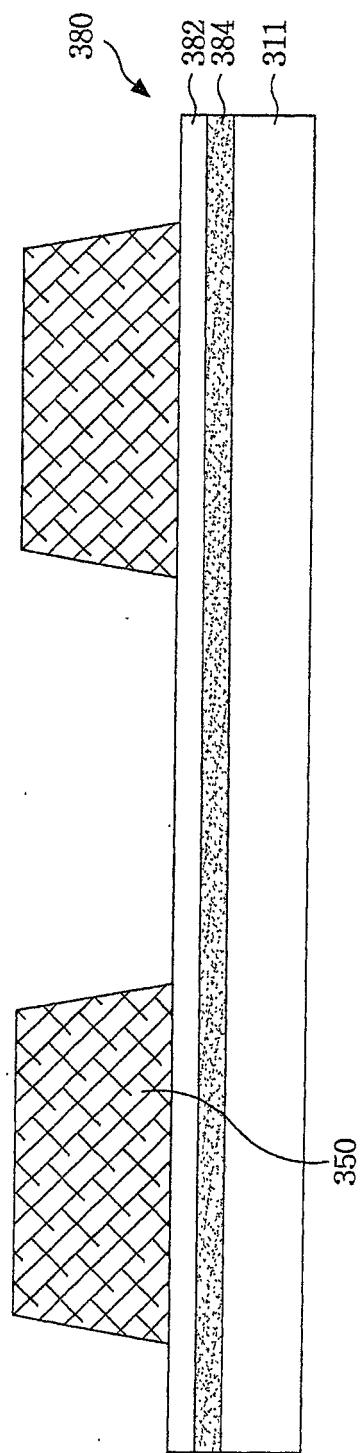

图 12 是沿图 10 所示的线 III-III' 截取的液晶显示器件的另一剖面图；

图 13A 至 13C 是用于说明根据本发明第三实施例的液晶显示器件的滤色器阵列基板的制造工艺的视图。

### 具体实施方式

现对本发明的优选实施例进行详细说明，附图中示出了其示例。

参照图 3 至 13C，如下对本发明的实施例进行说明。

液晶显示器件通过使用电场来控制具有介电各向异性的液晶的透光率，由此显示图像。为此，液晶显示器件包括：液晶显示板，其中以矩阵形式设置有多个液晶单元；以及用于驱动该液晶显示板的驱动器。

在该液晶显示板中，液晶单元根据像素信号来控制透光率，由此显示图像。

该驱动器包括：用于驱动液晶显示板的选通线的选通驱动器；用于驱动数据线的数据驱动器；用于控制选通驱动器和数据驱动器的驱动定时的定时控制器；以及用于提供驱动液晶显示板和驱动器所需的电源信号的电源。

图 3 是表示根据本发明第一实施例的液晶显示板的平面图。

参照图 3，该液晶显示板包括：薄膜晶体管基板 170，其中形成有薄膜晶体管阵列；滤色器基板 180，其中形成有滤色器阵列；以及用于接合薄膜晶体管基板 170 和滤色器基板 180 的导电密封剂 186。

薄膜晶体管阵列基板 170 具有形成在下基板上的薄膜晶体管阵列，并且该薄膜晶体管阵列包括：被形成为彼此交叉的选通线和数据线；形成在其交叉部分处的薄膜晶体管；连接到薄膜晶体管的像素电极；涂覆在其上的用于对准液晶的下配向膜。

滤色器阵列基板 180 具有形成在上基板 111 上的滤色器阵列，该滤色器阵列包括：用于防止光泄漏的黑底；用于实现颜色的滤色器；与像素电极形成垂直电场的公共电极 182；以及涂覆在其上的用于对准液晶的

上配向膜。

在下基板 101 上形成连接部分 190，该连接部分 190 通过导电密封剂 186 连接到公共电极 182，以将公共电压施加给公共电极 182。如图 4 和 5 所示，连接部分 190 包括：沿导电密封剂 186 形成在与导电密封剂 186 重叠的区域中的第一电源图案 192；通过贯穿至少一个层的绝缘膜 150 的电源接触孔连接到第一电源图案 192 的第二电源图案 196；以及用于将第二电源图案 196 与公共电极 182 相连接的导电体 184。在本发明的第一实施例中，导电密封剂 186 包括导电体 184，以具有导电性。

第一电源图案 192 在与连接到选通线的选通连接件 102 相同的平面上由与选通连接件 102 相同的金属形成，因此第一电源图案 192 被形成为与选通连接件隔开指定的间隙。第一电源图案 192 被形成为从连接到电源（未示出）的电源焊盘 188 延伸。

第二电源图案 196 在与像素电极（未示出）相同的平面上由与像素电极相同的材料形成。第二电源图案 196 沿以直线形状形成的第一电源图案 102 以直线形状形成，或以点状形成，以便部分地与第一电源图案 192 重叠。

电源接触孔 194 贯穿包括栅极绝缘膜和钝化膜的绝缘膜 150，以暴露出第一电源图案 192。

使用导电玻璃纤维和导电球中的至少任意一种作为导电体 184。这里，通过使球间隔物的外侧覆盖有银 Ag、金 Au 等的导电材料来形成导电球，以使导电球可以具有导电性并保持高度。即使在与包括在各向异性导电膜 ACF 中的导电球不同的指定压力下，该导电球也可以保持高度。

导电体 184 与导电密封剂 186 混合，以涂覆在基板上。

通过这种方式，本发明的第一实施例包括具有导电体 184 的导电密封剂 186，由此使得能够将公共电压施加给滤色器阵列基板 180 的公共电极，而不需要独立的银打点工艺。在这种情况下，独立的银打点工艺不是必需的，从而简化了该工艺。

图 6 表示了根据本发明第二实施例的液晶显示器件。参照图 6，在根据本发明第二实施例的液晶显示器件中，在面板上安装选通驱动器

220，以与本发明的第一实施例相同的方法使用导电密封剂 186，以接合根据第二实施例的薄膜晶体管阵列基板 270 和滤色器阵列基板 280。此外，导电密封剂 186 以与第一实施例相同的方式包括导电体 184，以具有导电性。通过包括在导电密封剂 186 中的导电体 184 来提供公共电压的路径与本发明第一实施例的相同，因此将省略对其的描述。

在本发明的第二实施例中，将选通驱动器直接安装在面板上的原因在于，保证液晶显示器件的价格竞争能力和简化模块工艺。通过这种方式，如果与形成选通线和数据线一起，将选通驱动器直接安装在面板上，则制造选通驱动器的集成电路和通过 TCP 粘附到面板上的工艺不需是独立的，因此具有下述的优点，即简化了液晶显示器件的工艺并且降低了价格。

根据本发明第二实施例的液晶显示器件包括：薄膜晶体管基板 270，其中形成有薄膜晶体管阵列；滤色器基板 280，其中形成有滤色器阵列；以及用于接合薄膜晶体管基板 270 和滤色器基板 280 的导电密封剂 186。

薄膜晶体管阵列基板 270 具有形成在下基板上的薄膜晶体管阵列，并且该薄膜晶体管阵列包括：被形成为彼此交叉的选通线 202 和数据线 204；形成在其交叉部分处的薄膜晶体管 206；连接到薄膜晶体管 206 的像素电极 222；涂覆在其上的用于对准液晶的下配向膜。如本发明的第一实施例所述，在下基板上形成通过包含在用于将公共电压施加给公共电极（未示出）的导电密封剂 186 中的导电体连接到公共电极（未示出）的连接部分（未示出）。此外，在下基板上形成用于接收来自定时控制器的选通控制信号和来自电源的电源信号的 LOG（玻上线）型线组 290。LOG 型线组 290 是以微小图案形成在下基板上的信号线组，并且与选通驱动器 220 相连。

如图 6 所示，涂覆导电密封剂 186，以包围除了设置有薄膜晶体管 206 的有源阵列区域 200 以外的液晶显示板的外部，并且导电密封剂 186 可以被涂覆为与安装在面板上的选通驱动器 220 重叠。

为了参照图 7 详细描述图 6 所示的选通驱动器 220，选通驱动器 220 由多个选通驱动 IC 构成，每一个驱动 IC 都包括：移位寄存器，该移位寄存器对于每一个水平周期都依次使起始脉冲移位以产生扫描脉冲；电

平移位器，用于将移位寄存器的输出信号转换为适合于驱动液晶单元的摆动（swing）宽度；以及输出缓冲器，其连接在电平移位器和选通线 G<sub>1</sub> 至 G<sub>n</sub> 之间。选通驱动器 220 向选通线 G<sub>1</sub> 至 G<sub>n</sub> 依次提供扫描脉冲，以选择液晶显示板的被提供了数据的水平线。

图 7 是选通驱动器 220 的移位寄存器电路构造的示例，该移位寄存器包括串联连接的 n 级 S<sub>\_1</sub> 至 S<sub>\_n</sub> 和虚拟级 S<sub>\_dum</sub>。输出缓冲器和电平移位器（未示出）安装在级 S<sub>\_1</sub> 至 S<sub>\_n</sub> 和选通线 G<sub>1</sub> 至 G<sub>n</sub> 之间。

在该移位寄存器中，作为起始脉冲的起始脉冲 V<sub>st</sub> 被输入到第一级 S<sub>\_1</sub>，而作为起始信号的前级输出信号 V<sub>g\_1</sub> 至 V<sub>g\_{n-1}</sub> 被输入到第二至第 n 级 S<sub>\_2</sub> 至 S<sub>\_n</sub>。并且，作为复位信号的下一级输出信号 V<sub>g\_2</sub> 至 V<sub>g\_n</sub> 被输入到第一至第 (n-1) 级 S<sub>\_1</sub> 至 S<sub>\_n-1</sub>，而作为复位信号的虚拟级的输出信号 V<sub>\_dum</sub> 被输入到第 n 级。

此外，级 S<sub>\_1</sub> 至 S<sub>\_n</sub> 中的每一级都具有相同的电路构造，并且响应于通过 LOG 线组 290 施加的四个时钟信号 C<sub>1</sub> 至 C<sub>4</sub> 当中的任意一个时钟信号，对起始脉冲 V<sub>st</sub> 或前级输出信号 V<sub>g\_1</sub> 至 V<sub>g\_{n-1}</sub> 进行移位，由此产生具有一个水平周期的脉冲的扫描脉冲。

级 S<sub>\_1</sub> 至 S<sub>\_n</sub> 的电路构造和时钟信号的数量可以按照不同的方式进行设计。

此外，各个级 S<sub>\_1</sub> 至 S<sub>\_n</sub> 都包括多个薄膜晶体管，并且响应于前级的起始脉冲或输出信号以及时钟信号而向选通线依次提供扫描脉冲。

包括在各个级 S<sub>\_1</sub> 至 S<sub>\_n</sub> 中的薄膜晶体管的数量和形状可以根据设计方法而不同地形成。

此外，形成在级 S<sub>\_1</sub> 至 S<sub>\_n</sub> 内的薄膜晶体管包括栅极、源极和漏极。

形成在各个级 S<sub>\_1</sub> 至 S<sub>\_n</sub> 中的薄膜晶体管的栅极、源极和漏极中的任意一个与提供时钟信号的 LOG 线组 290 相连，由此向各个级 S<sub>\_1</sub> 至 S<sub>\_n</sub> 提供时钟信号。

图 8 是图 6 所示的液晶显示器件的部分区域，并且该部分区域表示图 7 所示的移位寄存器中的第 i 级 S<sub>\_i</sub> (i 是小于或等于 n 的正整数) 以及与第 i 级 S<sub>\_i</sub> 相连的 LOG 线组 290。

图 9 表示沿图 8 所示的线 II-II' 截取的剖面图。

参照图 8 和 9，根据本发明第二实施例的薄膜晶体管阵列基板 270 包括下基板 241 上的第 i 级 S\_i 和 LOG 线组 290。

LOG 线组 290 包括多条信号线，这些信号线提供：电源信号，例如选通低压 VGL、选通高压 VGH、公共电压 VCOM、地电压 GND 和基本驱动电压 VCC；以及选通控制信号，例如选通起始脉冲 GSP、选通移位时钟信号 GSC 以及选通使能信号 GOE。

第 i 级 S\_i 与 LOG 线组 290 中的任意一个相连并且由多个薄膜晶体管 260 构成，该多个薄膜晶体管 260 向选通线提供电源信号 VGL、VGH、VCOM、GND、VCC 和选通控制信号 GSP、GSC、GOE。通过这种方式，可以根据第 i 级 S\_i 的电路构造以不同的方式形成构成第 i 级 S\_i 的薄膜晶体管 260。因此，根据第 i 级 S\_i 的电路结构，LOG 线组 290 中的任意一个与包括在第 i 级 S\_i 中的薄膜晶体管 260 的栅极、源极、漏极中的任意一个相连。

LOG 线组 290 与薄膜晶体管 260 的连接可以通过第一连接图案 225A 和第二连接图案 225B 来进行。

作为示例，图 9 示出了薄膜晶体管 260 的栅极 251 与 LOG 线组 290 的连接。

为了详细描述栅极 251 和 LOG 线组 290 的连接关系，LOG 线组 290 由下基板 241 上的栅极金属形成，而栅极 251 由下基板 241 上的栅极金属形成，并与 LOG 线组 290 分离。

LOG 线组 290 和栅极 251 通过栅极绝缘膜 243 而绝缘，并且在栅极绝缘膜 243 上形成有附加连接图案 227。在附加连接图案 227 和栅极绝缘膜 243 上形成用于从外部保护该附加连接图案 227 的钝化膜 247。此外，在薄膜晶体管阵列基板 270 中形成贯穿栅极绝缘膜 243 和钝化膜 247 中的至少任意一个的第一至第四接触孔 261、262、263、264。包括有源层 232 和欧姆接触层 234 的半导体图案 230 可以重叠在附加连接图案 227 的下面。

并且，第一和第三接触孔 261、263 被第一连接图案 225A 覆盖，而

第二和第四接触孔 262、264 被第二连接图案 225B 覆盖。

另一方面，第一接触孔 261 暴露出 LOG 线组 290，第三和第四接触孔 263、264 暴露出附加连接图案 227，而第二接触孔 262 暴露出栅极 251。因此，LOG 线组 290 通过第一和第三接触孔 261、263 以及第一连接图案 225A 连接到附加连接图案 227，而栅极 251 通过第二和第四接触孔 262、264 以及第二连接图案 225B 连接到附加连接图案 227。由此，通过第一连接图案 225A→附加连接图案 227→第二连接图案 225B 将通过 LOG 线组 290 提供的信号传送到第 i 级 S\_i 的栅极 251。

即使没有附加连接图案 227 以及第三和第四接触孔 263、264，LOG 线组 290 和栅极 251，也可以通过覆盖第一接触孔 261 和第二接触孔 264 的一条线的连接图案进行连接。但是，第一和第二连接图案 225A、225B 由电阻较高的透明导电金属（即 ITO 等）形成，并且该电阻与该金属的长度成正比。由此，在独立地形成第一和第二连接图案 225A、225B 的情况下，构成连接图案的金属的长度变得比在连接图案被形成为一条线的情况下更短，因此连接图案的电阻减小，从而可以更稳定地传送信号。

根据上述第二实施例的接合到薄膜晶体管阵列基板 270 上的滤色器阵列基板 280 在上基板 211 上具有：用于防止光泄漏的黑底 284；以及用于接收公共电压的公共电极 282。

并且，通过导电密封剂 186 接合滤色器阵列基板 280 和薄膜晶体管阵列基板 270。导电密封剂 186 包括导电体 184，因此在滤色器阵列基板 280 的公共电极 282 和薄膜晶体管阵列基板 270 的连接图案 225A、225B 之间可能产生短路。

但是，在通过连接图案 225A、225B 提供公共电压的情况下产生的短路用于向滤色器阵列基板 280 的公共电极 282 提供公共电压，由此在驱动液晶显示器件时不会引起问题。

根据本发明第三实施例的液晶显示器件具有以与本发明第二实施例相同的方式安装在面板上的驱动器，并且以与本发明第一实施例相同的方式使用导电密封剂 186，以接合滤色器阵列基板 380 和薄膜晶体管阵列基板 370。通过导电密封剂 186 提供公共电压的路径与本发明第一实施例

中的相同，因此将省略对其的描述。

图 10 是表示根据本发明第三实施例的液晶显示器件的视图，而图 11 是沿图 10 所示的线 III-III' 截取的液晶显示器件的剖面图。

图 10 和 11 所示的液晶显示器件的部分区域表示移位寄存器中的第 i 级 S\_i (i 是小于或等于 n 的正整数) 和连接到第 i 级 S\_i 的 LOG 线组 390。

图 11 表示沿图 10 所示的线 III-III' 截取的剖面。

参照图 10 和 11，根据本发明第三实施例的薄膜晶体管阵列基板 370 包括下基板 341 上的第 i 级 S\_i 和 LOG 线组 390。

LOG 线组 390 包括多条信号线，这些信号线提供：电源信号，例如选通低压 VGL、选通高压 VGH、公共电压 VCOM、地电压 GND 和基本驱动电压 VCC；以及选通控制信号，例如选通起始脉冲 GSP，选通移位时钟信号 GSC 和选通使能信号 GOE。

第 i 级 S\_i 与 LOG 线组 390 中的任意一个相连，并且由多个薄膜晶体管 300 构成，该多个薄膜晶体管 300 向选通线提供电源信号 VGL、VGH、VCOM、GND、VCC 和选通控制信号 GSP、GSC、GOE。通过这种方式，可以根据第 i 级 S\_i 的电路构造以不同的方式来形成构成第 i 级 S\_i 的薄膜晶体管 300。因此，根据第 i 级 S\_i 的电路构造，LOG 线组 390 中的任意一个与包括在第 i 级 S\_i 中的薄膜晶体管 300 的栅极、源极、漏极中的任意一个相连。

LOG 线组 390 和薄膜晶体管 300 的连接可以通过第一连接图案 325A 和第二连接图案 325B 来进行。

图 11 示出了薄膜晶体管 300 的栅极 351 和 LOG 组 390 的连接作为示例。

为了详细描述栅极 351 和 LOG 线组 390 的连接关系，LOG 线组 390 由下基板 341 上的栅极金属形成，而栅极 351 由下基板 341 上的栅极金属形成，并与 LOG 线组 390 分离。

LOG 线组 390 和栅极 351 通过栅极绝缘膜 343 绝缘，并且在栅极绝缘膜 343 上形成有附加连接图案 327。在附加连接图案 327 和栅极绝缘膜

343 上形成用于从外部保护附加连接图案 327 的钝化膜 347。此外，在薄膜晶体管阵列基板 370 中形成贯穿栅极绝缘膜 343 和钝化膜 347 中的至少任意一个的第一至第四接触孔 361、362、363、364。包括有源层 332 和欧姆接触层 334 的半导体图案 330 可以重叠在附加连接图案 327 的下面。

并且，第一和第三接触孔 361、363 被第一连接图案 325A 覆盖，而第二和第四接触孔 362、364 被第二连接图案 325B 覆盖。

另一方面，第一接触孔 361 暴露出 LOG 线组 390，第三和第四接触孔 363、364 露出附加连接图案 327，而第二接触孔 362 暴露出栅极 351。因此，LOG 线组 390 通过第一和第三接触孔 361、363 以及第一连接图案 325A 连接到附加连接图案 327，而栅极 351 通过第二和第四接触孔 362、364 以及第二连接图案 325B 连接到附加连接图案 327。由此，通过第一连接图案 325A→附加连接图案 327→第二连接图案 325B 将通过 LOG 线组 390 提供的信号传送到第 i 级 S\_i 的栅极 351。

即使没有附加连接图案 327 和第三和第四接触孔 363、364，LOG 线组 390 和栅极 351 也可以通过覆盖第一接触孔 361 和第二接触孔 364 的一条线的连接图案进行连接。但是，第一和第二连接图案 325A、325B 由电阻较高的透明导电金属（即 ITO 等）形成，并且该电阻与该金属的长度成正比。由此，在独立地形成第一和第二连接图案 325A、325B 的情况下，构成连接图案的金属的长度变得比在连接图案被形成为一条线的情况下更短，因此连接图案的电阻减小，从而可以更稳定地传送信号。

根据上述第三实施例的接合到薄膜晶体管阵列基板 370 上的滤色器阵列基板 380 在上基板 311 上具有：用于防止光泄漏的黑底 384；以及用于接收公共电压的公共电极 382。此外，滤色器阵列基板 380 在与薄膜晶体管阵列基板 270 的第一和第二连接图案 325A、325B 相对应的区域中还包括绝缘图案 350。绝缘图案 350 防止在滤色器阵列基板 380 的公共电极 382 和薄膜晶体管阵列基板 370 的连接图案 325A、325B 之间产生短路的现象。

为了完全地描述防止短路现象的绝缘图案 350，当通过导电密封剂

186 接合滤色器阵列基板 380 和薄膜晶体管阵列基板 370 时，在公共电极 382 和连接图案 325A、325B 之间设置由绝缘材料形成的绝缘图案 350，因此公共电极 382 与连接图案 325A、325B 电绝缘。通过这种方式，公共电极 382 和连接图案 325A、325B 被绝缘，因此可以使液晶显示器件的制造工艺稳定。

此外，如图 12 所示，绝缘图案 350 的厚度 ( $t_1$ ) 可以被形成为不大于间隔物的厚度，该间隔物被形成用来保持滤色器阵列基板 380 和薄膜晶体管阵列基板 370 之间的单元间隙。也就是说，绝缘图案 350 的厚度 ( $t_1$ ) 可以被形成为小于单元间隙。即使绝缘图案 350 的厚度 ( $t_1$ ) 被形成为小于单元间隙，公共电极 282 也可以通过绝缘图案 350 与导电间隔物 184 绝缘。由此，其与绝缘图案 350 的厚度 ( $t_1$ ) 被形成为不大于单元间隙的事实不相关。

并且，绝缘图案 350 可以形成在薄膜晶体管阵列基板 370 的连接图案 325A、325B 以及滤色器阵列基板 380 上。

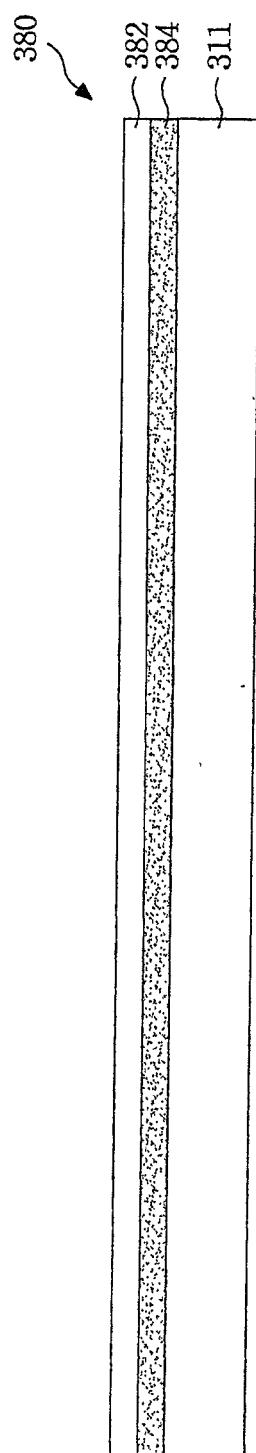

图 13A 至 13C 是用于说明根据图 11 和 12 所示的本发明第三实施例的滤色器阵列基板 380 的制造方法的视图。

参照图 13，在上基板 311 上形成用于防止光泄漏的黑底 384。

在淀积不透明金属材料或不透明树脂之后，通过利用刻蚀工艺以及使用掩模的光刻工艺对该不透明金属材料或不透明树脂进行构图来形成黑底 384。

参照图 13B，在形成有黑底的上基板 311 上形成用于控制液晶的移动的公共电极 382。

通过淀积透明导电材料（例如 ITO）来形成公共电极 382。

此外，在形成有黑底的上基板 311 上形成红色、绿色和蓝色滤色器阵列之后，在有源阵列区域（未示出）中形成公共电极 382。

参照图 13C，在形成有公共电极 382 的上基板 311 上形成用于防止滤色器阵列基板 380 和薄膜晶体管阵列基板 370 的短路的绝缘图案 350。

在整个表面上涂覆包括聚丙烯酸酯等的有机绝缘材料之后，通过刻蚀工艺和使用掩模的光刻工艺来形成绝缘图案 350。此外，绝缘图案 350

可以与间隔物一起形成，该间隔物形成在有源阵列区域中，用于保持液晶显示器件的单元间隙。

采用衍射曝光掩模或半色调掩模，以便形成厚度小于被形成用来保持单元间隙的间隔物的绝缘图案 350。

通过采用衍射曝光掩模和半色调掩模来形成高度低于间隔物的绝缘图案的方法如下。可以通过采用衍射曝光掩模和半色调掩模来形成第一高度和第二高度的光刻胶图案，该第二高度低于该第一高度。在与第一高度的光刻胶图案相对应的区域中形成间隔物，并且在与第一高度的光刻胶图案相对应的区域中形成绝缘图案。为了完全地描述形成间隔物和绝缘图案的工艺，使用第一和第二光刻胶图案对聚丙烯酸酯进行蚀刻。然后，对第一和第二高度的光刻胶图案进行灰化，由此去除第二高度的光刻胶图案。由于去除了第二高度的光刻胶图案，所以暴露出了在第二高度的光刻胶图案的下部中的聚丙烯酸酯，并且对所暴露出的聚丙烯酸酯部分地进行蚀刻，以形成绝缘图案。并且，在形成绝缘图案之后，通过剥离工艺去除通过灰化工艺减小了高度的第一高度的光刻胶图案，由此完成所有间隔物和高度低于间隔物的绝缘图案。

通过图 13A 至 13C 所示的方法设置滤色器阵列基板 380，并且设置根据本发明第三实施例的薄膜晶体管阵列基板 370，然后通过涂覆导电密封剂 186 来接合滤色器阵列基板 380 和薄膜晶体管阵列基板 370。

如上所述，根据本发明第一实施例的液晶显示器件通过包括导电体的导电密封剂将公共电极连接到公共线，因此可以施加公共电压，而不需要银打点工艺，从而可以简化该工艺。

此外，根据本发明第二实施例的液晶显示器件使用导电密封剂，并且将选通驱动器安装在面板上，从而其不需要单独地制造选通驱动器的集成电路以及通过 TCP 将该集成电路粘合到面板部分上，因此具有简化了液晶显示器件的工艺以及降低了价格的优点。

并且，根据本发明第三实施例的液晶显示器件使用导电密封剂，将选通驱动器安装在面板上，并且在与选通驱动器相对的滤色器阵列基板中具有绝缘图案，以使得可以防止滤色器阵列基板和液晶显示器件的驱

---

动器之间的短路现象。通过防止该短路现象可以使液晶显示器件的制造工艺稳定。

尽管通过上述附图中所示的实施例对本发明进行了说明，但是所属领域的技术人员应该理解，本发明不限于这些实施例，而是在不脱离本发明的精神的情况下可以对其进行各种变化或修改。因此，本发明的范围应该仅由所附权利要求及其等效物来确定。

本申请要求 2005 年 12 月 20 日提交的韩国专利申请 No. P2005-0126256 的优先权，在此通过引用将其并入。

图 1

现有技术

图 2

现有技术

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

图 12

图 13A

图 13B

图 13C

|                |                                                   |         |            |

|----------------|---------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器件及其制造方法                                      |         |            |

| 公开(公告)号        | <a href="#">CN100535714C</a>                      | 公开(公告)日 | 2009-09-02 |

| 申请号            | CN200610087803.0                                  | 申请日     | 2006-06-09 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                          |         |            |

| 申请(专利权)人(译)    | LG. 菲利浦LCD株式会社                                    |         |            |

| 当前申请(专利权)人(译)  | 乐金显示有限公司                                          |         |            |

| [标]发明人         | 李建熙<br>朴星一                                        |         |            |

| 发明人            | 李建熙<br>朴星一                                        |         |            |

| IPC分类号         | G02F1/133 G09G3/36 G02F1/1333 G02F1/136 H01L27/00 |         |            |

| CPC分类号         | G02F1/13454 G02F1/1339 G09G3/3677                 |         |            |

| 代理人(译)         | 李辉                                                |         |            |

| 审查员(译)         | 彭志红                                               |         |            |

| 优先权            | 1020050126256 2005-12-20 KR                       |         |            |

| 其他公开文献         | CN1987573A                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>    |         |            |

#### 摘要(译)

本发明涉及一种适于减小其上安装有驱动电路的液晶显示器件的处理时间和防止滤色器阵列基板的公共电极和薄膜晶体管阵列基板的驱动电路之间的短路的液晶显示器件及其制造方法。根据本发明实施例的液晶显示器件包括：形成在上基板上的公共电极；形成在与上基板相对的下基板上的选通驱动器；形成在与选通驱动器相对的公共电极上的绝缘图案；以及用于接合上基板和下基板的导电密封剂。