# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(43) 공개일자 2009년08월07일

(51) Int. Cl.

**GO2F 1/136** (2006.01)

(21) 출원번호10-2008-0011028(22) 출원일자2008년02월04일

심사청구일자 없음

(71) 출원인

(11) 공개번호

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

박기범

충남 천안시 두정동 561-7번지 307호

김동규

경기 용인시 풍덕천2동 삼성5차아파트 523동 130 5호

10-2009-0085235

(74) 대리인

특허법인가산

전체 청구항 수 : 총 21 항

#### (54) 박막 트랜지스터 및 이를 구비하는 표시 장치

#### (57) 요 약

본 발명은 박막 트랜지스터 및 이를 구비하는 표시 장치에 관한 것이다.

본 발명에 따른 일 박막 트랜지스터는 복수의 돌출부와 돌출부 사이의 공간부를 포함하는 핑거 구조로 소오스 전 극 및 드레인 전극을 형성하고, 소오스 전극 및 드레인 전극의 돌출부를 대응하는 전극의 공간부에 형성하여 게이트-드레인간 캐패시턴스(Cgd)와 게이트-소오스간 캐패시턴스(Cgs)의 비율이 1:1이 되도록 U-타입으로 형성한다.

그리고, 본 발명에 따른 타 박막 트랜지스터는 U-타입으로 복수의 부유 전극을 형성하고, 일 부유 전극 및 타 부유 전극의 공간부에 소오스 전극 및 드레인 전극을 형성하여 채널 폭을 크게 형성하여 충분한 저항을 갖도록 한다.

본 발명에 의하면 액정 표시 패널의 표시부와 주변부의 박막 트랜지스터를 동일하게 U-타입으로 형성할 수 있어 종래의 I-타입으로 주변부의 박막 트랜지스터를 형성할 때 발생되는 주변부의 박막 트랜지스터의 활성층이 과도 하게 제거되는 것을 방지할 수 있어 주변부의 박막 트랜지스터의 오동작을 방지할 수 있으며, 표시부 및 주변부 박막 트랜지스터의 패터닝 균일도 유지에 유리하다.

## 대 표 도 - 도4

#### 특허청구의 범위

#### 청구항 1

게이트 전극;

상기 게이트 전극 상에 형성된 절연막 및 활성층;

상기 활성층 상에 각각 형성되며, 복수의 돌출부와 돌출부 사이의 공간부를 각각 갖는 소오스 전극 및 드레인 전극을 포함하며.

상기 소오스 전극 및 드레인 전극의 돌출부가 대응하는 전극의 상기 공간부에 서로 이격되어 형성된 박막 트랜 지스터.

#### 청구항 2

제 1 항에 있어서, 상기 게이트 전극과 소오스 전극의 중첩 면적 및 상기 게이트 전극과 상기 드레인 전극의 중첩 면적이 동일한 박막 트랜지스터.

#### 청구항 3

제 2 항에 있어서, 상기 소오스 전극 및 드레인 전극은 동일 면적 및 동일 형상으로 형성된 박막 트랜지스터.

#### 청구항 4

제 1 항에 있어서, 상기 소오스 전극은 일 방향으로 형성된 평면부;

상기 평면부로부터 일 방향으로 연장되며, 서로 이격된 복수의 돌출부; 및

상기 평면부 및 상기 복수의 돌출부에 의해 일 방향이 개방된 복수의 공간부를 포함하는 박막 트랜지스터.

#### 청구항 5

제 4 항에 있어서, 상기 드레인 전극은 일 방향으로 형성된 평면부;

상기 평면부로부터 타 방향으로 연장되며, 서로 이격된 복수의 돌출부; 및

상기 평면부 및 상기 복수의 돌출부에 의해 타 방향이 개방된 복수의 공간부를 포함하는 박막 트랜지스터.

#### 청구항 6

제 5 항에 있어서, 상기 소오스 전극의 돌출부와 상기 드레인 전극의 돌출부 사이의 채널은 2.0 내지 2.5µm의 길이를 갖는 박막 트랜지스터.

#### 청구항 7

게이트 전극;

상기 게이트 전극 상에 형성된 절연막 및 활성층;

상기 활성층 상에 각각 형성되며, 일 방향이 개방되어 형성된 복수의 부유 전극; 및

상기 게이트 전극과 중첩되어 외곽 부유 전극의 개방된 공간부로 형성된 소오스 전극 및 드레인 전극을 포함하는 박막 트랜지스터.

#### 청구항 8

제 7 항에 있어서, 상기 소오스 전극 및 드레인 전극은 상기 외곽 부유 전극의 개방된 공간부로 형성된 부분이다른 부분보다 좁은 폭으로 형성된 박막 트랜지스터.

## 청구항 9

제 7 항에 있어서, 상기 복수의 부유 전극 각각은 소정 폭을 갖는 평면부;

상기 평면부의 일측 및 타측으로부터 일 방향으로 연장된 두 돌출부; 및

상기 평면부와 두 돌출부에 의해 일 방향이 개방된 상기 공간부를 포함하는 박막 트랜지스터.

#### 청구항 10

제 7 항에 있어서, 상기 부유 전극과 인접한 부유 전극을 각각 연결하기 위한 연결 전극을 더 포함하는 박막 트랜지스터.

#### 청구항 11

제 10 항에 있어서, 상기 연결 전극에 의해 연결되지 않은 인접한 부유 전극의 공간부에 형성된 브릿지 전극을 더 포함하는 박막 트랜지스터.

#### 청구항 12

제 11 항에 있어서, 상기 브릿지 전극은 일방향으로 평행하게 형성된 평면부; 및

상기 평면부의 일측 및 타측으로부터 일 방향으로 연장되어 상기 부유 전극의 공간부까지 형성된 돌출부를 포함 하는 박막 트랜지스터.

#### 청구항 13

제 12 항에 있어서, 상기 부유 전극의 상기 공간부에 형성된 상기 소오스 전극, 드레인 전극 및 브릿지 전극과 상기 부유 전극 사이의 채널은 각각 3.5 내지 4.5½m의 길이를 갖는 박막 트랜지스터.

#### 청구항 14

제 13 항에 있어서, 상기 부유 전극과 상기 공간부에 형성된 상기 소오스 전극, 드레인 전극 및 브릿지 전극과 상기 부유 전극 사이의 전체 채널 길이는 14 내지 184m인 박막 트랜지스터.

#### 청구항 15

게이트 라인, 데이터 라인, 화소 전극 및 박막 트랜지스터가 형성된 하부 기판과 공통 전극이 형성된 상부 기판에 의해 화상을 표시하는 표시부; 및

상기 표시부 외측의 상기 하부 기판에 형성되는 복수의 박막 트랜지스터를 포함하며, 상기 게이트 라인에 제어 전압을 인가하는 게이트 구동부를 포함하며,

상기 표시부 및 게이트 구동부의 상기 박막 트랜지스터들이 U-타입으로 형성된 표시 장치.

#### 청구항 16

제 15 항에 있어서, 상기 게이트 구동부는 제 1 게이트 전극과, 복수의 돌출부와 돌출부 사이의 공간부가 형성 된 제 1 소오스 전극 및 제 1 드레인 전극의 상기 돌출부가 대응하는 상기 공간부에 형성된 적어도 하나의 제 1 박막 트랜지스터를 포함하는 표시 장치.

#### 청구항 17

제 16 항에 있어서, 상기 제 1 게이트 전극과 제 1 소오스 전극 사이의 캐패시턴스 및 상기 제 1 게이트 전극과 상기 제 1 드레인 전극 사이의 캐패시턴스가 동일한 표시 장치.

## 청구항 18

제 15 항에 있어서, 상기 게이트 구동부는 제 2 게이트 전극과, 일 방향으로 개방된 복수의 부유 전극과, 외측의 두 부유 전극의 공간부에 제 2 소오스 전극 및 제 2 드레인 전극이 형성된 적어도 하나의 제 2 박막 트랜지스터를 포함하는 표시 장치.

#### 청구항 19

제 18 항에 있어서, 상기 제 2 게이트 전극 및 상기 제 2 소오스 전극은 클럭 단자에 연결되는 표시 장치.

#### 청구항 20

제 18 항에 있어서, 상기 제 2 소오스 전극과 상기 제 2 드레인 전극이 상기 공간부 상에 형성된 부유 전극과 인접한 부유 전극의 공간부에 형성된 브릿지 전극을 더 포함하는 표시 장치.

#### 청구항 21

제 20 항에 있어서, 상기 부유 전극과 상기 공간부에 형성된 상기 소오스 전극, 드레인 전극 및 브릿지 전극과 상기 부유 전극 사이의 전체 채널 길이는 14 내지 18µm인 표시 장치.

## 명 세 서

#### 발명의 상세한 설명

#### 기술분야

본 발명은 박막 트랜지스터 및 표시 장치에 관한 것으로, 특히 하부 기판의 주변부에 형성되는 게이트 구동부를 이루는 박막 트랜지스터 및 이를 구비하는 표시 장치에 관한 것이다.

#### 배경기술

- 정판 표시 장치 중의 하나인 액정 표시 장치(Liquid Crystal Display; LCD)는 화소 전극 등이 형성된 하부 기판과 공통 전극 등이 형성된 상부 기판 사이에 액정이 마련되어 화상을 표시하는 액정 표시 패널과, 액정 표시 패널을 구동시키기 위한 구동부를 포함한다. 이러한 액정 표시 장치는 액정 표시 패널의 두 전극 사이의 전계를 변화시켜 액정의 광 투과도를 조절함으로서 화상을 표시한다.

- <3> 그런데, 최근들어 액정 표시 장치의 원가 감소를 위해 하부 기판 상에 게이트 구동부를 형성한다. 즉, 하부 기판의 표시부에 박막 트랜지스터, 화소 전극 등을 형성하고, 표시부 이외의 주변부에 게이트 구동부를 형성한다. 게이트 구동부는 복수의 스테이지를 포함하여 외부의 클럭 신호와 반전된 클럭 신호 그리고 제어 신호인 프레임시작 신호에 따라 복수의 게이트 라인에 게이트 턴온 전압 또는 게이트 턴오프 전압을 인가한다. 이를 통해 1 프레임 동안 하부 기판의 표시부 내의 박막 트랜지스터를 순차적으로 턴온시킨다. 또한, 게이트 구동부의 각 스테이지는 복수의 비정질 실리콘 박막 트랜지스터로 형성된 비정질 실리콘 게이트(Amorphous Silicon Gate; ASG)회로이다. 이러한 비정질 실리콘 게이트 회로는 게이트 드라이버 IC와 동일 또는 유사한 동작을 수행한다.

- 세이트 구동부의 일 스테이지를 이루는 복수의 박막 트랜지스터는 상기 신호들에 응답하여 연결된 게이트 라인에 게이트 턴온 전압 또는 턴오프 전압을 인가하는 스위치로서 동작한다. 게이트 구동부를 이루는 복수의 박막트랜지스터는 표시부의 박막 트랜지스터와 동시에 형성된다.

- 일반적으로 박막 트랜지스터는 소오스 전극이 직선 형태로 형성된 I-타입과, 소오스 전극이 U자형으로 형성된 U-타입으로 디자인된다. 그런데, 표시부의 박막 트랜지스터는 U-타입으로 형성되는데 반해, 게이트 구동부의 박막 트랜지스터는 일부가 U-타입으로 형성되고 일부가 I-타입으로 형성된다. 즉, 복수의 박막 트랜지스터중에서 게이트-드레인간 캐패시턴스(Cgd)와 게이트-소오스간 캐패시턴스(Cgs)의 비율을 1:1로 설정하기 위한 박막 트랜지스터들과 저항 확보를 위해 채널 길이를 길게 형성하는 박막 트랜지스터가 I-타입으로 제조된다.

- <6> 그런데, 소오스 및 드레인 전극을 형성하기 위한 식각 공정시 노광 후 잔존하는 감광막의 두께 차이로 인해 I-타입으로 형성되는 박막 트랜지스터들의 채널로 작용되는 활성층이 U-타입으로 형성되는 박막 트랜지스터들에 비해 더 많이 제거된다. 이에 따라 표시부와 게이트 구동부의 박막 트랜지스터의 활성층의 두께 차가 예를들어 1000~2000Å 정도 차이나게 된다. 또한, 하프-톤(half-tone) 마스크를 이용하여 채널 길이를 길게 확보하기 위한 박막 트랜지스터는 전극 사이의 활성층이 완전히 제거될 수 있다. 따라서, 게이트 구동부의 박막 트랜지스터의 활성층은 안정적인 채널로서 기능하지 못하여 게이트 구동부의 동작에 문제가 발생한다.

#### 발명의 내용

#### 해결 하고자하는 과제

- <7> 본 발명은 액정 표시 패널의 주변부에 형성되며, U-타입으로 형성되는 박막 트랜지스터를 제공한다.

- <8> 본 발명은 액정 표시 패널의 주변부에 U-타입으로 형성되며, 게이트-드레인간 캐패시턴스(Cgd)와 게이트-소오스

간 캐패시턴스(Cgs)의 비율이 1:1인 박막 트랜지스터 및 채널 길이가 긴 박막 트랜지스터를 제공한다.

본 발명은 게이트-드레인간 캐패시턴스(Cgd)와 게이트-소오스간 캐패시턴스(Cgs)의 비율이 1:1인 박막 트랜지스 터와 채널 길이가 긴 박막 트랜지스터가 액정 표시 패널의 주변부에 U-타입으로 형성된 표시 장치를 제공한다.

#### 과제 해결수단

- <10> 본 발명의 일 양태에 따른 박막 트랜지스터는 게이트 전극; 상기 게이트 전극 상에 형성된 절연막 및 활성층; 상기 활성층 상에 각각 형성되며, 복수의 돌출부와 돌출부 사이의 공간부를 각각 갖는 소오스 전극 및 드레인 전극을 포함하며, 상기 소오스 전극 및 드레인 전극의 돌출부가 대응하는 전극의 상기 공간부에 서로 이격되어 형성된다.

- <11> 상기 게이트 전극과 소오스 전극의 중첩 면적 및 상기 게이트 전극과 상기 드레인 전극의 중첩 면적이 동일하며, 상기 소오스 전극 및 드레인 전극은 동일 면적 및 동일 형상으로 형성될 수 있다.

- <12> 상기 소오스 전극은 일 방향으로 형성된 평면부; 상기 평면부로부터 일 방향으로 연장되며, 서로 이격된 복수의 돌출부; 및 상기 평면부 및 상기 복수의 돌출부에 의해 일 방향이 개방된 복수의 공간부를 포함한다.

- <13> 상기 드레인 전극은 일 방향으로 형성된 평면부; 상기 평면부로부터 타 방향으로 연장되며, 서로 이격된 복수의 돌출부; 및 상기 평면부 및 상기 복수의 돌출부에 의해 타 방향이 개방된 복수의 공간부를 포함한다.

- <14> 상기 소오스 전극의 돌출부와 상기 드레인 전극의 돌출부 사이의 채널은 2.0 내지 2.5㎞의 길이를 갖는다.

- <15> 본 발명의 다른 양태에 따른 박막 트랜지스터는 게이트 전극; 상기 게이트 전극 상에 형성된 절연막 및 활성층; 상기 활성층 상에 각각 형성되며, 일 방향이 개방되어 형성된 복수의 부유 전극; 및 외곽 부유 전극의 개방된 공간부에 형성된 소오스 전극 및 드레인 전극을 포함한다.

- <16> 상기 소오스 전극 및 드레인 전극은 상기 외곽 부유 전극의 개방된 공간부로 형성된 부분이 다른 부분보다 좁은 폭으로 형성된다.

- <17> 상기 복수의 부유 전극 각각은 소정 폭을 갖는 평면부; 상기 평면부의 일측 및 타측으로부터 일 방향으로 연장 된 두 돌출부; 및 상기 평면부와 두 돌출부에 의해 일 방향이 개방된 상기 공간부를 포함한다.

- <18> 상기 부유 전극과 인접한 부유 전극을 각각 연결하기 위한 연결 전극을 더 포함한다.

- <19> 상기 연결 전극에 의해 연결되지 않은 인접한 부유 전극의 공간부에 형성된 브릿지 전극을 더 포함한다.

- <20> 상기 브릿지 전극은 일방향으로 평행하게 형성된 평면부; 및 상기 평면부의 일측 및 타측으로부터 일 방향으로 연장되어 상기 부유 전극의 공간부까지 형성된 돌출부를 포함한다.

- <21> 상기 부유 전극의 상기 공간부에 형성된 상기 소오스 전극, 드레인 전극 및 브릿지 전극과 상기 부유 전극 사이의 채널은 각각 3.5 내지 4.5½m의 길이를 갖는다.

- <22> 상기 부유 전극과 상기 공간부에 형성된 상기 소오스 전극, 드레인 전극 및 브릿지 전극과 상기 부유 전극 사이의 전체 채널 길이는 14 내지 18,m이다.

- <23> 본 발명의 또다른 양태에 따른 표시 장치는 게이트 라인, 데이터 라인, 화소 전극 및 박막 트랜지스터가 형성된 하부 기판과 공통 전극이 형성된 상부 기판에 의해 화상을 표시하는 표시부; 및 상기 표시부 외측의 상기 하부 기판에 형성되는 복수의 박막 트랜지스터를 포함하며, 상기 게이트 라인에 제어 전압을 인가하는 게이트 구동부를 포함하며, 상기 표시부 및 게이트 구동부의 상기 박막 트랜지스터들이 U-타입으로 형성된다.

- <24> 상기 게이트 구동부는 제 1 게이트 전극과, 복수의 돌출부와 돌출부 사이의 공간부가 형성된 제 1 소오스 전극 및 제 1 드레인 전극의 상기 돌출부가 대응하는 상기 공간부에 형성된 적어도 하나의 제 1 박막 트랜지스터를 포함한다.

- <25> 상기 제 1 게이트 전극과 제 1 소오스 전극 사이의 캐패시턴스 및 상기 제 1 게이트 전극과 상기 제 1 드레인 전극 사이의 캐패시턴스가 동일하다.

- <26> 상기 게이트 구동부는 제 2 게이트 전극과, 일 방향으로 개방된 복수의 부유 전극과, 외측의 두 부유 전극의 공간부에 제 2 소오스 전극 및 제 2 드레인 전극이 형성된 적어도 하나의 제 2 박막 트랜지스터를 포함한다.

- <27> 상기 제 2 게이트 전극 및 상기 제 2 소오스 전극은 클럭 단자에 연결된다.

- <28> 상기 제 2 소오스 전극과 상기 제 2 드레인 전극이 상기 공간부 상에 형성된 부유 전극과 인접한 부유 전극의 공간부에 형성된 브릿지 전극을 더 포함한다.

- <29> 상기 부유 전극과 상기 공간부에 형성된 상기 소오스 전극, 드레인 전극 및 브릿지 전극과 상기 부유 전극 사이의 전체 채널 길이는 14 내지 18,m이다.

#### 直 과

- <30> 본 발명에 의하면, 액정 표시 패널의 주변부에 형성되는 게이트 구동부를 이루는 일 박막 트랜지스터를 게이트-드레인간 캐패시턴스(Cgd)와 게이트-소오스간 캐패시턴스(Cgs)의 비율이 1:1이 되고 U-타입으로 형성하기 위해 복수의 돌출부와 돌출부 사이의 공간부를 포함하는 핑거 구조로 소오스 전극 및 드레인 전극을 형성하고, 소오스 전극 및 드레인 전극의 돌출부가 대응하는 전극의 공간부에 형성되도록 한다.

- <31> 또한, 액정 표시 패널의 주변부에 형성되는 게이트 구동부를 이루는 타 박막 트랜지스터의 채널 길이를 길게 형성하여 충분한 저항을 갖도록 하기 위해 U-타입 부유 전극을 복수 형성하고, 일 부유 전극 및 타 부유 전극의 공간부에 소오스 전극 및 드레인 전극을 형성한다.

- <32> 따라서, 액정 표시 패널의 하부 기판의 표시부와 주변부의 박막 트랜지스터를 동일하게 U-타입으로 형성할 수 있어 표시부와 주변부의 박막 트랜지스터 제조시 패터닝 균일성을 확보할 수 있다. 또한, 동일 제조 공정으로 표시부와 주변부의 박막 트랜지스터를 제조하더라도 주변부의 박막 트랜지스터의 활성층이 과도하게 제거되는 것을 방지할 수 있어 주변부의 박막 트랜지스터의 오동작을 방지할 수 있다.

#### 발명의 실시를 위한 구체적인 내용

- <33> 이하, 첨부된 도면을 참조하여 본 발명의 실시 예를 상세히 설명하기로 한다. 그러나, 본 발명은 이하에서 개시되는 실시 예에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시 예들은 본 발명의 개시가 완전하도록 하며, 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이다. 도면에서 여러 층 및 각 영역을 명확하게 표현하기 위하여 두께를 확대하여 표현하였으며 도면상에서 동일 부호는 동일한 요소를 지칭하도록 하였다. 또한, 층, 막, 영역, 판 등의 부분이 다른 부분 "상부에" 또는 "위에" 있다고 표현되는 경우는 각 부분이 다른 부분의 "바로 상부" 또는 "바로 위에" 있는 경우뿐만 아니라 각부분과 다른 부분의 사이에 또 다른 부분이 있는 경우도 포함한다.

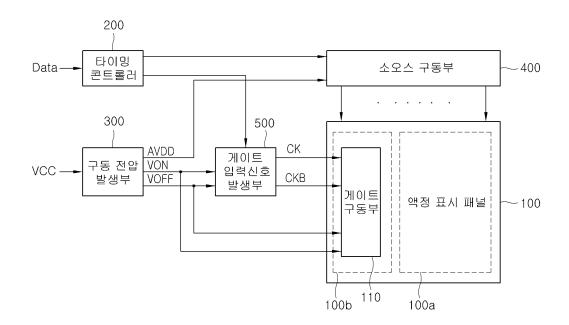

- <34> 도 1은 본 발명의 일 실시 예에 따른 액정 표시 장치를 설명하기 위한 블럭도이다.

- <35> 도 1을 참조하면, 액정 표시 장치는 액정 표시 패널(100), 타이밍 콘트롤러(200), 구동 전압 발생부(300), 소오 스 구동부(400), 그리고 게이트 입력 신호 발생부(500)를 포함한다. 또한, 액정 표시 패널(100) 내에 비정질 실리콘 박막 트랜지스터를 이용한 게이트 구동부(110)가 형성된다.

- 액정 표시 패널(100)은 화소 전극 등이 형성된 하부 기판과, 공통 전극 등이 형성된 상부 기판을 포함하며, 상부 기판과 하부 기판 사이에는 액정이 주입된다. 하부 기판에는 일 방향으로 연장 형성된 복수의 게이트라인과, 복수의 게이트라인과 절연되고 교차되는 방향으로 연장 형성된 복수의 데이터라인과, 게이트라인 및데이터라인이 교차되는 화소 영역에 형성된 화소 전극이 형성된다. 또한, 게이트라인과 연결된 게이트 전극,데이터라인과 연결된 소오스 전극 및 화소 전극과 연결된 드레인 전극을 포함하는 박막 트랜지스터가 일 화소 영역마다 형성된다. 이러한 게이트라인,데이터라인,화소 전극 및 박막 트랜지스터는하부 기판의표시부(100a)에 형성된다. 또한,액정표시 패널(100)의외곽 주변부(100b)에는게이트드라이버IC와동일한기능을수행하는게이트구동부(110)가 형성된다.게이트구동부(110)는복수의박막트랜지스터를포함하며,표시부의박막트랜지스터와동일공정으로형성될수있다.

- <37> 타이밍 콘트롤러(200)는 소오스 구동부(400) 및 게이트 입력 신호 발생부(500)에서 요구되는 타이밍에 맞도록 영상 데이터 신호들(Data)을 조절하여 출력한다. 또한, 타이밍 콘트롤러(200)는 소오스 구동부(400) 및 게이트 입력 신호 발생부(500)를 제어하기 위한 제어 신호들을 출력한다.

- <38> 구동 전압 발생부(300)는 외부로부터 입력된 입력 전압(VCC)을 이용하여 전원 전압(AVDD), 게이트 턴온 전압 (VON), 게이트 턴오프 전압(VOFF), 그리고 공통 전압을 발생한다.

- <39> 소오스 구동부(400)는 복수의 소오스 드라이버 IC로 이루어진다. 소오스 구동부(400)는 타이밍 콘트롤러(200)로 부터 입력된 제어 신호와 구동 전압 발생부(300)로부터 출력된 전원 전압(AVDD)에 응답하여 액정 표시 패널

(100)의 데이터 라인을 구동한다.

- <40> 게이트 입력 신호 발생부(500)는 타이밍 콘트롤러(200)에서 인가된 제어 신호와 구동 전압 발생부(300)로부터 출력된 게이트 턴온 전압(VON)과 게이트 턴오프 전압(VOFF)에 응답하여 액정 표시 패널(100) 내의 게이트 구동 부(110)의 동작을 제어하는 신호들, 예컨대 제 1 클럭 신호(CK)와 제 2 클럭 신호(CKB)를 출력한다. 제 1 클럭 신호(CK)와 제 2 클럭 신호(CKB)는 위상이 반전된 클럭 신호일 수 있다.

- <41> 액정 표시 패널(100) 내의 게이트 구동부(110)는 구동 전압 발생부(300)로부터 출력된 게이트 턴온 전압(VON), 게이트 턴오프 전압(VOFF)과, 게이트 입력 신호 발생부(500)로부터 출력된 제 1 및 제 2 클럭 신호(CK 및 CKB) 에 응답하여 액정 표시 패널(100)의 복수의 게이트 라인을 구동한다.

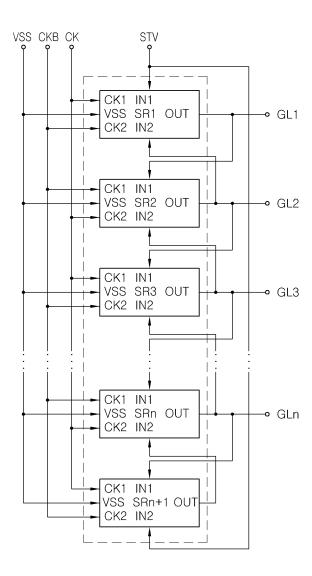

- <42> 도 2는 본 발명의 일 실시 예에 따른 게이트 구동부를 설명하기 위한 블럭도이다.

- <43> 도 2를 참조하면, 게이트 구동부(110)는 복수의 스테이지들(SR1 내지 SRn)과 하나의 더미 스테이지(SRn+1)을 포함하며, 이들이 종속 연결된다. 예를들어, 게이트 라인의 수가 100개인 경우 게이트 라인에 대응하는 100개의 스테이지들과 하나의 더미 스테이지를 포함한다.

- 각 스테이지는 제 1 입력 단자(IN1), 출력 단자(OUT), 제 2 입력 단자(IN2), 제 1 및 제 2 클럭 신호(CK 및 <44> CKB) 입력 단자(CK1 및 CK2), 접지 전압 입력 단자(VSS), 게이트 턴온 전압(VON) 입력 단자, 게이트 턴오프 전 압(VOFF) 입력 단자를 갖는다. 또한, 홀수번째 스테이지들(SR1, SR3, ..., SRn-1)과 더미 스테이지(SRn+1)은 제 1 입력 단자(CK1)로 제 1 클럭 신호(CK)가 입력되고 제 2 입력 단자(CK2)로 제 2 클럭 신호(CKB)가 입력된다. 이에 반해, 짝수번째 스테이지들(SR2, SR4, ..., SRn)은 제 1 입력 단자(CK1)로 제 2 클럭 신호 (CKB)가 입력되고 제 2 입력 단자(CK2)로 제 1 클럭 신호(CK)가 입력된다. 그리고, 첫번째 스테이지(SR1)의 제 1 입력 단자(IN1)에는 타이밍 콘트롤러(200)로부터 출력되는 수직 동기 시작 신호(STV)가 입력되고, 나머지 스 테이지들(SR2 내지 SRn+1)의 제 1 입력 단자(IN1)에는 이전 스테이지(SR1 내지 SRn)의 출력 단자(OUT)가 연결된 다. 그리고, 스테이지들(SR1 내지 SRn)의 제 2 입력 단자(IN2)에는 다음 스테이지들(SR2 내지 SRn+1)의 출력 단 자(OUT)가 연결되고, 더미 스테이지(SRn+1)의 제 2 입력 단자(IN2)에는 타이밍 콘트롤러(200)로부터 출력되는 수직 동기 시작 신호(STV)가 입력된다. 또한, 각 스테이지(SR1 내지 SRn)의 출력 단자(OUT)는 대응하는 각 게이 트 라인(GL1 내지 GLn)에 연결된다. 여기서, 스테이지들(SR1 내지 SRn)의 제 2 입력 단자(IN2)에 입력되는 신호 는 자신의 출력 신호의 듀티 기간 만큼 지연된 신호가 된다. 따라서, 각 스테이지의 출력 신호들이 순차적으로 활성화 구간을 가지고 발생되므로 각 출력 신호의 활성화 구간에 대응되는 액정 표시 패널(100)의 게이트 라인 (GL1 내지 GLn)이 동작된다.

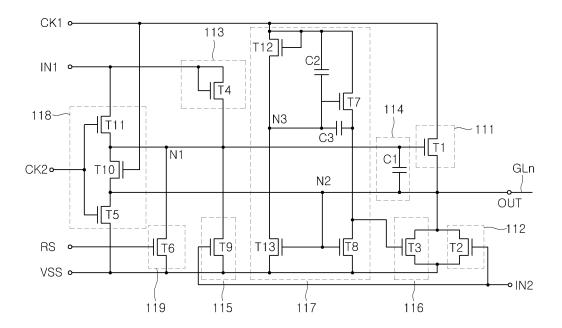

- <45> 도 3은 본 발명의 일 실시 예에 따른 게이트 구동부의 일 스테이지의 상세 회로도이다. 이하에서는 제 1 클럭 신호(CK)가 제 1 클럭 단자(CK1)로 입력되고 제 2 클럭 신호(CKB)가 제 2 클럭 단자(CK2)로 입력되는 제 m 스테 이지(SRm)을 예로하여 설명한다.

- <46> 도 3을 참조하면, 제 m 스테이지(SRm)는 출력 단자(OUT)로 출력되는 출력 신호를 제 1 클럭 단자(CK1)로 입력되는 대체 1 클럭 신호(CK)의 전위로 풀업시키는 풀업부(111)와, 제 2 입력 단자(IN2)로 입력되는 다음 스테이지(n+1)의 출력 신호에 응답하여 출력 단자(OUT)를 풀다운시키는 풀다운부(112)를 포함한다. 풀업부(111)는 게이트 전극이 제 1 노드(N1)에 연결되고, 소오스 전극이 제 1 클럭 단자(CK1)에 연결되며, 드레인 전극이 출력 단자(OUT)에 연결된 제 1 박막 트랜지스터(T1)를 포함한다. 풀다운부(112)는 게이트 전극이 제 2 입력 단자(IN2)에 연결되고, 소오스 전극이 출력 단자(OUT)에 연결되며, 드레인 전극에 접지 전압(VSS)이 인가되는 제 2 박막트랜지스터(T2)를 포함한다.

- <47> 또한, 제 m 스테이지(SRm)는 제 1 입력 단자(IN1)로 입력되는 이전 스테이지의 출력 신호에 응답하여 풀업부 (111)를 턴온시키고, 제 2 입력 단자(IN2)로 입력되는 다음 스테이지의 출력 신호에 응답하여 풀업부(111)를 턴오프시키는 풀업 구동부를 더 포함한다. 풀업 구동부는 버퍼부(113), 충전부(114) 및 제 1 방전부(115)를 포함한다. 버퍼부(113)는 게이트 및 소오스 전극이 제 1 입력 단자(IN1)에 공통 연결되고, 드레인 전극이 제 1 노드(N1)에 연결된 제 4 박막 트랜지스터(T4)를 포함한다. 충전부(114)는 제 1 전극이 제 1 노드(N1)에 연결되고, 제 2 전극이 제 2 노드(N2)에 연결된 제 1 캐패시터(C1)를 포함한다. 그리고, 제 1 방전부(115)는 게이트 전극이 제 2 입력 단자(IN2)에 연결되고, 소오스 전극이 제 1 노드(N1)에 연결되며, 드레인 전극에 접지 전압(VSS)이 제공되는 제 9 박막 트랜지스터(T9)를 포함한다.

- <48> 그리고, 제 m 스테이지(SRm)는 출력 단자(OUT)로 출력되는 출력 신호를 접지 전압(VSS)의 레벨로 홀딩시키는 홀 딩부(116)와 홀딩부(116)의 구동을 제어하는 스위칭부(117)를 더 포함한다. 홀딩부(116)는 게이트 전극이 제 3

노드(N3)에 연결되고, 소오스 전극이 제 2 노드(N2)에 연결되며, 드레인 전극에 접지 전압(VSS)이 제공되는 제 3 박막 트랜지스터(T3)를 포함한다. 스위칭부(117)는 제 7, 제 8, 제 12 및 제 13 박막 트랜지스터(T7, T8, T12 및 T13), 제 2 및 제 3 캐패시터(C2 및 C3)를 포함한다. 제 12 박막 트랜지스터(T12)는 게이트 전극과 소오스 전극이 제 1 클럭 단자(CK1)에 연결되고, 드레인 전극이 제 3 노드(N3)에 연결된다. 제 7 박막 트랜지스터(T7)는 소오스 전극이 제 1 클럭 단자(CK1)에 연결되고, 게이트 전극이 제 2 캐패시터(C2)를 통해 제 1 클럭 단자(CK1)에 연결되며, 드레인 전극은 제 3 노드(N3)에 연결된다. 제 7 박막 트랜지스터(T7)의 게이트 전극과 소오스 전극과의 사이에는 제 3 캐패시터(C3)가 연결된다. 제 13 박막 트랜지스터(T13)는 게이트 전극이 제 2 노드(N2)에 연결되고, 소오스 전극이 제 12 박막 트랜지스터(T12)의 드레인 전극에 연결되며, 드레인 전극에는 접지 전압(VSS)이 제공된다. 제 8 박막 트랜지스터(T8)는 게이트 전극에 제 2 노드(N2)에 연결되고, 소오스 전극이 제 7 박막 트랜지스터(T7)의 드레인 전극에 연결되며, 드레인 전극에 연결되며, 드레인 전극에 연결되다.

- <49> 또한, 제 m 스테이지(SRm)는 리플 방지부(118) 및 리셋부(119)를 더 포함한다. 리플 방지부(118)는 제 5, 제 10 및 제 11 박막 트랜지스터(T5, T10 및 T11)를 포함한다. 제 5 박막 트랜지스터(T5)는 게이트 전극이 제 2 클릭 단자(CK2)에 연결되고, 소오스 전극이 제 2 노드(N2)에 연결되며, 드레인 전극에 접지 전압(VSS)이 제공된다. 제 10 박막 트랜지스터(T10)는 게이트 전극이 제 1 클릭 단자(CK1)에 연결되고, 소오스 전극이 제 11 박막 트렌지스터(T11)의 드레인 전극에 연결되며, 드레인 전극이 제 2 노드(N2)에 연결된다. 그리고, 제 11 박막 트랜지스터(T11)는 게이트 전극이 제 2 클릭 단자(CK2)에 연결되고, 소오스 전극이 제 1 입력 단자(IN1)에 연결되며, 드레인 전극이 제 1 노드(N1)에 연결되다. 리셋부(119)는 게이트 전극이 마지막 스테이지의 출력 신호가 인가되는 리셋 단자(RS)와 연결되고, 소오스 전극이 제 1 노드(N1)에 연결되며, 드레인 전극에 접지 전압(VSS)이 제공되는 제 6 박막 트랜지스터(T6)를 포함한다.

- <50> 상기 스테이지에서 제 6, 제 7, 제 8 및 제 9 박막 트랜지스터(T6, T7, T8 및 T9)는 게이트-소오스간 캐패시턴 스(Cgs)와 게이트-드레인간 캐패시턴스(Cgd)의 비가 1:1이 되어야 하고, 제 12 박막 트랜지스터(T12)는 채널 길 이(channel length)가 다른 트랜지스터들에 비해 길게, 예를들어 14μm 이상으로 디자인되어야 한다. 즉, 풀업부 (111)의 제 1 박막 트랜지스터(T1)의 게이트 전극이 제 6 및 제 9 박막 트랜지스터(T6 및 T9)에 의해 제어되는 데, 제 6 및 제 9 박막 트랜지스터(T6 및 T9)의 기생 캐패시턴스가 다르면 제 1 노드(N1)의 전위가 변하게 되고, 이에 의해 풀업부(111)의 제 1 박막 트랜지스터(T1)가 오동작될 수 있다. 또한, 홀딩부(116)의 제 3 박막 트랜지스터(T3)의 게이트 전극이 제 7 및 제 8 박막 트랜지스터(T7 및 T8)에 의해 제어되는데, 제 7 및 제 8 박 막 트랜지스터(T7 및 T8)의 기생 캐패시턴스가 다르면 제 3 노드(N3)의 전위가 변하게 되고, 이에 의해 홀딩부 (116)의 제 3 박막 트랜지스터(T3)가 오동작될 수 있다. 따라서, 제 6, 제 7, 제 8 및 제 9 박막 트랜지스터 (T6, T7, T8 및 T9)는 게이트-소오스간 캐패시턴스(Cgs)와 게이트-드레인간 캐패시턴스(Cgd)를 1:1로 유지해야 한다. 그리고, 제 12 박막 트랜지스터(T12)는 저항 확보를 위해 채널 길이가 14㎜ 이상으로 형성되어야 하는데, 이는 제 1 클럭 단자(CK1)를 통해 로우 레벨의 신호가 인가되고 제 3 노드(N3)가 고전위를 유지할 경우 제 3 노 드(N3)로부터 제 1 클럭 단자(CK1)로 전류가 흐를 수 있기 때문에 충분한 저항을 확보하여 이를 방지하기 위함 이다. 이를 위해 종래에는 제 6, 제 7, 제 8, 제 9 및 제 12 박막 트랜지스터(T6, T7, T8, T9 및 T12)가 I-타 입으로 형성되고, 그 이외의 박막 트랜지스터들은 U-타입으로 형성되었다. 그러나, 본 발명은 게이트 구동부의 모든 박막 트랜지스터들을 U-타입으로 형성하고, 특히 제 6, 제 7, 제 8, 제 9 및 제 12 박막 트랜지스터(T6, T7, T8, T9 및 T12)는 아래와 같은 구조로 형성된다.

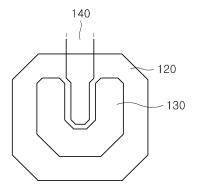

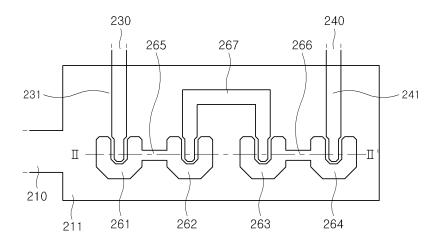

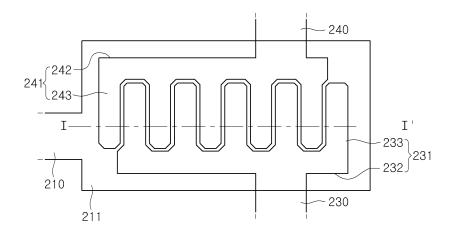

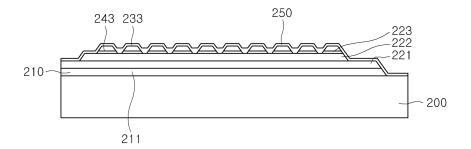

- <51> 도 4는 본 발명의 일 실시 예에 따른 게이트-소오스간 캐패시턴스(Cgs)와 게이트-드레인간 캐패시턴스(Cgd)를 1:1로 유지하는 박막 트랜지스터의 평면도이고, 도 5는 도 4의 I-I' 라인을 따라 절취한 상태의 단면도이다. 이러한 박막 트랜지스터는 예를들어 제 6, 제 7, 제 8 및 제 9 박막 트랜지스터(T6, T7, T8 및 T9)이다. 또한, 도 6은 표시부에 형성되는 박막 트랜지스터의 평면도이다.

- <52> 도 4 및 도 5를 참조하면, 본 발명의 일 실시 예에 따른 박막 트랜지스터는 일 방향으로 형성된 제 1 전극 라인 (210)과, 제 1 전극 라인(210)으로부터 돌출되어 형성된 제 1 전극(211)과, 제 1 전극 라인(210)과 절연되어 타 방으로 형성된 제 2 전극 라인(230)과, 제 2 전극 라인(230)으로부터 분기되어 제 1 전극(211) 상부에 형성된 제 2 전극(231)과, 제 1 전극 라인(210)과 절연되고 제 2 전극 라인(230)과 이격되어 형성된 제 3 전극 라인 (240)과, 제 3 전극 라인(240)으로부터 분기되어 제 1 전극(211) 상부에 제 2 전극(231)과 이격되어 형성된 제 3 전극(241)을 포함한다.

- <53> 제 1 전극 라인(210)은 기판(200) 상부에 예를들어 가로 방향으로 형성되고, 제 1 전극 라인(210)으로부터 소정 폭으로 돌출되어 제 1 전극(211)이 형성된다. 제 1 전극(211)은 제 1 전극 라인(210)보다 바람직하게는 큰 폭으로 형성되며, 제 1 전극 라인(210) 및 제 1 전극(211)은 도 6에 도시된 액정 표시 패널(100) 표시부(100a)의 게

이트 전극(120)과 동시에 형성될 수 있다.

- <54> 제 1 전극 라인(210) 및 제 1 전극(211)이 형성된 기판(200) 상부에 절연막(221)이 형성된다. 절연막(221)은 산화 실리콘(SiO<sub>2</sub>) 또는 질화 실리콘(SiNx) 등의 무기 절연막을 이용하여 단일층 또는 다중층으로 형성될 수있다. 또한, 절연막(221)은 액정 표시 패널(100) 표시부의 게이트 절연막(미도시)과 동시에 형성될 수 있다.

- <55> 제 1 전극(211) 상부의 절연막(221) 상부에는 제 1 반도체 물질로 이루어진 활성층(222)이 형성되며, 활성층 (222)의 상부에는 제 2 반도체 물질로 이루어진 오믹 콘택층(223)이 형성된다. 활성층(222)은 제 1 전극(211)과 완전 중첩되도록 형성될 수 있고, 제 1 전극(211)과 일부 중첩되도록 형성될 수 있다. 즉, 활성층(222)은 제 1 전극(211)와 동일 사이즈로 형성될 수 있고, 제 1 전극(211)보다 작은 사이즈로 형성될 수 있다. 여기서, 제 1 반도체 물질은 비정질 실리콘 등을 포함하고, 제 2 반도체 물질은 실리사이드 또는 n형 불순물이 고농도로 도핑되어 있는 n+ 수소화 비정질 실리콘 등을 포함한다. 활성층(222) 및 오믹 콘택층(223) 또한 액정 표시 패널 (100)의 표시부의 활성층 및 오믹 콘택층과 동시에 형성될 수 있다.

- <56> 제 2 전극 라인(230)은 제 1 전극 라인(210)과 교차되는 방향, 예를들어 세로 방향으로 형성되며, 평면상으로 제 1 전극(211) 하측으로부터 상향 연장되어 제 1 전극(211) 상부까지 형성된다. 제 2 전극(231)은 제 2 전극라인(230)으로부터 분기되어 제 2 전극 라인(230)보다 큰 폭으로 형성되며, 제 1 전극(211)과 중첩되어 형성된다. 제 2 전극(231)은 세로로 일정 폭을 갖고 가로로 일정 길이를 갖는 평면부(232)와, 평면부(232)로부터 상방으로 소정 길이로 돌출되며 서로 이격된 복수의 돌출부(233)와, 돌출부(233) 사이의 공간부를 포함한다. 즉, 제 2 전극(231)은 복수의 핑거 형상으로 형성된다.

- <57> 제 3 전극 라인(240)은 제 1 전극 라인(210)과 교차되는 방향, 예를들어 세로 방향으로 형성되며, 평면상으로 제 1 전극(211) 상측으로부터 하향 연장되어 제 1 전극(211) 상부까지 형성된다. 제 3 전극(241)은 제 3 전극라인(240)으로부터 분기되어 제 3 전극 라인(240)보다 큰 폭으로 형성되며, 제 1 전극(211)과 일부 중첩되어 형성된다. 제 3 전극(241)은 세로로 일정 폭을 갖고 가로로 일정 길이를 갖는 평면부(242)와, 평면부(242)로부터하방으로 소정 길이로 돌출된 복수의 돌출부(243)와, 돌출부(243) 사이의 공간부를 포함한다. 즉, 제 3 전극(241)은 복수의 핑거 형상으로 형성된다.

- <58> 여기서, 제 2 전극(231)의 평면부(232)과 제 3 전극(241)의 평면부(242)는 서로 이격되어 형성되며, 제 2 전극(231)의 돌출부(233) 사이의 공간에 제 3 전극(241)의 돌출부(243)가 형성되고, 제 3 전극(241)의 돌출부(243)사이의 공간부에 제 2 전극(231)의 돌출부(233)가 형성된다. 즉, 핑거 형상의 제 2 전극(231)과 핑거 형상의 제 3 전극(241)이 서로 소정 간격 이격되어 포개지게 형성된다. 그리고, 제 2 전극 라인(230)과 제 3 전극 라인(240)은 동일 공정에 의해 형성되며, 도 6에 도시된 액정 표시 패널(100)의 표시부(100a)에서 소오스 전극(130) 및 드레인 전극(140)과 동시에 형성될 수 있다. 따라서, 제 2 전극 라인(230)과 제 3 전극 라인(240)은 표시부(100a)의 소오스 전극(130) 및 드레인 전극(140)과 동일 폭 및 동일 간격으로 형성될 수 있다.

- 또한, 제 1 전극(211)이 게이트 전극이고, 제 2 전극(231) 및 제 3 전극(241)이 각각 드레인 전극 및 소오스 전극이 될 수 있고, 제 2 전극(231) 및 제 3 전극(241)이 소오스 전극 및 드레인 전극이 될 수 있다. 따라서, 제 7 박막 트랜지스터(T7)의 경우 제 1 전극(211)이 제 1 전극 라인(210)을 통해 제 1 클럭 단자(CK1)과 연결되고, 제 2 전극(231) 및 제 3 전극(241)은 제 2 전극 라인(230) 및 제 3 전극(240)을 통해 제 1 클럭 단자(CK1) 또는 제 3 노드(N3)에 연결될 수 있다. 여기서, 돌출부(233) 및 243)는 식각 공정 후 감광막을 제거한 후 측정된임계치수(Critical Dimension; CD), 즉 ACI(After Cleaning Inspection) 기준으로 예를들어 4.5~5.0μm의 폭으로 형성되며, 제 2 전극(231)의 돌출부(233)과 제 3 전극(241)의 돌출부(243) 사이의 간격은 ACI(After Cleaning Inspection) 기준으로 예를들어 2.0~2.5μm로 형성된다. 돌출부(233) 및 243)의 간격은 채널 길이(channel length)가 된다. 따라서, 제 2 전극(231)의 돌출부(233) 사이의 공간부 및 제 3 전극(241)의 돌출부(243) 사이의 공간부는 ACI(After Cleaning Inspection) 기준으로 예를들어 8.5~10μm의 폭으로 형성된다.

- <60> 그리고, 제 2 전극 라인(230) 및 제 3 전극 라인(240)을 포함한 전체 상부에 보호막(250)이 형성된다. 보호막 (250)은 산화 실리콘(SiO<sub>2</sub>) 또는 질화 실리콘(SiNx) 등의 무기 절연막 또는 유기 절연막을 이용하여 단일층 또는 다중층으로 형성될 수 있다.

- <61> 상기한 바와 같이 제 2 전극(231)과 제 3 전극(241)이 바람직하게는 동일 면적, 더욱 바람직하게는 동일 형상으로 형성되어 서로 포개지기 때문에 제 1 전극(211)과 제 2 전극(231)의 중첩 면적과 제 1 전극(211)과 제 3 전극(241)의 중첩 면적이 동일하므로 게이트-소오스간 캐패시턴스(Cgs)와 게이트-드레인간 캐패시턴스(Cgd)의 비가 1:1로 동일하게 유지된다.

- <62> 한편, 본 실시 예에서는 제 2 전극(230) 및 제 3 전극(240)의 핑거, 즉 돌출부(231 및 241)가 각각 5개 형성된 것으로 설명되었으나, 돌출부는 2개 이상 형성될 수 있다.

- <63> 또한, 상기에서는 기판(200) 상부에 제 1 전극 라인(210)을 형성한 후 제 1 전극 라인(210) 상부에 제 2 전극라인(230) 및 제 3 전극 라인(240)을 형성한 역 스태거형(Inverted Staggered Type) 구조를 설명하였다. 그러나, 기판(200) 상부에 제 2 및 제 3 전극 라인(230 및 240)을 형성한 후 제 2 및 제 3 전극 라인(230 및 240) 상부에 제 1 전극 라인(210)을 형성하는 스태거형(Staggered Type) 구조에도 동일하게 적용할 수 있다. 상기한스태거형 구조에 대해서는 별도의 도면을 이용한 설명은 생략한다.

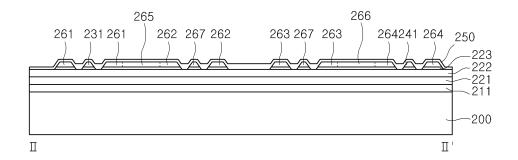

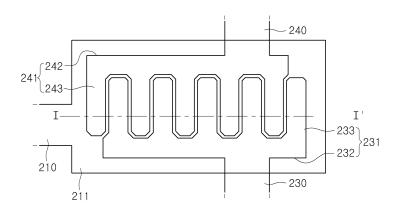

- <64> 도 7은 본 발명의 다른 실시 예에 따른 저항 확보를 위해 긴 채널 길이를 갖는 박막 트랜지스터의 평면도이고, 도 8은 도 7의 Ⅱ-Ⅱ' 라인을 따라 절취한 상태의 단면도이다. 이러한 박막 트랜지스터는 예를들어 제 12 박막 트랜지스터(T12)이다.

- <65> 도 7 및 도 8을 참조하면, 본 발명의 다른 실시 예에 따른 박막 트랜지스터는 일 방향으로 형성된 제 1 전극 라인(210)과, 제 1 전극 라인(210)으로부터 돌출된 제 1 전극(211)과, 제 1 전극 라인(210)과 절연되어 형성된 제 2 전극 라인(230)과, 제 2 전극 라인(230)으로부터 연장되어 제 1 전극(211) 상부에 형성된 제 2 전극(231)과, 제 1 전극 라인(210)과 절연되고 제 2 전극 라인(230)과 이격되어 형성된 제 3 전극 라인(240)과, 제 3 전극 라인(240)으로부터 연장되어 제 1 전극(211) 상부에 형성된 제 3 전극(241)을 포함한다. 여기서, 제 2 및 제 3 전 극(231 및 241)은 제 2 및 제 3 전극 라인(230 및 240)이 제 1 전극(211)과 중첩되는 영역으로 정의한다. 또한, 제 1 전극(211)과 절연되어 제 1 전극(211) 상부에 형성되며 U자 형상으로 형성된 제 1 내지 제 4 부유 전극(261, 262, 263 및 264)과, 제 1 및 제 2 부유 전극(261 및 262)을 연결하는 제 1 연결 전극(265)과, 제 3 및 제 4 부유 전극(263 및 264)을 연결하는 제 2 연결 전극(266)과, 제 2 및 제 3 부유 전극(262 및 263)의 U자 형상의 공간부에 형성된 브릿지 전극(267)을 더 포함한다.

- <66> 제 1 전극 라인(210)은 기판(200) 상부에 예를들어 가로 방향으로 형성되고, 제 1 전극 라인(210)으로부터 제 1 전극 라인(210)보다 바람직하게는 큰 폭으로 돌출되어 제 1 전극(211)이 형성된다. 제 1 전극 라인(210) 및 제 1 전극(211)은 도 6에 도시된 액정 표시 패널(100) 표시부(100a)의 게이트 전극(120)과 동시에 형성될 수 있다.

- <67> 제 1 전극 라인(210) 및 제 1 전극(211)이 형성된 기판(200) 상부에 절연막(221)이 형성된다. 그리고, 제 1 전 극(211) 상부의 절연막(221) 상부에는 제 1 반도체 물질로 이루어진 활성층(222)이 형성되며, 활성층(222)의 상부에는 제 2 반도체 물질로 이루어진 오믹 콘택층(223)이 형성된다.

- <68> 제 2 전극 라인(230)은 제 1 전극 라인(210)과 교차되는 방향, 예를들어 세로 방향으로 형성되며, 평면상으로 제 1 전극(211) 상측으로부터 하향 연장되어 형성된다. 제 2 전극 라인(230)으로부터 연장된 제 2 전극(231)은 제 1 전극(211)과 중첩되어 형성되며, 적어도 일부가 제 1 전극(211) 상부의 활성층(222) 상부에 형성된다. 또한, 제 2 전극(231)은 U자 형상의 제 1 부유 전극(261)이 이루는 공간부까지 형성되며, 제 1 부유 전극(261)과 소정 간격 이격되어 형성된다. 여기서, 제 2 전극(231)은 제 1 부유 전극(261)이 이루는 공간부에 형성되는 부분의 폭이 제 2 전극 라인(230)의 폭보다 좁을 수 있다.

- <69> 제 3 전극 라인(240)은 제 1 전극 라인(210)과 교차되는 방향, 예를들어 세로 방향으로 형성되며, 평면상으로 제 1 전극(211) 상측으로부터 하향 연장되어 형성된다. 즉, 제 3 전극 라인(240)은 제 2 전극 라인(230)과 평행하게 형성된다. 또한, 제 3 전극 라인(240)으로부터 연장된 제 3 전극(241)은 제 1 전극(211)과 중첩되어 형성된다. 제 3 전극(231)은 U자 형상의 제 4 부유 전극(264)이 이루는 공간부까지 형성되며, 제 4 부유 전극(264)과 소정 간격 이격되어 형성된다. 여기서, 제 4 부유 전극(264)이 이루는 공간부에 형성되는 제 3 전극(241)의일 부분의 폭이 다른 부분의 폭보다 좁을 수 있다.

- <70> 제 1 내지 제 4 부유 전극(261, 262, 263 및 264)은 U자 형상으로 형성된다. 즉, 제 1 내지 제 4 부유 전극(261, 262, 263 및 264)은 제 1 전극 라인(210)과 평행한 평면부와, 평면부의 일측 및 타측으로부터 평면부와 수직 상방으로 연장된 두 돌출부와, 두 돌출부 사이의 공간부를 포함한다. 또한, 제 1 내지 제 4 부유 전극(261, 262, 263 및 264)은 동일 간격으로 이격되어 형성되는 것이 바람직하다. 그리고, 제 1 연결 전극(265)은 제 1 및 제 2 부유 전극(261 및 262) 사이에 형성되어 이들을 연결하고, 제 2 연결 전극(266)은 제 3 및 제 4 부유 전극(263 및 264) 사이에 형성되어 이들을 연결한다. 또한, 브릿지 전극(267)은 제 1 전극(211) 상부에 형성되어 제 1 전극 라인(210)과 평행한 방향으로 형성된 평면부와, 평면부의 일측 및 타측으로부터 하방 연장되는 두 돌출부를 포함한다. 브릿지 전극(267)의 평면부는 제 2 부유 전극(262)의 공간부에 수직 방향으로 대응되는 영역으로부터 제 3 부유 전극(263)의 공간부에 수직 방향으로 대응되는 영역까지 형성되며, 브릿지(267)의

두 돌출부는 평면부의 일측 및 타측으로부터 하방 연장되어 제 2 및 제 3 부유 전극(262 및 263)의 공간부까지 형성된다. 여기서, 브릿지 전극(267)의 돌출부중에서 제 2 및 제 3 부유 전극(262 및 263)이 이루는 공간부에 형성된 돌출부의 일 부분은 다른 부분보다 폭이 좁게 형성될 수 있다.

- <71> 상기 제 2 전극 라인(230), 제 3 전극 라인(240), 부유 전극들(261, 262, 263, 264 및 267), 그리고 제 1 및 제 2 연결 전극(265 및 266)은 동일 공정에 의해 형성되고, 도 6에 도시된 액정 표시 패널(100)의 표시부(100 a)에서 소오스 전극(130) 및 드레인 전극(140)과 동시에 형성될 수 있다. 그리고, 제 2 전극 라인(230), 제 3 전극 라인(240), 부유 전극들(261, 262, 263, 264 및 267), 그리고 제 1 및 제 2 연결 전극(265 및 266)은 표시부(100a)의 소오스 전극(130) 및 드레인 전극(140)과 동일 폭 및 간격으로 형성될 수 있다.

- <72> 또한, 제 1 전극(211)이 게이트 전극이고, 제 2 전극(231) 및 제 3 전극(241)이 각각 드레인 전극 및 소오스 전 극이 될 수 있고, 제 2 전극(231) 및 제 3 전극(241)이 소오스 전극 및 드레인 전극이 될 수 있다. 따라서, 제 12 트랜지스터(T12)의 경우 제 1 전극(211) 및 제 2 전극(231)이 제 1 전극 라인(210) 및 제 2 전극 라인(230)을 통해 제 1 클릭 단자(CK1)과 연결되고, 제 3 전극(241)은 제 3 노드(N3)에 연결될 수 있다.

- <73> 그리고, 제 1 내지 제 4 부유 전극(261, 262, 263 및 264)은 예를들어 6.0~6.5µm의 폭으로 형성되며, 제 2 전 극(231), 제 3 전극(241), 브릿지(267)의 폭 또한 예를들어 6.0~6.5µm로 형성된다. 또한, 제 1 내지 제 4 부유 전극(261, 262, 263 및 264)이 이루는 공간부에 형성되는 제 2 전극(231), 제 3 전극(241), 브릿지(267)의 돌출부의 일부분은 예를들어 4.5~5.0µm의 폭으로 형성된다. 그리고, 제 1 내지 제 4 부유 전극(261, 262, 263 및 264)과 이들이 이루는 공간부에 형성되는 제 2 전극(231), 제 3 전극(241), 브릿지(267)의 돌출부 사이가 채널 길이(channel length)가 되는데, 채널 길이는 예를들어 3.5~4.5µm의 간격으로 형성되어 전체 채널 길이는 14~18µm가 된다. 따라서, 제 1 내지 제 4 부유 전극(261, 262, 263 및 264)의 두 돌출부 사이의 공간부는 11.5~14.5µm의 폭으로 형성될 수 있다.

- <74> 그리고, 제 2 전극 라인(230) 및 제 3 전극 라인(240)을 포함한 전체 상부에 보호막(250)이 형성된다. 보호막(250)은 산화 실리콘(SiO<sub>2</sub>) 또는 질화 실리콘(SiNx) 등의 무기 절연막 또는 유기 절연막을 이용하여 단일층 또는 다중층으로 형성될 수 있다.

- <75> 한편, 상기 실시 예에서는 제 1 내지 제 4 부유 전극(261, 262, 263 및 264)이 동일 방향으로 개방된 공간부를 갖는 것으로 설명되었으나, 상부 또는 하부 방향 어느 방향으로 개방된 공간부를 갖을 수 있는데, 특히 브릿지 (267)의 두 돌출부가 공간부에 형성되는 제 2 및 제 3 부유 전극(262 및 263)은 동일한 방향을 개방된 공간부를 갖는 것이 바람직하다.

- <76> 상기한 바와 같이 본 발명의 다른 실시 예에 따른 박막 트랜지스터는 U자 형상의 제 1 내지 제 4 부유 전극 (261, 262, 263 및 264)가 제 1 전극(211) 상부에 각각 형성되고, 제 1 및 제 4 부유 전극(261 및 264)의 공간부에 제 2 및 제 3 전극(231 및 241)이 형성되며, 제 2 및 제 3 부유 전극(262 및 263)의 공간부에 브릿지 (267)의 돌출부가 형성된다. 따라서, 제 2 전극(231) 및 제 3 전극(241)과 제 1 내지 제 4 부유 전극(261, 262, 263 및 264) 사이의 채널이 각각 저항으로 작용하여 네개의 저항이 직렬 연결된 것이 되고, 전체 채널 길이는 14~18ょm가 되므로 충분한 저항을 갖게 된다.

#### 도면의 간단한 설명

- <77> 도 1은 본 발명의 일 실시 예에 따른 액정 표시 장치를 설명하기 위한 블럭도.

- <78> 도 2는 본 발명의 일 실시 예에 따른 게이트 구동부를 설명하기 위한 블럭도.

- <79> 도 3은 본 발명의 일 실시 예에 따른 게이트 구동부의 일 스테이지의 상세 회로도.

- <80> 도 4는 본 발명의 일 실시 예에 따른 게이트 구동부의 일 박막 트랜지스터의 평면도.

- <81> 도 5는 도 4의 I-I' 라인을 절취한 상태의 단면도.

- <82> 도 6은 본 발명에 따른 게이트 구동부의 일 박막 트랜지스터와 동시에 형성되는 표시부 박막 트랜지스터의 평면 도.

- <83> 도 7은 본 발명의 다른 실시 예에 따른 게이트 구동부의 타 박막 트랜지스터의 평면도.

- <84> 도 8은 도 7의 Ⅱ-Ⅱ' 라인을 절취한 상태의 단면도.

<85> <도면의 주요 부분에 대한 부호의 설명>

<86> 210 : 제 1 전극 라인 211 : 제 1 전극

<87> 221 : 절연막 222 : 활성층

<88> 223 : 오믹 콘택층 230 : 제 2 전극 라인

<89> 231 : 제 2 전극 240 : 제 3 전극 라인

<90> 241 : 제 3 전극

## 도면

# 도면6